Изобретение относится к импульсной технике и может быть использовано в автоматике и вычислительной технике для контроля импульсных последовательностей.

Цель изобретения - расширение функциональных возможностей за счет контроля последовательности чередования как синхронизированных, так и асинхронных импульсных сигналов.

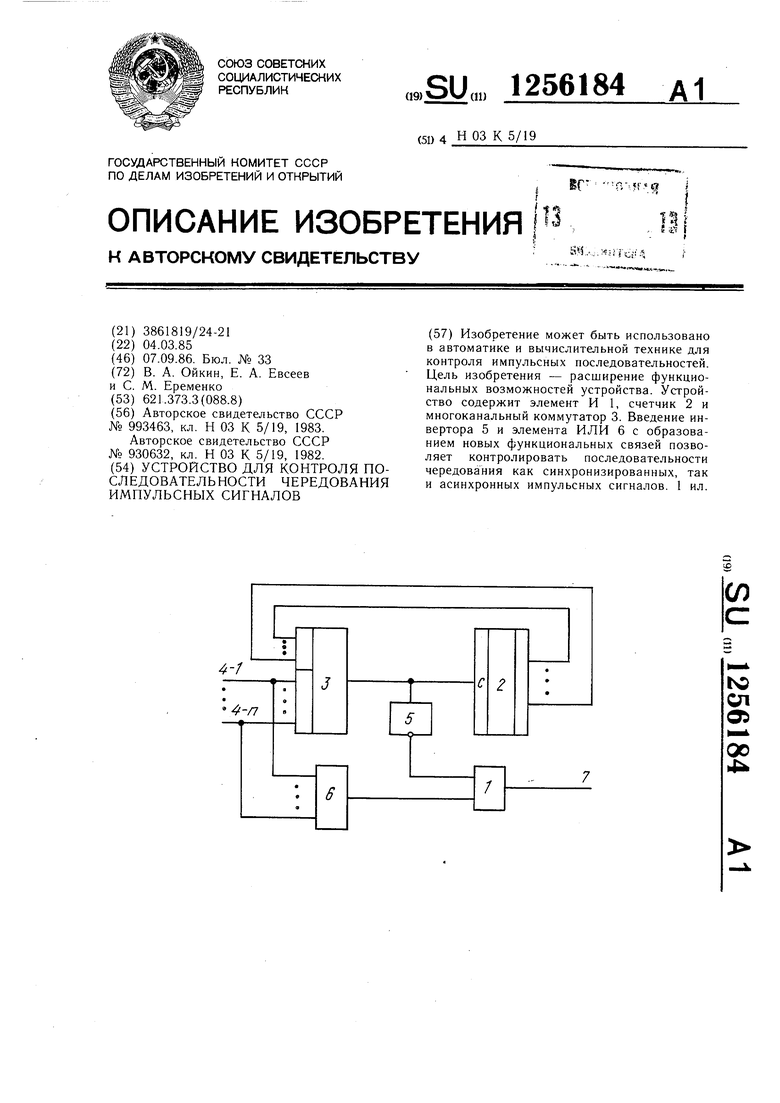

На чертеже представлена электрическая принципиальная схема устройства.

Устройство для контроля последовательности чередования импульсных сигналов содержит элемент И 1, счетчик 2 импульсов, многоканальный коммутатор 3, первая группа входов которого подключена к входным шинам (4-1) -(4-п), а вторая управляющая группа входов соединена с выходами счетчика 2 импульсов, инвертор 5 и элемент ИЛИ 6, выход многоканального коммутатора 3 подключен к входу счетчика 2 и через инвертор 5 к первому входу элемента И 1, второй вход которого соединен с выходом элемента ИЛИ б, входы которого соединены с входными шинами (4-1) - (4-п), выход элемента И 1 подключен к выходной шине 7.

Устройство работает следующим образом.

Перед началом работы счетчик 2 устанавливается в нулевое состояние любым известным способом (цепи сброса не показаны). Выходы счетчика 2, подключенные к второй управляющей группе входов коммутатора 3, задают номер опрашиваемой входной шины. При установке счетчика 2 в нулевое состояние к выходу коммутатора 3 подключается первая входная шина. Сигнал, поступивший на первый вход коммутатора 3, проходит на его выход и вход счетчика 2. По окончании входного сигнала счетчик 2 изменяет свое состояние на по- следуюш,ее и тем самым к выходу коммутатора 3 подключается следующая, т. е. вторая входная шина. При правильном чередовании входных сигналов процесс повторяется. Каждый из поступающих на входные щины {4-1) - (4-п) сигналов также поступает на вход элемента ИЛИ бис его выхода на второй вход элемента И 1. Элемент И 1 первым входом подключен к выходу коммутатора 3 через инвертор 5 и поэтому при отсутствии сигнала на выходе коммутатора 3 элемент И 1 открывается по первому входу и наоборот при наличии сигнала на выходе коммутатора 3 элемент И,1 закрывается по первому входу. При правильном чередовании сигналов на входных шинах (4-1) - (4-п) устройства элемент И 1 открывается по второму входу и закрывается по первому, т. е. на выходе элемента И 1 и на выходной шине 7 сигнал отсутствует.

При нарушении порядка чередования сигналов на входных шинах (4-1) - (4-п), например после прихода сигнала на входную

шину 4-1, поступает сигнал на входную шину 4-3, на выход коммутатора 3 сигнал не проходит, так как код на второй управляющей группе входов коммутатора 3 подключает к его выходу входную шину 4-2. Отсутствие сигнала на выходе коммутатора 3 открывает по первому входу элемент И 1 и сигнал с входной шины 4-3 через элемент ИЛИ 6 проходит через элемент И 1 на выходную шину 7. Наличие сигнала на

выходной шине 7 свидетельствует о нарушении порядка чередования входных импульсов

При поступлении на любой из входов двух импульсов вместо одного устройство формирует на выходной шине 7 сигнал нарушения порядка чередования следующим образом.

По окончании входного сигнала счетчик 2 устанавливается в его следующее положение и подключает к выходу коммутатора 3 следующую входную щину. Сигнал, поступивший вторично на ту же входную шину, не,поступает на выход коммутатора 3 и не закрывает по первому входу элемент И 1, но проходит через элемент ИЛИ 6 на второй вход элемента И I. Так как элемент И 1 оказывается открыт по двум входам, то на его выходе и выходной шине 7 появляется сигнал нарушения порядка чередования.

При наличии на контролируемой входной шине постоянного сигнала счетчик 2

не изменяет своего состояния, так как он работает по заднему фронту входного сигнала и, следовательно, не подключает к выходу коммутатора 3 следующую входную щину. Поступление сигнала на следующую входную шину приводит к формированию

сигнала нарущения порядка чередования ВХОДНЫХ сигналов аналогично. Устройство не связывает время поступления сигналов с какой-либо тактовой частотой, т. е. работоспособно при контроле асинхронных сигналов.

Таким образом, предлагаемое устройство контролирует порядок чередования асинхронных сигналов и формирует сигнал сбоя как в случае нарушения порядка поступления асинхронных сигналов на входные шины, так и при поступлении нескольких сигналов вместо одного (прерывающийся сигнал), а также при наличии на входных шинах постоянного сигнала.

50

Формула изобретения

Устройство для контроля последовательности чередования импульсных сигналов, содержащее элемент И, счетчик импульсов и многоканальный коммутатор, первая группа 55 входов которого подключена к соответствующим входным шинам, а вторая управляющая группа входов соединена с соответствующими выходами счетчика импульсов, отли1256184

3

чающееся тем, что, с гюлью расширенияпервому входу элемента И, второй вход кофуикциональных возможностей, в него вве-торого соединен с выходом элемента ИЛИ,

деиы инвертор и элемент ИЛИ, причем вы- входы которого соединены с соответствуюход многоканального коммутатора подклю-щими входными шинами, а выход элеменчен к входу счетчика и через инвертор кта И подключен к выходной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности чередования импульсных сигналов | 1987 |

|

SU1413711A2 |

| Устройство контроля импульсных последовательностей | 1990 |

|

SU1795539A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2054796C1 |

| Устройство для контроля последовательности чередования импульсных сигналов | 1987 |

|

SU1495985A2 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1984 |

|

SU1215113A1 |

| Устройство для контроля последовательности чередования асинхронных импульсных сигналов | 1978 |

|

SU744953A1 |

| Многоканальное устройство для управления преобразователем | 1980 |

|

SU909793A1 |

| Устройство для контроля последовательности чередования импульсных сигналов | 1987 |

|

SU1432758A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1252930A2 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

Изобретение может быть использовано в автоматике и вычислительной технике для контроля импульсных последовательностей. Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит элемент И 1, счетчик 2 и многоканальный коммутатор 3. Введение инвертора 5 и элемента ИЛИ 6 с образованием новых функциональных связей позволяет контролировать последовательности чередования как синхронизированных, так и асинхронных импульсных сигналов. 1 ил. (Л 1С сл О5 00 4i

| Устройство для контроля последовательности чередования асинхронных импульсных сигналов | 1981 |

|

SU993463A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство контроля импульсных сигналов | 1980 |

|

SU930632A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-04—Подача