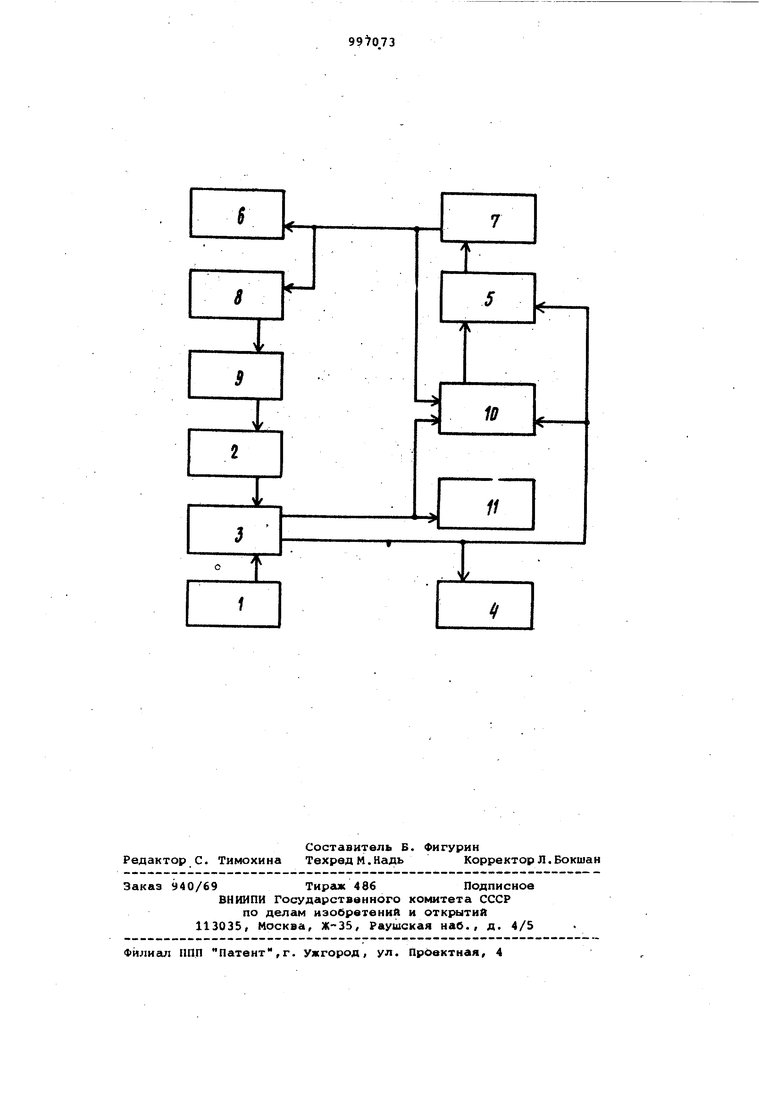

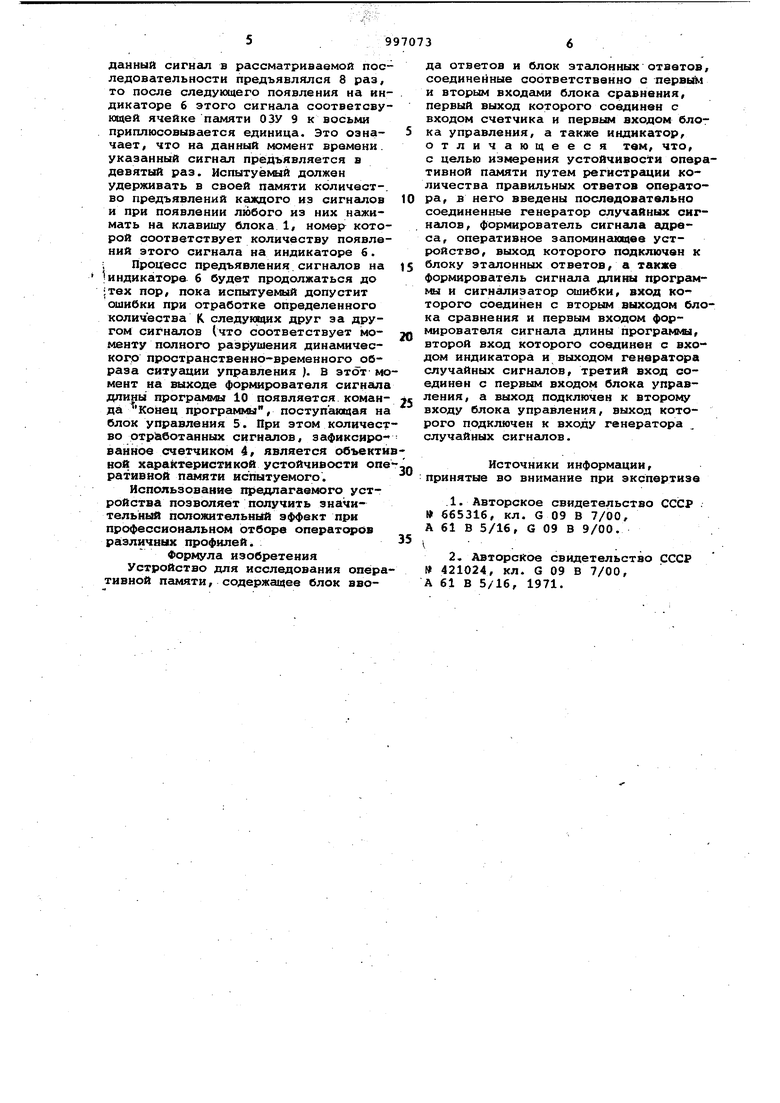

рователь сигнала адреса, оперативное запоминающее устройство, выход которого подключен к блоку эталонных ответов, а также формирователь сигнала длины программы и сигнализатор ошибки, вход которого соединен с вторым выходом блока сравнения и с первым входом формирователя сигнала длины програмьи, второй вход которого соединен с входом индикатора и с выходом генератора случайных сигна лов, третий вход соединен с первым входом блока управления, а выход подключен ко второму входу блока управления, выход которого подключе к входу генератора случайных сигналов. На чертеже изображена структурна электрическая схема устройства для исследования оперативной памяти. Устройство содержит блок ввода ответов 1 и блок эталонных Ответов соединенные соответственно с первым и вторым входами блока сравнения 3, первый выход которого соедичен с входом счетчика 4 и первым входом блока управления 5, и индикатор 6, а также последовательно соединенные генератор случайных сигналов 1, фор мирователь сигнала адреса записи 8, оперативное запоминаквдее устройство t,03y 91 выход которого подключен к блоку эталонных, ответов 3, а также формирователь сигнала длины програм |уы 10 и сигнализатор ошибки И вход которого соединен с вторым выходом блока сравнения 3 и с первым входом формирователя сигнала длины програм мы 10, второй вход которого соедине с входом индикатора бис выходом ге нератора случайных сигналов 7, третий вход соединен с первым входом блока управления 5, а выход подключен ко второму входу блока управления 5, выход которого подключен к входу генератора случайных сигна-. лов 7. Устройство для исследования oneративной памяти работает следующим образом. При подаче команды с блока управ ления 5 на генератор случайных сигналов 7 на выходе последнего появля ется один из сигналов случайного ря да. Этот сигнал реализуется индикат ром 6 в виде ряда,цифр, букв, цвето вых сигналов и т.д. и, кроме того, поступает на формирователь сигнала длины программы 10 и формирователь сигнала адреса, записи 8, где происходит его идентификация с. констай-. тной группой, состоящей из п сигнало после чего в ОЗУ 9 поступает адрес ячейки памяти, соответствующей данному сигналу. Одновременно блок 8 формирует команду, по которой к информации, содержащейся в указанной ячейке памяти, приплюсовывается единица. Всякий раз при появлении на индикаторе 6 данного сигнала по указанному адресу прибавляется единица. Этопроисходит и при предъявлении испытуемому любого другого сигнала с той лишь разницей, что суммиг рование осуществляется в той ячейке пг1мяти ОЗУ , адрес которой соответствует предъявляемому сигналу. Одновременно с окончанием суммирования происходит считывание информации из ячейки, в которую приплюсо|вана единица, и перезапись этой новой информации в блок эталонных ответов 2. При этом содержащаяся ранее в блоке 2 информация автоматически стирается. Следовательно, каждый раз после предъявления испытуемому одного из сигналов случайного ряда на выходе блока эталонных ответов 2 появляется информация о количестве предъявлений на индикаторе б того конкретного сигнала, который индицируется этим индикатором в данный момент времени. В свою очередь, испытуемый должен постоянно удерживать в своей оперативной памяти количество предъявлений каждого из сигналов, так как от этого зависит успешность его работы на устройстве. После отработки испытуемым очередного сигнала на выходе блока ввода ответов 1 появляется информация, которая сопоставляется блоком сравнения 3 с информацией, содержащейся на выходе блока эталонных ответов 2. В случае правильной реакции на выходе блока сравнения 3 формируется команда, поступающая на счетчик 4, формирователь сигнала длины программы 10 и через блок управления 5 на генератор случайных сигналов 7. При этом сумма .отработанных сигналов на блоке 4 увеличивается на единицу, а на выходе генератора 7 появляется следующий сигнал случайного ряда, который отображается индикатором б. Если при отработке какого-либо из сигналов испытуекмй допускает ошибку, то на другом выходе блока сравнения 3 формируется команда, поступакхцая на формирователь сигнала длины програм1уш 10 и на сигнализатор сшибки 11, информирующий испытуемого о неадекватности произведен-ной им управляющей реакции. При этом смены сигнала на индикаторе б не происходит, а испытуемый должен активизировать свою память и повторить попытку. Например, если ранее в ячейке памяти 9 , соответствующей, какому-либо сигналу случайного зафиксировано число 8 и это означало, что

данный сигнал в рассматриваемой последовательности предъявлялся 8 раз, то после следующего появления на индикаторе 6 этого сигнала соответсвующей ячейке памяти ОЗУ 9 к восьми приплюсовывается единица. Это оэначает, что на данный момент времени, указанный сигнал предъявляется в девятый раз. Исшлтуёкг й должен удерживать в своей пг1мяти количест-. во предъявлений каждого из сигналов и при появлении любого из них нажимать на клавишу блока 1, номер которой соответствует количеству появлений этого сигнала на индикаторе 6.

Процесс предъявления сигналов на 1 индикаторе 6 будет продолжаться до тех пор, пока испытуемый допустит ошибки при отработке определенного количества К следукющх друг за другом сигналов (что соответствует моменту полного разрушения динамического пространственно-временного образа ситуации управления ). В этот момент на выходе формирователя сигнгша

длины программы 10 появляется команда Конец прогрг ммы, поступающая на блок управления 5. При этом количество отработанных сигналов, зафиксиро ванное счетчиком 4 является объектиной характеристикой устойчивости oneративной памяти испытуемого.

Использование предлагаемого устройства позволяет получить значительный попожительнЕЛй эффект при профессиональном отборе оператсфов ра:зличных профилей.

Формула изобретения

Устройство для исследования оперативной памяти, содержащее блок ввода ответов и блок эталонных ответов соединенные соответственно с первый и вторым входами блока сравнения, первый выход которого соединен с входом счетчика н первым входом блока управления, а также индикатор, отличающееся тем, что, с целью измерения устойчивости оперативной памяти путем регистрации количества правильных ответов оператора, в него введены последовательно соединенные генератор случайных сигналов, формирователь сигнала адреса, оперативное запоминающее устройство, выход которого подключен к блоку эталонных ответов, а также формирователь сигнгша длины программы и сигнализатор ошибки, вход которого соединен с вторым выходом блока сравнения и первым входом формирователя сигнала длины програмкы, второй вход которого соединен с входом индикатора и выходом генератора случайных сигналов, третий вход соединен с первым входом блока управления, а выход подключен к второму входу блока управления, выход которого подключен к входу генератора случайных сигнсшов.

Источники информации, : принятые во внимание при экспертизе

. 1. Авторское свидетельство СССР . 665316, кл. G 09 В 7/00, А 61 В 5/16, G 09 В 9/00.

I ..

2. Авторское свидетельство СССР 421024, кл. G 09 В 7/00, А 61 В 5/16, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования оперативной памяти | 1986 |

|

SU1404059A1 |

| Устройство для оценки профессиональной пригодности оператора | 1989 |

|

SU1714646A1 |

| Устройство для оценки работы оператора | 1990 |

|

SU1735885A1 |

| Устройство для контроля психофизиологического состояния испытуемого | 1980 |

|

SU960850A1 |

| Устройство для обучения радиотелеграфистов | 1982 |

|

SU1125222A1 |

| Устройство для контроля работы оператора | 1990 |

|

SU1737485A1 |

| Устройство для контроля профессиональных навыков радиотелеграфистов | 1983 |

|

SU1121697A1 |

| Устройство для профессионального отбора операторов | 1989 |

|

SU1777164A1 |

| УСТРОЙСТВО ДЛЯ ТРЕНИРОВКИ ОПЕРАТОРА | 1991 |

|

RU2020603C1 |

| Устройство для оценки профессиональной пригодности операторов | 1990 |

|

SU1709374A1 |

//

Авторы

Даты

1983-02-15—Публикация

1981-08-06—Подача