(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ коорданАТ

АНТЕННОЙ РЕШЕТКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования чисел в дополнителььном коде с плавающей запятой | 1991 |

|

SU1833864A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Трехфазная полюсопереключаемая обмотка с соотношением чисел полюсов 2Р @ : 2Р @ = 16 : 4 | 1989 |

|

SU1658300A1 |

| Трехфазная полюсопереключаемая обмотка | 1989 |

|

SU1653081A1 |

| Трехфазная полюсопереключаемая обмотка двухскоростного двигателя | 1990 |

|

SU1721733A1 |

| Трехфазная полюсопереключаемая обмотка двухскоростного двигателя | 1989 |

|

SU1686632A1 |

| Трехфазная четырехскоростная обмотка с отношением чисел пар полюсов 1 : 2 : 3 : 4 | 1988 |

|

SU1658298A1 |

| Трехфазная полюсопереключаемая обмотка электрической машины | 1990 |

|

SU1714761A1 |

| Трехфазная полюсопереключаемая обмотка | 1989 |

|

SU1663711A1 |

| Трехфазная полюсопереключаемая обмотка | 1989 |

|

SU1674319A1 |

1

Изобретение от.носится к вычислительной технике, в частности к специализированным вычислительным машинам, и может быть использовано для вычисления управляющих кодов (значений фаз) по координате, вдоль которой излучатели располагаются на одинаковом расстоянии по . прямой линии, в линейных, плоских, ш лкндрических антенных решетках.

Известно устройство, содержащее ре- JQ гистр, и сумматоры, в котором управляющие коды по координате вычисляются умножением величины набега фазы на расстоянии между излучателями на ряд чисел l,2,..JVl, где М + 1 - число строк в ,j решетке. Причем в уем вз числа К на выходе регистра .сдвигом на разряд, два, три и т.д. осуществляется умножение на 2,4,8,16 и т.д., после чего в блоке сумматоров умножение на 3,5,6 и т.д. 20 сводится к сложению 2К + К, 4К + 2К, а также умножение на 7,11 и т.д., сводится к сложению уже полученных чисел + К; 11К 8К + 2К + К и т.д. ClJ

Недостатком такого устройства являет ся то, что управляющие кодь по коордв нате получаются суммированием чисел только одного знака, причем операция суммирования шлпрлняется с попнораз- рядными числами, вследствие чего устройство имеет кюкое быстродействие. Кроме того, введение в него операции округления управляющих кодов по координате для повышения его точности ведет к большим аппаратурным затратам.

Наиболее близким по технической сущности к предлагаемому устройству явля- ется устройство, содержащее регистр, вход которого является входом устройства, блок сумматоров, выходы...которого являются выходами устройства, два блока умножения, элемент НЕ, asa логических коммутатора, каждый вз которых содержит две группы элементов И по i элементов И в каждой rpymte и i - 1 элементов ИЛИ, причем выхрды регистра через пер вый в второй блоки умножения соединены с першами входами элементов И первой

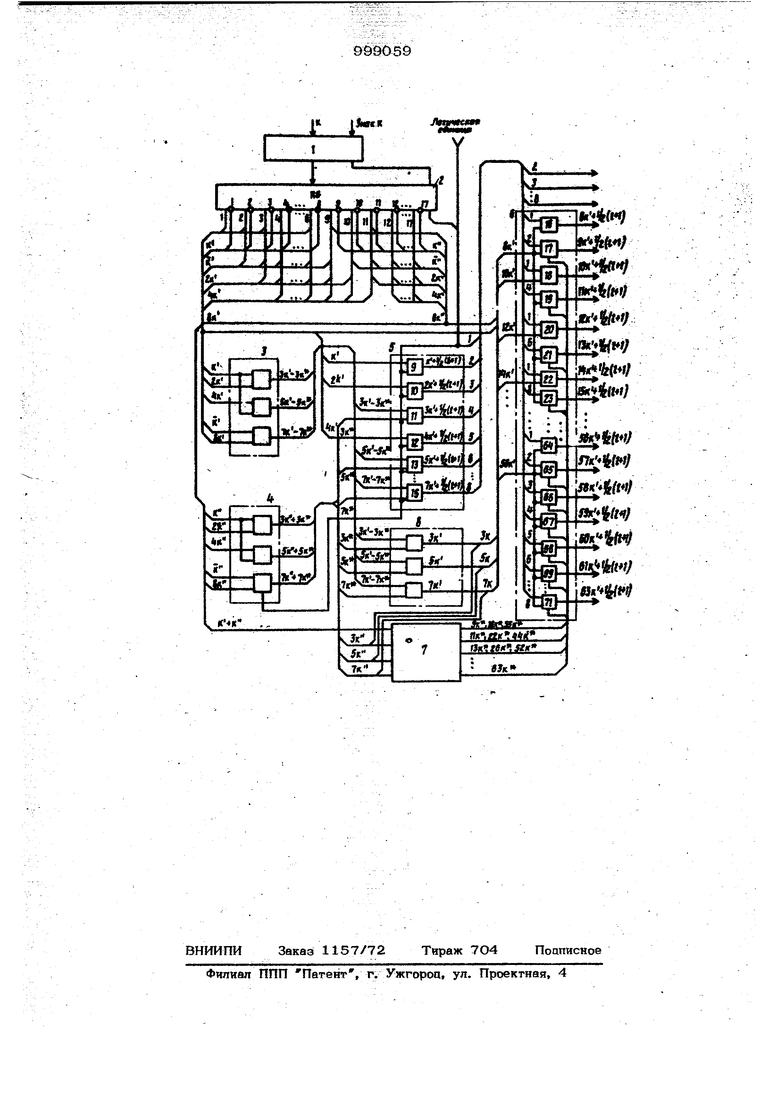

и второй групп каждого логического коммутатора, вторые входы эпементов И первой группы каждого логического коммутатора объединены и соединены со знаковым выходом регистра и входом элемента НЕ, выход которого соединен со вторыми входами элементов И второй груЕН пы каждого логического коммутатора, выходы i - 1-го элемента И второй группы каждого логического коммутатора соед№вены с первыми входами соответствующих элементов ИЛИ того же логического коммутатора, выходы -1-1, 1-2,...2,1 элементов И первой группы каждого логи|Ческого коммутатора соединены со вторыМИ входами 1,2..., i-2, -i -1 элементов ИЛИ того же логического коммутатора, выходы i -X элементов И первой и второй групп и элементов ИЛИ каждого логического коммутатора соединены с соответствующими входами блока сумматоров. В этом устройстве рыходы регистра, на которых вырабатываются числа К, 2К, 4К,8К, 16К, 32К только одного знака соединены со входами первого и второго множительных блоков соответственно 2. Однако известное устройство обладает относительно низким быстродействием из-за потерь времени на распространение переноса при суммировании чисел от млад шего разряда к старшему. Введение в нем операции округления для повышения точности требует больших аппаратурных затрат. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее коммутатор, регистр/блоки вычисления кратного старших и младших разрядов и суммирующие блоки, причем первый вход коммутатора подключен к входу величины набега . фазы устройства, а второй вход - к входу знака устройства, выходы коммутатора подключены соответственно к информационным и знаковому входам регист ра, выходы старших разрядов которого , соединены с входами блока вычисления кратного старших разрядов, а выходы младших разрядов подключены к инфо1 мационным входам блока вычисления крат ного младших разрядов, входы первой группы первого суммирующего блока подключены к выходам старших разрядой р&гистра, а входы второй группы - к выходам блока вычисления кратного старших разрядов, выходы старших разрядов блока вычисления кратного младших разрядов подключены к входам первой группы ВТЕ рого суммирующего блока, выходы первого и второго cy fмиpyющиx блоков подключены к соответствующим входам третьего суммирующего блока, выходы которого являются выходами устройства, введен четвертый суммирующий блок, причем к второй .группе входов второго суммирующего блока подключены выходы блока вычисления кратного старших разрядов, выходы старших разрядов блока вычисления кратного младших разрядов подклкхчены к входам третьей группы первого суммирующего блока, выходы младших разрядов регистра соединены с входами етвертого суммирующего блока, выходы младших разрядов блока вычисления кратного младших разрядов подключены к входам четвертого суммирующего блока, соответственно, выходы которого подключены к соответствующим входам третьего суммирующего блока, вход логической единицы устройства подключен к соответствующему входу первого суммирующего блока и блока вычисления кратного младших разрядов. На чертеже представлена функциональная схема устройства для М 63. Устройство содержит логический коммутатор 1, регистр 2, блоки 3 и 4 вы-v числения кратного старших и младших разрядов соответственно, первый, четвертый, третий и второй суммирующие блоки 5-8 соответственно, сумматоры 9-71. Выходы логического коммутатора 1 подключены к входам регистра 2. Прямые и инверсные выходы регистра 2, соот- в§тствующие старшим разрядам, частичных произведений числа К, соединены со входами блока 3 вычисления кратного старших разрядов, первой группой входов первого суммируклцего блока 5 и входами части сумматоров третьего суммирующ&го блока 6, а прямые и инверсные выходы регистра 2, соответствующие младшим разрядам частичных произведений числа К, соединены со входами блока вычисления кратного младших разрядов и второй группой входов четвертого суммирующего блока 7. Выходы блока вычисления кратного старших разрядов соединены со второй группой входов первого суммирутощего блока 5 и второй группой входов второго суммирующего блока 8. Часть (ВЫХОДОВ, соответствующая старшим разрядам чисел блока вычисления кратного младших разрядов, соединена с. третьей группой входов первого суммирующего блока 5 и первой группой входов второго суммирующего блока 8. Другая часть выходов, соответствующая младшим разрядам блока вычисления кратного младшигс разрядов, соединена с первой группой входов четвертого суммирующего блока 7 Выходы четвертого суммирующего блока 7 соединены со входами переноса сумматоров третьего суммирующего блока 6, выходы сумматоров первого 5 и второго 8 суммирующих блоков соед№некы с соответствующими входами третьгего сумк ирующего блока 6. Вход лог ческой единицы устройства подключен к соответствующему входу первого суммирующего блока 5 и блока вычисления кратного младших разрядов. Устройство работает следующим обраПрямое или инверсное значение набега фазы на расстоянии между излучателями К (в зависимости от знака К) поступает 20 на вход регистра 2. Подключение прямого или инверсного значения К обеспечиваег.ся коммутатором 1. Из регистра 2 группы старших разрядов значений частичных произведений К, 2К, 4К, 8К и инверти- 15 рованного значение К, обозначаемые К , 2К, 4К, 8К и к , поступают на блока 3 вычисления кратного старших ;разрядов, на выходах которого вырабатываются старшие разряды значений ЗК, ЗО ,5К , 7К без учета переносов, возникак ашх в результате суммирования младших .разрядов. Эти числа обозначаются ЗК ЗК, 5К - 5К, 7К - 7К, переносы обозначаются соответственно ЗК , 5К , 7К. Из регистра 2 группы младших разрядов значений К, 2JK, 4К, 8К и инвертированного значения К, обозначаемые К, 2К, 4К, 8К, к, поступают на входы блока вычисления кратного младших раз- рядов, на выходах которого вырабатываются значения ЗК -ьЗК, 5К, , где ЗК, 5К, 7К - переносы в группу старших разрядов, возникающие при суммировании групп младших разрядов. В блоках вычисления кратных значе- .

ние 7К получается не суммированием К + 2К + 4К, которое может быть выполнено в два этапа, а вычитанием 8К-К, которое выполняется в один этап. Операция вычитания выполняется суммированием 8К + К иединицы в младшем разряде

Значения (К -ЗК), (5К -5К), (7К -7К) поступают с блока 3 на вторые группы входов первого и второго суммирующих блоков 5 и 8, где суммируются со значениями ЗК, 5К, 7К поступающими с блока 4 на третью группу входов первого суммирующего блока 99

няются с числами, имеющими в 2 раза меньшую разрядность.

Формула изобретения

Устройство для вычисления координат антенной решетки, содержащее коммутатор, регистр, блоки вычисления краткогостарших и младших разрядов и суммиру ющие бло.ки, причем первый вход комму татора подключен к входу величины набега фазы устройства, а второй вход 9«5 и первую группу входов второго суммирующего блока 8. На первый суммирующий блок 5 поступают также значения к, 2К, 4К с регистра 2 (на первую группу входов) и сигнал 1 для округ - ления чисел. В результате ва выходах первого суммирующего блока 5 формиру-к ются значения К, 2К, ЗК,...,7К с округлении, на выходах второго суммн рующего блока 8 - значеаия ЗК, 5К, 7К. Числа ЗК, 5К, 7К с выходов второго суммирующего блока совместно с числами ЗК, 5К, 7К с выходов блока вь1 числения кратного младгодах раз рядов 4 образуют числа ЗК, 5К, 7К. Эти числа, числа 2К, 4К, вК с регист- , ра 2, а также формируемые сдвигом из перечисленных чисел ЮК, 12К, 14К, 16К, 2ОК, 24К, 28К, 32К, 4ОК, 48К, 56К поступают на входы трет его суммирующего блока 6. В блока 6 суммированием указанных чисел с чвспами, поступающими с выходов первого суммирующего блока 5, формируются уп равляющие коды по координате. Младшие разряды значений К , ЗК , 5К, 7К с выходов регистра 2 и блока 4 вычисления кратного младших разрядов поступают на входы четвертого сумм рующего блока 7, формирующего значения переносов в старшие разряды .9К, ПК , ..., бЗК. Величины переносов поступают на входы переноса сумматоров 17, 19, 21,...71. Старшие разряды значений 9К, 11К,...,63К, сдвинутые влево на 1,2,.. разрядов, поступают на входы переноса сумматоров 26, ЗО, 34,.., 7О, на выходах которых вырабатываются значения 18К, 22К, 26K...,62K Taким образом, учитываются результаты выпопнения операций с младшими разрядами чисел.. Предлагаемое устройство, при отно сительно небольших аппаратурных затра- тах, обеспечивает высокое быстродейст вие благодаря тому, что операции выполк входу знака устройства, выходы коммутатора подключены соответственно к информационным и знаковому входам региоtpa, выходы старших разрядов которого соединены с входами блока вычисления ; кратного старших разрядов, а выходы младших разрядов подключены к информационным входам блока вычисления кратного младших разрядов, входы первой группы первого суммирующего блока дод-

ключены к выходам старших разрядов регистра, а входы второй группы - к выходам блока вычиспевия кратного разрядов, выходы старших разрядов блока вычисления кратного младших разрядов подключены к входам первой грутьпы второго сум лирующего блока, выходы первого и второго суммирующих блоков подключены к соответствующим входам третьего суммирующего блока, выходы которого являются выходами устройства, отличающееся тем, что, с иелью повышения быстродействия, в него введен четвертый суммирующий блок, причем к второй группе входов второго суммирующего блока подключены выходы

соответственно, выходы которого подклк чены к соответствующим входам третьего суммирующего блока, вход логической ед№ницы устройства подключен к соответствующему входу первого суммирующего блока и блока вычисления кратного младших разрядов.

Источники информации, . принятые во внимание при экспертизе

1,Самойленко В. И. Системы управления фазированными антенными решетками. Известия ВУЗов Радиоэлектроника.

Т. 22, Mi 2, 1979, с. 3-17,

Г

Авторы

Даты

1983-02-23—Публикация

1980-10-24—Подача