со

CD СО

N:)

со

Изобретение относится к вычислительной технике и может быть применено для быстрого выполнения операций умножения и деления чисел (осо- бенно эффективно его использование в качестве элементной базы больших и сверхбольших интегральных схем).

Цель изобретения - расширение функциональных возможностей устрой- ства за счет вьтолнения операции деления..

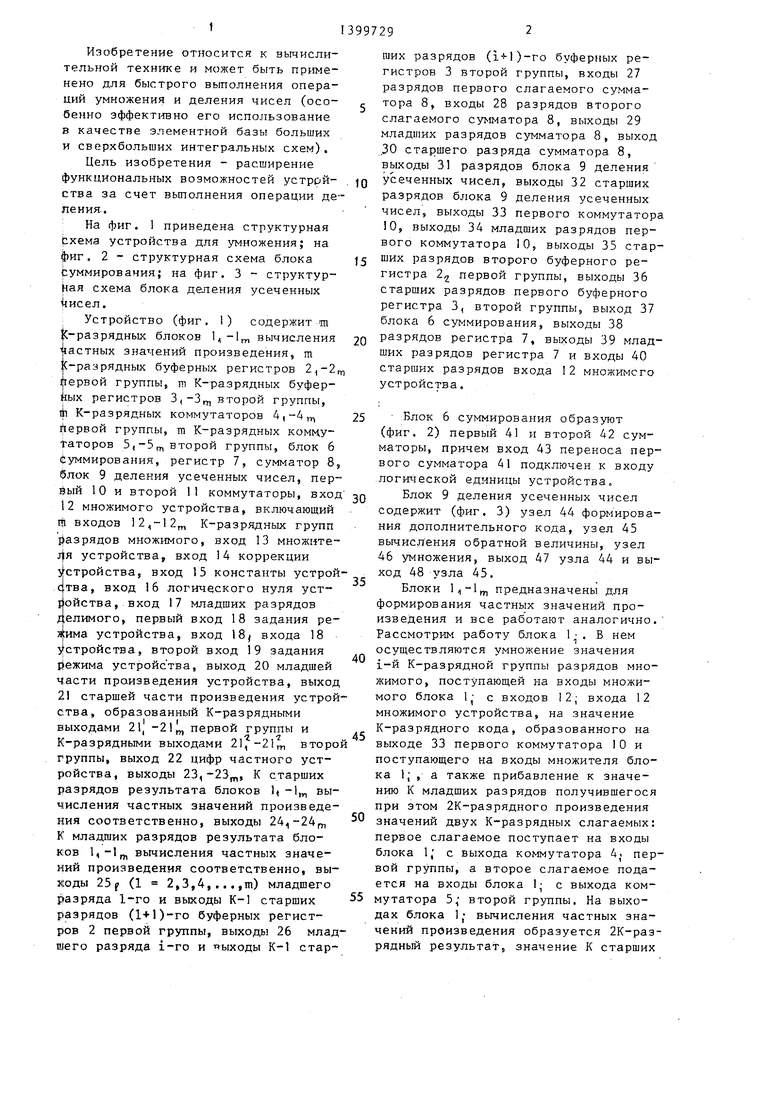

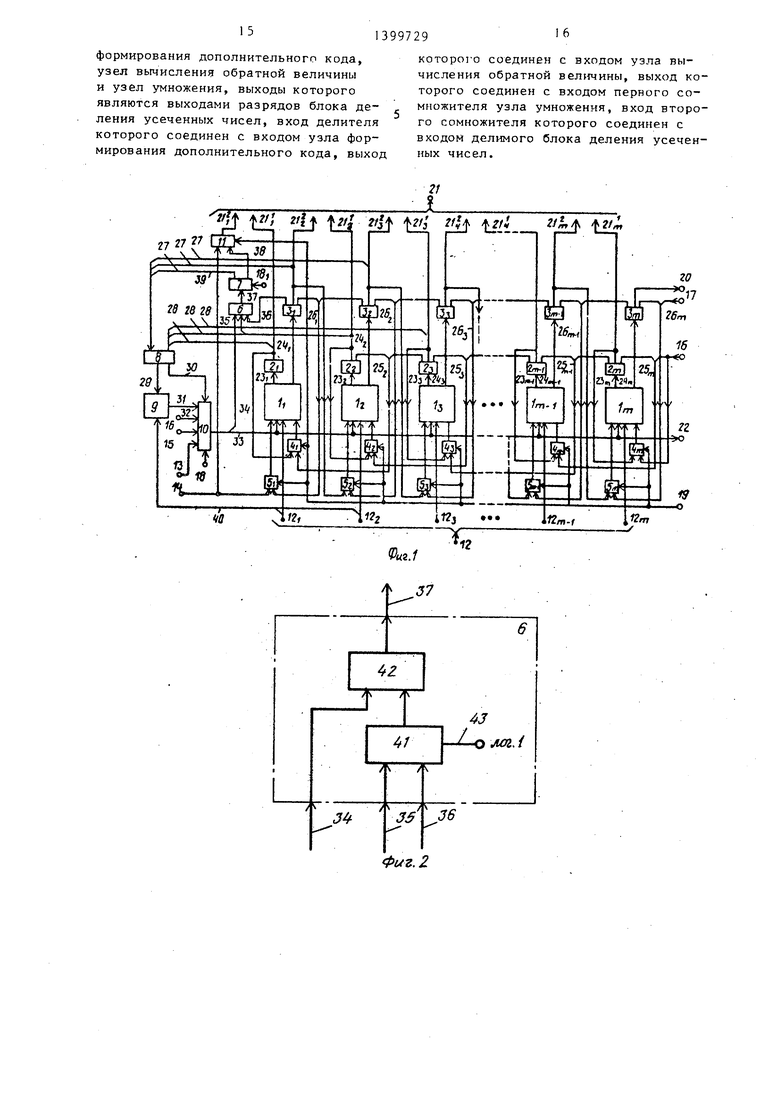

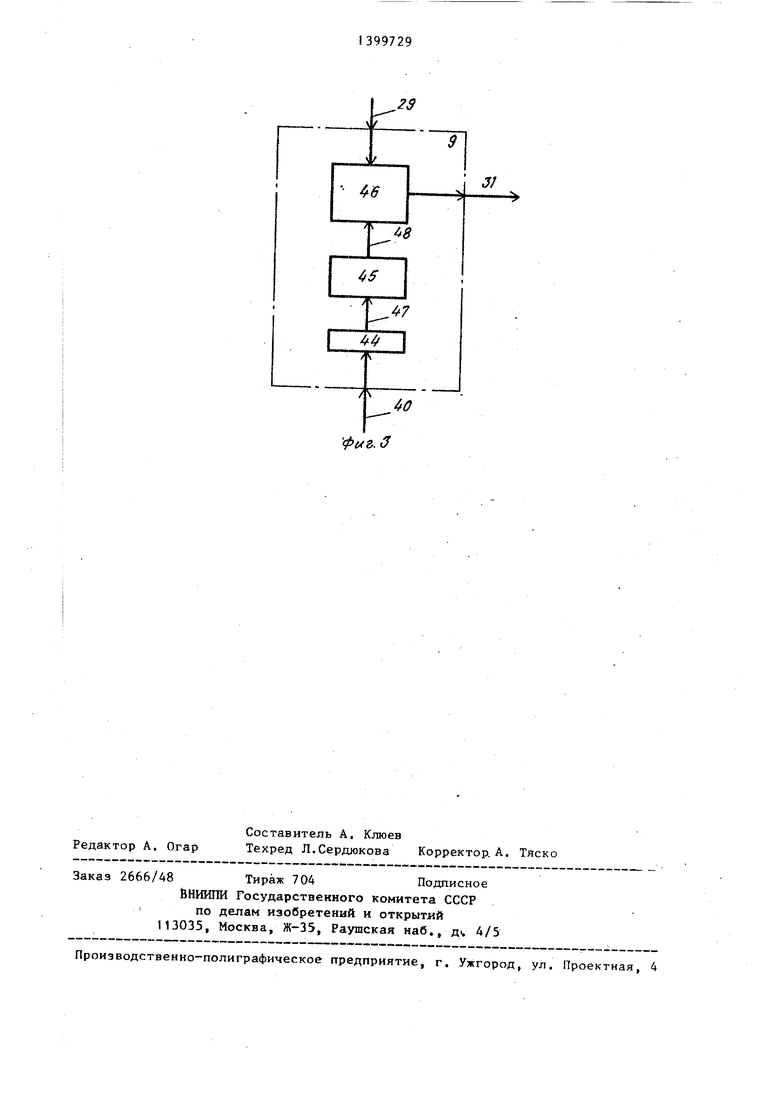

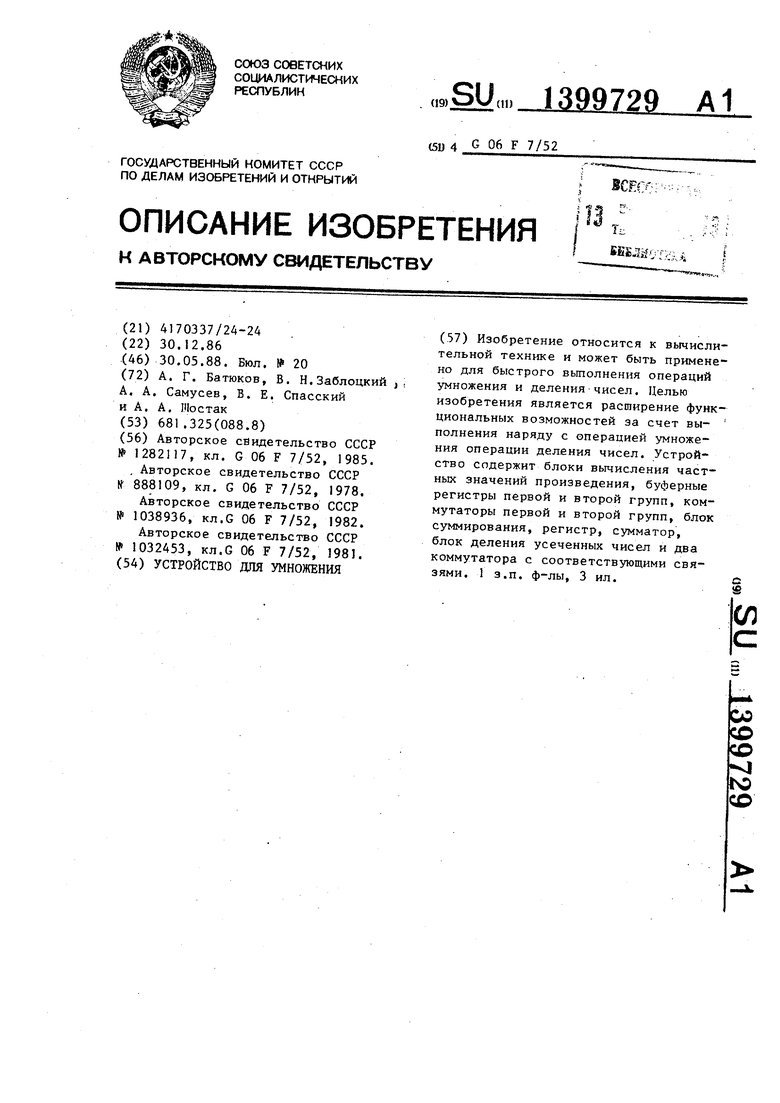

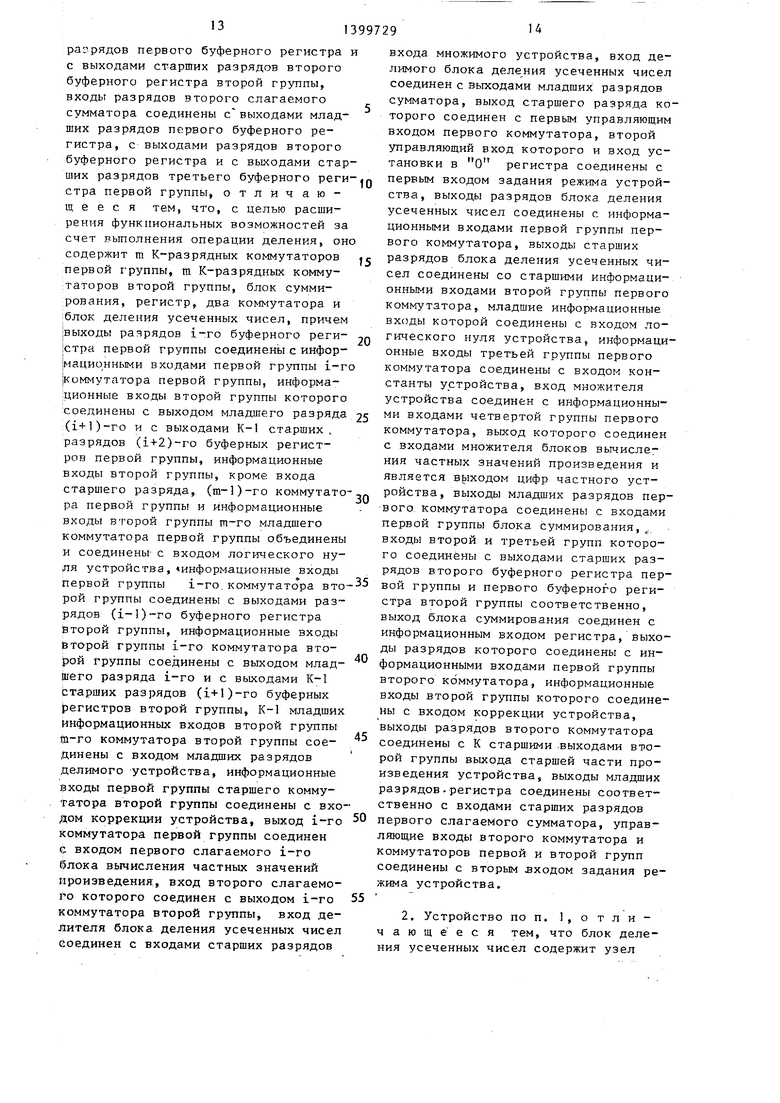

На фиг. 1 приведена структурная Ьхема устройства для умножения; на фиг. 2 - структурная схема блока |:уммирования; на фиг. 3 структур- Йая схема блока деления усеченных исел.

: Устройство (фиг. 1) содержит тп {(-разрядных блоков вычисления Частных значений произведения, m |(-разрядных буферных регистров 2,-2г 1|1ервой группы, m К-разрядных буфер- йых регистров 3,-3 второй группы, ih К-разрядных коммутаторов 4(-4гт,

фервой группы, га К-разрядных комну- taTopoB 5,-5m второй группы, блок 6 Суммирования, регистр 7, сумматор 8, 0ЛОК 9 деления усеченных чисел, пер- йый 10 и второй 11 коммутаторы, вход 12 множимого устройства, включающий входов 12,-12г„ К-разрядных групп разрядов множимого, вход 13 множите- т|я устройства, вход 14 коррекции 5 стройства, вход 15 константы устрой .с.тва, вход 16 логического нуля устройства, вход 17 младших разрядов Делимого, первый вход 18 задания ре 4има устройства, вход IBj входа 18 у|стройства, второй вход 19 задания Йежима устройства, выход 20 младшей части праизведения устройства, выход 21 старшей части произведения устройства, образованный К-разрядными выходами 21| -21 первой группы и

К-разрядными выходами 21, -21 второ группы, выход 22 цифр частного устройства, выходы 23,-23fn, К старших разрядов результата блоков l -1 вычисления частных значений произведения соответственно, выходы 24,-24гл К младших разрядов результата блоков вычисления частных значений произведения соответственно, выходы 25f (1 2,3,4,...,m) младшего разряда 1-го и выходы К-1 старших разрядов (1+1)-го буферных регистров 2 первой группы, выходы 26 младшего разряда i-ro и выходы К-1 стар

Q

5

0 5

Q .

5

ших разрядов ()-ro буферных ре- гистрюв 3 второй группы, входы 27 разрядов первого слагаемого сумматора 8, входы 28 разрядов второго слагаемого сумматора 8, выходы 29 младших разрядов сумматора 8, выход ,30 старшего разряда сумматора 8, выходы 31 разрядов блока 9 деления усеченных чисел, выходы 32 старших разрядов блока 9 деления усеченных чисел, выходы 33 первого коммутатора 0, выходы 34 младших разрядов первого коммутатора 10, выходы 35 старших разрядов второго буферного регистра 2 первой группы, выходы 36 старших разрядов первого буферного регистра 3, второй группы, выход 37 блока 6 суммирования, выходы 38 разрядов регистра 7, выходы 39 младших разрядов регистра 7 и входы 40 старших разрядов входа 12 множимого устройства.

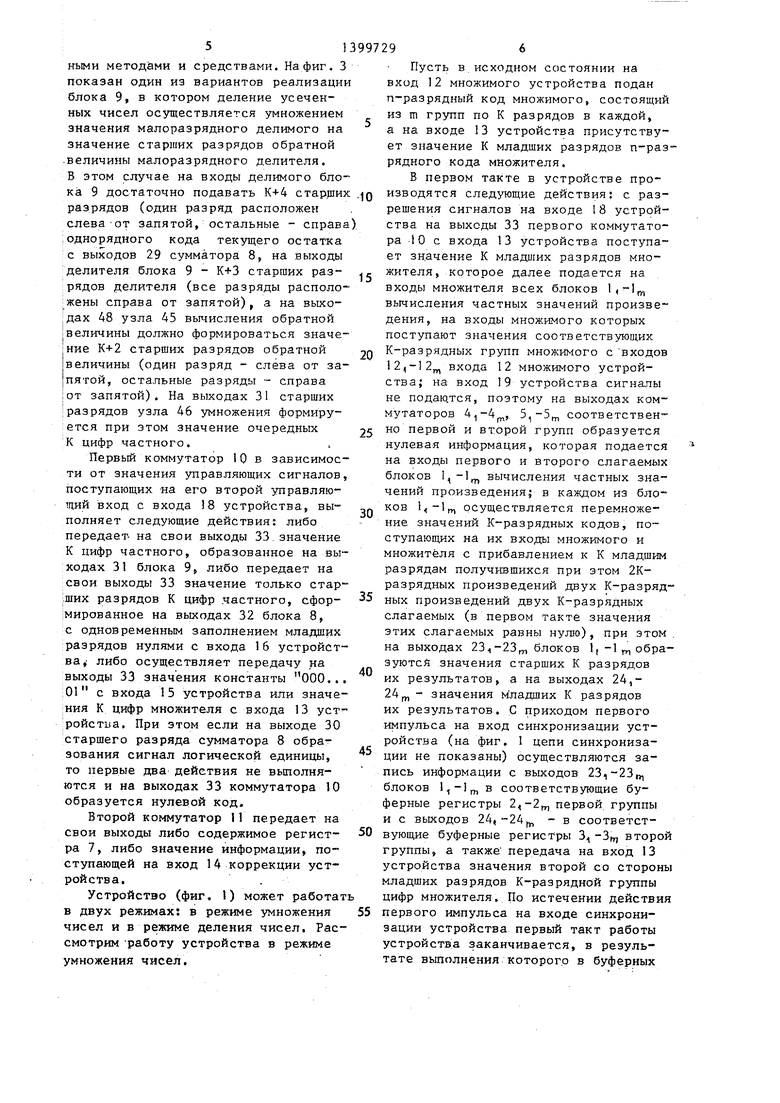

Влок 6 суммирования образуют (фиг. 2) первый 41 и второй 42 сумматоры, причем вход 43 переноса первого сумматора 41 подключен к входу логи геской единицы устройства.

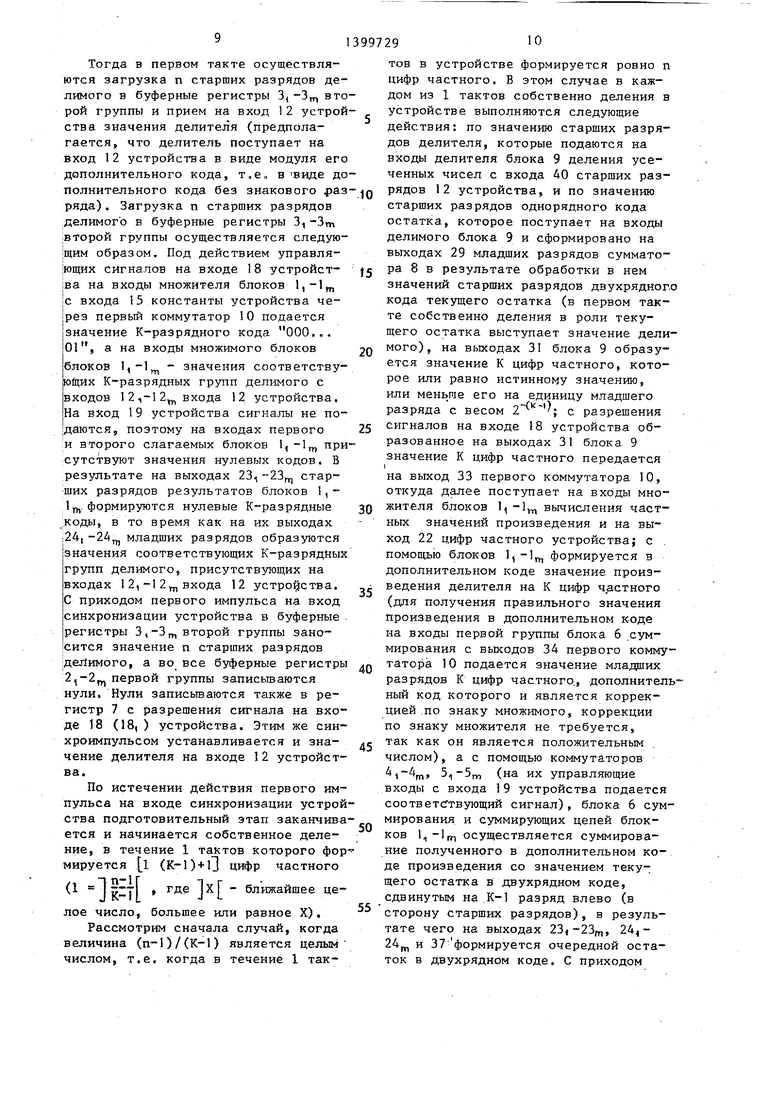

Блок 9 деления усеченных чисел содержит (фиг. 3) узел 44 формирования дополнительного кода, узел 45 вычисл ения обратной величины, узел 46 умножения, выход 47 узла 44 и выход 48 узла 45.

Блоки 1;,- предназначены для формирования частных значений произведения и все работают аналогично. Рассмотрим работу блока Ь . Б нем осуществляются умножение значения i-й К-разрядной группы разрядов множимого, поступающей на входы множимого блока 1| с входов 12; входа 12 множимого устройства, на значение К-разрядного кода, образованного на выходе 33 первого коммутатора 10 и поступающего на входы множителя блока 1; , а также прибавление к значению К младших разрядов получившегося при зтом 2К-разрядного произведения значений двух К-разрядных слагаемых: первое слагаемое поступает на входы блока 1; с выхода коммутатора 4 первой группы, а второе слагаемое подается на входы блока 1; с выхода коммутатора 5, второй группы. На выходах блока вычисления частных значений произведения образуется 2К-раз- рядный результат, значение К старших

разрядов которого подается на информационные входы буферных регистров 2 первой группы с выходов 23 блока 1-, а значение К младших разрядов этого результата поступает на информационные входы буферного регистра 3; второй группы С ВЫХОДОВ 24, блока 1; . Каждый из блоков , -1, вычисления частных значений произведения может быть реализован так же, как в известном устройстве, или, например, на базе серийно выпускаемого БИС-умножителя KI800BPI.

Коммутаторы А, -4 первой группы предназначены для передачи информации с выхода буферных регистров 2 первой группь на входы первого слагаемого блоков I;,-1 ,, вычисления частных значений произведения либо со сдвигом на К разрядов вправо (в сторону младших разрядов) при выполнении в устройстве операции умножения, либо со сдвигом влево на К-1 разряд при выполнении в устройстве операции деления. Они работают под воздействием двух сигналов, поступающих на их управляющие входы с входа 19 устройства. Если на вход 19 устройства не подается ни один из сигналов, то на выходах коммутаторов 4,-4 образуется нулевой код. Аналогичны по построению и в работе коммутаторы 5(-5 второй группы. Однако они осуществляют передачу информации с выходов буферных регистров 3,-3 второй группы на входы второго слагаемого блоков 1,-1 вычисления частных значений произведения или со сдвигом вправо на К разрядов при реализации в устройстве операции умножения, или со сдвигом влево на К-1 разряд при вьшолнении в устройстве операции деления.

Совокупность i-ro блока 1 вычисления частных значений произведения, i-ro буферного регистра 2 первой группы, i-ro буферного регистра 3 второй группы, i-ro коммутатора 4 первой группы и i-ro коммутатора 5 второй группы может быть вьтолнена в виде единого модуля,

В блоке 6 осуществляется суммирование хранимых в буферных регистрах 2 и 3, значений старших разрядов двухрядного кода текущего остатка, которые при сдвиге текущего остатка на К-1 разряд в сторону младших разрядов не могут быть обработаны с помощью суммирующих цепей блока 1, . В блок 6 через входы его первой группы поступает и значение младших разрядов кода, образованного на выходах 34 первого коммутатора 10. Таким образом вводится коррекция в значение произведения при умножении в устройстве модуля дополнительного

кода отрицательного множимого на модуль прямого кода положительного мно- жителя. Минимальная разрядность суммирующих цепей блока 6 равна двум, максимальная - К-1. Предполагается,

что в- блоке 6, показанном на фиг. 2 на выходы 34 первого коммутатора 10 подается инверсное значение младших разрядов кода, образованного на его выходах 33. Д.ая преобразования этого обратного кода в дополнительный на вход переноса первого сумматора 41 блока 6 подается потенциал логической единицы.

Сумматор 8 осуществляет преобразование к однорядному коду, например, K-f5 старших разрядов (два разряда расположены слева от запятой, остальные разряды - справа от запятой) двухрядного кода текущего остатка,

хранимого в регистре бив буферных

регистрах 2,-2„, ,. На выходах 23 разрядов cyNfMaTopa 8 образуется значение К+4 старших разрядов (один разряд слева от запятой, остальные - справа от запятой) однорядного кода текущего остатка, а на выходе 30 формируется значение старшего из двух расположенных слева от запятой разрядов однорядного кода текущего остатка.

в блоке 9 осуществляется деление значения старших разрядов однорядного кода текущего остатка, сформированного на вьЕходах 29 младших разрядов сумматора 8 по значению старших разрядов двухрядного кода текущего остатка, на значение старших разрядов делителя, поступающее на входы делителя блока 9 с входом 40 старших разрядов входа 12 множимого

устройства. В результате на выходах 31 блока 9 формируется значение К : очередных цифр частного, которое (за исключением случая, когда, на выходе 30 старшего разряда сумматора 8

образован сигнал логической единицы) либо равно истинному значению К цифр частного, либо меньше его на единицу младшего разряда с весом 2 . Блок 9 йожет быть реализован различ

51

ными методами и средствами. На фиг, 3 показан один из вариантов реализации блока 9, в котором деление усеченных чисел осуществляется умножением значения малоразрядного делимого на значение старших разрядов обратной .величины малоразрядного делителя. В этом случае на входы делимого блока 9 достаточно подавать K-i-4 старших разрядов (один разряд расположен слева-от запятой, остальные - справа :однорядного кода текущего остатка с выходов 2.9 сумматора 8, на выходы делителя блока 9 - К+3 старших раз- рядов делителя (все разряды располо- ;жены справа от запятой), а на выхо- ;дах 48 узла 45 вычисления обратной :величины должно формироваться значе- ние К+2 старших разрядов обратной Iвеличины (один разряд - слева от за- |пятой, остальные разряды - справа :от запятой). На выходах 31 старших iразрядов узла 46 умножения формиру ;ется при этом значение очередных К цифр частногоi

Первый коммутатор 10 в зависимости от значения управляющих сигналов, поступающих на его второй управляю щий вход с входа 18 устройства, БЫ полняет следующие действия; либо передает- на свои выходы 33 значение К пифр частного, образованное на выходах 31 блока 9 либо передает на свои выходы 33 значение только стар ших разрядов К цифр частного, сфор- :мированное на выходах 32 блока 8, с одновременным заполнением младших разрядов нулями с входа 16 устройст™ ва, либо осуществляет передачу на выходы 33 значения константы 000... 01 с входа 15 устройства или значения К цифр множителя с входа 13 уст :ройстиа. При этом если на выходе 30 старшего разряда сумматора 8 обра-г зования сигнал логической единицы, то первые два действия не выполняются и на выходах 33 коммутатора 10 образуется нулевой код.

Второй коммутатор 11 передает на свои выходы либо содержимое регист- ра 7, либо значение информации, поступающей на вход 14 коррекции устройства..

Устройство (фиг, 1) может работат в двух режимах в режиме умножения чисел и в режиме деления чисел. Рассмотрим работу устройства в режиме умножения чисел.

с Q 5

5

0

5

0

296

Пусть Б исходном состоянии на вход 12 множимого устройства подан п-разрядный код множимого, состоящий из m групп по К разрядов в каждой, а на входе 13 устройства присутствует значение К младших разрядов п-раз- рядного кода множителя.

В первом такте в устройстве производятся следующие действия: с разрешения сигналов на входе I8 устройства на выходы 33 первого коммутатора -10 с входа 13 устройства поступает значение К младших разрядов множителя, которое далее подается на входы множителя всех блоков Ь- вычисления частных значений произведения, на входы множимого которых поступают значения соответствуюпщх К-разрядных групп множимого с входов 12,-12 входа 12 множимого устройства; на вход 19 устройства сигналы не подаю.тся, поэтому на выходах коммутаторов 4,-4|, 5,-БГП соответственно первой и второй групп образуется нулевая информация, которая подается на входы первого и второго слагаемых блоков 1,-1,т1 вычисления частных значений произведения; в каждом из бло ков осуществляется перемножение значений К-разрядных кодов, поступающих на их входы множимого и множителя с прибавлением к К младшим разрядам получившихся при этом 2К- разрядных произведений двух К-разрядных произведений двух К-разрядных слагаемых (в первом такте значения этих слагаемых равны нулю), при этом . на выходах блоков 1; -1 г,, обра- зуютсй значения старших К разрядов их результатов, а на выходах 24,- 24 - значения младших К разрядов их результатов. С приходом первого импульса на вход синхронизации устройства (на фиг. I цепи синхронизации не показаны) осуществляются запись информации с выходов 23i-23ni блоков 1,- в соответствующие буферные регистры первой группы и с выходов 24, 24fj, - в соответствующие буферные регистры 3 -3,, второй группы, а также передача на вход 13 устройства значения второй со стороны младших разрядов К-разрядной гр уппы цифр множителя. По истечении действия первого импульса на входе синхронизации устройства первый такт работы устройства заканчивается, в результате вьтплнения которого в буферных

/

регистрах 2,-2, 3,-3 образуется значение первого частичного произведения п-разрядного множимого на К младших разрядов множителя в дву рядном коде.

Во втором такте (а также и во всех других, включая т-й такт) в устройстве выполняются в основном те же действия, что и в первом так те. Отличие состоит только в том, что на вход 19 устройства подается управляющий сигнал, разрешающий передачу на входы первого и второго

8

празрядных сомножителей, п младших разрядов которого по К разрядов в каждом также уже вьгоедены через выход 20 устройства. Пр1-шедение к однорядному коду двухрядного кода п старших разрядов произведения, образованного на выходе 2 устройства, может быть осуществлено или внешними системными средствами, или посредством использования специального празрядного быстродействующего сумматора, входы первого и второго елагаемьцс которого подключены к равно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого вьтолнения операций умножения и деления чисел. Целью изобретения является расширение функциональных возможностей за счет вы- полнения наряду с операцией умножения операции деления чисел. Устройство Содержит блоки вычисления частных значений произведения, буферные регистры первой и второй групп, коммутаторы первой и второй групп, блок суммирования, регистр, сумматор, блок деления усеченных чисел и два коммутатора с соответствующими связями, 1 з.п. ф-лы, 3 ил. о

слагаемых блоков 1,-. через информа-|5 весовым выходам соответственно 21 -

35

г

. ционные входы коммутаторов i

5,-5 т, содержимого буферных регистров ) , сформированного в устройстве после выполнения в нем первого такта. Так, в i-м блоке I вы- 20 числения частных значений произведения (i l,2,3,...,m) осуществляются умножение значения i-й К-разрядной группы множимого, поступающего на его входы множимого с входа 12|, на 25 значение второй со стороны младших разрядов К-разрядной группы множителя, сформированное на выходах 33 первого коммутатора 10 и поступающее на входы множителя i-ro блока 1, а JQ также прибавление к значению К млад- , ших разрядов получившегося при этом 2К-разрядного произведения двух К- разрядных слагаемых: одно слагаемое поступает на входы первого слагаемого i-ro блока 1 через i-й коммутатор 4 первой группы с выходов i-ro буферного регистра 2 первой группы, второе слагаемое подается на входы второго слагаемого i-ro блока 1 через i-й коммутатор 5 второй группы с выходов (i-l)-ro буферного регистра 3 второй группы. Фактически во втором такте работы устройства с

помощью блоков 1,-1,т,И коммутаторов де

5,-5п, осуществляются формирование значения второго частичного произведения п-разрядного множимого К разрядов второй со стороны младших разрядов группы разрядов п-разрядного множителя и прибавление его к значению первого частичного произведения, образованному в первом такте и сдвинутому на К разрядов вправо (в сторону младших разрядов).

После выполнения т-го такта в буферных регистрах 2,-2,„, , запоминаются в двухрядном коде п старших разрядов 2п-разрядного произведения

-t

„, выхода 21 устройства.

40

21

Выполняя в устройстве еще m дополнительных тактов с подачей на вход 13 множителя устройства нулевого кода можно через выход 20 вывести в однорядном коде и п старших разрядов.про изведения.

Если в устройстве осуществляется умножение чисел в дополнительном коде, то вход 14 коррекции устройства может быть использован для ввода в произведение значения обп(ей коррекции как по знаку множимого, так и по знаку множителя. На последнем, (m+i) такте умножения значение старших К разрядов этой коррекции с входа 14 устройства непосредственно передается на выход 211 выхода 21 устройства через второй коммутатор II.

Вход 14 коррекции устройства может быть использован также для выполнения округления знач ния конечного произведения без дополнительных временных затрат (в этом случае на вход 14 устройства в первом такте его работы необходимо подать код 1000...О), а также для выполнения в устройстве более сложной операции, как, например, умножение п-раз- рядных сомножителей с одновременным подсуммированием к п старшим разрядам 2п-разрядного произведения некоторого п-разрядного слагаемого.

Рассмотрим работу устройства в режиме деления чисел.

Пусть делимое имеет Р() разрядов, а делитель и частное - по

п разрядов и пусть в исходном состоя нии на входе 12 устройства уже присутствуют п старших -разрядов дели- мого (младшие Р-п разрядов делимого в ходе собственного деления чисел по К-1 разрядов в каждом такте подаются в устройство через его вход 17)

весовым выходам соответственно 21 -

-t

„, выхода 21 устройства.

21

Выполняя в устройстве еще m дополнительных тактов с подачей на вход 13 множителя устройства нулевого кода можно через выход 20 вывести в однорядном коде и п старших разрядов.произведения.

Если в устройстве осуществляется умножение чисел в дополнительном коде, то вход 14 коррекции устройства может быть использован для ввода в произведение значения обп(ей коррекции как по знаку множимого, так и по знаку множителя. На последнем, (m+i)- такте умножения значение старших К разрядов этой коррекции с входа 14 устройства непосредственно передается на выход 211 выхода 21 устройства через второй коммутатор II.

Вход 14 коррекции устройства может быть использован также для выполнения округления знач ния конечного произведения без дополнительных временных затрат (в этом случае на вход 14 устройства в первом такте его работы необходимо подать код 1000...О), а также для выполнения в устройстве более сложной операции, как, например, умножение п-раз- рядных сомножителей с одновременным подсуммированием к п старшим разрядам 2п-разрядного произведения некоторого п-разрядного слагаемого.

Рассмотрим работу устройства в режиме деления чисел.

Пусть делимое имеет Р() разрядов, а делитель и частное - по

п разрядов и пусть в исходном состоянии на входе 12 устройства уже присутствуют п старших -разрядов дели- мого (младшие Р-п разрядов делимого в ходе собственного деления чисел по К-1 разрядов в каждом такте подаются в устройство через его вход 17).

Тогда в первом такте осуществляются загрузка п старших разрядов делимого в буферные регистры второй группы и прием на вход 12 устрой ства значения делителя (предполагается, что делитель поступает на вход 12 устройства в виде модуля его дополнительного кода, т.е. в виде дополнительного кода без знакового ряда). Загрузка п старших разрядов делимого в буферные регистры 3, -3т ;второй группы осуществляется следую- ;щим образом. Под действием управля- |ющих сигналов на входе 18 устройст- :ва на входы множителя блоков Ц- 1с входа 15 константы устройства че- |рез первый коммутатор 10 подается :значение К-разрядного кода 000.„. 101, а на входы множимого блоков

блоков , значения соответству- рощих К-разрядных групп делимого с входов 12i-12 входа 12 устройства, На вход 19 устройства сигналы не поддаются, поэтому на входах первого и второго слагаемых блоков Ц-1 при :Сутствуют значения нулевых кодов. В результате на выходах 23, --23„, старших разрядов результатов блоков 1, . формируются нулевые К-разрядные коды, в то время как на их выходах ;24| -24 младших разрядов образуются значения соответствующих К-разрядных групп делимого, присутствующих на входах 12,-12 входа 12 устройства. С приходом первого импульса на вход 1синхронизации устройства в буферные регистры 3,-3 второй группы заводится значение п старших разрядов делимого, а во все буферные регистры 2,-2 первой группы записьтаются нули. Нули записьшаются также в регистр 7 с разрешения сигнала на входе 18 (18,) устройства. Этим же синхроимпульсом устанавливается и значение делителя на входе 12 устройства.

По истечении действия первого импульса на входе синхронизации устройства подготовительный зтап заканчивается и начинается собственное деление, в течение 1 тактов которого фор мируется .l ( цифр частного

(1 ° 1;;;т где 1х - ближайшее целое число, большее или равное X).

Рассмотрим сначала случай, когда величина (п-1)/(К-1) является целым числом, т.е. когда в течение 1 так

тов в устройстве формируется ровно п цифр частного. В этом случае в каждом из 1 тактов собственно деления в устройстве выполняются следующие действия: по значению старших разрядов делителя, которые подаются на входа делителя блока 9 деления усеченных чисел с входа 40 старших разрядов 12 устройства, и по значению старших разрядов однорядного кода остатка, которое поступает на входы делимого блока 9 и сформировано на выходах 29 младших разрядов сумматора 8 в результате обработки в нем значений старших разрядов двухрядного кода текущего остатка (в первом такте собственно деления в роли текущего остатка выступает значение делимого), на выходах 31 блока 9 образуется значение К цифр частного, которое или равно истинному значению, или меньше его на единицу младшего разряда с весом с разрешения сигналов на входе 18 устройства образованное на выходах 31 блока 9

значение К цифр частного передается

1

на выход 33 первого коммутатора 10, откуда далее поступает на входы множителя блоков Ц -1у вьиисления частных значений произведения и на выход 22 цифр частного устройства; с . помощью блоков Ц -1 формируется в дополнительном коде значение произведения делителя на К цифр ч,астного (для получения правильного значения гхроизведения в дополнительном коде на входы первой группы блока 6 .суммирования с выходов 34 первого коммутатора 10 подается значение младших разрядов К цифр частного., дополнительный код которого и является коррекцией .по знаку множимого, коррекции по знаку множителя не требуется, так как он является положительным числом), а с помощью коммутаторов 4,-4, (на их управляющие входы с входа 19 устройства подается соответс твующий сигнал) , блока 6 суммирования и суммирующих цепей бпок- ков 1, -Iff, осуществляется суммирование полученного в дополнительном коде произведения со значением текущего остатка в двухрядном коде, сдвинутым на К-1 разряд влево (в сторону старших разрядов), в результате чего на выходах 23(-23,„, 244- 24j и 37 формируется очередной остаток в двухрядном коде. С приходом

импульса на вход синхронизации устройства осуществляется запись очередного остатка в двухрядном коде в регистр 7 и в буферные регистры , 3,-3 первой и второй групп. После окончания действия импульса такт работы устройства заканчивается.

После выполнения 1 тактов на выходе 20 и на выходах 21 -21, 2lf- 21 выхода 21 устройства образуется значение окончательного остатка в двухрядном коде. В режиме деления на выходы 21, через второй коммутатор- 1I передается значение содержимого регистра 7.

Образование в. устройстве конечного значения п-разрядного частного по значениям К цифр частного, получаемым

во всех тактах собственно деления и

подаваемым на выход 22 устройства, может быть выполнено в соответствии с основным алгоритмом с помощью, например, накапливающего сумматора. Для этого могут быть также привлече- ны и некоторые внешние системные средства, позволяющие выполнять операцию суммирования. Старшая из К формируемых в текущем такте цифр частного является корректирующей для частного, полученного на всех предыдущих тактах и сдвинутого на К-1 разряд в сторону старших разрядов.

Сформированное таким образом п- разрядное частное (один разряд расположен слева от запятой, остальные разряды - справа от запятой) или равно истинному значению, или меньше его на единицу младшего разряда с весом . Получение точного значения п-разрядного частного может быть обе:спечено очевидным путем (посредством, например, пробного вьти- тания соответствующим образом сдвинутого делителя) с помощью специальных или системных средств.

Если величина (n-l)/() не является целым числом, а значение остатка необходимо получить дли рядного частного, то в последнем из 1 тактов собственно деления на выход 33 первого коммутатора 10 с выходов 32 блока 9 передается значение такого числа старших разрядов К-разрядно- го частного, которое обеспечивает получение значения п-разрядного частного. Для этого на второй управляющий вход первого коммутатора JO с

входа 18 устройства подаются соответствующие управляющие сигналы.

Так как на формирование К цифр частного и остатка требуется примерно в два раза больше времени, чем на обработку в устройстве К цифр множителя, то для эффективной загрузки устройства целесообразно использовать две серии синхроимпульсов, поступающих на вход синхронизации устройства. Первую из этих серий, например, с периодом Т можно использовать в режиме умножения чисел, а вторую серию, например, с периодом 2Т - в режиме деления чисел.

Формула изобретения

R

, где п - разрядность множи5.

0

5

0

мого; К - целочисленная переменная, принимающая значения в пределах 2бК п/2;ЗхС- ближайшее целое число, .большее или равное X), т, К-раз- рядных буферных регистров первой группы, m К-разрядных буферных регистров второй группы и сумматор, причем вход множимого i-ro блока вычисления частных значений произведения

(i 1,2,3m) соединен с входом

i-й К-разрядной группы входа множимого устройства, выходы К старших разрядов результата i-ro блока вычисления частных значений произведения соединены соответственно с входами разрядов i-ro буферного регистра первой группы, выходы К младших разрядов результата i-ro блока вычисления частных значений произведения соединены соответственно с входами разрядов 1-го буферного регистра второй группы, выходы буферных регистров первой группы образуют первую группу выходов выхода старшей части произведения устройства, выходы буферных регистров второй группы, кроме выхода младшего буферного регистра, являются выходами второй группы вькода старшей части произведения устройства, выход младшего буферного регистра второй группы соединен с выходом младшей части произведения устройства, входы разрядов первого слагаемого сумматора, кроме старших, соединены соответственно с выходам.

par.рядов первого буферного регистра и с выходами старших разрядов второго буферного регистра второй группы, входы разрядов второго слагаемого сумматора соединены с выходами младших разрядов первого буферного регистра, с выходами разрядов второго буферного регистра и с выходами старших разрядов третьего буферного регистра первой группы, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции деления, оно содержит m К-разрядных коммутаторов первой группы, га К разрядных комму- ;таторов второй группы, блок суммирования, регистр, два коммутатора и блок деления усеченных чисел, причем |выходы разрядов i-ro буферного реги- стра первой группы соединены с инфор- |мацицнными входами первой группы i-r ркоммутатора первой группы, информа- :ционные входы второй группы которого соединены с выходом младшего разряда :(i+i)-ro и с выходами К-1 старших, разрядов (1+2)-го буферных регистров первой группы, информационные входы второй группы, кроме входа старшего разряда, (m-l)-ro коммутатора первой группы и информационные входы второй группы т-го младшего коммутатора первой группы объединены и соединены- с входом логического нуля устройства, «информационные входы первой группы i-ro.коммутатора второй группы соединены с выходами разрядов (i-l)-ro буферного регистра йторой группы, информационные входы Второй группы i-ro коммутатора второй группы соединены с выходом млад- ttiero разряда i-ro и с выходами К-1 старших разрядов (i+l)-ro буферных регистров второй группы, К-1 младших информационных входов второй группы fti-ro коммутатора второй группы соединены с входом младших разрядов делимого устройства, информационные шходы первой группы старшего коммутатора второй группы соединены с вхо ;а;ом коррекции устройства, выход i-ro Коммутатора первой группы соединен (iL входом первого слагаемого i-ro (5лока вычисления частных значений произведения, вход второго слагаемо- которого соединен с выходом i-ro коммутатора второй группы, вход делителя блока деления усеченных чисел соединен с входами старших разрядов

5

0

5

0

5

0

5

0

5

входа множимого устройства, вход делимого блока деления усеченных чисел соединен с выходами младших разрядов сумматора, выход старшего разряда которого соединен с первым управляющим входом первого коммутатора, второй управляющий вход которого и вход установки в О регистра соединены с первым входом задания режима устройства, выходы разрядов блока деления усеченных чисел соединены с информационными входами первой группы первого коммутатора, выходы старших разрядов блока деления усеченных чисел соединены со старшими информационными входами второй группы первого коммутатора, младшие информационные входы которой соединены с входом логического нуля устройства, информационные входы третьей группы первого коммутатора соединены с входом константы устройства, вход множителя устройства соединен с информационными входами четвертой группы первого коммутатора, выход которого соединен с входами множителя блоков вычисления частных значений произведения и является выходом цифр частного устройства, выходы младших разрядов пер- -вого. коммутатора соединены с входами первой группы блока суммирования, входы второй и третьей групп которого соединены с выходами старших разрядов второго буферного регистра первой группы и первого буферного регистра второй группы соответственно, выход блока суммирования соединен с информационным входом регистра, выходы разрядов которого соединены с информационными входами первой группы второго коммутатора, информационные входы второй группы которого соединены с входом коррекции устройства, выходы разрядов второго коммутатора соединены с К старшими .выходами второй группы выхода старшей части произведения устройства, выходы младших разрядов.регистра соединены соответственно с входами старших разрядов первого слагаемого сумматора, управляющие входы второго коммутатора и коммутаторов первой и второй групп соединены с вторым входом задания режима устройства.

формирования дополнительного кода, узел вычисления обратной величины и узел умножения, выходы которого являются выходами разрядов блока деления усеченных чисел, вход делителя которого соединен с входом узла формирования дополнительного кода, выход

I//; г/|| /Jt { t

KOTOpoi o соединен с входом узла вычисления обратной величины, выход которого соединен с входом первого сомножителя узла умножения, вход второго сомножителя которого соединен с входом делимого блока деления усеченных чисел.

Фм.1

37

Фиг. 2

.б

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , Авторское свидетельство СССР № 888109, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1038936A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-30—Подача