Изобретение относится к вычислительной технике и может быть использовано в автоматических и вычислительных устройствах для преобразования хранимого кода в обратный или дополнительный с возможностью обратного преобразования, а также для выполнения прямого и обратного счета либо в двоичном коде, либо в коде Грея.

Целью изобретения является расширение функциональных возможностей за счет обеспечения формирования прямой и обратной последовательности кода Грея.

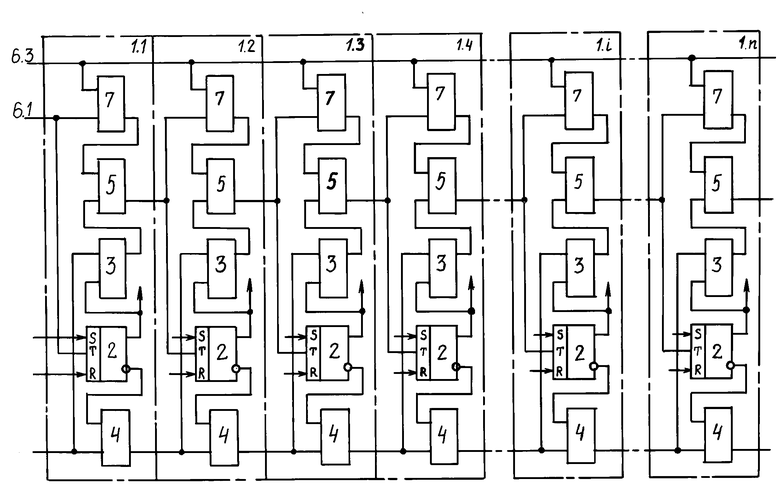

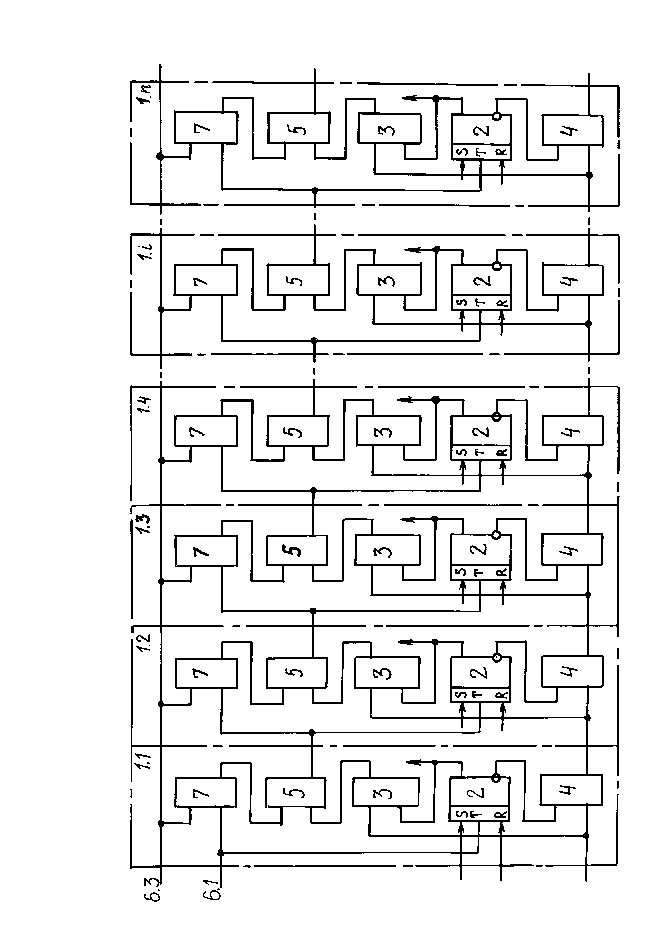

На чертеже представлена схема преобразователя кодов.

Преобразователь кодов содержит разряды 1.1-1. n (n =  ), каждый из которых включает в себя триггер 2, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И 3 и 4, причем выход первого элемента И 3 соединен с первым входом элемента ИЛИ 5, выход элемента ИЛИ 5 каждого предыдущего разряда преобразователя соединен со счетным входом триггера 2 последующего разряда преобразователя, счетный вход триггера 2 первого разряда 1.1 преобразователя является входом 6.1 задания преобразования в обратный код преобразователя, выход второго элемента И 4 каждого предыдущего разряда соединен с объединенными вторыми входами первого и второго элементов И 3 и 4 последующего разряда преобразователя, объединенные вторые входы первого и второго элементов И 3 и 4 первого разряда 1.1 преобразователя являются входом 6.2 задания преобразования в дополнительный код преобразователя, первый вход третьего элемента И 7 разряда преобразователя соединен со счетным входом триггера 2 своего разряда преобразователя, выход которого соединен с вторым входом элемента ИЛИ 5 своего разряда преобразователя, объединенные вторые входы третьих элементов И 7 всех разрядов преобразователя соединены с входом 6.3 задания двоичного кода или кода Грея преобразователя.

), каждый из которых включает в себя триггер 2, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И 3 и 4, причем выход первого элемента И 3 соединен с первым входом элемента ИЛИ 5, выход элемента ИЛИ 5 каждого предыдущего разряда преобразователя соединен со счетным входом триггера 2 последующего разряда преобразователя, счетный вход триггера 2 первого разряда 1.1 преобразователя является входом 6.1 задания преобразования в обратный код преобразователя, выход второго элемента И 4 каждого предыдущего разряда соединен с объединенными вторыми входами первого и второго элементов И 3 и 4 последующего разряда преобразователя, объединенные вторые входы первого и второго элементов И 3 и 4 первого разряда 1.1 преобразователя являются входом 6.2 задания преобразования в дополнительный код преобразователя, первый вход третьего элемента И 7 разряда преобразователя соединен со счетным входом триггера 2 своего разряда преобразователя, выход которого соединен с вторым входом элемента ИЛИ 5 своего разряда преобразователя, объединенные вторые входы третьих элементов И 7 всех разрядов преобразователя соединены с входом 6.3 задания двоичного кода или кода Грея преобразователя.

Преобразователь кодов работает следующим образом.

Преобразуемое число записывается в триггеры 2 с входами R (установки нуля) и S (установки единицы) и хранится этими триггерами как до, так и после преобразований.

Предусмотрено два режима работы преобразователя в зависимости от наличия потенциального единичного или потенциального нулевого сигнала на входе 6.3 преобразователя.

При наличии потенциального единичного сигнала на входе 6.3 преобразователя для преобразования кода хранимого числа в обратный необходимо подать импульсный единичный сигнал на вход 6.1, а в дополнительный - на вход 6.2. Преобразование кода хранимого числа в обратный заключается в инвертировании всего кода числа. Сигнал преобразования с входа 6.1 поступает непосредственно на счетный вход триггера 2 первого разряда 1.1, инвертируя его состояние, и далее через элементы И 7 или ИЛИ 5 на счетные входы триггеров 2 всех последующих 1.2-1. n разрядов, обеспечивая инвертирование хранимого триггерами кода. Преобразование кода хранимого числа в дополнительный заключается в инвертировании части кода, расположенной старше самой младшей единицы. Сигнал преобразования с входа 6.2 поступает на вторые входы первого и второго элементов И 3 и 4 первого разряда 1.1. Если первый разряд хранит нулевое значение, то действие этого сигнала проявляется на вторых входах первого и второго элементов И 3 и 4 второго разряда 1.2. Если первый разряд хранит единичное значение, то действие этого сигнала проявляется на счетных входах триггеров 2 второго и последующих разрядов 1.2-1. n.

Рассматривая аналогично работу второго и последующих разрядов, можно отметить, что распространение сигнала с входа 6.2 через вторые элементы И 4 осуществляется в группе младших разрядов, хранящих нулевое значение, причем на счетные входы триггеров 2 этих разрядов сигнал не проходит. В самом первом разряде (после группы нулевых разрядов), хранящем единичное значение, осуществляется перекоммутация сигнала через первый элемент И 3 этого разряда, а также через элементы И 7 и ИЛИ 5 последующих разрядов на счетные входы триггеров 2 этих разрядов, что приводит к инвертированию всей группы старших разрядов, следующих за самым младшим единичным разрядом, причем на счетный вход триггера 2 самого младшего единичного разряда сигнал не поступает. Отсутствие состязаний при этом гарантируется тем, что в группе младших нулевых разрядов и в самом младшем единичном разряде сигнал с входа 6.2 на счетные входы триггеров 2 этих разрядов не поступает вообще, а также тем, что в группе старших разрядов, следующих за самым младшим единичным разрядом, сигналы на счетных входах триггеров 2 последующих разрядов не зависят от состояния триггеров 2 предыдущих разрядов.

Операция прямого счета осуществляется в два такта, а именно путем последовательного преобразования записанного в разряды числа сначала в обратный, а затем в дополнительный код. Для этого необходимо подать сигнал вначале на вход 6.1, а затем на вход 6.2. В результате модуль записанного в разряды числа увеличится на единицу.

Операция обратного счета также осуществляется в два такта, но при этом число, записанное в разряды, последовательно преобразуется сначала в дополнительный, а затем в обратный код. Для этого необходимо подать сигнал сначала на вход 6.2, а затем на вход 6.1. В результате модуль записанного в разряды числа уменьшается на единицу.

При наличии потенциального нулевого сигнала на входе 6.3 преобразователь обеспечивает формирование прямой и обратной последовательностей кода Грея, что также может быть использовано для прямого и обратного счета с пониженным потреблением энергии на переключение, так как в каждом такте работы устройства изменяет свое состояние только один элемент памяти (триггер 2). В этом случае подача импульсного единичного сигнала на вход 6.1 приводит к инвертированию только младшего разряда, а подача импульсного единичного сигнала на вход 6.2 - к инвертированию только одного разряда, расположенного после самой младшей единицы. Сигнал преобразования с входа 6.1 поступает непосредственно на счетный вход триггера 2 первого разряда 1.1, инвертируя его состояние, и не проходит через элемент И 7 первого разряда 1.1 на остальные разряды. Сигнал преобразования с входа 6.2 распространяется через вторые элементы И 4 в группе младших разрядов, хранящих нулевое значение, причем на счетные входы триггеров 2 этих разрядов сигнал не проходит. В самом первом разряде (после группы нулевых разрядов), хранящем единичное значение, осуществляется перекоммутация сигнала через первый элемент И 3 и элемент ИЛИ 5 этого разряда на счетный вход триггера 2 следующего разряда, инвертируя его состояние, и не проходит через элемент И 7 следующего разряда на остальные старшие разряды. Операции прямого и обратного счета выполняются так же, как и в ранее рассмотренном режиме, но не в стандартном двоичном коде.

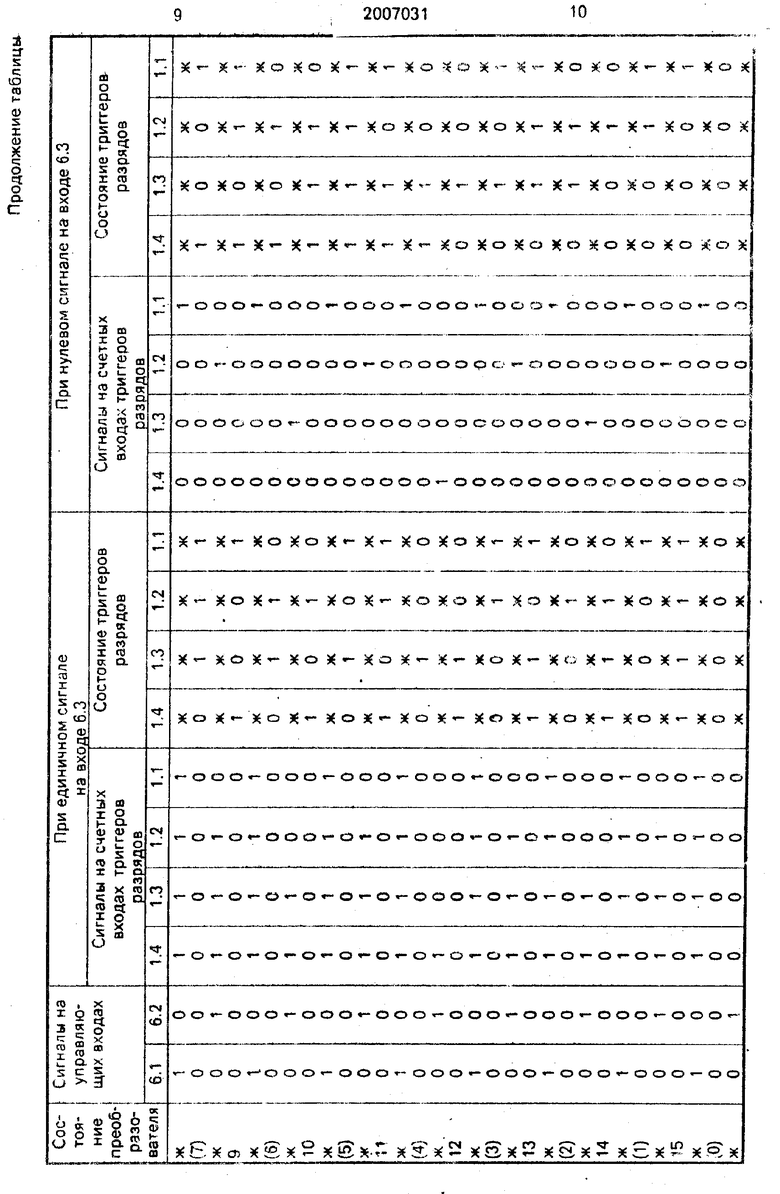

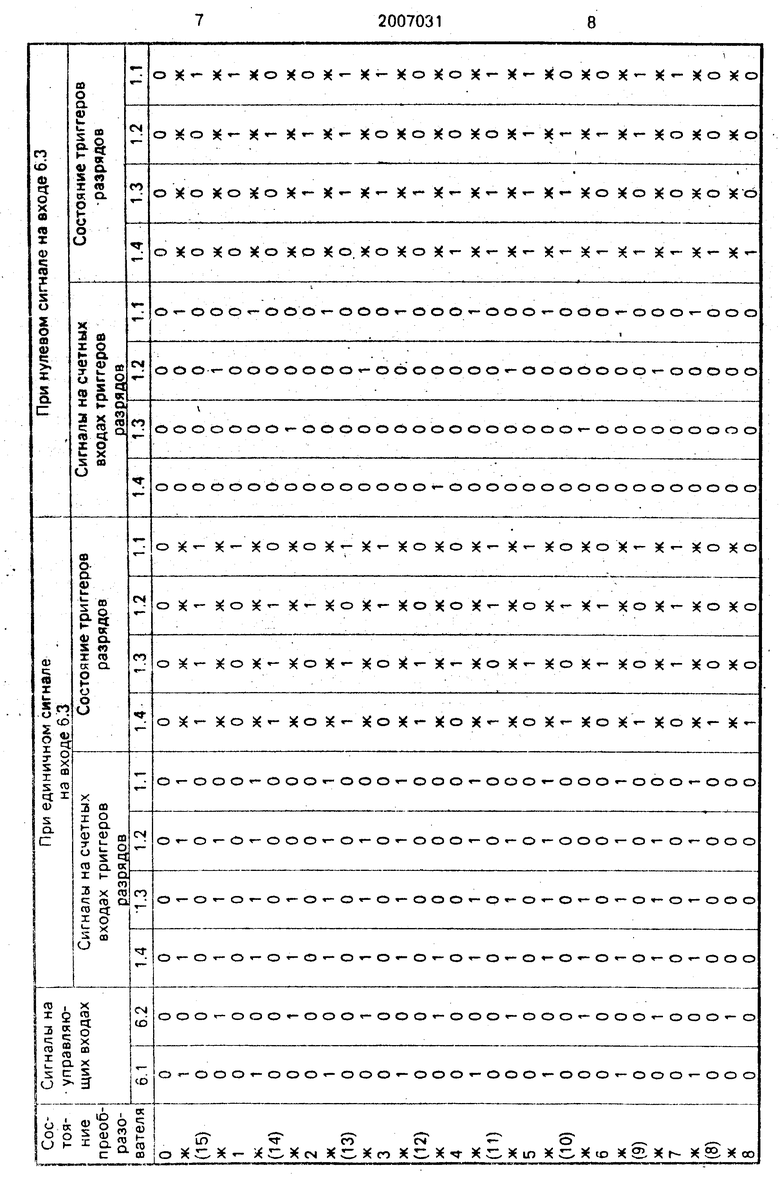

Таблица переходов для случая, когда в устройстве использованы триггеры, переключающиеся по заднему фронту входного сигнала, приведена ниже. В таблице представлено функционирование первых четырех разрядов устройства, причем звездочкой обозначено сохранение предыдущего состояния.

В первой колонке таблицы переходов обозначены состояния преобразователя, которые условно могут быть разбиты на основные (номера состояний без скобок) и промежуточные (номера состояний в скобках). Анализ таблицы переходов позволяет сделать вывод о том, что при нулевом сигнале на входе 6.3 переход в соседние состояния осуществляется путем переключения только одного элемента памяти. При этом прямая и обратная последовательности формируемых кодовых комбинаций являются последовательностью комбинаций кода Грея. (56) Авторское свидетельство СССР N 1368992, кл. Н 03 М 7/12, 1986.

Авторское свидетельство СССР N 1455392, кл. Н 03 М 7/12, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1987 |

|

SU1455392A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДОВ | 1991 |

|

RU2022468C1 |

| Реверсивное счетное устройство | 1989 |

|

SU1651377A1 |

| Счетное устройство | 1989 |

|

SU1707760A1 |

| Реверсивное счетное устройство | 1988 |

|

SU1651302A1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1992 |

|

RU2047272C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧЕТЫРЕХРАЗРЯДНОГО ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД | 1993 |

|

RU2040115C1 |

| Реверсивный двоичный счетчик | 1991 |

|

SU1811004A1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматических и вычислительных устройствах для преобразования хранимого кода в обратный или дополнительный, для выполнения операций прямого и обратного счета в стандартном и нестандартном двоичном коде, а также для формирования прямой и обратной последовательностей кодовых комбинаций кода Грея. Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования прямой и обратной последовательностей кода Грея. Преобразователь содержит разряды 1, каждый из которых включает в себя триггер 2, элементы И 3, 4, 7, элемент ИЛИ 5. 1 табл. , 1 ил.

ПРЕОБРАЗОВАТЕЛЬ КОДОВ, содержащий в каждом разряде триггер, первый и второй элементы И и элемент ИЛИ, причем парафазные входы разрядов информационного входа преобразователя соединены соответственно с входами установки в "1" и "0" триггеров соответствующих разрядов преобразователя, прямой выход триггера каждого разряда преобразователя соединен с первым входом первого элемента И того же разряда преобразователя и является выходом соответствующего разряда выхода преобразователя, инверсный выход триггера каждого разряда преобразователя соединен с первым входом второго элемента И того же разряда преобразователя, выход первого элемента И каждого разряда преобразователя соединен с первым входом элемента ИЛИ того же разряда преобразователя, вход задания преобразования в обратный код преобразователя соединен со счетным входом триггера первого разряда преобразователя, вход задания преобразования в дополнительный код преобразователя соединен с вторыми входами первого и второго элементов И первого разряда преобразователя, выход элемента ИЛИ каждого предыдущего разряда преобразователя соединен со счетным входом триггера последующего разряда преобразователя, выход второго элемента И каждого предыдущего разряда преобразователя соединен с вторыми входами первого и второго элементов И последующего разряда преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения формирования прямой и обратной последовательности кода Грея, каждый разряд преобразователя содержит третий элемент И, причем счетный вход триггера каждого разряда преобразователя соединен с первым входом третьего элемента И того же разряда преобразователя, выход третьего элемента И каждого разряда преобразователя соединен с вторым входом элемента ИЛИ того же разряда преобразователя, вход задания двоичного кода или кода Грея преобразователя соединен с вторым входом третьего элемента И каждого разряда преобразователя.

Авторы

Даты

1994-01-30—Публикация

1990-03-29—Подача