Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах отображения цифровой информации.

Известны преобразователь двоичных чисел в двоично-десятичный код, содержащий двоично-десятичные сумматоры, включающие в себя разделенные на тетрады сумматоры коррекции и двоичные сумматоры, а также группу разрядных преобразователей (авт. св. СССР N 1481897), и преобразователь двоичного кода в двоично-десятичный, содержащий регистры, блок управления вычитанием, сумматор, коммутатор, шифраторы и блок дешифрации (авт. св. СССР N 1330762).

Указанные преобразователи имеют сложную схемную реализацию и не обеспечивают полного преобразования входной информации, что требует введения дополнительных каскадов преобразования при необходимости полного использования входной двоичной информации.

Наиболее близким к изобретению техническим решением является четырехразрядный преобразователь двоичного кода в двоично-десятичный (авт. св. СССР N 1172019), содержащий три элемента НЕ и три элемента И, подключенные к управляющим входам, и четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, обеспечивающие выдачу выходной информации. Это устройство при преобразовании входной информации не учитывает состояние старшего разряда двоичного кода для двоичных чисел, десятичный эквивалент которых превышает число девять, что при использовании данных преобразователей в схемах управления цифровыми индикаторами приводит к необходимости на каждый десятичный разряд иметь свой преобразователь.

Технический результат изобретения предполагает расширение области применения преобразователя и достигается тем, что в преобразователь четырехразрядного двоичного кода в двоично-десятичный код, содержащий первый, второй, третий и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, введены первый, второй, третий и четвертый мажоритарные элементы, при этом управляющий вход первого разряда напрямую подключен к первому выходу преобразователя, управляющий вход второго разряда подключен к первым входам первого мажоритарного элемента, первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход третьего разряда подключен к вторым входам первого и четвертого мажоритарных элементов, управляющий вход четвертого разряда подключен к первым входам второго и третьего мажоритарных элементов и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход первого мажоритарного элемента и вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к плюсовой шине питания, третьи входы второго, третьего и четвертого мажоритарных элементов подключены к минусовой шине питания, выход первого мажоритарного элемента соединен с вторым входом второго мажоритарного элемента, выход которого соединен общей связью с вторыми входами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и пятым выходом преобразователя, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму входу третьего мажоритарного элемента, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенного выходом к первому входу четвертого мажоритарного элемента, выходы третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образуют второй и четвертый выходы преобразователя, а выход четвертого мажоритарного элемента образует третий выход преобразователя.

Новизна предложенного преобразователя заключается в том, что он содержит четыре мажоритарных элемента, связанных с управляющими входами преобразователя и четырьмя элементами ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом в отличие от прототипа данный преобразователь имеет пять выходов, первые четыре из которых соответствуют двоичному эквиваленту младшего разряда десятичного числа (единицы), а пятый соответствует младшему разряду двоичного эквивалента второго разряда десятичного числа (десятки).

Анализ существующих устройств в области, к которой относится изобретение, свидетельствует об отсутствии в них признаков, сходных с отличительными признаками в изобретении, что позволяет сделать вывод о существенном отличии данного устройства от имеющихся.

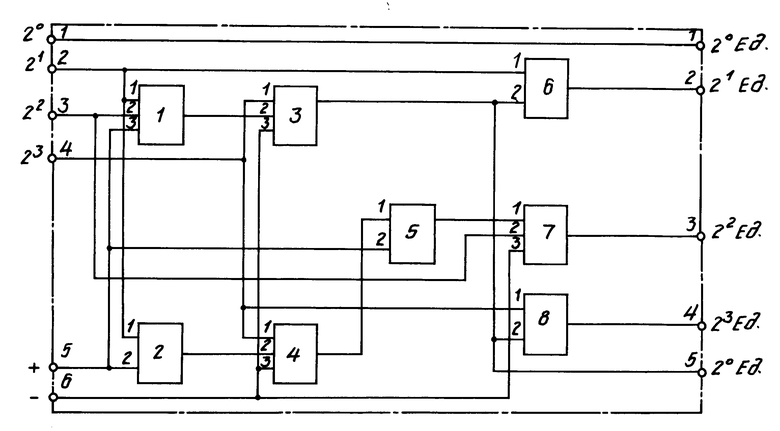

На чертеже приведена функциональная схема предлагаемого преобразователя.

В состав преобразователя входят первый мажоритарный элемент 1, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, второй мажоритарный элемент 3, третий мажоритарный элемент 4, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, четвертый мажоритарный элемент 7 и четвертый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Управляющий вход первого разряда 2о напрямую подключен к первому выходу преобразователя 2о Ед, управляющий вход второго разряда 21 подключен к первым входам первого мажоритарного элемента 1, первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 6, управляющий вход третьего разряда 22 подключен к вторым входам первого и четвертого мажоритарных элементов 1 и 7, управляющий вход четвертого разряда 23 подключен к первым входам второго и третьего мажоритарных элементов 3 и 4 и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Третий вход первого мажоритарного элемента 1 и вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 5 подключены к плюсовой шине питания. Третьи входы второго, третьего и четвертого мажоритарных элементов 3, 4 и 7 подключены к минусовой шине питания. Выход первого мажоритарного элемента 1 соединен с вторым входом второго мажоритарного элемента 3, выход которого соединен общей связью с вторыми входами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и 8 и пятым выходом преобразователя 2о Дес. Выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 подключен к второму входу третьего мажоритарного элемента 4, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, подключенного выходом к первому входу четвертого мажоритарного элемента 7. Выходы третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и 8 образуют второй и четвертый выходы 21 Ед. и 23 Ед. преобразователя, а выход четвертого мажоритарного элемента 7 образует третий выход 22 Ед преобразователя.

Преобразователь функционирует следующим образом.

При поступлении на управляющие входы 20, 21, 22, 23 преобразователя кода двоичного числа состояние первого выхода 2о Ед преобразователя, соответствующего младшему разряду двоичного эквивалента первого разряда ("единицы") десятичного числа, однозначно соответствует состоянию входа 2о. Состояние остальных выходов, кроме состояния входов, определяется внутренней логикой работы преобразователя. При этом при поступлении на вход преобразователя двоичных чисел, десятичные эквиваленты которых соответствуют числам от 0 до 9, состояние пятого выхода 2о Дес. преобразователя будет нулевым, поскольку оно соответствует младшему разряду двоичного числа, эквивалентного второму разряду (десятки) десятичного числа. Состояние остальных выходов преобразователя в этом случае соответствует состоянию одноименных входов.

Например, при поступлении на вход двоичного числа 0101, десятичный эквивалент которого соответствует числу 5, единичное состояние управляющего входа 2о напрямую передается на первый выход 2о Ед. преобразователя. Нулевой сигнал с второго управляющего входа 21 поступает на первые входы мажоритарного элемента 1 и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 6, единичный сигнал с третьего управляющего входа 22 поступает на вторые входы мажоритарных элементов 1 и 7, а нулевой сигнал с четвертого управляющего входа 23 поступает на первые входы мажоритарных элементов 3 и 4 и элемента ИСКЛЮЧЕНИЕ ИЛИ 8. При этом, поскольку третий вход мажоритарного элемента 1 и вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 5 подключены к положительной шине питания, что соответствует единичному сигналу, а третьи входы мажоритарных элементов 3, 4 и 7 подключены к минусовой шине питания, что соответствует нулевому сигналу, состояние выходов элементов схемы следующее: мажоритарных элементов 1 и 7 "1", мажоритарных элементов 3 и 4 "0", элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 5 "1", а элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и 8 "0". В этом случае состояние второго выхода 21 Ед. будет нулевым, третьего выхода 22 Ед. единичным, четвертого выхода 23 Ед. нулевым, т.е. соответствует состоянию входов 21, 22 и 23, а состояние пятого выхода 2о Дес. будет нулевым. Таким образом, состояние выходов преобразователя эквивалентно десятичному числу "05".

Если на вход преобразователя поступают двоичные числа, десятичный эквивалент которых соответствует числам с 10 до 15, состояние пятого выхода 2о Дес. будет единичным, а состояние остальных выходов соответствует двоичному эквиваленту младшего (единичного) разряда десятичного числа. Например, при поступлении на вход двоичного числа 1101, десятичный эквивалент которого соответствует числу 13, состояние первого выхода 2о Ед. преобразователя будет единичным, а состояние выходов элементов следующее: мажоритарных элементов 1, 3 и 4 единичным, мажоритарного элемента 7 нулевым, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 6 единичным, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и 8 нулевым. Тогда состояния второго 21 Ед. и пятого 2о Дес. выходов преобразователя будут единичными, а третьего 22 Ед. и четвертого 23 Ед. нулевыми и в целом состояние выходов преобразователя эквивалентно десятичному числу "13".

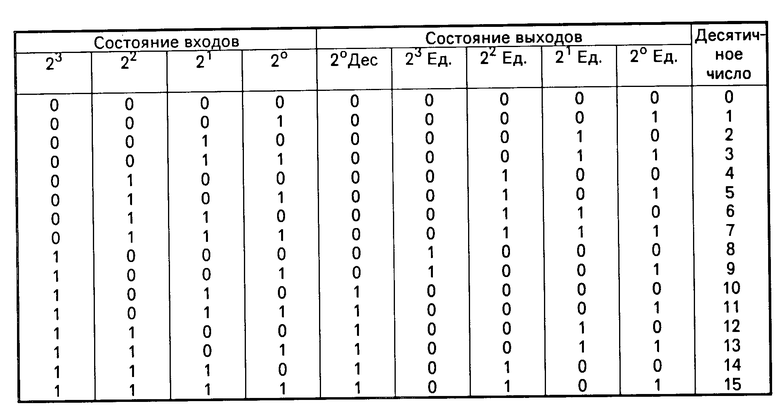

В таблице приведены состояния выходов преобразователя для всех возможных состояний управляющих входов и соответствующий им десятичный эквивалент числа.

Предложенный преобразователь четырехразрядного двоичного кода в двоично-десятичный код обеспечивает более полное преобразование входной информации, поскольку обеспечивает однозначное соответствие между состояниями выходов и каждой из шестнадцати входных комбинаций двоичного кода. Тем самым в отличие от существующих устройств данный преобразователь обеспечивает не только формирование одной тетрады вторично-десятичного кода, соответствующей десятичным числам от 0 до 9, но и младшего разряда следующей тетрады, что создает возможность иметь на выходе информацию, соответствующую десятичным числам от 0 до 15.

Таким образом, данный преобразователь обладает более широкими функциональными возможностями, что позволяет, в частности, использовать в схемах индикации цифровой информации всего один преобразователь для управления двумя цифровыми индикаторами десятичного числа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1990 |

|

RU2007031C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДОВ | 1991 |

|

RU2022468C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| Преобразователь кодов | 1987 |

|

SU1455392A1 |

| РЕЗЕРВИРОВАННАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2072567C1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1992 |

|

RU2047272C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| Преобразователь частоты в код | 1990 |

|

SU1751851A1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах отображения цифровой информации. Преобразователь четырехразрядного двоичного кода в двоично-десятичный код обеспечивает расширение функциональных возможностей с одновременным упрощением схемного решения, что достигается включением в состав преобразователя мажоритарных элементов 1,3,4,7, входы которых связаны с управляющими входами преобразователя, а выходы через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 5,6,8 обеспечивают выдачу двоично-десятичной информации на выходе преобразователя. Тем самым данный преобразователь обеспечивает в отличие от существующих формирование как первой тетрады двоично-десятичного кода, соответствующей разряду единиц десятичного числа, так и младшего разряда второй тетрады, соответствующей разряду десятков десятичного числа, что позволяет использовать данный преобразователь в схемах индикации для управления работой двух десятичных цифровых индикаторов. 1 табл. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ ЧЕТЫРЕХРАЗРЯДНОГО ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД, содержащий первый, второй, третий и четвертый элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что он включает в себя первый, второй, третий и четвертый мажоритарные элементы, при этом управляющий вход первого разряда напрямую подключен к первому выходу преобразователя, управляющий вход второго разряда подключен к первым входам первого мажоритарного элемента, первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход третьего разряда подключен к вторым входам первого и четвертого мажоритарных элементов, управляющий вход четвертого разряда подключен к первым входам второго и третьего мажоритарных элементов и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход первого мажоритарного элемента и вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к плюсовой шине питания, третьи входы второго, третьего и четвертого мажоритарных элементов подключены к минусовой шине питания, выход первого мажоритарного элемента соединен с вторым входом второго мажоритарного элемента, выход которого соединен общей связью с вторыми входами третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и пятым выходом преобразователя, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму входу третьего мажоритарного элемента, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенного своим выходом к первому входу четвертого мажоритарного элемента; выходы третьего и четвертого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ образауют второй и четвертый выходы преобразователя, а выход четвертого мажоритарного элемента образует третий выход преобразователя.

| Четырехразрядный преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1172019A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-07-20—Публикация

1993-03-10—Подача