Изобретение относится к вычислительной технике и может быть использовано в устройствах для формирования элементов конечных колей, в устройствах, функционирующих в СОК, а также в устройствах для формирования кодовых последовательностей, построение которых основывается на теppитоpии конечных полей.

Известно устройство для формирования остатка по произвольному модулю от числа, содержащее два блока элементов ИЛИ, два блока элементов И, два регистра, вычитатель, два формирования импульсов, два элемента ИЛИ и схему сравнения [1] .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для формирования остатка по произвольному модулю от числа, содержащее первый и второй регистры, первый и второй элементы ИЛИ, вычитатель, первую схему сравнения и мультиплексор [2] .

Недостатком данного устройства является низкое быстродействие процесса формирования остатка.

Сущность изобретения состоит в реализации следующей идеи приведения чисел по произвольному модулю. Известно, что позиционные системы счисления строятся по следующему принципу. Выбирается некоторое число m - основание системы счисления, и каждое число А представляется в виде комбинации его степеней с коэффициентами ai, i=  , принимающими значения от 0 до m - 1, т. е. в виде

, принимающими значения от 0 до m - 1, т. е. в виде

akmk + . . . a1m + ao, (1) где k - разрядность представляемого числа. Для двоичной системы счисления выражение (1) принимает вид

ak2k + ak-12k-1 + . . . + a12 + ao, (2) где ai, i =  принимает значение 0 или 1.

принимает значение 0 или 1.

Известно также, что сравнения можно почленно складывать, т. е.

A1 ≡ B1(modP), A2 ≡ B2(modP) . . . Ak ≡ Bk(modP), тогда справедливо следующее выражение:

A1 + A2 + . . . Ak ≡ B1 + B2 + . . . +

+ Bk (nodP). (3)

Учитывая выражения (2) и (3), можно записать

(ak2k + ak-12k-1 + . . . a12 + ao)modP ≡ ak2k(mod P) + ak-12k-1(modP) + . . . + +a12(modP) + ao(modP).

Так как для двоичной системы счисления коэффициенты ai, i=  , где k - разрядность представляемого числа А, принимают только два значения 0 или 1, то, суммируя заранее вычисленные остатки по модулю Р от чисел 2i, i=

, где k - разрядность представляемого числа А, принимают только два значения 0 или 1, то, суммируя заранее вычисленные остатки по модулю Р от чисел 2i, i=  , для тех i, для которых коэффициенты ai = 1, получают остаток по модулю Р от числа А. Для модулей Pi, с которыми предполагается работа устройства, в постоянном запоминающем устройстве запоминаются заранее вычисленные остатки от чисел 2i, i=

, для тех i, для которых коэффициенты ai = 1, получают остаток по модулю Р от числа А. Для модулей Pi, с которыми предполагается работа устройства, в постоянном запоминающем устройстве запоминаются заранее вычисленные остатки от чисел 2i, i=  , где k - разрядность чисел, от которых необходимо формировать остатки.

, где k - разрядность чисел, от которых необходимо формировать остатки.

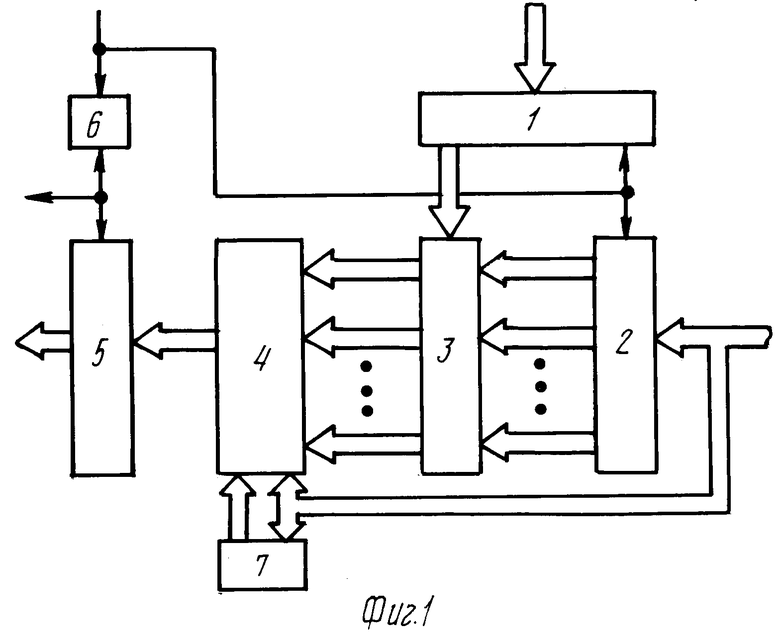

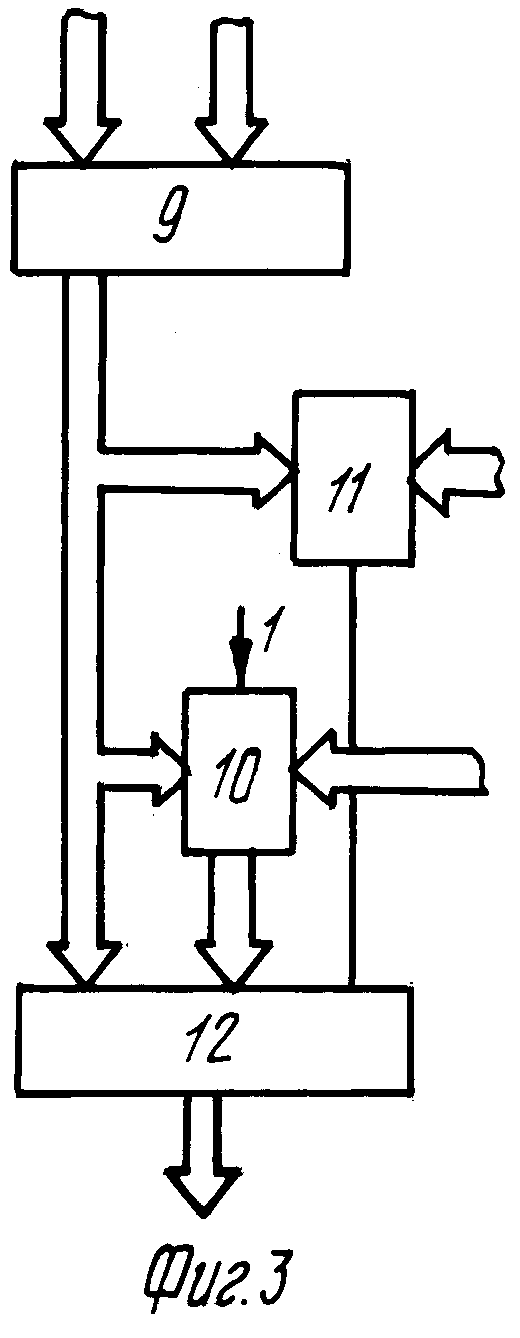

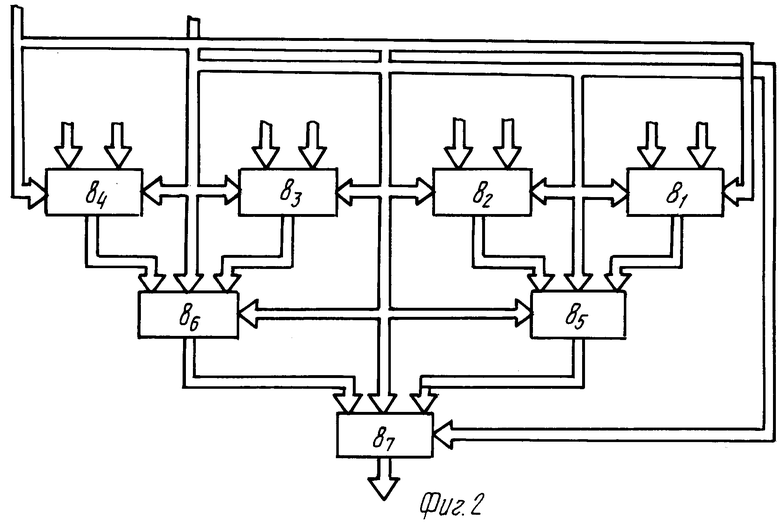

На фиг. 1 представлена функциональная схема устройства для формирования остатка по произвольному модулю от числа; на фиг. 2 - функциональная схема блока сумматоров по произвольному модулю; на фиг. 3 - сумматор по произвольному модулю.

Устройство содержит (фиг. 1) первый регистр 1, информационные входы которого являются входами кода числа, последовательно соединенные блок 2 постоянной памяти, группу 3 блоков элементов И, блок 4 сумматоров по произвольному модулю и второй регистр 5, а также элемент 6 задержки и блок 7 инверторов. Код модуля подается на адресный вход блока 2 постоянной памяти, на первые входы блока 4 сумматоров по произвольному модулю и вход блока 7 инверторов, выходы которого соединены с вторыми входами блока 4 сумматоров по произвольному модулю. Вход начала вычисления соединен с входами элемента 6 задержки, входом разрешения записи блока 2 постоянной памяти и входом разрешения записи регистра 1, информационные выходы которого подсоединены к вторым входам группы 3 блоков элементов И, а выход элемента 6 задержки соединен с управляющим входом второго регистра 5, информационные выходы которого являются информационными выходами устройства, и является управляющими выходами устройства.

Блок 4 сумматоров по произвольному модулю содержит (фиг. 2) сумматоры 8 по произвольному модулю, на каждый из которых поступают значения модуля в прямом и в инверсном коде.

Сумматор 8 по произвольному модулю содержит (фиг. 3) первый 9 и второй 10 комбинационные сумматоры, схему 11 сравнения и мультиплексор 12. На вход переноса сумматора 10 подан код единицы.

Устройство для формирования остатка по произвольному модулю от числа работает следующим образом.

В исходном состоянии регистры 1 и 5 обнулены. В блоке 2 постоянной памяти 2 предварительно записаны заранее вычисленные остатки от чисел 2i, i=  , где k - максимальная разрядность числа Ak, по модулям Pj, с которыми предполагается работа устройства. Модуль Pi, по которому осуществляется формирование остатков чисел, задается параллельным двоичным кодом, подаваемым на вход модуля устройства. На информационные входы регистра 1 поступает число Ak в параллельном двоичном коде. После подачи кодов числа Ak и модуля Pi на входы устройства на вход "Начало вычисления" подается импульс, который, поступая на вход записи регистра 1, записывает в него код числа Ak и поступает на вход разрешения чтения блока 2. В результате на выходе блока 2 появляются остатки от чисел 2i, i=

, где k - максимальная разрядность числа Ak, по модулям Pj, с которыми предполагается работа устройства. Модуль Pi, по которому осуществляется формирование остатков чисел, задается параллельным двоичным кодом, подаваемым на вход модуля устройства. На информационные входы регистра 1 поступает число Ak в параллельном двоичном коде. После подачи кодов числа Ak и модуля Pi на входы устройства на вход "Начало вычисления" подается импульс, который, поступая на вход записи регистра 1, записывает в него код числа Ak и поступает на вход разрешения чтения блока 2. В результате на выходе блока 2 появляются остатки от чисел 2i, i=  по модулю Pi. Импульс с входа "Начало вычисления" поступает также на вход элемента 6 задержки. Одновременно с информационных выходов регистра 1 на группу 3 блоков элементов И поступает код числа Ak, открывая те блоки группы, на которые поступает единица. В результате на соответствующие входы блока 4 сумматоров поступают остатки от чисел 2i, i=

по модулю Pi. Импульс с входа "Начало вычисления" поступает также на вход элемента 6 задержки. Одновременно с информационных выходов регистра 1 на группу 3 блоков элементов И поступает код числа Ak, открывая те блоки группы, на которые поступает единица. В результате на соответствующие входы блока 4 сумматоров поступают остатки от чисел 2i, i=  , для тех i, для которых ai = 1 для числа Ak. На управляющие входы блока 4 поступает значение модуля в прямом и инверсном коде. Блок 4 осуществляет суммирование по модулю Pi поступающих на его входы чисел, эта сумма оказывается на его выходах и поступает на информационные входы регистра 5. Время задержки элемента 6 равно времени формирования остатка, поэтому по окончанию процесса формирования остатка по заданному модулю на выходе элемента 6 задержки появляется импульс, который записывает код остатка в регистр 5 и поступает на выход окончания работы устройства.

, для тех i, для которых ai = 1 для числа Ak. На управляющие входы блока 4 поступает значение модуля в прямом и инверсном коде. Блок 4 осуществляет суммирование по модулю Pi поступающих на его входы чисел, эта сумма оказывается на его выходах и поступает на информационные входы регистра 5. Время задержки элемента 6 равно времени формирования остатка, поэтому по окончанию процесса формирования остатка по заданному модулю на выходе элемента 6 задержки появляется импульс, который записывает код остатка в регистр 5 и поступает на выход окончания работы устройства.

Сумматор 8 по произвольному модулю работает следующим образом. На входы сумматора 9 подаются слагаемые в диапазоне чисел от 0 до Р - 1, на второй вход схемы 11 сравнения подается прямой код модуля Р, а на второй вход сумматора 10 - инверсный код модуля Р. Если сумма слагаемых меньше модуля Р, то на выходе "Меньше" схемы 11 сравнения появляется потенциал, который поступает на управляющий вход мультиплексора 12. Последний в результате воздействия управляющего импульса коммутирует со своим выходом свой первый вход и на выходе сумматора 8 по модулю оказывается сумма слагаемых, поступающих на его входы. Если эта сумма превышает величину модуля (или равна ей), то потенциала на управляющем входе мультиплексора 12 нет и мультиплексор 12 коммутирует со своим выходом свой второй вход. При этом на втором входе оказывается код числа, равного сумме слагаемых, поступающих на вход сумматора 8, приведенный по модулю Р.

При следующем цикле формирования остатка может быть выбран любой другой модуль Ра и задано любое другое число Ае. (56) Авторское свидетельство СССР N 1396281, кл. H 03 M 7/18, 1986.

Авторское свидетельство СССР N 1633495, кл. H 03 M 7/18, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 1991 |

|

RU2007037C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНДЕКСОВ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007035C1 |

| КОМБИНАЦИОННЫЙ РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ | 1992 |

|

RU2029435C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1992 |

|

RU2012137C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНДЕКСОВ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007034C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007036C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| СУММАТОР ПО МОДУЛЮ P | 1992 |

|

RU2032934C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2023346C1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах для формирования элементов конечных полей, в устройствах, функционирующих в СОК, а также в устройствах для формирования кодовых последовательностей, построение которых основывается на теории конечных целей. Целью изобретения является повышение быстродействия устройства. Устройство для формирования остатка по произвольному модулю от числа содержит два регистра, блок постоянной памяти, группу блоков элементов И, блок сумматоров по произвольному модулю, элемент задержки и блок инверторов, соединенные между собой функционально. 1 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-01-30—Публикация

1991-01-09—Подача