Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей.

Известен сумматор по модулю, содержащий три сумматора, элементы ИЛИ-НЕ и элемент ИЛИ с соответствующими связями [1]

Недостатком данного сумматора является его ограниченные функциональные возможности, так как оно работает только с простыми модулями и диапазон суммируемых чисел лежит в пределах

O ≅ X/Y/≅ Р-1, где Х первое число;

Y второе число;

Р величина модуля.

Известен сумматор по модулю, содержащий первый и второй сумматоры и коммутатор с соответствующими сведениями [2]

Недостатком данного сумматора являются ограниченные функциональные возможности, так как диапазон суммируемых чисел лежит в пределах от нуля до Р-1.

Целью изобретения является расширение функциональных возможностей сумматора за счет расширения диапазона суммирующих чисел.

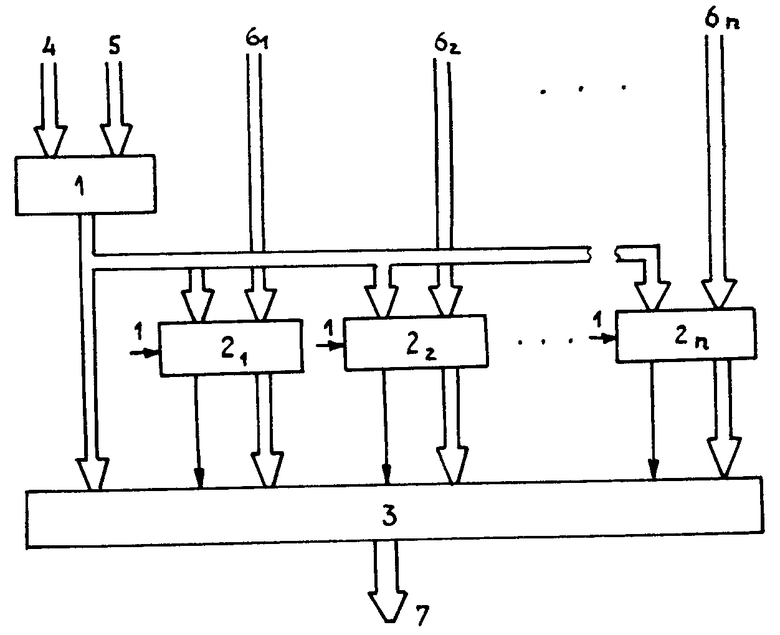

На чертеже представлена функциональная электрическая схема сумматора по модулю Р.

Предлагаемый сумматор содержит двоичные сумматор 1, n сумматоров 21+2n и коммутатор (мультиплексор) 3. Входы 4 и 5 служат для подачи кодов первого и второго числа. На входы 6i(i  ) подаются инверсные коды i-Р, а выход 7 сумматора является информационным. Число сумматоров n зависит от максимальной разрядности суммируемых чисел и определяется выражением

) подаются инверсные коды i-Р, а выход 7 сумматора является информационным. Число сумматоров n зависит от максимальной разрядности суммируемых чисел и определяется выражением

n  где Хмакс максимально возможное значение первого числа;

где Хмакс максимально возможное значение первого числа;

Yмакс максимально возможное значение второго числа;

Р значение модуля свертки;

[*] операция приведения до большого целого числа.

Сумматор по модулю Р работает следующим образом.

На входы 4 и 5 сумматора поступают числа из диапазона чисел O≅X/Y/≅Хмакс/Yмакс/, которые суммируются в сумматоре 1 и с его выхода результат суммирования поступает на первые входы сумматоров 21/2nи первые входы мультиплексора 3. Если значение суммы превышает значение модуля, то в сумматорах 2i за счет перевода инверсных кодов i ˙Р в дополнительные коды происходит вычитание из полученной суммы значений кодов. В первом сумматоре 21 вычитается код Р, во втором 22 код 2Р и т.д. В последнем сумматоре происходит вычитание кода nР. На управляющих выходах тех сумматоров 2i, в которых значение суммы превышает значение числа i ˙Р, появляется управляющий сигнал, а на управляющих выходах сумматоров 2i, в которых значение суммы меньше значения констант i˙ Р, управляющий сигнал отсутствует. Управляющая логика мультиплексора выполнена таким образом, что реагирует на управляющий сигнал старшего разряда. Поэтому, если введено число Ак, лежащее в интервале (i+1)˙ P>Ak ≥i˙ Р, выход i-го сумматора 2 будет скоммутирован на выход мультиплексора 3 и остаток r Ak -i ˙Р будет сформирован на выходе сумматора.

Если же значение суммы не превышает значения модуля, то с управляющих выходов сумматоров 21-22 управляющих сигналов на управляющие входы мультиплексора 3 не подается, первые его информационные входы остаются скоммутированными на информационные выходы и значение суммы с выхода сумматора 1 через мультиплексор 3 поступает на информационные выходы 7 сумматора.

Пусть Х 1510 011112, Y 4710 1011112, максимальное значение суммы чисел равно 7010, а Р 1010 10102. Тогда n 7. Инверсные значения кодов будут соответственно равны

11101012,

11101012,

11010112,

11010112,

11000012,

11000012,

10101112,

10101112,

10011012,

10011012,

10000112,

10000112,

01110012. На выходе сумматора 1 получается число А Х + Y 1510 + 4710 6210 1112 + 1011112= 1111102.

01110012. На выходе сумматора 1 получается число А Х + Y 1510 + 4710 6210 1112 + 1011112= 1111102.

Тогда на выходах сумматоров 2 образуются следующие коды:

A+ +1 i

+1 i

=

=

21: 01111102, + 11101012 + 1 100001002,

22 01111102 + 11010112 + 1 100010102,

23 01111102 + 11000012 + 1 101000002,

24 01111102 + 10101112 + 1 100101102,

25 01111102 + 10011012 + 1 100011002,

26 01111102 + 10000112 + 1 100000102,

27 01111102 + 01110012 + 1 011110002.

Таким образом, на выходе переноса (восьмой разряд) всех сумматоров за исключением последнего образуется единица, логика коммутатора 3 реагирует на сигнал старшего (шестого) сумматора 2 и код 102 с его выхода через коммутатор 3 поступает на выход 7 сумматора. При подаче кодов других чисел работа сумматора осуществляется аналогично описанному выше.

Таким образом, предлагаемый сумматор обладает расширенными функциональными возможностями за счет расширения диапазона суммируемых чисел и работы с любыми модулями.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2007033C1 |

| КОМБИНАЦИОННЫЙ РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ | 1992 |

|

RU2029435C1 |

| РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 1991 |

|

RU2007037C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1992 |

|

RU2012137C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007036C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНДЕКСОВ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007034C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНДЕКСОВ ЭЛЕМЕНТОВ МУЛЬТИПЛИКАТИВНЫХ ГРУПП ПОЛЕЙ ГАЛУА GF (P) | 1991 |

|

RU2007035C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

| УМНОЖИТЕЛЬ НА ДВА ПО МОДУЛЮ | 1991 |

|

RU2015537C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах для формирования элементов конечных полей. Цель изобретения - расширение функциональных возможностей. Это достигается использованием коммутатора и сумматоров. 1 ил.

СУММАТОР ПО МОДУЛЮ P, содержащий первый и второй двоичные сумматоры и коммутатор, причем первый и второй информационные входы первого двоичного сумматора соединены с входами кодов первого и второго чисел сумматора по модулю, а информационный выход с первыми информационными входами коммутатора и второго двоичного сумматора, второй информационный вход которого соединен с входом инверсного кода p сумматора по модулю, вход переноса второго двоичного сумматора соединен с входом сигнала логической единицы сумматора по модулю, выход переноса и информационный выход соответственно с первым управляющим и вторым информационным входами коммутатора, выход которого соединен с выходом сумматора по модулю, отличающийся тем, что в него введены n 1 двоичных сумматоров n xмакс + yмакс)P где xмакс, yмакс - максимально возможные значения первого и второго чисел), причем первый информационный вход i-го двоичного сумматора  соединен с информационным выходом первого двоичного сумматора, второй информационный вход с входом инверсного кода (i 1).p, вход переноса с входом сигнала логической единицы, выход переноса и информационный выход соответственно с (i 1)-м управляющим и i-м информационным входом коммутатора.

соединен с информационным выходом первого двоичного сумматора, второй информационный вход с входом инверсного кода (i 1).p, вход переноса с входом сигнала логической единицы, выход переноса и информационный выход соответственно с (i 1)-м управляющим и i-м информационным входом коммутатора.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 4722067, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1995-04-10—Публикация

1992-04-30—Подача