Изобретение относится к вычислительной системе, включающей конфигурацию разъемов с первым множеством контактов, а также дополнительную плату со вторым множеством контактов, в которой первое множество контактов сделано для сцепления со вторым множеством контактов, что позволяет вставить дополнительную пасту в конфигурацию разъемов.

Известно, что компьютер, например компьютер серии PS/2 корпорации 1ВМ, снабжают гнездами, включающими один или несколько шинных разъемов, чтобы позволить подсоединить к компьютерной шине топологические платы с соответствующими схемами, с целью расширения компьютерных возможностей для пользователя. Эти гнезда обеспечивают физическую поддержку для топологических плат, а шинный(ые) разъем(ы) приспособлен(ы) таким образом, чтобы сопрягаться с разъемом на топологической плате, когда плата полностью вставлена в гнездо.

В определенных компьютерах, как, например, 1ВМ PS/2 модели 80, в соответствующих гнездах предусмотрены шинные разъемы двух разных размеров. Эти разные разъемы отражают различия в количестве параллельных разрядов, отведенных для адресации к данным и памяти. Обычно разряды распределяют кратно восьми, а в случае с моделью 80 имеются гнезда, которые предусмотрены для 16-разрядной параллельной адресации, а также гензда, которые предусмотрены для 32 параллельных разрядов. Известно, что предусматривается позиция флагового разряда, чтобы показать, когда команда, посланная по шине, является 16-разрядной командой, а когда 32-разрядной (например, логическая 1 - 32 разрядам, а логический 0 = 16 разрядам) для того, чтобы плата в 16-разрядном гнезде могла обнаружить команды, выходящие за ее диапазон, и не выполнять никаких действий. Это позволяет 16-разрядной плате избежать ситуации, когда, видя только часть команды или адреса, она приступает к неправильному действию.

Эта позиция флагового разряда однако не дает никакой защиты в случае, когда 32-разрядную плату вставляют в 16-разрядное гнездо. В этом случае будет работать так, как будто она находится в 32-разрядном гнезде, и неправильно интерпретировать сигналы в пропущенных позициях.

Известно битовое управление данными между двумя шинами данных разного размера, но такое битовое управление обычно осуществляют посредством фиксированной интерфейсной логики, осознавая, что определение шин на каждой стороне будет оставаться одинаковым.

Целью изобретения является разработка платы расширения, которая адаптируется к ширине разъема, т. е. которая обнаруживает, когда она находится в разъеме, который предусмотрен для платы с меньшей шириной шины.

Разработана топологическая плата, включающая специальные схемы для обнаружения условия, которое обычно не обеспечивает информацию о состоянии и последующей реакции на это условие, так, чтобы был выработан двоичный сигнал, характеризующий ширину шины гнезда.

Цель достигается тем, что в плату расширения, содержащую разъем с первой группой контактов и дополнительную плату со второй группой контактов, выполненную с возможностью соединения с первой группой контактов разъема при вставлении дополнительной платы в разъем, введен в дополнительную плату блок идентификации, первый вывод которого соединен с К-м контактом дополнительной платы, второй вывод блока идентификации соединен с локальной шиной дополнительной платы, при этом К-й контакт первой группы разъема соединен с шиной питания вычислительной системы, а блок идентификации содержит делитель напряжения, первый вывод первого резистора которого является первым выводом блока, первый вывод второго резистора соединен с шиной нулевого потенциала, а объединенные вторые выводы резисторов образуют второй вывод блока.

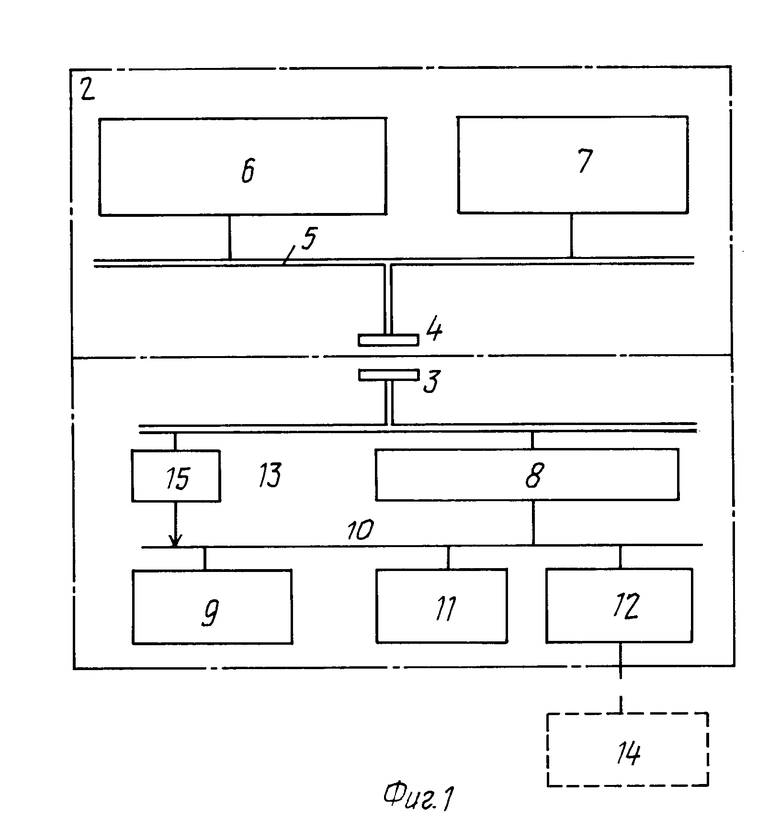

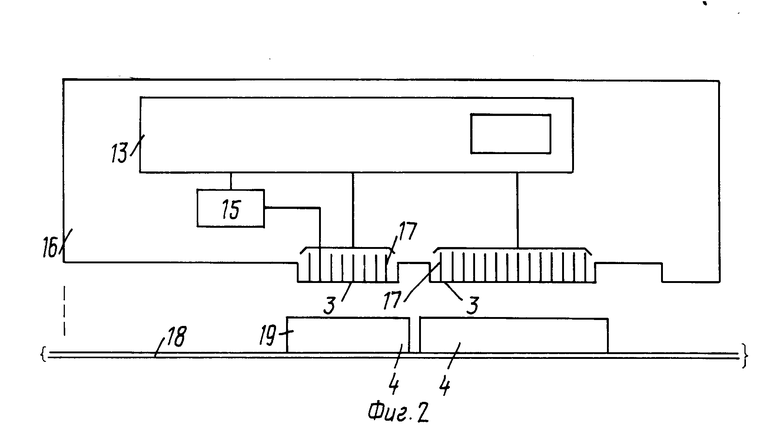

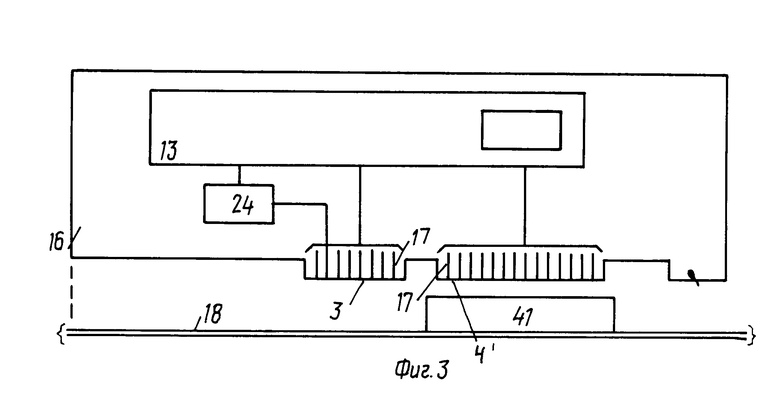

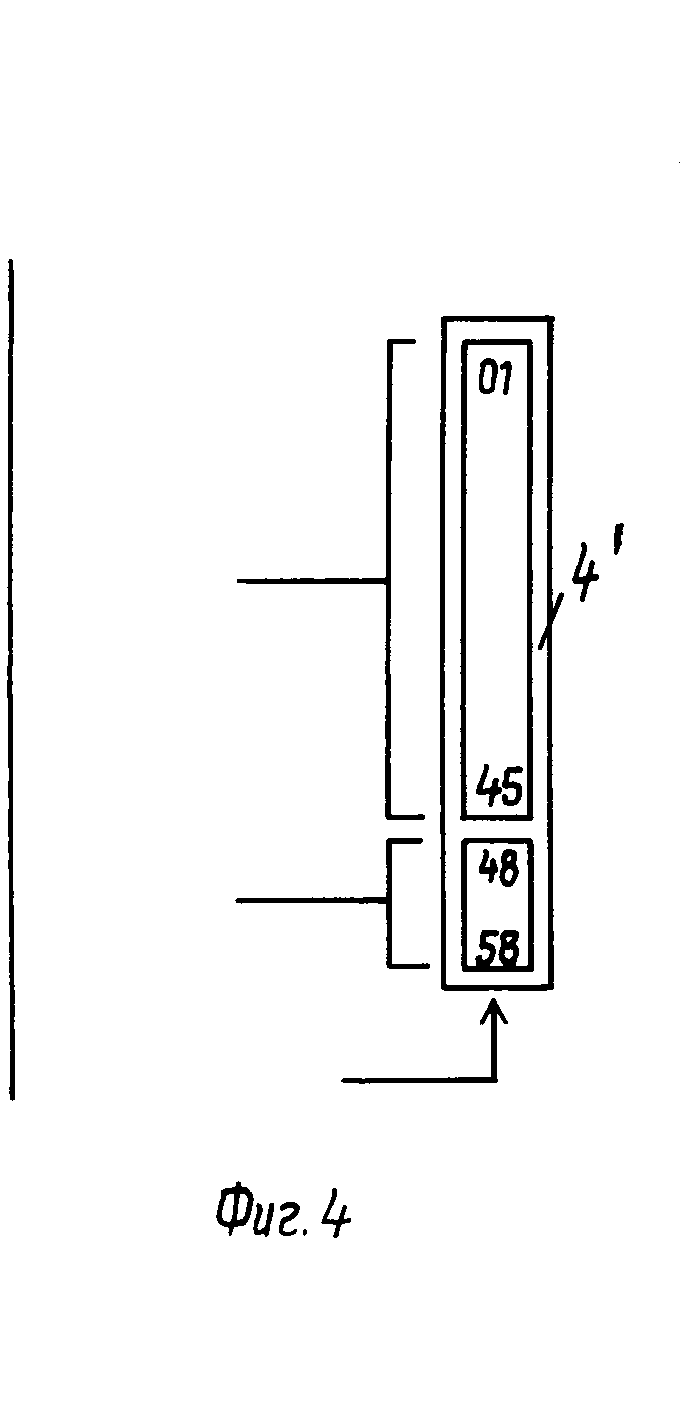

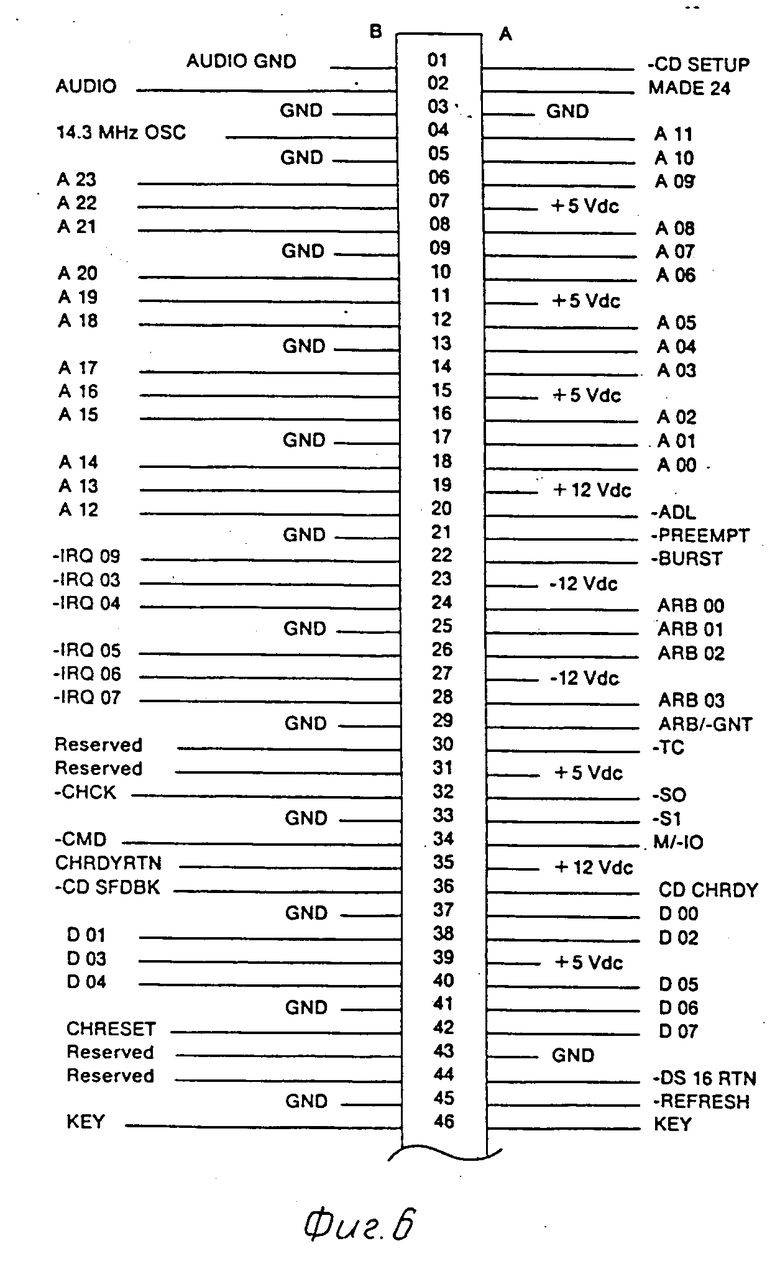

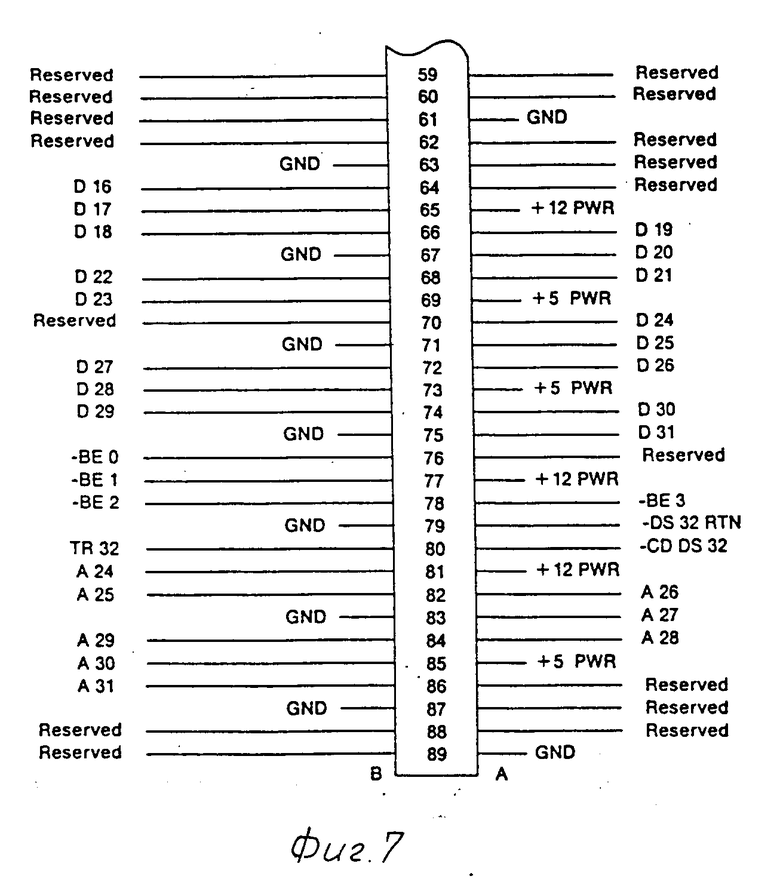

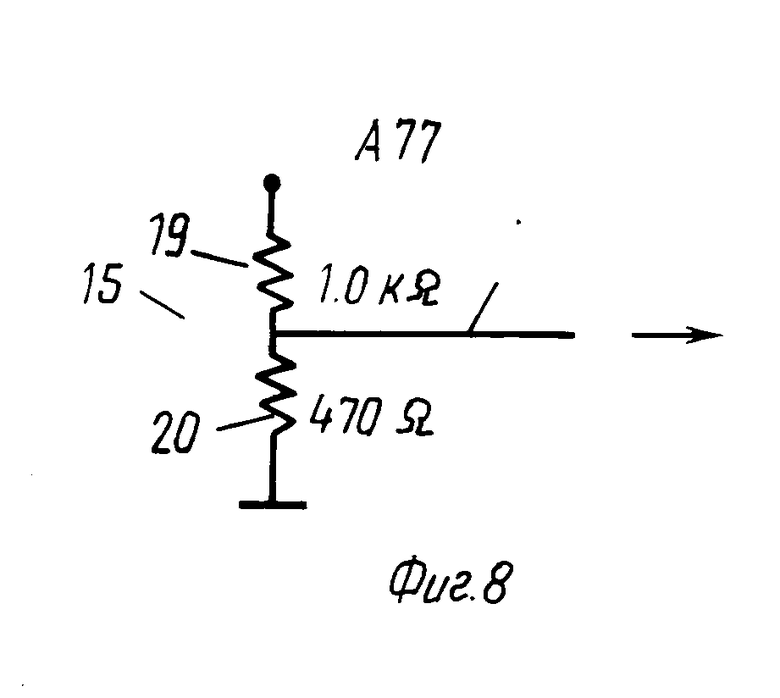

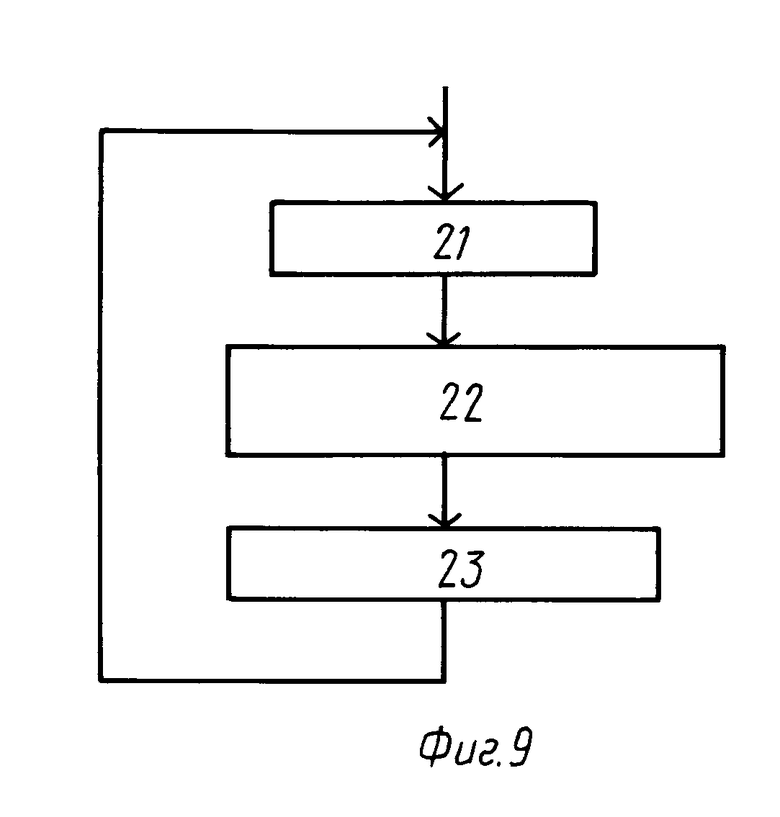

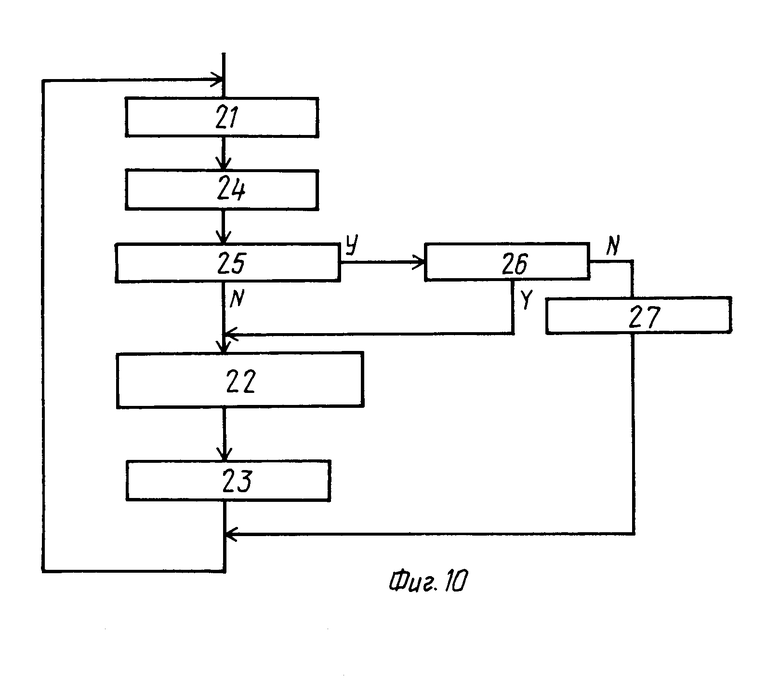

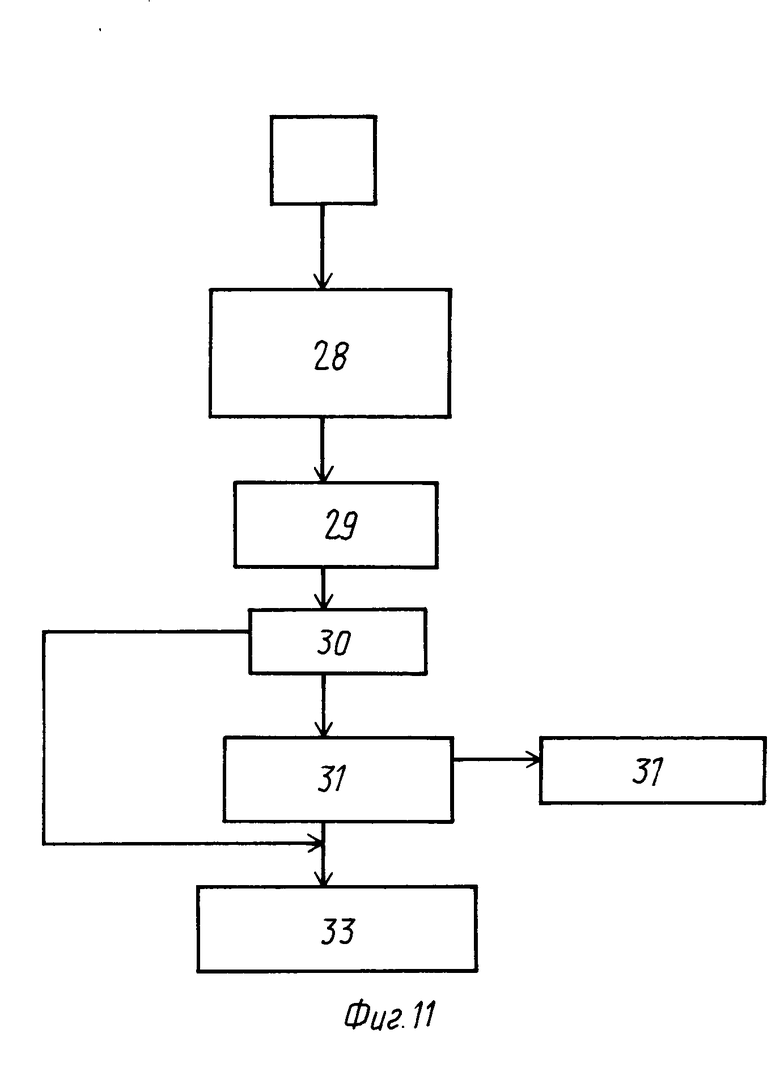

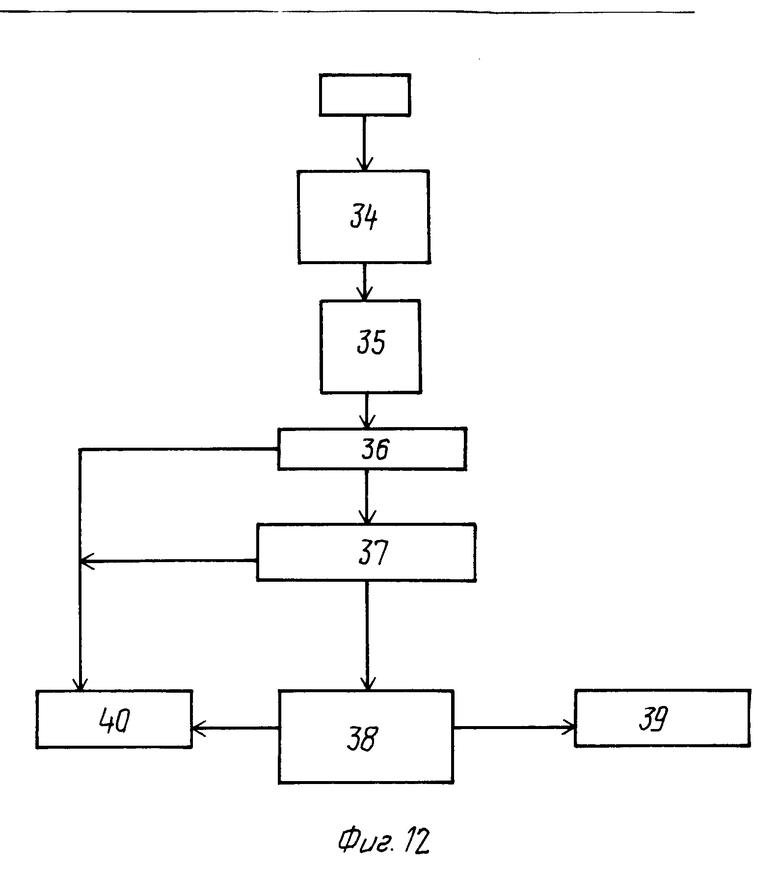

На фиг. 1 показана структурная схема, показывающая элементы базисной системы, соединенные с предпочтительной в настоящее время реализацией для платы расширения, в которой логическая часть, распознающая команды, может быть реализована программируемым локальным процессором; на фиг. 2 - схематическое изображение платы расширения, ориентированной, чтобы вставляться в гнездо, имеющее разъем с полным набором контактов, для которого рассчитана данная плата; на фиг. 3 - схематическое изображение платы расширения, ориентированной, чтобы вставляться в гнездо, в котором часть контактов разъема не зацепляет контакты разъема системы; на фиг. 4 и 5 - упрощенные схематические изображения 16-битового и 32-битового разъемов соответственно; на фиг. 6 и 7 - схематическое изображение назначений штырьков разъема для 16-битовой ширины шины, согласно микроканальной фирменной архитектуре, применяемой а персональных ЭВМ марки PS/2 фирмы ИВМ; на фиг. 8 - схематическое изображение предпочтительной реализации для блока идентификации; на фиг. 9 - структурная схема алгоритма обработки команд для платы расширения; на фиг. 10 - схема алгоритма, соответствующая фиг. 8, но включающая проверку команд, согласно предпочтительной реализации этого изобретения, чтобы блокировать выполнение команд, которые не могут исполняться надлежащим образом; на фиг. 11 - схема алгоритма для реализации универсальным процессором проверки определенных типов невыполнимых команд, полученных от базисной системы; на фиг. 12 - детализированная схема алгоритма идентификации невыполнимых команд, принятых от базисного процессора.

Плата расширения I показана (фиг. 1) соединенной с базисной системой 2 разъемом платы 3, который соединяется с разъемом системы 4, чтобы принимать сигналы и питание от шины системы 5. Базисная система 2 включает центральый процессор 6 и системную память 7, соединенные с шиной системы 5, как представляется типичным для таких систем, как вычислительные машины марки "Персональная Система/2" фирмы ИБМ.

Сигналы от разъема платы 3 принимаются на регистрах интерфейса 8, с которых делается выборка локальным процессором 9 через локальную шину 10. Системная память 11 и суперпозиционные драйверы 12 также соединяются с локальной шиной 10 и могут рассматриваться вместе с локальным процессором 9 и системной памятью 11 в качестве части расширительного устройства 13. Суперпозиционые драйверы 12 могут меняться от платы к плате и могли бы, например, управлять внешними устройствами 14, такими как накопители на дисках, согласующимися с интерфейсом системы с малой вычислительной машиной. Блок идентификации 15 соединяется с разъемом платы 3 согласно предпочтительной реализации для этого изобретения и обеспечивает сигнал к локальной шине 10.

Рассмотрим фиг. 2, плата расширения 1 показывается включающей панель 16 из недеформируемого материала для монтажных плат. Отдельные контакты 17 разъема платы 3 располагаются в предварительно выбранных разнесенных друг от друга на некоторое расстояние положениях на любой стороне панели 16 (меньшее, чем предпочтительное число контактов, показано для ясности иллюстрации). Разъем системы 4 монтируется на плоской монтажной плате 18 и ему придается конфигурация контактами (не показана) для соприкосновения с контактами 17 по длине разъема платы 3 и служит для того, чтобы определять принимающее гнездо 19. Разъем платы представляет, предпочтительно, вкладышевый (вилочный) краевой разъем платы, а разъем системы тогда должен представлять гнездовой (розеточный) краевой разъем платы, фиг. 3 показывает сокращенный разъем системы 4 .

На фиг. 4 и 5 показаны положения контактов для типовых разъемов 4 и 4, поддерживающих 16-битовые и 32-битовые операции соответственно. Фиг. 6 и 7 показаны назначения для контактов разъема 3 системой шины 5 (см. фиг. 1), согласующиеся со спецификацией микроканальной шины с обозначениями А и Д, показывающими позиции адреса и данных соответственно. Дополнительное описание, касающееся такой системы, может быть найдено в руководстве Техническое обращение с интерфейсом аппаратных средств персональнной системы PS/2.

На фиг. 8 изображен блок идентификации 15, который соединяется с отдельным контактом разъема 3, обозначенным А77 на фиг. 7, который не зацепляется 16-битовым разъемом системы 4 (см. фиг. 3), однако мог бы контактировать с 12-вольтовым источником постоянного напряжения через 32-битовый разъем 4 (см. фиг. 2). Резисторы 19 и 20 действуют в качестве делителя напряжения, чтобы образовывать логический сигнал на отводном соединении, которое подает сигнал в качестве управляющего сигнала к порту ввода для процессора 9 (фиг. 1) через локальную шину 10.

Нормальная последовательность операций для исполнения команд, представленных базисной системой 2 (см. фиг. 1), показана на фиг. 9. Этот алгоритм, предпочтительно, реализуется использованием программируемого процессора 9 (см. фиг. 1), который, например, может представлять процессор модели "Интел-8032". Первоначально команда выбирается блоком 21 из регистров 8. Затем обрабатывается команда (блоком 22), которая могла бы подготавливаться разработчиком в соответствии с функцией конкретной платы 1. Затем блок 23 должен завершать цикл обработки и подготавливать следующую команду.

Фиг. 10 показывает изменения в алгоритме, показанные на фиг. 9, согласно предпочтительной в настоящее время реализации для данного изобретения. После выборки команды согласно блоку 21 все адреса ячеек памяти, которые эта команда требует, чтобы они были представлены на шине 5 (см. фиг. 1), извлекаются (блок 24) и проверяются, чтобы определять, не превышают ли они 16-мегобайтовый предел для 16-битовой адресации (блок 25). Если да, то логический блок 26 проверяет сигнал "Большой разъем", представленный блоком идентификации 15, чтобы определять, не превышает ли данный адрес пределов адресации данного разъема. Следовательно, только в том случае, если адрес превышает предел разъема, согласно предпочтительной в настоящее время реализации этого изобретения, эта плата блокирует команду, пользуясь блоком 27.

На фиг. 11 изображен алгоритм обработки команд в блоке управления, который начинается с приема адреса для обращения к управляющему блоку (блок 28). Уровень сигнала "БОЛЬШОЙ РАЗЪЕМ" выбирается в блоке 29 и проверяется в блоке 30. Если разъем ограничивает адресацию, то адрес управляющего блока проверяется в блоке 31, если таковой превышает интервал, базисной системе 2 посылается сообщение об ошибке логической частью 32. В противном случае логическая часть 33 выбирает управляющий блок.

На фиг. 12 показана дополнительная часть алгоритма, чтобы дополнять алгоритм, показанный на фиг. 11. В блоке 34 команда принимается в память 11. Сигнал "БОЛЬШОЙ РАЗЪЕМ" считывается в блоке 35 и, если он дает индикацию ограниченного сегмента блоку 36 для адресации, эта команда проверяется в блоке 37, чтобы определить, является ли эта команда требующей одну или более операций обращения к памяти. Если да, то эти адреса проверяются в блоке 38 для определения, не превышают ли они предел разъема. Если какие-либо адреса будут превышать предел разъема, то сообщение об ошибках посылается базисной системе 2 блоком 39, в противном случае эта команда исполняется блоком 40.

Хотя только определенные предпочтительные признаки этого изобретения были показаны методом иллюстрации, многие модификации и изменения будут представляться специалистам в данной области техники. Поэтому, следует понимать, что настоящие пункты формулы изобретения предназначаются, чтобы охватывать все такие модификации и изменения, которые попадают в пределы истинной сущности данного изобретения. (56) Компьютер 1ВМ PS/2 мод. 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ПРЯМОГО ДОСТУПА (DASD) ЕМКОСТЬЮ БОЛЬШЕ 528 МЕГАБАЙТ И СПОСОБ ЕГО ВОПЛОЩЕНИЯ ДЛЯ ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ | 1994 |

|

RU2155369C2 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИНИЦИАЛИЗАЦИИ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1992 |

|

RU2155376C2 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2072553C1 |

| ТРАНСФОРМАЦИЯ ПРЕРЫВИСТЫХ СПЕЦИФИКАТОРОВ КОМАНД В НЕПРЕРЫВНЫЕ СПЕЦИФИКАТОРЫ КОМАНД | 2012 |

|

RU2568241C2 |

| СПОСОБ ГЕНЕРИРОВАНИЯ ДАННЫХ ИЗОБРАЖЕНИЯ | 1991 |

|

RU2113770C1 |

| ЦИФРОВОЙ КОМПЬЮТЕР С ВОЗМОЖНОСТЬЮ ПАРАЛЛЕЛЬНОГО ВЫПОЛНЕНИЯ ДВУХ И БОЛЕЕ КОМАНД | 1991 |

|

RU2109333C1 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

| УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ ОРГАНИЗАЦИИ ДОСТУПА К ОБЩЕЙ ШИНЕ ВО ВРЕМЯ ПЕРЕДАЧИ ДАННЫХ С ПРЯМЫМ ДОСТУПОМ К ПАМЯТИ | 1991 |

|

RU2110838C1 |

Использование: сменная плата расширения для системы вычислительных машин имеет специальные схемы, чтобы позволять плате самой приспосабливаться к техническим характеристикам отдельного разъема, в который она вставляется. Вычислительные машины, предназначенные для индивидуального использования или использования в малых сетях, обеспечивают разъемы для подключения, чтобы позволять платам расширения, добавляться и соединяться с шиной вычислительной машины для добавления новой функции или возможности. Целью изобретения является создание платы расширения, которая адаптируется к ширине разъма. Плата содержит разъем и дополнительную плату, в которую введен блок идентификации, соединенный с одним из контактов платы, входящим в зацепление с контактом разъема, соединенным с источником питания, в случае 32-разрядной шины системы, и не входящим в контакт в случае 16-разрядной шины. 1 з. п. ф-лы, 12 ил.

Авторы

Даты

1994-03-15—Публикация

1990-06-11—Подача