Изобретение относится к устройству для управления передачами данных через неспециализированную шину между запоминающим устройством или совокупностью каналов связи (включая процессоры) как по отдельности, так и в совокупности и, более конкретно, к средствам, включаемым в состав такового, чтобы разрешать конфликты на основе приоритетов между такими устройствами более эффективно, посредством исключения бесполезно отработавших циклов разрешения конфликтов (арбитражных циклов) и больших пакетных буферных устройств, и делать всю пропускную способность доступной для передачи данных.

Приложение по микроканальной архитектуре фирмы IBM к техническому справочному материалу для интерфейса аппаратного оборудования персональной вычислительной системы P S/2, опубликованное в ноябре 1989 года, описывает канальную архитектуру, которая широко используется в настоящее время, где на с. 30-33 раскрыта пакетная передача и локальное разрешение конфликтных ситуаций, а также приоритетное прерывание обслуживания между устройствами управления передачей данных по шине. Этот и другие используемые в настоящее время способы и средства для разрешения конфликтных ситуаций относительно доступа к шине канала связи для непосредственного доступа к запоминающему устройству требуют целый ряд циклов, чтобы разрешать конфликты на основе приоритетов между многочисленными внешними устройствами, чтобы определить победителя. Это укорачивает время, доступное для передачи данных.

В известных вычислительных системах не обеспечивается какая-либо возможность предоставления управления шиной в течение этих циклов разрешения конфликтных ситуаций. Эти циклы разрешения конфликтных ситуаций составляют непроизводительные издержки, которые снижают доступность к пропускной способности. Чтобы сократить эти непроизводительные издержки в известных вычислительных системах, предпринималась попытка группировать передачи данных в пакеты обращенных в противоположные стороны (то есть, следующих один за другим, непрерываемых) циклов. Однако это нежелательно, поскольку требует дополнительных аппаратных средств в виде больших буферных запоминающих устройств и их схем управления, работа которых должна прерываться с переменными интервалами так, чтобы не выходить за границы памяти других передающих устройств, работающих в режиме прямого доступа и обладающих более высоким приоритетом, которым должно разрешаться приоритетное прерывание обслуживания. Для того чтобы избежать захвата шины внешним каналом связи были разработаны сложные алгоритмы равнодоступности, которые еще в большей степени усложняют логику и, следовательно, не решают задачу.

Ни одно из решений известного уровня техники не раскрывает устройство, которое оптимизирует разрешение конфликтных ситуаций доступа к общей шине между многочисленными внешними каналами связи, посредством использования минимума арбитражной логики, которая [1] исключает большие пакетные буферные запоминающие устройства и бесполезно отработавшие циклы разрешения конфликтных ситуаций (арбитражные циклы), [2] позволяет передачу данных в мультиплексированном непрерывном последовательном потоке от различных внешних каналов связи, и еще [3], подобно известному уровню техники, позволяет приоритетам соответствующих внешних каналов связи изменяться динамически.

Известно устройство для оптимизации организации доступа к общей шине во время передачи данных с прямым доступом к памяти (Шевкопляс Б.В, Микропроцессорные структуры. -М.: Радио и связь, 1986, с. 152, рис. 8.6), выбранное за прототип, и которое как и заявленное содержит центральный процессор, блок оперативной памяти, не менее двух внешних каналов связи, входы - выходы которых подключены к системной шине устройства, связанной с выходом генератора.

Для исключения недостатков известного уровня техники заявленное устройство для оптимизации организации доступа к общей шине во время передачи данных с прямым доступом к памяти отличается тем, что каждый из внешних каналов связи содержит первый инвертор, вход которого связан с выходом генератора через системную шину, второй инвертор, вход которого соединен с выходом первого инвертора, выход второго инвертора соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора через системную шину, выход первого элемента И соединен с входом первого элемента ИЛИ-НЕ, выход которого соединен с входом первого буферного драйвера, и первым входом второго элемента И, второй вход которого соединен с выходом первого инвертора, выход второго элемента И соединен с первым входом второго элемента ИЛИ-НЕ, выход которого соединен с входом второго буферного драйвера.

В заявленном устройстве каждый из внешних каналов связи содержит первый триггер, первый вход которого соединен с выходом первого буферного драйвера и первым входом третьего триггера, второй вход первого триггера подключен к линии запросов считывания-записи внешних каналов связи, первый вход второго триггера соединен с выходом второго буферного драйвера, второй вход третьего триггера соединен с выходом элемента И-ИЛИ-НЕ, первый вход которого соединен с выходом второго триггера, первый вход четвертого триггера соединен с выходом второго буферного драйвера, прямой выход третьего триггера соединен с вторым входом четвертого триггера, выход которого соединен с вторым входом пятого триггера, первый вход которого соединен с выходом первого буферного драйвера, выход первого триггера соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом нулевого инвертирующего драйвера, вход которого является входом логического нуля устройства, выход первого элемента ИЛИ-НЕ соединен с входом первого инвертора и с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом второго инвертора, вход которого соединен с выходом второго инвертирующего драйвера, вход которого является входом логического нуля устройства, выходы первых инвертора и элемента И-НЕ соединены входами первого и третьего инвертирующих драйверов соответственно, выход первого элемента И-НЕ соединен с вторым входом второго триггера, выходы инвертирующего драйвера с нулевого по четвертый через монтажное ИЛИ соединены с арбитражной шиной устройства, вход продолжения собственной работы устройства и инверсный выход третьего триггера соединены соответственно с первым и вторым входами второго элемента И-НЕ, выход которого соединен с вторым входом шестого триггера и входом четвертого инвертирующего драйвера, выход которого соединен с вторым входом седьмого триггера, выход которого соединен с вторым входом элемента И-ИЛИ-НЕ, первый вход второго триггера соединен с первыми входами шестого и седьмого триггеров, выход шестого триггера соединен с третьим входом элемента И-ИЛИ-НЕ, выход пятого триггера является выходом управления устройства.

В заявленном устройстве каждое из внешних устройств содержит четырехбитный регистр, прямые выходы первого и второго разрядов которого соединены с первым и вторым входами первого элемента И-ИЛИ-НЕ, выход которого соединен с первыми входами второго, третьего, четвертого и пятого элементов И-НЕ, входы положительного и отрицательного запросов устройства соединены с пятым входом первого элемента И-ИЛИ-НЕ и первым входом первого элемента И-НЕ соответственно, второй вход которого соединен с инверсным выходом первого разряда четырехбитного регистра, инверсные выходы второго, третьего и четвертого разрядов которого соединены с вторыми входами второго, третьего и четвертого элементов И-НЕ соответственно, выходы элементов И-НЕ с первого по четвертый соединены с входами инвертирующих драйверов с первого по четвертый соответственно, выходы которых объединены через арбитражную шину устройства, выходы первого и второго инвертирующих драйверов соединены соответственно с третьим и четвертым входами первого элемента И-ИЛИ-НЕ, прямые выходы третьего и четвертого разрядов четырехбитных регистров соединены с первым и вторым входами второго элемента И-ИЛИ-НЕ, третий и четвертый входы которого соединены с выходами третьего и четвертого инвертирующих драйверов, выход второго элемента И-ИЛИ-НЕ соединен с третьим входом четвертого и вторым входом пятого элементов И-НЕ, выход которого является выходом переменного приоритера устройства.

В заявленном устройстве исключаются циклы ожидания разрешения конфликтных ситуаций и задержка пакетного режима. Протокол сопряжения с общей шиной упрощается устранением необходимости использования буферных устройств образования потока данных и арбитражной логики, которые требовались ранее. Внешние каналы связи знают заранее, когда будет предоставляться доступ к шине, позволяя ускоренную работу в конвейеризованном режиме. Также, поскольку самым высокоприоритетным запрашивающим устройствам будет всегда предоставляться владение шиной в последовательности до тех пор, пока не будут обслужены все устройства, проблемы захвата и равнодоступности автоматически разрешаются на основе приоритета, потому что длинные пакетные передачи уже не требуются.

Эти преимущества достигаются обеспечением по меньшей мере двух неперекрывающихся тактовых импульсов на цикл передачи и по меньшей мере одного цикла передачи на цикл разрешения конфликтов. Запросы разрешения конфликтов на основе приоритета от каждого внешнего канала связи передаются арбитражной шине только при нарастании первого из тактовых импульсов. Код приоритета внешнего канала связи с самым высоким приоритетом определяется в конце последнего из тактовых импульсов. Коды приоритета могут быть фиксированными или динамически изменяться.

Настоящее изобретение может быть реализовано: (a) с адресной шиной и двунаправленной шиной данных; или (b) для ускоренного конвейерного режима, с однонаправленной выходной шиной для адресов и данных в полупериодных промежутках времени, причем с шиной данных, которая является только входящей однонаправленной; или (c) с одной неспециализированной двунаправленной шиной, причем с адресами, которые посылаются только однажды в начале длинной передачи и во время последующих циклов передачи данных инкрементируются последовательно до тех пор, пока не будет посылаться новый непоследовательный адрес.

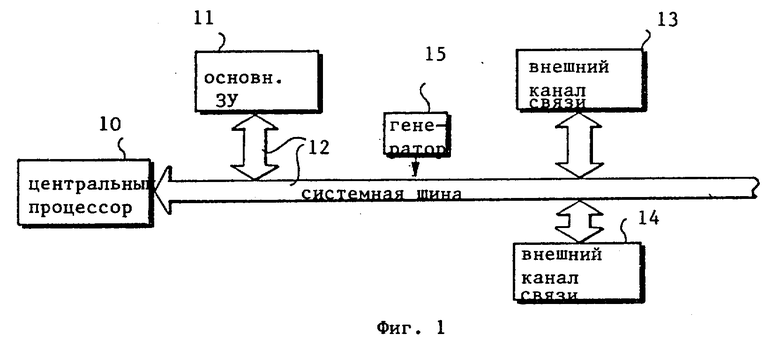

На фиг. 1 - блок-схема устройства управления шиной вычислительной машины, согласно настоящему изобретению.

На фиг. 2 - принципиальная схема компоновки схем, связанных с каждым внешним устройством, для генерирования двух циклов неперекрывающихся тактовых импульсов от одного источника для реализации настоящего изобретения.

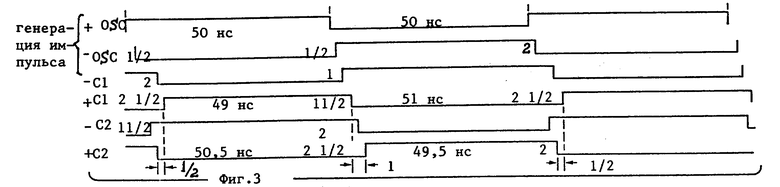

На фиг. 3 - временная диаграмма, показывающая циклы неперекрывающихся тактовых импульсов, генерируемые компоновкой схем, по фиг. 2.

На фиг. 4 - принципиальная схема компоновки схем разрешения конфликтов, которая предоставляет устройство управления передачей данных по шине в конце последнего из упомянутых циклов тактовых импульсов согласно фиксированному приоритету, иллюстративно предполагаемое в качестве "5" (0101).

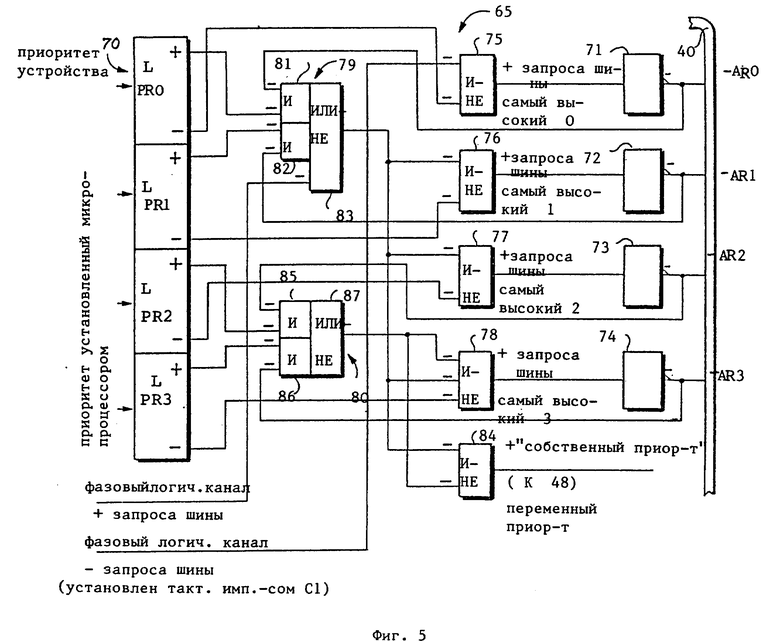

На фиг. 5 - принципиальная схема, которая может быть использована в части компоновки, показанной на фиг. 4, чтобы обеспечивать компоновку схем, которая предоставляет устройство управления передачей данных по шине в конце последнего из упомянутых циклов тактовых импульсов согласно приоритету, который может устанавливаться динамически.

На фиг. 6 - временная диаграмма, иллюстрирующая конвейерную обработку запросов шины, предоставлений шины, адресов, передач данных и блокировок, чтобы обеспечивать последовательный пакет или поток операций считывания/записи.

Как показано на фиг. 1, устройство согласно настоящему изобретению содержит центральный процессор (ЦП) 10, который сообщается через системную шину 12 с основным запоминающим устройством 11 и совокупностью внешних каналов связи, таких как 13 и 14. Термин "внешние каналы связи" в контексте настоящего описания обозначает другие центральные процессоры и периферийные устройства, такие как дисковые файлы, печатающие устройства и т.п. Источник сигналов, такой как генератор 15, обеспечивает сигналы прямоугольной формы к каждому внешнему устройству. Как иллюстрировано, генератор 15 является отдельным от центрального процессора, однако если предпочитается, его обеспечивающая сигналы функция может восполняться центральным процессором.

Следует отметить, что согласно одному из вариантов воплощения изобретения не требуется никакого контроллера шины или контроллера прямого доступа к памяти.

Как показано на фиг. 2, каждый внешний канал связи 13 и 14 включает пару инверторов 20 и 21 и пару буферных драйверов 22 и 23. Когда генератор 15 генерирует положительный сигнал, он обусловливает нарастание сигнала в линии 24. Этот сигнал подается непосредственно к элементу И 25 и также к упомянутому элементу И, будучи инвертированным и затем реинвертированным инверторами 20 и 21, чтобы обеспечивать временную задержку. В конце этой временной задержки сигнал, прошедший элемент И 25, инвертируется элементом ИЛИ-НЕ 26 и заставляет буферный драйвер 22 возбуждать положительный тактовый импульс C1. Между тем, выходной сигнал элемента ИЛИ 26 будет подвергаться операции И в позиции 27 с до некоторой степени задержанным выходным сигналом от инвертора 20 и заставляет элемент ИЛИ 28 инвертировать этот сигнал, а буферный драйвер 23 - возбуждать положительный тактовый импульс C2. Элементы 25 и 26 идентичны элементам 27 и 28.

Синхронизация положительных и отрицательных циклов соответствующих тактовых импульсов C1 и C2 показана на фиг. 3. Тактовые импульсы C1 и C2 являются сдвинутыми по фазе на 180o. Однако согласно одному из вариантов воплощения изобретения, благодаря задержке через инвертор 21, длина цикла тактового импульса C1 является несколько короче тактового импульса C2, чтобы приводить в непрерывное состояние циклы тактовых импульсов. Например, полагая что длительность цикла генератора 15 составляет 100 наносекунд (нс), тогда длительность фазы положительного тактового импульса C1 составляет 49 нс, основанная на задержке 2 1/2 нс от переднего фронта и задержке 1 1/2 нс, добавленной к заднему фронту, и это обеспечивает в результате длительность фазы порядка 51 нс для отрицательного тактового импульса C1. Однако положительный тактовый импульс C2 имеет слегка большую длительность фазы порядка 49,5 нс, основанную на задержке 2 1/2 нс от переднего фронта и задержке 2 нс, добавляемой к заднему фронту, что обеспечивает в результате длительность фазы порядка 50,5 нс для отрицательного тактового импульса C2.

Пунктирные линии 29, 30 и 31 (фиг. 2) представляют соединения, которые, предпочтительно, выполняют для целей диагностического тестирования и обычно являются недействующими; они приведены на фиг. 2 лишь для завершенности схемы. Отрицательный сигнал на линии 29 будет подавлять тактовый импульс C1, обеспечивая в результате такое состояние, когда только тактовый импульс C2 является активизируемым. Аналогично, отрицательный сигнал на линии 30 будет подавлять тактовый импульс C2, обеспечивая в результате такое состояние, когда только тактовый импульс C1 является активизируемым. Положительный сигнал на линии 31 будет согласовывать инвертирующие элементы ИЛИ-НЕ 26 и 28 так, чтобы поддерживать оба тактовых импульса C1 и C2 непрерывно положительными.

Согласно другому варианту изобретения каждый внешний канал связи 13 и 14 знает в одинаковое предварительно выбранное время в самом начале цикла, а именно, при нарастании первого тактового импульса C1, когда оно должно становиться устройством управления передачей данных по шине "хозяином" шины. Запросы на разрешение конфликтных ситуаций могут изменяться только на кодированной арбитражной шине 40 (фиг. 4) при нарастании тактового импульса C1, и после этого будут являться стабильными для предоставления устройства управления для передачи данных по шине при спадании последнего тактового импульса C2.

Как показано на фиг. 4, линии AR0, AR1, AR2, AR3 и -Lock (-Блокировка), через точечное монтажное ИЛИ, соединяются с арбитражной шиной 40. Любой внешний канал связи 13 и 14, который желает получить доступ к шине 12, записывает его запрос на Считывание или Запись в триггер, устанавливаемый в состояние "1" тактовым импульсом C2. Этот запрос пропускается через триггер, запоминающий полярность сигнала запроса собственной шины 41, тактируемую тактовым импульсом C1. Триггер 41 имеет положительный выходной сигнал, который подается к схеме 42. Если не имеется никакого более высокого приоритета на арбитражной шине 40, уровень AR0 является положительным и элемент ИЛИ 42 выполняет функцию инвертора, который обеспечивает отрицательный выходной сигнал. Этот выходной сигнал инвертируется в элементе 43 и становится положительным запросом шины с наивысшим приоритетом 1. Этот запрос инвертируется инвертирующим драйвером 44, устанавливающим отрицательный уровень AR1 на арбитражной шине 40. Этот запрос, вместе с запросом шины наивысшего приоритета 3, будет пропускаться через шину и запрашивающее устройство 13 или 14 будет становиться "хозяином" шины.

Если другое устройство на арбитражной шине 40 имеет наивысший уровень AR0 активизируемым, сигнал в линии AR0 от шины к инвертирующему элементу ИЛИ-НЕ 42 будет являться отрицательным, обеспечивая в результате положительный выходной сигнал от схемы 42, который блокирует любой выходной сигнал от запросов шины на линиях AR1 и AR3. Положительный выходной сигнал от схемы 42 будет также заставлять инвертирующий элемент И-НЕ 45 блокировать любое прохождение через нее запросов к ответвлению AR3 арбитражной шины 40.

Как показано на фиг. 4, приоритет установлен на 5. Следовательно, для кода 5 собственный приоритет в четырехразрядном двоичном коде представляют биты AR1 и AR3, причем AR3 представляет самый младший двоичный разряд.

Если бит AR2 более высокого приоритета от внешнего канала связи является активизируемым, он будет инвертироваться в элементе 46 и изменять полярность на входном сигнале к инвертирующему элементу И-НЕ 45 на положительную. Если любой один из этих входных сигналов к инвертирующему элементу И-НЕ 45 является положительным, выходной сигнал упомянутой схемы будет являться отрицательным и в таком случае через инвертирующий драйвер 47 никакого отрицательного выходного сигнала не может появиться на AR3.

Если не имеется никакого запроса приоритета на AR0 или AR2 от любых других внешних каналов связи, оба входных сигнала к инвертирующему элементу И-НЕ 45 будут являться отрицательными. Тогда выходной сигнал схемы 45 будет представлять выходной сигнал запроса шины наивысшего приоритета 3 положительным. Этот выходной сигнал инвертируется инвертирующим драйвером 47 и появляется в качестве отрицательного активизируемого выходного сигнала на AR3. Выходной сигнал инвертирующего элемента И-НЕ 45 (который в этом случае представляет запрос шины наивысшего приоритета 3) является также декодером своего собственного приоритета и предварительно согласует триггер 48, запоминающий полярность сигнала собственного приоритета, в течение тактового импульса C2. Триггер 48 будет фиксировать данные согласно состоянию в конце тактового импульса C2.

Согласно одному из вариантов реализации изобретения, после того как фиксируется триггер собственного приоритета 48, он может устанавливать триггер 49, запоминающий полярность сигнала предоставления собственной шины, на следующий цикл для предоставления следующего цикла. Выходной сигнал триггера собственного приоритета 48 проходит через элемент И 50 и инвертируется инвертирующим элементом ИЛИ-НЕ 51 и будет фиксироваться триггером предоставления собственной шины 49 в начале тактового импульса C1. Это подает сигнал конкретному устройству, кто является "хозяином" шины в течение этого цикла.

Предшествующее устройство, которое являлось "хозяином" шины перед определением этого приоритета, может продолжить его цикл даже если триггер собственного приоритета (подобный триггеру 48) другого внешнего устройства находился в защелкнутом состоянии. Это задерживает следующий цикл до тех пор, пока предшествующий "хозяин" шины не освободит шину 12. Функция задержки управляется вторым входным сигналом к элементу И 50, который представляет выходной сигнал триггера 52, запоминающего полярность сигнала любой блокировки. Триггер 52 будет приводиться в состояние фиксации данных предшествующим тактовым импульсом C2 от сигнала -Lock(-Блокировка) на шине 40. Задержка может иметь место в течение любого числа циклов тактового импульса C2.

Как только продолженные циклы становятся завершенными, сигнал - блокировка будет освобождаться предшествующим "хозяином" шины во время тактового импульса C1. Это будет позволять триггеру 49 возможность предоставления собственной шине продолжать работать в конвейеризированном режиме при следующем тактовом импульсе C1, контролируемом триггером любой блокировки 52, освобождающейся при тактовом импульсе C2, при условии если тем временем не принимаются запросы более высокого приоритета, чтобы делать приоритетное прерывание текущего арбитражного приоритета.

Предположим, что некоторое устройство имеет желание получить два или более циклов в последовательности из-за медленного подчиненного приемника, или потому что оно хочет работать в пакетном режиме. Это устройство будет фиксировать его в триггере 53, запоминающем полярность сигнала собственной блокировки при тактовом импульсе C2, через инвертирующий элемент И-НЕ 54. Запрос собственного продолжения должен устанавливаться тактовым импульсом C1 в другом триггере (не показан), который также появляется в инвертирующем элементе И-НЕ 54. Тот же самый выходной сигнал инвертирующего элемента И-НЕ 54 через инвертирующий драйвер 55 устанавливает в состояние "1" триггер собственной блокировки 52 и также возбуждает общий сигнал - Блокировка на арбитражной шине 40. Пока регистр-триггер собственной блокировки остается установленным в состояние "1", его положительный выходной сигнал будет подвергаться операции ИЛИ в инвертирующем элементе ИЛИ-НЕ 51, чтобы удерживать в включенном состоянии триггер предоставления собственной шины 49 в течение многих циклов. Снова, после того как завершается продолженный цикл, триггер собственной блокировки 53 будет устанавливаться в состояние "0" тактовым импульсом C2 и триггер предоставления собственной шины 49 будет устанавливаться в состояние "0" тактовым импульсом C1. Это дает возможность снятия сигнала-Блокировка. Теперь все внешние каналы связи будут свободно продолжать последовательные передачи данных.

Инвертирующие драйверы 56 и 57 являются внутренне неактивными, и их входные сигналы отводятся к заземлению, так как они не вовлекаются в образование кода приоритета 0101, однако они остаются активизируемыми внешними входными сигналами от шины 40.

Синхронизация с конвейерной организацией для управления пропусканием данных на шину 12 получается установкой положительного выходного сигнала от триггера предоставления собственной шины 49 к триггеру задерживаемого предоставления собственной шины 58 при тактовом импульсе C2 и установкой выходного сигнала триггера 58 к триггеру передачи собственных данных 59 при тактовом импульсе C1. Выходной сигнал от триггера 59 представляет синхронизирующий сигнал, который управляет пропусканием данных к шине 12 и от этой шины.

Фиг. 5 изображает компоновку схем, которая может заменять компоновку схем 65 (заключенную в прерывистые линии на фиг. 4), чтобы обеспечивать возможность динамического изменения кода приоритета. Четырехразрядный код приоритета, который обеспечивает вплоть до 16 различных приоритетов, устанавливается в регистр 70 в начале операции, такой как во время начальной загрузки программы (НЗП). Эта компоновка схем 65 включает четыре инвертирующих драйвера 71, 72, 73 и 74. Эти драйверы представляют собой драйверы с открытым коллектором или драйверы прямоугольных импульсов. Они устанавливают арбитражные биты AR0, AR1, AR2 и AR3, вводимые элементами И 75, 76, 77 и 78 соответственно. Эти элементы И определяют самый высокий приоритет посредством двух элементов сложной логики 79 и 80, которые представляют собой фактически отдельные схемы.

Элемент 79 содержит два элемента И 81 и 82 и трехходовой инвертирующий элемент ИЛИ-НЕ 83. Инвертирующий ИЛИ-НЕ 83 запрещает работу всех линий пониженного запроса AR1, AR2 и AR3. Элемент 83 также запрещает работу схемы собственного приоритета 84, если более высокий приоритет является внешне действующим на арбитражной шине 40. Если AR0 является активизируемой, а выходной сигнал триггера PR0, запоминающей полярность сигнала, не находится в таком состоянии, вентиль И 81 через инвертирующую схему ИЛИ 83 будет запрещать AR1, AR2 и AR3 и сигналы собственного приоритета.

Аналогично и с элементом И 82, если AR1 является активизируемой, а триггер PR1, запоминающий полярность сигнала, не находится в таком состоянии, тогда AR1, AR2, AR3 и сигналы собственного приоритета будут запрещаться, после чего операция разрешения конфликтных ситуаций будет препятствовать работе устройства в том, чтобы оно было следующим, которое должно обслуживаться.

Последний входной сигнал к инвертирующему элементу 83 представляет собой выходной сигнал триггера, запоминающего полярность сигнала запроса шины (не показан), которая устанавливается в состояние "1" тактовым импульсом C1, и запрашивает арбитражный цикл для передачи данных. Линия триггера, запоминающего полярность сигнала + запроса шины, будет являться отрицательной, если она не является активизированной. Это будет автоматически запрещать работу всех блоков 76, 77, 78 и 84. Когда выходной сигнал инвертирующего элемента И-НЕ 84 является положительным, таковой индицирует, что это устройство в текущий момент является устройством самого высокого приоритета, которое победило в разрешении конфликтной ситуации и может начинать передачу в следующей далее последовательности циклов.

Элемент сложной логики 80 содержит элементы И 85 и 86, которые работают аналогично элементам 81 и 82, за исключением того, что они имеют дело с двумя более младшими битами AR2 и AR3 арбитражной шины. Также, инвертирующий элемент ИЛИ-НЕ 87 имеет одинаковую функцию, что и схема 83 относительно этих более младших двух двоичных разрядов, однако эта схема не требует соединения триггера, запоминающего полярность сигнала + запроса шины не показан потому что выходной сигнал уже управляется схемой 83, выходной сигнал которой уже подается ко всем элементам 76, 77, 78 и 84. Выходной сигнал инвертирующего элемента ИЛИ-НЕ 87 поэтому контролирует только самый младший двоичный разряд на линии AR3 арбитражной шины 40 и также управляет элементом 84 его собственного приоритета для фиксирования данных.

Самый старший двоичный разряд на линии AR0 арбитражной шины 40 представляет бит самого высокого приоритета. Любое устройство, возбуждающее этот бит, будет автоматически иметь самый высокий приоритет. Если установленный микропроцессором приоритет в регистре 70 дает индикацию, что определенное устройство имеет приоритет PR0, или что является активизируемым бит более высокого приоритета, тогда любой триггер, запоминающий полярность сигнала - запроса шины, (не показан), который также устанавливается в состояние "1" тактовым импульсом C1, будет автоматически возбуждать линию AR0 арбитражной шины 40. В этом случае этот бит будет всегда активизированным и не нуждается в том, чтобы запрещаться.

Фиг. 6 представляет временную диаграмму, изображающую конвейерную организацию различных операций, основанную на использовании несинхронизируемого генератора 15 (фиг. 1), который может быть любого номинала, в зависимости от технологии. Текущая технология использует длительность цикла 100 нс, а технологии будущего уже планируются на длительность цикла 50 нс. Запрос шины может всегда изменяться в начале тактового импульса C1, то есть в первой половине цикла генератора. Запрос шины остается действительным вплоть до появления следующего тактового импульса C1. Предоставление шины также устанавливается тактовым импульсом C1, однако он следует за циклом запроса шины и поэтому всегда конвейеризируется одним циклом после.

Фиг. 6 показывает совокупность устройств с различными приоритетами - от A, самым высоким, до H, самым низким. Фиг. 6 также показывает каким образом эти приоритеты формируют следующие один за другим циклы либо в качестве пакетов, либо задерживаемые медленными подчиненными компонентами системы, которые не образуют потока данных, таким образом, подчиненные компоненты системы могут принимать данные в пределах их соответствующих распределенным интервалам времени. Понятие "подчиненный компонент системы" в контексте описания обозначает любое устройство, с которым устройство "хозяина" шины имеет намерение установить связь.

Каждый раз, когда некоторое устройство получает доступ к шине 12, оно будет внутренне фиксировать его триггер предоставления собственной шины (подобный триггеру 49, фиг. 4). Этот триггер управляет текущим циклом для устройства, которое выигрывает в разрешении конфликтных ситуаций. В это время это устройство распоряжается циклом для осуществления связи с подчиненным компонентом системы. Оно посылает адрес на шину 12 в течение цикла предоставления собственной шины. Оно также показывает, какую функцию - считывания или записи - оно намерено осуществлять на сигнале + Считывание/-Запись. (+ RD/ - WR). Сигнал - Блокировки (-Lock) будет также становиться активизируемым, если "хозяин" шины имеет желание работать в монопольном (пакетном) режиме, то есть блокировать другие устройства для короткого пакета циклов, прежде чем следующее устройство наивысшего приоритета может вступить в работу. Если произошла одна передача данных и подчиненный компонент системы тогда видит повторяемым его собственный адрес, он может пожелать продлить время, в котором он нуждается, для того чтобы либо принимать, либо посылать данные. Он может делать это в одном или более приращений основного цикла шины установкой сигнала - Блокировка при логической схеме, аналогичной логической схеме, показанной на фиг. 4, используемой "хозяевами" шины. Линия ответных сигналов от каждого устройства дает индикацию, что устройство либо послало, либо приняло данные на шине 12. Сигнал - Блокировка может также быть ответом на следующий цикл от подчиненного компонента системы, индицирующий, что таковой не может принять любой последующий цикл.

Как показано на фиг.6, запрос шины сопровождается предоставлением шины и адресацией, выполняемой "хозяином" (master) шины, и функция считывания или записи появляется в качестве третьей последовательности операции с конвейерной организацией.

Фиг. 6 изображает запись и считывание различными ведущими (master) устройствами A-H к подчиненным (slave) компонентам системы P-W или от них, в различных типах рабочего режима.

Как иллюстрировано, это изобретение было реализовано с адресной шиной и двунаправленной шиной данных. Однако для ускоренной конвейерной обработки это изобретение может быть реализовано с однонаправленной выходной шиной для адресов и данных, мультиплексируемых при полуцикловых периодах, а шина данных может быть только входной однонаправленной шиной данных.

Или, если предпочтительно реализовать с одной неспециализированной двунаправленной шиной, адреса будут посылаться только один раз в начале длинной передачи и во время последующих циклов передачи данных, эти адреса будут инкрементироваться последовательно, если только не будет посылаться новый непоследовательный адрес. Более конкретно, в начале длинной передачи устройство будет получать пакет из двух циклов, посылая адрес во время первого и данные в течение второго и последующих циклов. Фиг. 6 в этом случае можно было бы модифицировать, чтобы исключить адресную шину, и арбитражная шина будет тогда становиться косвенным указателем адреса для мультиплексированных внешних устройств.

Хотя данное изобретение было показано и описано в отношении предпочитаемых вариантов его осуществления, специалистам в данной области техники будет понятно, что изменения в форме и деталях могут быть выполнены в этих вариантах осуществления данного изобретения, без отступления от объема патентной защиты определяемого формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ОБРАБОТКИ ЗАПРОСОВ НА ДОСТУП К ШИНЕ | 1990 |

|

RU2067314C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2117405C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2110839C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2072553C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ПРЯМОГО ДОСТУПА (DASD) ЕМКОСТЬЮ БОЛЬШЕ 528 МЕГАБАЙТ И СПОСОБ ЕГО ВОПЛОЩЕНИЯ ДЛЯ ПЕРСОНАЛЬНЫХ КОМПЬЮТЕРОВ | 1994 |

|

RU2155369C2 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

| Устройство доступа к видеопамяти | 1988 |

|

SU1523058A3 |

| СПОСОБ ГЕНЕРИРОВАНИЯ ДАННЫХ ИЗОБРАЖЕНИЯ | 1991 |

|

RU2113770C1 |

| ДИНАМИЧЕСКИЙ ВОЛНОВОЙ КОНВЕЙЕРНЫЙ ИНТЕРФЕЙС И СПОСОБ ЕГО ПРИМЕНЕНИЯ | 2000 |

|

RU2213992C2 |

Изобретение относится к устройствам для управления передачами данных через неспециализированную шину между запоминающим устройством или совокупностью внешних устройств (включая процессоры), как по отдельности, так и в совокупности, а более конкретно, к средствам, позволяющим разрешать конфликты на основе приоритетов между устройствами более эффективно, посредством исключения бесполезно отработавших циклов разрешения конфликтов и больших пакетных буферных устройств, и делать пропускную способность доступной для передачи данных. В состав устройства входят центральный процессор 10, блок оперативной памяти 11, не менее двух внешних каналов 13 и 14 связи, входы-входы которых подключены к системной шине 12 устройства, связанной с выходом генератора 15. 2 з.п.ф-лы, 6 ил.

| Шевкопляс Б.В | |||

| Микропроцессорные структуры | |||

| - М.: Радио и связь, 1986, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| SU, авторское свидетельство, 550650, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 907536, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| РСТ, заявка, WO 87004827, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| EP, заявка, 0137609, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| EP, заявка, 0138676, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| EP, заявка, 0167193, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-05-10—Публикация

1991-09-20—Подача