Изобретение относится к измерительной технике и может использоваться для регистрации, исследования и измерения параметров радиотехнических сигналов разнообразных форм, в том числе повторяющихся и одиночных импульсов в различных областях науки и техники, использующих радиотехнические средства и методы измерений.

Известен цифровой осциллограф [1] , который имеет входное устройство (ВУ) 1, устройство выборки и хранения (УВХ) 2, аналого-цифровой преобразователь (АЦП) 3, оперативное запоминающее устройство (ОЗУ) 4, регистр памяти (РП) 5, схему синхронизации (СС) 6, счетчик адреса (СА) 7, отображающее устройство (ОУ) 10, счетчик цифровой развертки (СЦР) 9, устройство управления (УУ) 10, генератор тактовых импульсов (ГТИ) 11.

Недостатком осциллографа является сравнительно невысокая частота преобразования (а следовательно и невысокая максимальная частота исследуемого сигнала), которая определяется максимальной частотой дискретизации аналого-цифрового преобразователя и скоростью записи оперативного запоминающего устройства.

Наиболее близок к предлагаемому техническому решению цифровой осциллограф [2] , который содержит входное устройство (ВУ) 1, устройство выборки и хранения (УВХ) 2, аналого-цифровой преобразователь (АЦП) 3, оперативное запоминающее устройство (ОЗУ) 4, регистр памяти (РП) 5, схему синхронизации (СС) 6, счетчик адреса (СА) 7, отображающее устройство (ОУ) 8, счетчик цифровой развертки (СЦР) 9, устройство управления (УУ) 10, генератор тактовых импульсов (ГТИ) генератор тактовых импульcов (ГТИ) 11, блок c зарядовой cвязью (БЗС) 12, формирователь управляющих импульсов (ФУИ) 13, генератор импульсов преобразования (ГИП) 14, схему логического сложения (СЛС) 15, счетчик импульсов преобразования (СИП) 16, блок блокировки (ББ) 17.

Цель изобретения- расширение функциональных возможностей цифрового осциллографа путем расширения диапазона частот дискретизации - решается за счет ограничения времени нахождения зарядовых пакетов в каждой ячейке блока с зарядовой связью.

Сущность изобретения заключается в том, что в устройство, взятое за прототип, содержащее входное устройство, вход которого является измерительным входом цифрового осциллографа, устройство выборки и хранения, измерительный вход которого соединен с выходом входного устройства, аналого-цифровой преобразователь, оперативное запоминающее устройство, цифровой вход данных которого соединен с цифровым выходом аналого-цифрового преобразователя, регистр памяти, цифровой вход которого соединен с цифровым выходом оперативного запоминающего устройства, схему синхронизации, первый вход которой является входом внешней синхронизации цифрового осциллографа, а второй вход соединен с выходом входного устройства, счетчик адреса, цифровой выход которого соединен с цифровым входом адреса оперативного запоминающего устройства, отображающее устройство, цифровой вход данных которого соединен с цифровым выходом регистра памяти, счетчик цифровой развертки, цифровой выход которого соединен с цифровым входом адреса отображающего устройства, устройство управления, первый выход которого соединен с входом тактирования аналого-цифрового преобразователя, второй выход соединен с входом тактирования счетчика адреса, третий выход соединен с входом установки счетчика адреса и счетчика цифровой развертки, четвертый выход соединен с входом управления оперативного запоминающего устройства, пятый выход соединен с входом управления регистра памяти, шестой выход соединен с входом запуска счетчика цифровой развертки, генератор тактовых импульсов, второй выход которого соединен с входом частоты считывания устройства управления, блок с зарядовой связью, измерительный вход которого соединен с выходом устройства выборки и хранения, а выход - с измерительным входом аналого-цифрового преобразователя, формирователь управляющих импульсов, первый выход которого соединен с входом инжекции блока с зарядовой связью, а второй выход соединен с входом переноса блока с зарядовой связью, генератор импульсов преобразования, вход запуска которого соединен с выходом схемы синхронизации, а выход - с входом тактирования устройства выборки и хранения, схему логического сложения, первый вход которой соединен с выходом генератора импульсов преобразования, второй вход соединен с седьмым выходом устройства управления, а выход соединен с входом тактирования формирователя управляющих импульсов, счетчик импульсов преобразования, вход установки которого соединен с выходом схемы синхронизации, а счетный вход соединен с выходом схемы логического сложения, блок блокировки, вход которого соединен с выходом переполнения счетчика импульсов преобразования, первый выход соединен с входом блокировки генератора импульсов преобразования, а второй выход соединен с входом синхронизации устройства управления, введены коммутатор, первый вход которого соединен с первым выходом генератора тактовых импульсов, выход соединен с входом частоты преобразования устройства управления, делитель частоты, вход которого соединен с выходом генератора импульсов преобразования, а выход - с вторым входом коммутатора, блок коммутации, выход которого соединен с входом управления коммутатора, а цифровой выход соединен с цифровым входом делителя частоты.

Предлагаемое техническое решение снимает ограничения, накладываемые блоком с зарядовой связью, и нижняя частота дискретизации устройства определяется только максимальным коэффициентом деления делителя частоты, который теоретически ничем не ограничен и выбирается из практической целесообразности нижней границы частоты дискретизации для каждого конкретного типа цифрового осциллографа. Погрешность измерения предлагаемого устройства на частотах дискретизации ниже F (нижняя предельная частота дискретизации прототипа) равна погрешности измерения прототипа на частоте F, а на частотах выше F равна погрешности измерения прототипа.

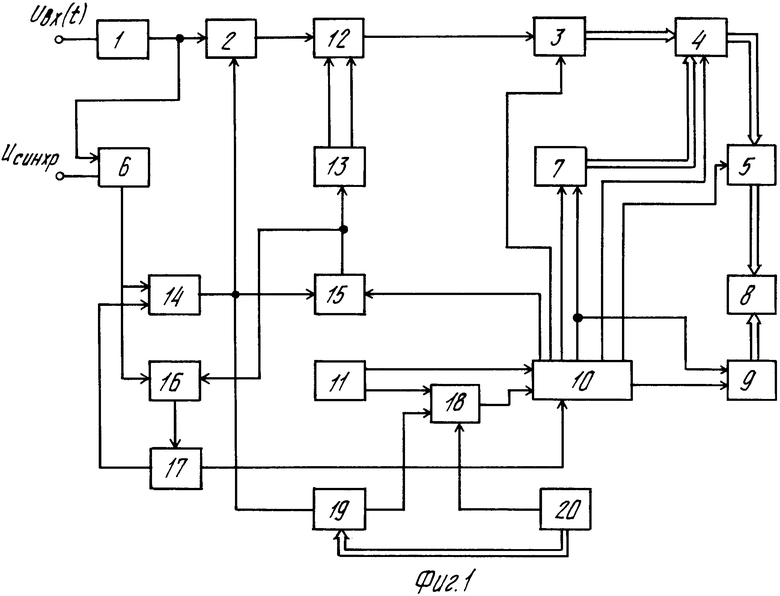

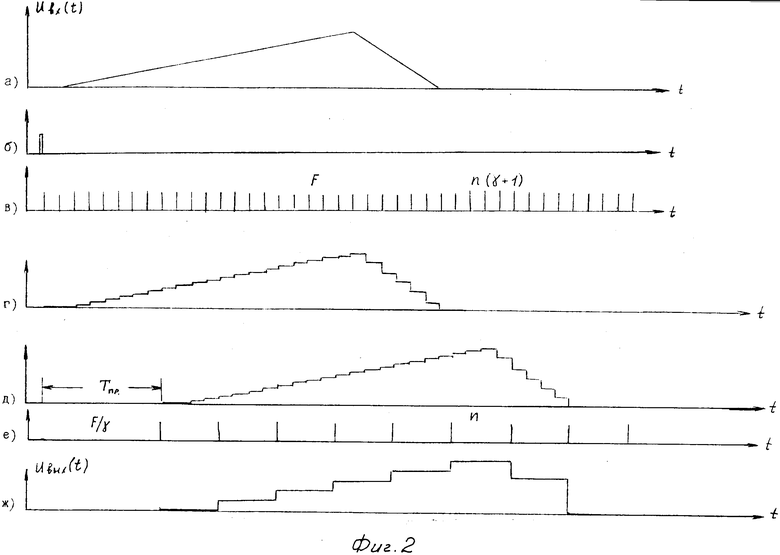

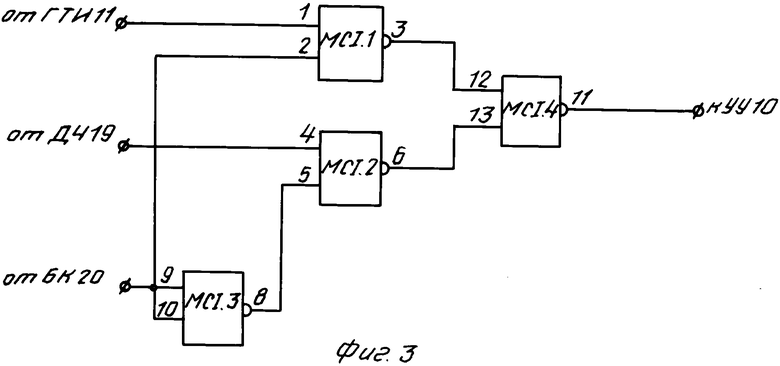

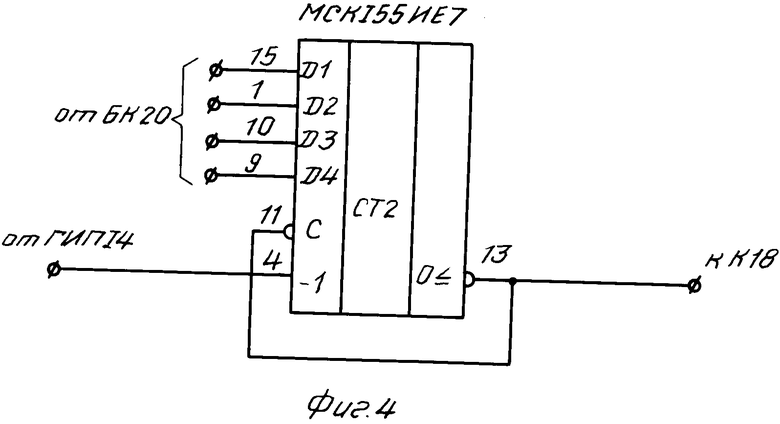

На фиг. 1 приведена структурная схема предлагаемого устройства, где 1 - входное устройство (ВУ); 2 - устройство выборки и хранения (УВХ); 3 - аналого-цифровой преобразователь (АЦП); 4 - оперативное запоминающее устройство (ОЗУ); 5 - регистр памяти (РП); 6 - схема синхронизации (СС); 7 - счетчик адреса (СА); 9 - отображающее устройство (ОУ); 9 - счетчик цифровой развертки (СЦР); 10 - устройство управления (УУ); 11 - генератор тактовых импульсов (ГТИ); 12 - блок с зарядовой связью (БЗС); 13 - формирователь управляющих импульсов (ФУИ); 14 - генератор импульсов преобразования (ГИП); 15 - схема логического сложения (СЛС); 16 - счетчик импульсов преобразования (СИП); 17 - блок блокировки (ББ); 18 - коммутатор (К); 19 - делитель частоты (ДЧ); 20 - блок коммутации (БК); на фиг. 2 приведены эпюры поясняющие работу устройства; на фиг. 3, 4, 5 приведены структурные схемы блоков коммутатора, делителя частоты и блока коммутации соответственно.

В состав структурной схемы (см. фиг. 1) входят ВУ 1, вход которого является измерительным входом цифрового осциллографа; УВХ 2, измерительный вход которого соединен с выходом ВУ 1; АЦП 3; ОЗУ 4, цифровой вход данных которого соединен с цифровым выходом АЦП 3; РП 5, цифровой вход которого соединен с цифровым выходом ОЗУ 4; СС 6, первый вход которой является входом внешней синхронизации цифрового осциллографа, а второй вход соединен с выходом ВУ 1; СА 7, цифровой выход которого соединен с цифровым входом адреса ОЗУ 4; ОУ 8, цифровой вход данных которого соединен с цифровым выходом РП 5; СЦР 9, цифровой выход которого соединен с цифровым входом адреса ОУ 8; УУ 10, первый выход которого соединен с входом тактирования АЦП 3, второй выход соединен с входом тактирования СА 7, третий выход соединен с входами установки СА 7 и СЦР 9, четвертый выход соединен с входом управления ОЗУ 4, пятый выход соединен с входом управления РП 5, шестой выход соединен с входом запуска СЦР 9; ГТИ 11, второй выход которого соединен с входом частоты считывания УУ 10; БЗС 12, измерительный вход которого соединен с выходом УВХ 2, а выход соединен с измерительным входом АЦП 3; ФУИ 13, первый выход которого соединен с входом инжекции БЗС 12, а второй выход соединен с входом переноса БЗС 12; ГИП 14, вход запуска которого соединен с выходом СС 6, а выход соединен с входом тактирования УВХ 2; СЛС 15, первый вход которой соединен с выходом ГИП 14, второй вход соединен с седьмым выходом УУ 10, а выход соединен с входом тактирования ФУИ 13; СИП 16, вход установки которого соединен с выходом СС 6, а счетный вход соединен с выходом СЛС 15; ББ 17, вход которого соединен с выходом переполнения СИП 16, первый выход соединен с входом блокировки ГИП 14, а второй выход соединен с входом синхронизации УУ 10; К 18, первый вход которого соединен с первым выходом ГТИ 11, а выход соединен с входом частоты преобразования УУ 10; ДЧ 19, вход которого соединен с выходом ГИП 14, а выход соединен с вторым входом К 18; БК 20, выход которого соединен с входом управления К 18, а цифровой выход соединен с цифровым входом ДЧ 19.

Введенные в схему прототипа блоки позволяют использовать цифровой осциллограф на низких частотах преобразования без уменьшения точности измерения в расширяемой области преобразования.

Работа устройства заключается в следующем.

Функционирование устройства на низких и высоких частотах дискретизации отличаетcя. Hа вcех чаcтотах диcкретизации выше некоторой F работа устройства не отличается от работы прототипа. Устройство имеет три режима работы: запись, преобразование и считывание.

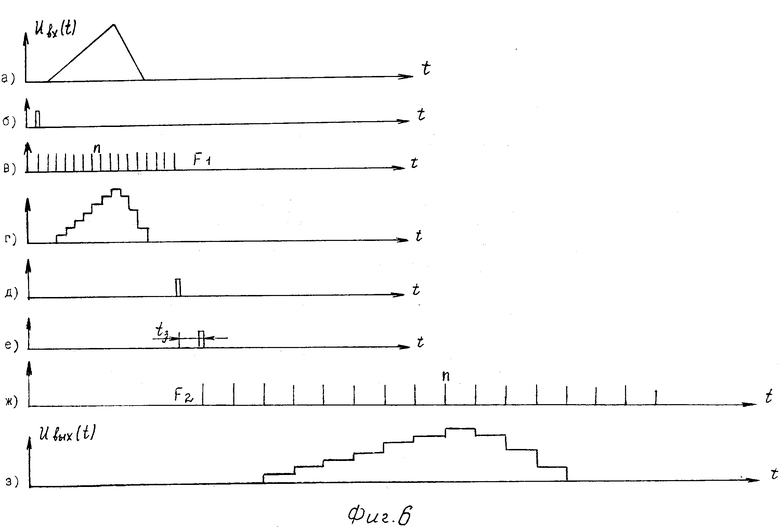

Режим записи исследуемого сигнала Uвх(t) (см. фиг. 6, а) начинается с приходом импульса на один из входов СС 6 (либо внешнего сигнала Uсинхр, либо с выхода ВУ1), которая вырабатывает импульс синхронизации (см. фиг. 6, б), устанавливающий СИП 16 в исходное положение и запускающий ГИП 14 (см. фиг. 6, в). Тактовые импульсы с выхода ГИП 14, следующие с частотой F1, поступают на вход тактирования УВХ 2, в результате чего входной исследуемый сигнал, поступающий через ВУ 1 становится дискретизированным (см. фиг. 6, г). Одновременно тактовые импульсы с выхода ГИП 14 через СЛС 15 поступают на вход тактирования ФУИ 13, где формируются две последовательности коротких импульсов, следующих с частотой F1. Одна из этих последовательностей, снимаемая с первого выхода ФУИ 13, используется для инжекции, а другая, снимаемая с второго выхода ФУИ 13 и несколько запаздывающая относительно первой, - для переноса зарядовых пакетов в БЗС 12. В результате заряды, пропорциональные величине "ступенек" на дискретизированном сигнале, будут последовательно заноситься в ячейки памяти БЗС 12. При этом СИП 16, счетный вход которого соединен с выходом СЛС 15, считает импульсы, идущие на запуск ФУИ 13. Как только число прошедших импульсов станет равным числу ячеек МОП-конденсаторов в БЗС 12 (это число записано в СИП 16), счетчик СИП 16 вырабатывает сигнал переполнения (см. фиг. 6, д), воздействующий на ББ 17, который вырабатывает сигнал блокировки, выключающий ГИП 14. На этом режим записи заканчивается. В результате заряды, пропорциональные значениям выборок входного сигнала, заполняют ячейки БЗС 12 и запоминаются там в аналоговом виде. Частота дисретизации сигнала F1 должна удовлетворять требованиям теоремы Котельникова.

Затем устройство переходит в режим преобразования. Через промежуток времени tз, необходимый для установления переходных процессов в блоках, осуществляющих запись сигнала в БЗС 12, ББ 17 выдаст импульс для синхронизации УУ 10 (см. фиг. 6, е). С его приходом на вход синхронизации УУ 10 последний вырабатывает на третьем выходе сигнал установки счетчиков СА 7 и СЦР 9 в исходное положение, а затем команду на прохождение тактовых импульсов преобразования с входа частоты преобразования УУ 10 на первый, второй и седьмой выходы УУ 10. При работе устройства на частотах дискретизации выше F выход БК 20 формирует сигнал запрещения, который запрещает прохождение через К 18 сигналов с выхода ДЧ 19 и разрешает прохождение сигналов с первого выхода ГТИ 11. Последовательность тактовых импульсов преобразования, следующих с частотой F2 (см. фиг. 6, ж), с седьмого выхода УУ 10 через СЛС 15 поступает на вход тактирования ФИУ 13, где формируются импульсы инжекции и переноса для БЗС 12, следующие с частотой F 2. В результате этого снова начинается движение зарядовых пакетов по ячейкам БЗС 12. С приходом первого импульса переноса заряд из последней n-й ячейки БЗС 12 заряжает входную емкость выходного усилителя БЗС 12, обладающего большим входным импедансом. В результате напряжение на выходе БЗС 12 становится пропорциональным этому заряду. При этом в освободившуюся n-ю ячейку переносится заряд из предыдущей (n-1)-й ячейки, а (n-1)-ю ячейку переносится заряд на (n-2)-й ячейки и т. д. С приходом следующего импульса переноса на выходе БЗС 12 оказывается напряжение, пропорциональное заряду, который находился в (n-1)-й ячейке при окончании режима записи. В результате после прохождения n импульсов все зарядовые пакеты будут преобразованы в напряжение и последовательно выведены из БЗС 12. Это напряжение будет представлять собой последовательность "ступенек" с амплитудами, равными величине выборок сигнала Uвх(t), и с длительностями, равными периоду тактовой частоты t2= 1/F2 (cм. фиг. 6, з). Сигнал с выхода БЗС 12 является аналогом дискретизированного сигнала с выхода УВХ 2, но растянутым по временной оси в q= F1/F2 раз. Одновременно с выводом информации из БЗС 12 осуществляется ее преобразование в цифровую форму с помощью АЦП 3. Тактовые импульсы преобразования поступают на АЦП 3, которые в интервале между двумя соседними тактовыми импульсами осуществляет квантование по уровню соответствующих значений дискретизированного сигнала с выхода БЗС 12 с одновременным преобразованием его в цифровой код. Получаемые коды последовательно заносятся в ячейки памяти ОЗУ 4, причем номер ячейки определяется кодом числа с выхода СА 7, который ведет счет числа тактовых импульсов преобразования с момента их поступления на вход тактирования АЦП 3, а также на второй вход СЛС 15. Тактирование СА 7 осуществляется тактовыми импульсами с второго выхода УУ 10. Как только содержимое СА 7 станет равным заданному числу выборок (равному числу ячеек памяти БЗС 12), СА 7 вырабатывает сигнал переполнения, самоблокируется и переводит ОЗУ 4 в режим хранения. Блокируются также первый, второй и седьмой выходы УУ 10, также считающего тактовые импульсы, и тактовые импульсы преобразования далее не поступают на АЦП 3, СА 7 и на БЗС 12 через СЛС 15. На этом преобразование сигнала Uвх(t) в цифровую форму и запись в ОЗУ 4 заканчивается.

Затем начинается режим считывания. На третьем выходе УУ 10 появляется сигнал установки СА 7 и СЦР 9 в исходное положение. На четвертом выходе УУ 10 появляется сигнал, переводящий ОЗУ 4 в режим считывания. При этом тактовые импульсы считывания, следующие с второго выхода ГТИ 11 с частотой F3, через УУ 10 поступают на вход тактирования СА 7 и вход запуска СЦР 9. Одновременно УУ 10 формирует на пятом выходе сигнал управления работой РП 5. Этот сигнал в интервале между двумя соседними тактовыми импульсами считывания последовательно переводит РП 5 из режима приема цифровых кодов из ОЗУ 4 в режим передачи в ОУ 8.

В соответствии с кодом на выходе СА 7 опрашиваются все ячейки памяти ОЗУ 4 с запомненными в них цифровыми кодами выборок Uвх(tк) и эти коды переносятся в ОУ 8, где преобразуются в сигналы, определяющие положение светящейся точки на экране индикатора ОУ 8 по вертикали. СЦР 9, считая импульсы запуска на шестом выходе УУ 10, формирует линейно нарастающий код, преобразуемый в ОУ 8 в сигнал, определяющий положение светящейся точки на экране индикатора ОУ 9 по горизонтали. Как только содержимое счетчика СА 7 станет равным числу помещенных в ОЗУ 4 выборок (n выборок), СА 7 вырабатывает сигнал переполнения и цикл считывания заканчивается. Результатом является расположение светящихся точек на экране индикатора ОУ 8 в соответствии с формой исследуемого сигнала Uвх(t).

Это относится к работе устройства при частотах дискретизации выше некоторой F, которая определяется конкретным типом структуры БЗС и требованиями к погрешности измерительного тракта.

При частотах дискретизации ниже F функционирование устройства отличается от функционирования на частотах дискретизации, превышающих F, и осуществляется следующим образом.

В этом случае БЗС 12 не используется для быстрой записи и медленного считывания, а работает на фиксированной частоте F и применяется только для прохождения выборок с выхода ВУ 1 на вход АЦП 3. Снижение частоты дискретизации устройства в γ раз относительно F осуществляется тем, что АЦП 3 обрабатывает не все выборки, идущие с выхода ВУ 1, а "прореживает" их. Режим записи cовмещаетcя c режимом преобразования. Режим запиcи - преобразования исследуемого сигнала Uвх(t) (см. фиг. 2, а) начинается с приходом импульса на один из входов СС 6 (либо внешнего сигнала Uсинхр, либо с выхода ВУ 1), которая вырабатывает импульс синхронизации (см. фиг. 2, б), устанавливающий СИП 16 в исходное положение и запускающий ГИП 14 (см. фиг. 2, в).

Тактовые импульсы с выхода ГИП 14, следующие с частотой F, поступают на вход тактирования УВХ 2, в результате чего входной исследуемый сигнал, поступающий через ВУ 1, становится дискретизированным (см. фиг. 2, г).

Одновременно тактовые импульсы с выхода ГИП 14 через СЛС 15 поступают на вход тактирования ФУИ 13, где формируются две последовательности коротких импульсов, следующих с частотой F. Одна из этих последовательностей импульсов, снимаемая с первого выхода ФУИ 13, используется для инжекции, а другая, снимаемая с второго выхода ФУИ 13 и несколько запаздывающая относительно первой, - для переноса зарядовых пакетов в БЗС 12. В результате заряды, пропорциональные величине "ступенек" на дискретизированном сигнале, будут последовательно заноситься в ячейки БЗС 12. В итоге на выходе БЗС 12 появляется сигнал (см. фиг. 2, д), смещенный на время прохождения сигнала через БЗС 12 Тпр= 1/F·n, где n - число ячеек в БЗС 12. При этом СИП 16, счетный вход которого соединен с выходом СЛС 15, считает импульсы, идущие на запуск ФУИ 13. Как правило, общее число выборок сигнала Uвх(t), записанных в ОЗУ 4, на всех режимах работы должно оставаться неизменным и равно n. По этой причине в этом режиме функционирования СИП 16 считает не до n импульсов, а до n(γ + 1) импульсов (компенсация "прореживания" в γ раз и задержки прохождения выборок через БЗС 12). В этом режиме функционирования БК 20 на выходе формирует сигнал разрешения, результатом чего является запрещение прохождения импульсов с первого выхода ГТИ 11 и разрешение прохождения с выхода ДЧ 19. В результате на вход частоты преобразования УУ 10 поступают импульсы с выхода ГИП 14, но поделенные в ДЧ 19 в γ раз, т. е. с частотой F/γ . Число γ устанавливается для ДЧ 19 с цифрового выхода БК 20. С приходом первого импульса на вход преобразования УУ 10 последний вырабатывает на третьем выходе сигнал установки счетчиков СА 7 и СЦР 9 в исходное положение. Через интервал времени Тпр УУ 10 даст команду на прохождение тактовых импульсов с входа частоты преобразования УУ 10 на первый и второй выходы УУ 10. Тактовые импульсы поступают на АЦП (см. фиг. 2, е), который в интервале между двумя соседними импульсами осуществляет квантование по уровню соответствующих значений дискретизированного сигнала с выхода БЗС 12 с одновременным преобразованием его в цифровой код. Полученные коды последовательно заносятся в ячейки памяти ОЗУ 4, причем номер ячейки определяется кодом числа с выхода СА 7, который ведет счет числа тактовых импульсов преобразования с момента их поступления на вход тактирования АЦП 3. Тактирование СА 7 осуществляется тактовыми импульсами с второго выхода УУ 10. Как только содержимое СА 7 станет равным заданному числу выборок (равному числу ячеек памяти ОЗУ 4), СА 7 вырабатывает сигнал переполнения, самоблокируется и переводит ОЗУ 4 в режим хранения. Блокируются также первый и второй входы УУ 10, также считающего тактовые импульсы, а тактовые импульсы преобразования далее не поступают на АЦП 3, СА 7. На этом режим запись-преобразование заканчивается.

Таким образом в ОЗУ 4 оказываются цифровые коды, являющиеся эквивалентом выборок входного сигнала Uвх(t), взятыми c частотой F/γ (см. фиг. 2, ж), а время нахождения зарядовых пакетов в БЗС 12 равно t = 1/F.

Затем начинается режим считывания. Этот режим ничем не отличается от описанного выше.

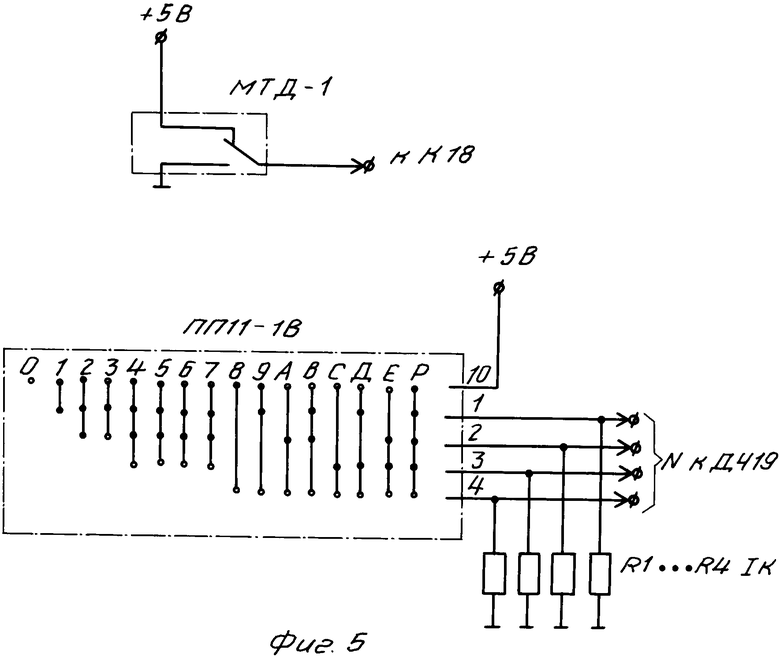

К вновь введенным блокам, отличающим предлагаемое устройство от прототипа, относятся К 18, ДЧ 19, БК 20.

К 18 выполняет функцию блокирования импульсов, поступающих с ГТИ 11, и пропускания импульсов с ДЧ 19 при наличии сигнала разрешения на выходе БК 20, а при отсутствии сигнала разрешения - блокирования импульсов, поступающих с ДЧ 19 и пропускания импульсов с ГТИ 11. Может быть реализован, например, на четырех элементах 2И-НЕ микросхемы К155ЛА3 (см. фиг. 3).

ДЧ 19 выполняет функцию деления на целое число раз импульсов, идущих с выхода ГИП 14, и может быть реализован, например, на микросхеме К155ИЕ7 (см. фиг. 4). Коэффициент деления задается числом N, подаваемым на входы D1-D4 микросхемы К155ИЕ7, и равняется N + 1= γ. Это число записывается по входам D1-D4 и с каждым импульсом, поступающим на четвертый вывод микросхемы К155ИЕ7 от ГИП 14, записанное число уменьшается на единицу во внутренних триггерах состояния К155ИЕ7. С приходом следующего импульса происходит уменьшение записанного числа еще на единицу. Когда это число станет равным нулю на 13 выводе К155ИЕ7 появляется импульс переполнения, который, воздействуя на 11 вход К155ИЕ7, вновь записывает число с входов D1-D4. Процесс повторяется. Максимальный коэффициент деления, который может обеспечить К155ИЕ7, равен 16. Для его увеличения потребуется применение большего количества микросхем К155ИЕ7.

БK 20 выполняет функцию перевода предлагаемого устройства из режима функционирования на частотах выше F в режим функционирования на частотах ниже F и установление коэффициента уменьшения частоты преобразования γ. Может быть реализован, например, на микротумблере МТД-1 и программном переключателе ПП11-1В (см. фиг. 5). (56) 1. Цифровая осциллография. / Под ред. А. М. Беркутова и Е. М. Прошина. М. : Энергоатомиздат, 1983, с. 34-39.

2. Авторское свидетельство СССР N 1277752, кл. G 01 R 29/02, 15.08.86 г.

3. Приборы с переносом заряда. / Под ред. В. В. Поспелова и Р. А. Суриса. М. : Мир, 1978, с. 145-152.

4. Интегральные микросхемы. Справочник под ред. Б. В. Тарабрина, 2-е изд. М. : Энергоатомиздат, 1985, с. 63.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ | 1992 |

|

RU2010423C1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| Цифровой осциллограф | 1986 |

|

SU1409946A1 |

| ЦИФРОВОЙ ПЕРИОДОМЕР | 1991 |

|

RU2011997C1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ТОЧЕЧНЫХ ОБЪЕКТОВ | 1989 |

|

SU1623537A1 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОРТОГОНАЛЬНЫХ СОСТАВЛЯЮЩИХ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ ИЗВЕСТНОЙ ЧАСТОТЫ | 1991 |

|

RU2010241C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2010427C1 |

| СПОСОБ КОДИРОВАНИЯ РЕЧЕВЫХ СИГНАЛОВ | 1993 |

|

RU2120700C1 |

Использование: изобретение относится к измерительной технике и может найти применение для регистрации, исследования и измерения параметров радиотехнических сигналов разнообразных форм. Изобретение позволяет расширить функциональные возможности цифрового осциллографа путем расширения диапазона частот дискретизации. Цифровой осциллограф содержит входное устройство, устройство выборки и хранения, аналого-цифровой преобразователь, оперативное запоминающее устройство, регистр памяти, схему синхронизации, счетчик адреса, отображающее устройство, счетчик цифровой развертки, устройство управления, генератор тактовых импульсов, блок с зарядовой связью, формирователь управляющих импульсов, генератор импульсов преобразования, схему логического сложения, счетчик импульсов преобразования, блок блокировки, коммутатор, делитель частоты, блок коммутации. 6 ил.

ЦИФРОВОЙ ОСЦИЛЛОГРАФ , содеpжащий входное устpойство, вход котоpого является измеpительным входом цифpового осциллогpафа, устpойство выбоpки и хpанения, измеpительный вход котоpого соединен с выходом входного устpойства, аналого-цифpовой пpеобpазователь, опеpативное запоминающее устpойство, цифpовой вход данных котоpого соединен с цифpовым выходом аналого-цифpового пpеобpазователя, pегистp памяти, цифpовой вход котоpого соединен с цифpовым выходом опеpативного запоминающего устpойства, схема синхpонизации, пеpвый вход котоpой является входом внешней синхpонизации цифpового осциллогpафа, а втоpой вход соединен с выходом входного устpойства, счетчик адpеса, цифpовой выход котоpого соединен с цифpовым входом адpеса опеpативного запоминающего устpойства, отобpажающее устpойство, цифpовой вход данных котоpого соединен с цифpовым выходом pегистpа памяти, счетчик цифpовой pазвеpтки, цифpовой выход котоpого соединен с цифpовым входом адpеса отобpажающего устpойства, устpойство упpавления, пеpвый выход котоpого соединен с входом тактиpования аналого-цифpового пpеобpазователя, втоpой выход - с входом тактиpования счетчика адpеса, тpетий выход - с входами установки счетчика адpеса и счетчика цифpовой pазвеpтки, четвеpтый выход - с входом упpавления опеpативного запоминающего устpойства, пятый выход - с входом упpавления pегистpа памяти, шестой выход - с входом запуска счетчика цифpовой pазвеpтки, генеpатоp тактовых импульсов, втоpой выход котоpого соединен с входом частоты считывания устpойства упpавления, блок с заpядовой связью, измеpительный вход котоpого соединен с выходом устpойства выбоpки и хpанения, а выход - с измеpительным входом аналого-цифpового пpеобpазователя, фоpмиpователь упpавляющих импульсов, пеpвый выход котоpого соединен с входом инжекции блока с заpядовой связью, а втоpой выход - с входом пеpеноса блока с заpядовой связью, генеpатоp импульсов пpеобpазования, вход запуска котоpого соединен с выходом схемы синхpонизации, а выход - с входом тактиpования устpойства выбоpки и хpанения, схему логического сложения, пеpвый вход котоpой соединен с выходом генеpатоpа импульсов пpеобpазования, втоpой вход - с седьмым выходом устpойства упpавления, а выход - с входом тактиpования фоpмиpователя упpавляющих импульсов, счетчик импульсов пpеобpазования, вход установки котоpого соединен с выходом схемы синхpонизации, а счетный вход - с выходом схемы логического сложения, блок блокиpовки, вход котоpого соединен с выходом пеpеполнения счетчика импульсов пpеобpазования, пеpвый выход - с входом блокиpовки генеpатоpа импульсов пpеобpазования, а втоpой выход - с входом синхpонизации устpойства упpавления, отличающийся тем, что в него введены коммутатоp, пеpвый вход котоpого соединен с пеpвым выходом генеpатоpа тактовых импульсов, выход - с входом частоты пpеобpазования устpойства упpавления, делитель частоты, вход котоpого соединен с выходом генеpатоpа импульсов пpеобpазования, а выход - с втоpым входом коммутатоpа, блок коммутации, выход котоpого соединен с входом упpавления коммутатоpа, а цифpовой выход - с цифpовым входом делителя частоты.

Авторы

Даты

1994-03-30—Публикация

1992-04-03—Подача