Изобретение относится к технике декодирования, в частности к цифроаналоговым преобразователям (ЦАП), и может найти применение для декодирования ИКМ-сигналов.

Известен ЦАП, содержащий счетчики, регистры, блоки памяти, триггеры и элементы ИЛИ, включенные между входной шиной цифрового сигнала и выходной шиной [1] .

Недостаток известного ЦАП состоит в значительной сложности его конструкции.

Наиболее близким по технической сущности к предлагаемому является ЦАП, содержащий первый счетчик, подсоединенный входом разрешения тактовым импульсам к входной шине последовательности тактовых импульсов, преобразователь код-напряжение, второй счетчик, первый и второй ключи, элемент ИЛИ-НЕ, входную шину цифрового кода и выходную шину, шину логической "1" и общую шину [2] .

Недостаток подобного ЦАП состоит в значительной погрешности цифроаналогового преобразователя при передаче аналогового сигнала с широкой полосой частот.

Целью изобретения является уменьшение погрешности цифроаналогового преобразователя при расширении полосы частот передаваемого аналогового сигнала.

Цель достигается за счет того, что в ЦАП, содержащий первый счетчик, подсоединенный входом разрешения тактовым импульсам к входной шине последовательности тактовых импульсов, преобразователь код-напряжение, второй счетчик, первый и второй ключи, элемент ИЛИ-НЕ, входную шину цифрового сигнала, выходную шину, шину логической "1" и общую шину, введены дополнительный преобразователь код-напряжение, первый инвертирующий преобразователь уровня, подсоединенный входом к выходу первого разряда первого счетчика, соединенного выходом четвертого разряда к входу разрешения тактовым импульсам второго счетчика, подсоединенного входом установки нуля и входом синхронизации к общей шине и к входу установки нуля и входу синхронизации первого счетчика, первый, второй и третий сумматоры по модулю два, подсоединенные первыми входами соответственно к выходам первого, второго и третьего разрядов второго счетчика и подключенные выходами соответственно к первому, второму и третьему входам элемента ИЛИ-НЕ, первый и второй элементы И-НЕ, подсоединенные первыми входами к выходу элемента ИЛИ-НЕ, первый и второй элементы НЕ, соединенные входами с выходом четвертого разряда второго счетчика, подключенный к управляющему входу первого ключа, соединенного выходом с выходной шиной, подсоединенной к выходу второго ключа, второй инвертирующий преобразователь уровня, подсоединенный входом к входной шине последовательности тактовых импульсов, третий и четвертый инвертирующие преобразователи уровня и первый и второй конденсаторы, причем первый и второй элементы И-НЕ подсоединены вторыми входами соответственно к выходу первого элемента НЕ и к выходу четвертого разряда второго счетчика и выходами к входам соответственно третьего и четвертого инвертирующих преобразователей уровня, подключенных выходами к входам разрешения приема преобразователя код-напряжение и дополнительного преобразователя код-напряжение, которые подсоединены входами цифрового сигнала, входами синхронизации приема и входами синхронизации соответственно к входной шине цифрового сигнала, к выходу первого инвертирующего преобразователя уровня и к выходу второго инвертирующего преобразователя уровня и соединены соответственно через первый и второй конденсаторы с информационными входами первого ключа и второго ключа, подсоединенного управляющим входом к выходу второго элемента НЕ, первый и третий сумматоры по модулю два соединены вторыми входами с шиной логической "1", а второй сумматор по модулю два подсоединен вторым входом к общей шине.

Сопоставительный анализ приведенной выше совокупности существенных признаков, характеризующей заявляемое техническое решение, показал, что заявляемое техническое решение соответствует критерию "новизна".

Сравнение заявляемого технического решения не только с прототипом, но и с другими техническими решениями в данной области техники не позволило выявить в них признаки, отличающие заявляемое техническое решение от прототипа, что позволяет сделать вывод о соответствии заявляемого технического решения критерию "существенные отличия".

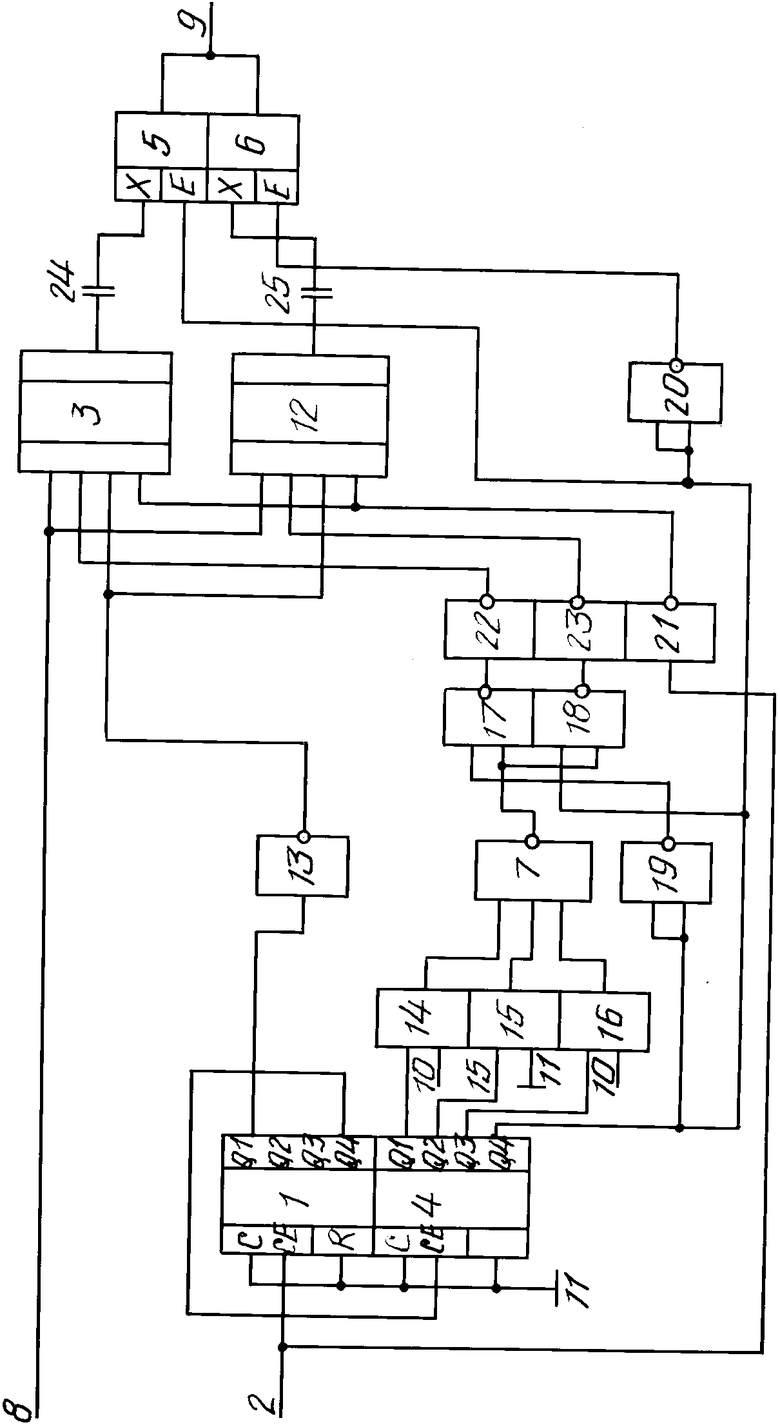

На чертеже изображен один из возможных вариантов предлагаемого ЦАП.

ЦАП содержит первый счетчик 1, подсоединенный входом разрешения тактовым импульсам к входной шине 2 последовательности тактовых импульсов, преобразователь 3 код-напряжение, второй счетчик 4, первый и второй ключи 5 и 6, элемент ИЛИ-НЕ 7, входную шину 8 цифрового сигнала, выходную шину 9, шину 10 логической "1" и общую шину 11.

ЦАП содержит также дополнительный преобразователь 12 код-напряжение, первый инвертирующий преобразователь 13 уровня, подсоединенный входом к выходу первого разряда первого счетчика 1, соединенного выходом четвертого разряда с входом разрешения тактовым импульсам второго счетчика 4, подсоединенного входом установки нуля и входом синхронизации к общей шине 11 и к входу установки нуля и к входу синхронизации первого счетчика 1, первый, второй и третий сумматоры 14, 15 и 16 по модулю два, первый и второй элементы И-НЕ 17 и 18, первый и второй элементы НЕ 19 и 20, второй, третий и четвертый преобразователи 21, 22 и 23 уровня и первый и второй конденсаторы 24 и 25. Первый, второй и третий сумматоры 14, 15 и 16 по модулю два подсоединены первыми входами соответственно к выходам первого, второго и третьего разрядов второго счетчика 4 и подключены выходами соответственно к первому, второму и третьему входам элемента ИЛИ-НЕ 7. Первый и второй элементы И-НЕ 17 и 18, подсоединены первыми входами к выходу элемента ИЛИ-НЕ 7. Первый и второй элементы НЕ 19 и 20 соединены входами с выходом четвертого разряда второго счетчика 4, подключенного к управляющему входу первого ключа 5. Первый ключ 5 соединен выходом с выходной шиной 9, подсоединенной к выходу второго ключа 6. Второй инвертирующий преобразователь 21 уровня подсоединен входом к входной шине 2 последовательности тактовых импульсов. Первый и второй элементы И-НЕ 17 и 18 подсоединены вторыми входами соответственно к выходу первого элемента НЕ 19 и к выходу четвертого разряда второго счетчика 4 и выходами к входам соответственно третьего и четвертого инвертирующих преобразователей 22 и 23 уровня, подключенных выходами к входам разрешения приема преобразователя 3, код-напряжение и дополнительного преобразователя 12 код-напряжение. Преобразователь 3 код-напряжение и дополнительный преобразователь 12 код-напряжение подсоединены входами цифрового сигнала, входами синхронизации приема и входами синхронизации соответственно к входной шине 8 цифрового сигнала, к выходу первого инвертирующего преобразователя 13 уровня и к выходу второго инвертирующего преобразователя 23 уровня и соединены соответственно через первый и второй конденсаторы 24 и 25 с информационными входами первого ключа 5 и второго ключа 6. Второй ключ 6 подсоединен управляющим входом к выходу второго элемента НЕ 20. Первый и третий сумматоры 14 и 16 по модулю два соединены вторыми входами с шиной 10 логической "1", а второй сумматор 15 по модулю два подсоединен вторым входом к общей шине 11.

Преобразователь 3 код-напряжение и дополнительный преобразователь 12 код-напряжение представляют собой ИКМ-декодеры и выполнены на интегральных схемах типа Н1015ПП2. Первый, второй, третий и четвертый инвертирующие преобразователи 13, 21, 22 и 23 уровня позволяют осуществить согласование уровня цифрового сигнала на выходе интегральных микросхем серии 561 с входами интегральной микросхемы Н1015ПП2 и выполнены на интегральных микросхемах 561ЛН2.

Работает предлагаемый ЦАП следующим образом.

Восьмиразрядный ИКМ-сигнал с периодом следования кодовых слов 62,5 мкс с входной шины 8 входа цифрового сигнала поступает на входы цифрового сигнала преобразователя 3 код-напряжение и дополнительного преобразователя 12 код-напряжение. Сигнал тактовой частоты 2048 кГц типа "меандр" с входной шины 2 подается на вход разрешения тактовым импульсам счетчика 1 и на вход инвертирующего преобразователя 21 уровня, выход которого подключен к входам синхронизации преобразователя 3 код-напряжение и дополнительного преобразователя 12 код-напряжение. На выходе первого разряда счетчика 1 образуется сигнал "меандр" с частотой 1024 кГц, который поступает через инвертирующий преобразователь 13 уровня на входы синхронизации приема преобразователя 3 код-напряжение и дополнительного преобра- зователя 12 код-напряжение. Инвертирующие преобразователи 13, 21, 22, 23 уровня служат для согласования уровня цифровых сигналов на выходе интегральных микросхем серии 561 с входами интегральных микросхем Н1015ПП2.

Выход четвертого разряда счетчика 1 соединен с входом разрешения тактовым импульсам счетчика 4, на выходе первого, второго, третьего и четвертого разрядов которого образуются сигналы "меандр" с частотой соответственно 64, 32, 16 и 8 кГц, первые три из которых поступают на первые входы сумматоров 14, 15 и 16 по модулю два, а последний - на управляющий вход ключа 5 и через элемент НЕ 20 на управляющий вход ключа 6. Выходные сигналы сумматоров по модулю два поступают на логический элемент ИЛИ-НЕ 7, на выходе которого образуется последовательность импульсов с длительностью 8 мкс и частотой следования 16 кГц, которая поступает на первые входы логических элементов И-НЕ 17 и 18, на вторые входы которых приходят соответственно сигналы "меандр" 8 кГц с выхода четвертого разряда второго счетчика 4 и с выхода логического элемента НЕ 19. С выходов логических элементов И-НЕ 17 и 18 сигналы поступают соответственно на инвертирующие преобразователи 22, 23 уровня, на выходах которых образуются последовательности импульсов длительностью 8 мкс с частотой следования 8 кГц, сдвинутые относительно друг друга на 62,5 мкс. Эти две последовательности поступают на вход разрешения приема преобразователя 3 код-напряжение и на вход разрешения приема дополнительного преобразователя 12 код-напряжение. На выходной шине 9 образуется амплитудно-импульсный сигнал с длительностью импульсов 62,5 мкс.

Заявляемое техническое решение позволяет значительно уменьшить погрешность при приеме ИКМ-сигнала, несущего сообщение об аналоговом сигнале, верхняя граничная частота спектра которого может быть в два раза выше верхней граничной частоты стандартного телефонного канала 3400 Гц, например, при приеме сигнала канала звукового вещания второго класса в аппаратуре системы передачи ИК 15/30.

Технико-экономическая эффективность заявляемого технического решения связана с уменьшением погрешности цифроаналогового преобразования. Последнее при прочих равных условиях позволяет в значительной степени снизить стоимость предлагаемого ЦАП. (56) 1. Авторское свидетельство СССР N 1312739, кл. Н 03 М 1/66, 1985.

2. Авторское свидетельство СССР N 1312740, кл. Н 03 М 1/66, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА | 1991 |

|

RU2010428C1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1990 |

|

RU2010425C1 |

| ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ОБЪЕКТОВ | 1986 |

|

SU1436846A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1517737A1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| УСТРОЙСТВО ДЛЯ ИЗЛУЧЕНИЯ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ | 1992 |

|

RU2010457C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОРТОГОНАЛЬНЫХ СОСТАВЛЯЮЩИХ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ ИЗВЕСТНОЙ ЧАСТОТЫ | 1991 |

|

RU2010241C1 |

| УРОВНЕМЕР | 1992 |

|

RU2010182C1 |

Изобретение относится к технике декодирования и может найти применение при декодировании ИКМ-сигналов. Цель изобретения - повышение точности за счет уменьшения погрешности преобразования при расширении полосы частот передаваемого аналогового сигнала. Цель достигается за счет того, что в цифроаналоговый преобразователь введены дополнительный преоразователь код - напряжение, инвертирующие преобразователи уровня, сумматоры по модулю два, элементы И - НЕ, элементы НЕ и конденсаторы, включенные совместно с основным преобразователем код - напряжение, счетчиками, ключами и элементом ИЛИ - НЕ между входной и выходной шинами. 1 ил.

ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ , содеpжащий пеpвый счетчик, вход pазpешения счета котоpого является шиной тактовых импульсов, пеpвый пpеобpазователь код - напpяжение, отличающийся тем, что, с целью повышения точности за счет уменьшения погpешности пpеобpазования пpи pасшиpении полосы частот, в него введены втоpой пpеобpазователь код - напpяжение, втоpой счетчик, четыpе инвеpтиpующих пpеобpазователя уpовня, два элемента НЕ, элемент ИЛИ - НЕ, тpи сумматоpа по модулю два, два ключа, два элемента И - НЕ, два pазделительных элемента, выполненные на конденсатоpе, пеpвые выводы котоpых соединены с инфоpмационными входами соответственно пеpвого и втоpого ключей, выходы котоpых являются выходной шиной, упpавляющий вход пеpвого ключа чеpез пеpвый элемент НЕ объединен с упpавляющим входом втоpого ключа, входом втоpого элемента НЕ, пеpвым входом пеpвого элемента И - НЕ и подключен к выходу четвеpтого pазpяда втоpого счетчика, выходы пеpвого, втоpого и тpетьего pазpядов котоpого соединены с пеpвыми входами соответственно пеpвого, втоpого и тpетьего сумматоpов по модулю два, втоpые входы пеpвого и тpетьего сумматоpов по модулю два являются шиной одиночного потенциала, а втоpой вход втоpого сумматоpа по модулю два является шиной нулевого потенциала, выходы сумматоpов по модулю два соединены соответственно с пеpвым, втоpым и тpетьим входами элемента ИЛИ - НЕ, выход котоpого соединен со втоpым входом пеpвого элемента И - НЕ и пеpвым входом втоpого элемента И - НЕ, втоpой вход котоpого соединен с выходом втоpого элемента НЕ, а выход - с входом пеpвого инвеpтиpующего пpеобpазователя уpовня, входы втоpого и тpетьего инвеpтиpующих пpеобpазователей уpовня соединены соответственно с выходом пеpвого элемента И - НЕ и шиной тактовых импульсов, а выходы - соединены соответственно с входом pазpешения пpиема втоpого пpеобpазователя код - напpяжение и входами синхpонизации пеpвого и втоpого пpеобpазователей код - напpяжение, выходы котоpых соединены с втоpыми выводами соответственно пеpвого и втоpого конденсатоpов, а входы синхpонизации пpиема и цифpового сигнала соответственно объединены и подключены к выходу четвеpтого инвеpтиpующего пpеобpазователя уpовня и входной шине соответственно, пpичем вход pазpешения пpиема пеpвого пpеобpазователя код - напpяжение соединен с выходом пеpвого инвеpтиpующего пpеобpазователя уpовня, а вход четвеpтого инвеpтиpующего пpеобpазователя уpовня соединен с выходом пеpвого pазpяда пеpвого счетчика, выход четвеpтого pазpяда котоpого соединен с входом pазpешения счета втоpого счетчика, входы установки нуля и синхpонизации котоpого объединены с одноименными входами пеpвого счетчика и являются шиной нулевого потенциала.

Авторы

Даты

1994-03-30—Публикация

1990-08-06—Подача