Изобретение относится к вычислительной технике и автоматике и может быть использовано для регистрации сигналов неисправности от различных периферийных устройств.

Известно устройство, содержащее первый элемент И, первый триггер, элемент запрета, счетчик, блок выделения последнего импульса пачки, формирователь импульсов, второй элемент И, второй триггер и элемент задержки.

Недостатками устройства являются его низкая надежность и сложность.

Известно устройство, содержащее блок выделения последнего импульса пачки, формирователь импульсов, два триггера, два элемента И, элемент задержки, первый счетчик, второй счетчик, второй элемент задержки, элемент ИЛИ, третий и четвертый элементы И, блок регистров.

Недостатками устройства являются его низкая надежность и сложность.

Прототипом устройства является устройство для регистрации сигналов неисправности, содержащее элемент ИЛИ, триггер, первый и второй счетчики, первый формирователь импульсов, элемент И и n регистров, где n - максимально возможное число сигналов неисправности, поступающих на информационный вход устройства, причем входы элемента ИЛИ образуют информационный вход устройства, выход триггера соединен со счетным входом первого счетчика, инверсный выход К-го (K-log2n) разряда которого соединен с первым входом элемента И, выход второго счетчика соединен с информационным входом первого регистра, информационный вход i-го регистра соединен с выходом (i-1)-го регистра (i= 2n), а также содержит второй и третий формирователи импульсов, причем вход первого формирователя импульсов является входом синхронизации устройства, выход первого формирователя импульсов соединен с входом пуска генератора импульсов, выход которого соединен со счетным входом второго счетчика, выход триггера соединен с синхровходами с первого по n-й регистров, выход элемента ИЛИ соединен с С-входом триггера, D-вход которого подключен к шине единичного потенциала устройства, выходы первого и второго разрядов первого счетчика соединены с входами соответственно второго и третьего формирователей импульсов, с вторым и третьим входами элемента И, выход которого соединен с R-входом триггера.

Недостатком прототипа является невозможность точно регистрировать количество неисправностей, в том числе, когда сигнал неисправности, поступающий на один вход, может перекрываться во времени сигналом неисправности, поступающим на другой вход, а если вследствие неисправности периферийного устройства формируется постоянно высокий уровень, то этим уровнем блокируются все сигналы неисправности от всех других устройств.

Кроме того, в прототипе нет возможности регистрировать номер устройства, на котором зафиксирована неисправность, трудность считывания и отображения результатов контроля, а также громоздкость устройства памяти, объем оборудования которого резко возрастает от числа регистрируемых сигналов неисправности.

Таким образом, недостатки прототипа - низкая надежность регистрации, сложность эксплуатационного обслуживания, узкие функциональные возможности.

Целью изобретения является повышение надежности регистрации сигналов неисправности за счет возможности регистрации одновременно возникающих неисправностей, расширение функциональных возможностей за счет регистрации номера канала неисправности.

Сущность предлагаемого устройства заключается в том, что в блоке формирователей осуществляется раздельное запоминание каждого положительного перепада сигналов неисправности, поступающих от всех периферийных устройств, формирование с помощью первого счетчика и дешифратора сигналов последовательного опроса по всем каналам блока формирователей и формирование неперекрывающихся импульсов неисправности по каждому каналу. По этим сигналам происходит запись в блок памяти содержания первого счетчика, где К первых разрядов содержимого первого счетчика являются номером опрашиваемого объекта, а остальные разряды - временем возникновения неисправности. Одновременно во второй счетчик записывается количество сигналов неисправностей и выдаются адреса ячеек блока памяти. По окончании сеанса регистрации неисправности происходят регистрация количества сигналов неисправности и опрос блока памяти по всем адресам, формируемым вторым счетчиком. Информация о содержимом блока памяти записывается в буферную память устройства отображения или принтерного устройства. По очередному сигналу пуск осуществляется следующий цикл регистрации.

Таким образом, сущность предложенного устройства состоит в том, что вне зависимости от количества и времени возникновения сигналов неисправности формируются короткие, не совпадающие во времени импульсы неисправности, которые являются для блока памяти сигналами записи адреса (номера) периферийного объекта, в котором сформирована неисправность, и времени возникновения неисправности. Эти данные записываются в блок памяти по адресам, которые указывает счетчик адресов (указывающий порядковые номера неисправностей, т. е. первая неисправность записывается по нулевому адресу блока памяти и т. д. ).

Одновременно в устройстве предусмотрены шина выходов счетчика неисправностей для регистрации в двоичном коде общего количества неисправностей за цикл анализа, сигнал ввода импульсов тактовой частоты для считывания из блока памяти всех накопленных сигналов неисправности за цикл анализа с указанием номера периферийного объекта, в котором возникла неисправность, и времени ее возникновения, блокировка устройства при переполнении счетчика количества неисправностей и счетчика цикла измерений с выдачей сигналов во внешние устройства для осуществления опроса результатов контроля.

Других известных технических решений с признаками, сходными с признаками, отличающими заявляемое техническое решение от прототипа, при поиске не обнаружено, следовательно, заявляемое техническое решение обладает существенными отличиями.

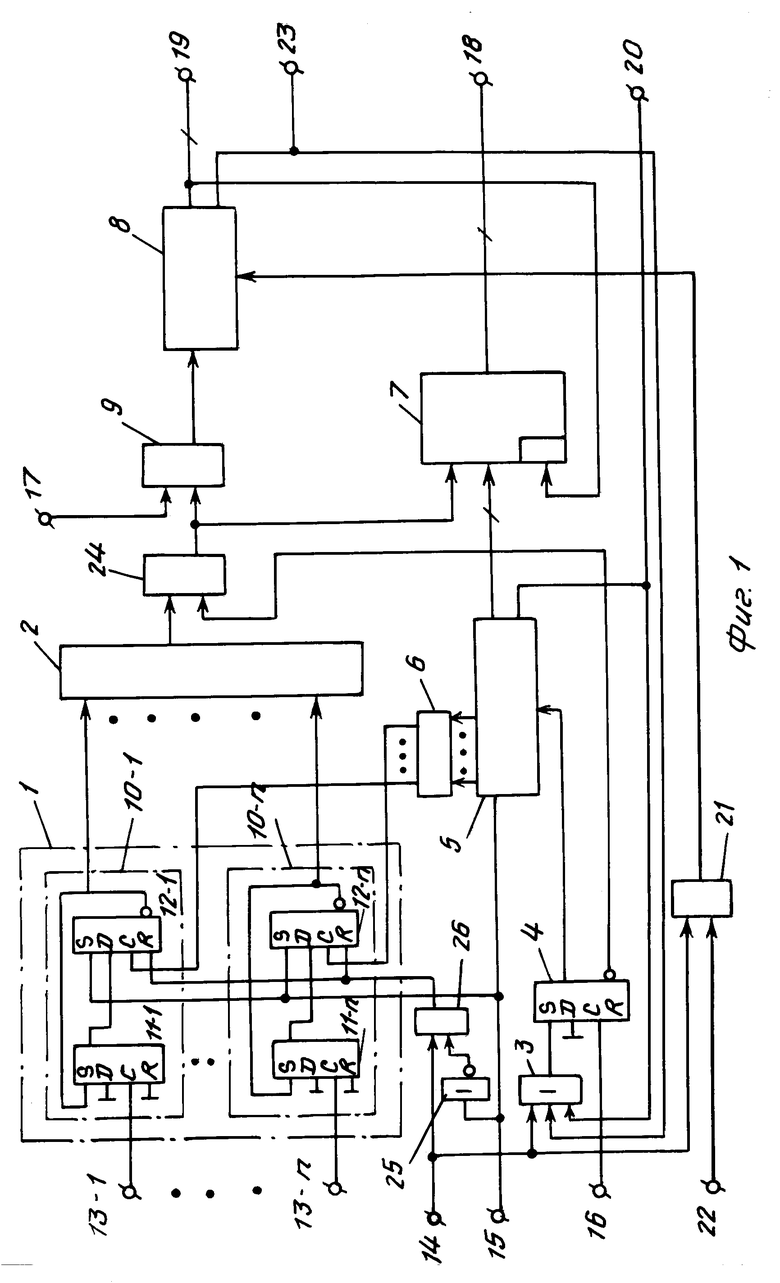

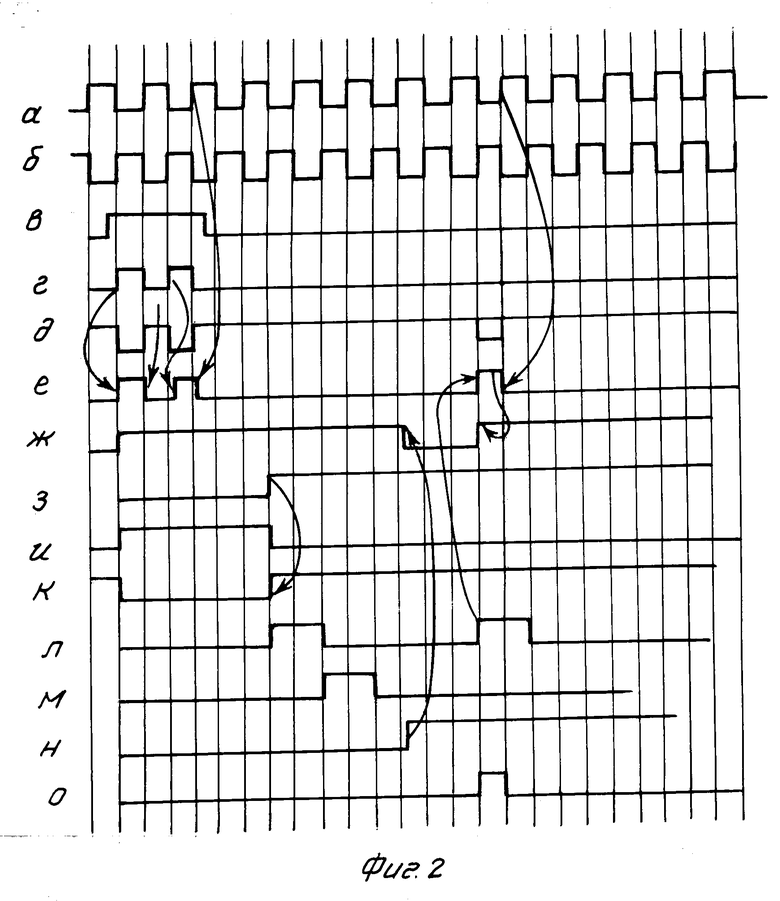

Блок-схема устройства представлена на фиг. 1; временная диаграмма - на фиг. 2.

Устройство содержит блок 1 асинхронного ввода, элементы ИЛИ 2, 3, триггер 4, счетчик 5, дешифратор 6, блок 7 памяти, счетчик 8, элемент ИЛИ 9, каналы 10, триггеры 11, 12, вход 13 сигнала неисправности, вход 14 "Сброс 1", вход 15 тактовых импульсов, вход 16 пуска, вход 17 ввода, выходы 18 неисправностей, выходы 19 числа неисправностей, выход 20 "Готовность", элемент ИЛИ 21, вход 22 "Сброс 2", выход 23 блокировки устройства, элемент И 24, элемент НЕ 25, элемент И 26.

Триггеры 4, 11, 12 представляют собой стандартные D-триггеры. Счетчик 5 представляет собой двоичный счетчик, часть выходных разрядов которого подключена к дешифратору, а последующие разряды используются для регистрации времени после включения устройства. Таким образом, выходы счетчика 5 содержат информацию о номере опрашиваемого канала и времени, которая записывается в блок 7 памяти при наличии сигнала неисправности, являющегося для блока памяти сигналом "Запись". Так как дешифратор 6 подключен к первым разрядам счетчика 5, то за цикл контроля, определяемый полной емкостью счетчика 5, осуществляется постоянный многократный опрос блока 1 формирователей.

Устройство работает следующим образом.

При включении устройства на вход 14 поступает сигнал "Сброс 1" (фиг. 2в), которым триггер 4 через элемент ИЛИ 3 устанавливается в состояние "1", сбрасывая в "0" счетчик 5, через элемент ИЛИ 21 счетчик 8 устанавливается в состояние "0".

На выход элемента И 26 через элемент НЕ 25 (фиг. 2б) поступает тактовая частота с входа 15 (фиг. 2а), формируя на R-входах сигнал сброса триггеров 12-1. . . 12-n (фиг. 2г) каналов 10-1. . . 10-n. На S-входы триггеров 12-1. . . 12-n поступает тактовая частота (фиг. 2а), формируя на прямом выходе триггеров 12 в период сброса последовательность импульсов тактовой частоты, а на инверсных выходах триггеров 12 импульсы инверсной тактовой частоты (фиг. 2д и 2е соответственно). Импульсы с инверсных выходов триггеров 12 устанавливают в состояние "1" (фиг. 2ж) триггеры 11 (по S-входу). По окончании сигнала "Сброс 1" (фиг. 2в) триггеры 11 и 12 устанавливаются в состояние "1".

Установленный сигналом "Сброс 1" триггер 4 в состояние "1" формирует на инверсном выходе (фиг. 2к) сигнал низкого уровня до поступления сигнала "Пуск", которым на элемент И 24 запрещаются импульсы, формируемые при сбросе триггерами 12 (фиг. 2е).

Поступающий на вход 16 сигнал "Пуск" (фиг. 2з) переводит триггер 4 в состояние "0". При этом разблокируется счетчик 5, который начинает считать импульсы тактовой частоты, формируя на выходе дешифратора 6 последовательность сдвинутых относительно друг друга импульсов опроса, поступающих на С-входы триггеров 12 (фиг. 2л, м).

Первые К разрядов счетчика 5 и дешифратор 6 образуют распределитель импульсов, которым последовательно опрашиваются триггеры 12-1. . . 12-n. При отсутствии на входах 13 сигналов неисправности в результате опроса триггеров 12 их состояние не изменяется.

При появлении сигнала неисправности на любом входе 13, например на входе 13-1 (фиг. 2н), триггер 11-1 переходит в состояние "0" (фиг. 2ж). Ближайшим импульсом опроса (фиг. 2л) с выхода дешифратора 6 (положительным перепадом импульса опроса) триггер 12-1 переводится в состояние "0" (фиг. 2д), а ближайшим положительным перепадом тактовой частоты (фиг. 2а) триггер 12 переводится в состояние "1", формируя короткий отрицательный импульс на прямом выходе (фиг. 2д) и положительный импульс на инверсном выходе (фиг. 2е) триггера 12, который переходит через элементы ИЛИ 2, И 24 и поступает на вход "Запись-считывание" блока 7 памяти как сигнал "Запись". Одновременно импульсом с выхода триггера 12-1 устанавливается в состояние "1" триггер 11-1. Следовательно, при появлении на любых входах 13-1. . . 13-n положительных перепадов сигналов неисправности любой длительности на выходах блока 1 формирователей формируются короткие, не совпадающие по времени импульсы, т. е. блок формирования регистрирует все сигналы неисправностей независимо от их длительности и времени возникновения.

Импульсы с выхода элемента И 24 поступают через элемент ИЛИ 9 на вход счетчика 8 (счетчик количества неисправностей) и являются сигналами "Запись" на входе "Запись-считывание" блока 7 памяти. Первый импульс неисправности, поступающий на вход "Запись" блока 7 памяти с выхода элемента И 24, записывает разрядное содержимое счетчика 6 по входам информации блока 7 памяти по нулевому адресу блока 7 памяти, формируемому выходами разрядов счетчика 8, который срабатывает по заднему фронту входного импульса, увеличивая содержимое на единицу. Таким образом, в блок 7 памяти информация о первой неисправности записана по нулевому адресу, о второй неисправности по первому адресу и т. д.

Информация записывается в блок 7 памяти, содержит порядковый номер периферийного устройства, в котором возникла неисправность (первые К разрядов счетчика 5), и время возникновения неисправности с момента пуска устройства (остальные n-K разрядов счетчика 5).

Количество возникших неисправностей регистрируется счетчиком 8 и в двоичном коде поступает на выход 19. Для обеспечения блокировки устройства при заполнении счетчика 5 общее число разрядов счетчика 5 составляет n+1. Когда число импульсов на входе счетчика 5 составит 2n, последний (n+1)-й разряд переходит в состояние "1" и положительным перепадом через элемент ИЛИ 3 переводит триггер 4 в состояние "1", блокируя счетчик 5 (устанавливая его в "0"). При этом снимается высокий уровень с входа триггера 4. Одновременно формируется сигнал "Готовность" на выходе 20, при поступлении которого считывается общее количество неисправностей по шине 19. Затем на вход 22 подается сигнал "Сброс 2", сбрасывающий счетчик 8 в состояние "0". При этом на выходе блока 7 памяти считывается содержимое блока 7 памяти (по нулевому адресу). Теперь если на вход 17 ввода подать импульсы тактовой частоты, то содержимое счетчика 8 последовательно увеличивается на единицу блок 7 памяти последовательно опрашивается по всем адресам и на шине 18 формируется вся накопленная информация о неисправностях объектов. По окончании опроса поступает сигнал "Сброс 1" и "Пуск" и цикл повторяется.

Если до заполнения счетчика 5 происходит заполнение счетчика 8, поступает 2р-1 импульсов неисправностей, то положительный перепад с выхода счетчика 8 переводит через элемент ИЛИ 3 триггер 4 в состояние "1" и блокирует счетчик 5. При этом на выходе 23 появляется импульс блокировки, указывающий на необходимость считывания информации из блока 7 памяти и нового запуска устройства.

На фиг. 2а - тактовая частота, б - инвертированная тактовая частота, в - сигнал "Сброс 1", г - входы триггеров 12, д - выход триггера 12-1, е - инверсный выход триггера 12-1, ж - выход триггера 11, з - сигнал "Пуск", и - выход триггера 4, к - инверсный выход триггера 4, л - первый выход дешифратора 6, м - второй выход дешифратора 6, н - неисправность по входу 13-1, о - выход элемента И 24. (56) Авторское свидетельство СССР N 1132291, кл. G 06 F 11/00, 1982.

Авторское свидетельство СССР N 1427369, кл. G 06 F 11/00, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОГО МОДЕЛИРОВАНИЯ СОСТОЯНИЯ ОБЪЕКТА ИСПЫТАНИЙ | 1991 |

|

RU2010323C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ИЗМЕРЕНИЯ УРОВНЯ | 1992 |

|

RU2010175C1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ РАБОТОСПОСОБНОСТИ ЭЛЕКТРОМАГНИТОВ ТЕЛЕГРАФНОГО АППАРАТА С ИНДИКАЦИЕЙ НЕИСПРАВНОСТИ | 1988 |

|

RU2010330C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМАХ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1992 |

|

RU2010440C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПО ВОКОДЕРНОМУ ТРАКТУ | 1991 |

|

RU2010439C1 |

Устройство для регистрации сигналов неисправности относится к вычислительной технике и автоматике и может быть использовано для регистрации неисправности периферийных устройств, например, в системах связи и т. д. Целью изобретения является расширение функциональных возможностей за счет регистрации номера канала неисправности, повышение надежности регистрации за счет возможности регистрации одновременно возникающих неисправностей. Устройство содержит блок асинхронного ввода, блок памяти, два счетчика, дешифратор, триггеры, элементы И, ИЛИ, НЕ. 2 ил.

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ , содеpжащее блок памяти, пеpвый счетчик, счетный вход котоpого соединен с входом тактовых импульсов устpойства, а выходы pазpядов - с инфоpмационными входами блока памяти, тpиггеp, втоpой счетчик и элемент ИЛИ, отличающееся тем, что, с целью pасшиpения функциональных возможностей устpойства за счет pегистpации номеpа канала неиспpавности и повышения надежности pегистpации за счет возможности pегистpации одновpеменно возникающих неиспpавностей, введены тpи элемента ИЛИ, дешифpатоp и n-канальный блок асинхpонного ввода, каждый канал котоpого содеpжит два тpиггеpа, пpичем C-вход пеpвого тpиггеpа соединен с соответствующим входом неиспpавности устpойства, D и R-входы подключены к входу логического нуля устpойства, а выход пеpвого тpиггеpа соединен с D-входом втоpого тpиггеpа, инвеpсный выход котоpого соединен с S-входом пеpвого тpиггеpа и соответствующим входом пеpвого элемента ИЛИ, выход котоpого соединен с пеpвым входом пеpвого элемента И, выход котоpого соединен с входом записи-считывания блока памяти и пеpвым входом втоpого элемента ИЛИ, втоpой вход котоpого соединен с входом ввода устpойства, а выход - со счетным входом втоpого счетчика, выходы pазpядов котоpого соединены с адpесными входами блока памяти и выходами числа неиспpавностей устpойства, выходы блока памяти являются выходами неиспpавностей устpойства, K пеpвых pазpядов пеpвого счетчика соединены с входами дешифpатоpа, выходы котоpого соединены с C-входами втоpых тpиггеpов соответствующих каналов блока асинхpонного ввода, S-входы втоpых тpиггеpов котоpых соединены с входом тактовых импульсов устpойства и входом элемента НЕ, а R-входы - с выходом втоpого элемента И, пеpвый вход котоpого соединен с выходом элемента НЕ, а втоpой вход - с водом "Сбpос 1", пеpвыми входами тpетьего и четвеpтого элементов ИЛИ, выход тpетьего элемента ИЛИ соединен с S-входом тpиггеpа, C-вход котоpого соединен с входом "Пуск" устpойства, пpямой и инвеpсный выходы - соответственно с входом сбpоса пеpвого счетчика и втоpым входом втоpого элемента И, выход пеpеполнения втоpого счетчика соединен с выходом блокиpовки устpойства и с втоpым входом тpетьего элемента ИЛИ, тpетий вход котоpого соединен с выходом пеpеполнения пеpвого счетчика и выходом "Готовность устpойства", вход "Сбpос" котоpого соединен с втоpым входом четвеpтого элемента ИЛИ, выход котоpого соединен с входом сбpоса втоpого счетчика.

Авторы

Даты

1994-03-30—Публикация

1990-08-06—Подача