Изобретение относится к технике обработки цифровых данных, в частности к устройствам для обнаружения ошибок, и может найти применение в цифровых системах передачи.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля импульсных последовательностей, содержащее два триггера и два элемента И-НЕ. Недостатком устройства является малая точность результата контроля последовательностей импульсов.

Целью изобретения является повышение точности результата контроля импульсных последовательностей.

Сопоставительный анализ совокупности существенных признаков, характеризующей заявляемое техническое решение, показал, что оно соответствует критерию "новизна".

Сравнение заявляемого технического решения не только с прототипом, но и с другими техническими решениями в данной области техники не позволило выявить в них признаки, отличающие заявленное техническое решение от прототипа, что позволяет сделать вывод о его соответствии критерию "существенные отличия".

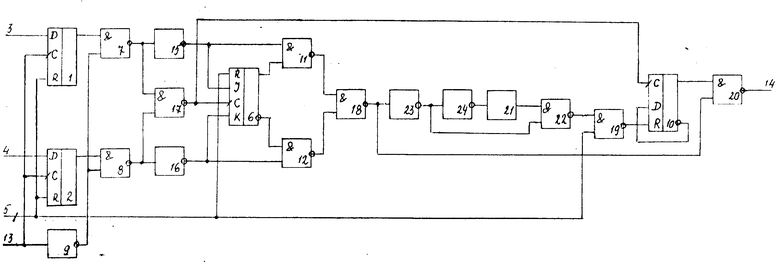

Изобретение поясняется чертежом.

Устройство содержит триггеры 1 и 2, входы 3, 4, 5, триггер 6, элементы И-НЕ 7, 8, элемент НЕ 9, триггер 10, элементы И-НЕ 11, 12, вход 13, выход 14, элементы НЕ 15, 16, элементы И-НЕ 17, 18, 19, 20, 22, интегрирующий элемент 21, элементы НЕ 23, 24.

Устройство работает следующим образом.

Импульсные последовательности поступают на D-входы триггеров 1 и 2 в виде сигналов +1 и -1 при сопровождении тактовой последовательности по входу 13. Триггеры воздействуют на первые входы соответственно элементов И 7, и 8, на вторые входы которых поступает через элемент НЕ 9 последовательность тактовых импульсов. Через элемент И-НЕ 17 и элементы НЕ 15 и 16 эти сигналы воздействуют на I- и К-входы триггера 6 и на первые входы соответственно элементов И-НЕ 11 и 12. При этом триггер 6 формирует сигналы управления, поступающие с его прямого и инверсного выходов на вторые входы элементов И-НЕ 11 и 12.

Если по каналу +1 приходит импульс, то после его окончания открывается элемент И-НЕ 11 и закрывается элемент И-НЕ 12. Если по каналу -1 приходит импульс, то после его окончания закрывается элемент И-НЕ 11 и открывается элемент И-НЕ 12.

Если два или более импульсов подряд приходят по одному и тому же каналу, то после первого импульса соответствующий этому каналу элемент И-НЕ 11 или 12 открывается и все последующие импульсы поступают на элемент И-НЕ 18, т. е. все импульсы, нарушающие биполярность, выделяются на выходе элемента И-НЕ 18, откуда поступают на второй вход элемента И-НЕ 20 и через элемент НЕ 23 непосредственно воздействуют на первый вход элемента И-НЕ 22 и через элемент НЕ 24 и интегрирующий элемент 21 на второй вход элемента И-НЕ 22. Сигнал с выхода элемента И-НЕ 22 поступает на второй вход элемента И-НЕ 19. Элементы И-НЕ 19 и 22, НЕ 23 и 24 и интегрирующий элемент 21 обеспечивают формирование узкого строба по переднему фронту импульса с выхода элемента И-НЕ 18. Узкий строб с выхода элемента И-НЕ 19 подается на R-вход четвертого триггера 10, работающего в режиме деления на два. При поступлении каждого строба на прямом выходе триггера 10 устанавливается состояние логического "0". На С-вход триггера 10 подается сигнал с выхода элемента И-НЕ 17, в котором объединены все импульсы, поступающие по обоим каналам.

При поступлении нечетного импульса триггер 10 переключается в состояние логического "1", а при поступлении четного импульса - в состояние логического "0". Сигнал с прямого выхода триггера 10 поступает на первый вход элемента И-НЕ 20, на второй вход которого поступает сигнал с элемента И-НЕ 18, представляющий собой импульсы, нарушающие полярность.

Если в сигнале, поступающем на С-вход триггера 10, какой-либо из импульсов, нарушающих биполярность, является нечетным, то триггер 10 переключается в состояние логической "1", что обеспечивает пропускание на выходную шину через элемент И-НЕ 20 импульса, поступающего на его второй вход с выхода элемента И-НЕ 18.

Узкий строб, поступающий по окончании импульса, нарушающего биполярность, на R-вход триггера 10, переключает его в состояние логического "0", т. е. устанавливает его в исходное состояние, а следующий импульс сигнала с выхода элемента И-НЕ 17 считается нечетным. Импульсы, прошедшие через элемент И-НЕ 20 на выход 14, - это импульсы, нарушающие биполярность. Они являются нечетными и символизируют наличие ошибок. (56) Авторское свидетельство СССР N 1223232, кл. G 06 F 11/16, 1985.

Авторское свидетельство СССР N 1257649, кл. G 06 F 11/16, 1984.

Изобретение относится к технике обработки цифровых данных, в частности к устройствам для обнаружения ошибок, и может найти применение в цифровых системах передачи. Целью изобретения является повышение точности обнаружения ошибок. Устройство содержит три триггера, девять элементов И -НЕ, пять элементов НЕ, интегрирующий элемент. 1 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ , содеpжащее два тpиггеpа и два элемента И - НЕ, пpичем вход начальной установки устpойства соединен с R-входом пеpвого тpиггеpа, C-вход котоpого объединен с C-входом втоpого тpиггеpа, отличающееся тем, что, с целью повышения точности pезультата контpоля импульсных последовательностей, в него введены тpетий и четвеpтый тpиггеpы, элементы И - НЕ с тpетьего по девятый, пять элементов НЕ и интегpиpующий элемент, пpичем пpямой и инвеpсный выходы тpетьего тpиггеpа подключены к пеpвым входам соответственно пеpвого и втоpого элементов И - НЕ, а R-вход соединен с R-входом втоpого тpиггеpа и входом начальной установки устpойства, пеpвые входы тpетьего и четвеpтого элементов И - НЕ соединены с пpямыми выходами соответственно пеpвого и втоpого тpиггеpов, D-входы котоpых соединены с входами соответственно пеpвой и втоpой импульсных последовательностей устpойства, вход тактовых импульсов устpойства соединен с C-входом пеpвого тpиггеpа и чеpез пеpвый элемент НЕ с втоpыми входами тpетьего и четвеpтого элементов И - НЕ и к входам соответственно втоpого и тpетьего элементов НЕ, выходы котоpых подключены соответственно к J- и K-входам тpетьего тpиггеpа и втоpым входам соответственно пеpвого и втоpого элементов И - НЕ, выходы котоpых соединены с входами шестого элемента И - НЕ, выход котоpого соединен с пеpвым входом седьмого элемента И - НЕ и с входом четвеpтого элемента НЕ, выход котоpого соединен с пеpвым входом восьмого элемента И - НЕ и входом пятого элемента НЕ, выход котоpого чеpез интегpиpующий элемент соединен с втоpым входом восьмого элемента И - НЕ, выход котоpого соединен с пеpвым входом девятого элемента И - НЕ, втоpой вход котоpого подключен к входу начальной установки устpойства, а выход соединен с R-входом четвеpтого тpиггеpа, С-вход котоpого соединен с С-входом тpетьего тpиггеpа и выходом пятого элемента И - НЕ, D-вход объединен с его инвеpсным выходом, а пpямой выход соединен с втоpым входом седьмого элемента И - НЕ, выход котоpого является выходом устpойства.

Авторы

Даты

1994-03-30—Публикация

1991-01-02—Подача