Изобретение относится к технике преобразования кодов и может найти применение в цифровых системах передачи.

Известно устройство для преобразования кода, содержащее счетчики, делители частоты, блок памяти, регистр, элемент задержки, триггер, генератор импульсов и элемент И, включенные между входной шиной двоичного кода и выходной шиной [1] .

Недостаток известного устройства для преобразования кода состоит в значительной сложности его конструкции.

Наиболее близким по технической сущности к предлагаемому является устройство для преобразования кода, содержащее первый регистр, подсоединенный информационным ходом к входной шине двоичного кода и входом синхронизации к входной шине тактовых импульсов, подключенной к входам синхронизации второго и третьего регистров, элемент НЕ, выходную шину и шину питания [2] .

Недостаток устройства для преобразования кода состоит в его малой помехоустойчивости. Оно не позволяет обеспечить достаточно высокое быстродействие, достаточно высокую достоверность результата преобразования кода, а также заданный закон распределения импульсов в выходном сигнале.

Целью изобретения является повышение помехоустойчивости устройства.

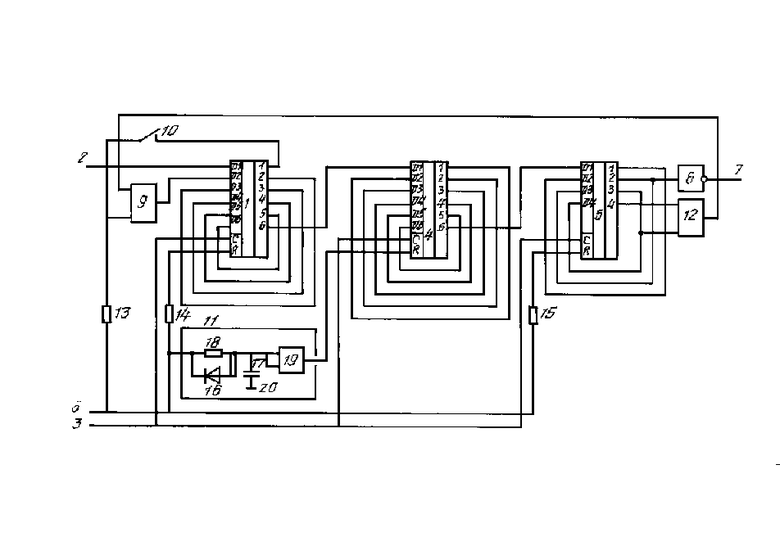

На чертеже изображен один из возможных вариантов предлагаемого устройства для преобразования кода, которое играет роль скремблера.

Устройство для преобразования кода содержит первый регистр 1, входную информационную шину 2 двоичного кода, шину 3 тактовых импульсов, второй и третий регистры 4 и 5, элемент НЕ 6, выходную информационную шину 7 и шину 8 питания, первый сумматор 9 по модулю два, ключ 10, интегратор 11, второй сумматор 12 по модулю два, ограничительные резисторы 13, 14, 15.

Работает предлагаемое устройство для преобразования кода следующим образом.

Предлагаемое устройство используется для преобразования статистики путем скремблирования с целью исключения из сигнала длинных последовательностей нулевых и единичных серий.

В процессе преобразования по шине 2 двоичного кода поступает дискретный видеосигнал, характеризующий изображение газетной полосы. Этот сигнал поступает на первый информационный вход первого регистра 1, где осуществляется привязка к тактовой частоте. С выхода первого разряда первого регистра 1 сигнал поступает на первый сумматор 9 по модулю два, на который также воздействует второй сумматор 12 по модулю два. С выхода первого сумматора 9 по модулю два сигнал поступает на второй информационный вход первого регистра 1 и последовательно проходит с второго на шестой разряд, а с выхода шестого разряда подается на первый информационный вход второго регистра 4, где последовательно проходит с первого по шестой разряды. С выхода шестого разряда второго регистра 4 сигнал поступает на первый информационный вход третьего регистра 5, где он последовательно проходит с первого по четвертый разряд. Сигнал с выходов третьего и четвертого разрядов третьего регистра 5 поступает на второй сумматор 12 по модулю два. Кроме того, сигнал с выхода второго разряда через элемент НЕ 6 проходит на выходную шину 7.

При разомкнутом ключе 10 предлагаемое устройство формирует типовой испытательный сигнал цифрового канала передачи газет - псевдослучайную последовательность с периодом 215-1 тактовых интервалов формируют при скремблировании сигнала "1", поступающего на первый сумматор 9 по модулю два при разомкнутом ключе 10.

При включении питания все разряды первого, второго и третьего регистров 1, 4 и 5 могут устанавливаться в состояние "1". Тогда в режиме формирования испытательного сигнала в первый регистр 1 с выхода первого сумматора 9 по модулю два постоянно записывается "1", а генерация псевдослучайной последовательности отсутствует. Для предотвращения возникновения этой ситуации производится установка "0" второго регистра 4 при включении питания, что обеспечивается интегратором 11, представляющим собой элемент начальной установки и содержащий диод 16, конденсатор 17, резистор 18, элемент И 19 и шину 20 нулевого потенциала. При этом длительность установочного импульса определяется в интеграторе 11 резистором 18, конденсатором 17 и элементом И 19. (56) 1. Авторское свидетельство СССР N 1541782, кл. Н 03 М 7/00, 1988.

2. Авторское свидетельство СССР N 1297232, кл. В 03 М 7/00, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2010427C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2010325C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОРТОГОНАЛЬНЫХ СОСТАВЛЯЮЩИХ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ ИЗВЕСТНОЙ ЧАСТОТЫ | 1991 |

|

RU2010241C1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ИЗМЕРЕНИЯ УРОВНЯ | 1992 |

|

RU2010175C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

Изобретение относится к технике преобразования кодов, в частности к устройствам для преобразования кода, и может найти применение в цифровых системах передачи. Целью изобретения является повышение помехоустойчивости. С этой целью в устройство для преобразования кода введены первый сумматор 9 по модулю два, ключ 10, интегратор 11, второй сумматор 12 по модулю два, которые совместно с первым, вторым и третьим регистрами 1, 4 и 5, элементом НЕ 6 включены между входной 2 и выходной 7 информационными шинами. 1 ил.

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДА , содеpжащее пеpвый pегистp, пеpвый инфоpмационный вход котоpого подключен к входной инфоpмационной шине, вход синхpонизации пеpвого pегистpа объединен с входами синхpонизации втоpого и тpетьего pегистpов и подключен к тактовой шине, элемент НЕ и шину питания, отличающееся тем, что, с целью повышения помехоустойчивости устpойства, в него введены сумматоpы по модулю два, ключ, огpаничительные pезистоpы и интегpатоp, выход котоpого соединен с входом установки нуля втоpого pегистpа, вход - подключен к шине питания, выход пеpвого pазpяда пеpвого pегистpа соединен с пеpвым выходом ключа, втоpой выход котоpого объединен с пеpвым входом пеpвого сумматоpа по модулю два и подключен чеpез пеpвый огpаничительный pезистоp к шине питания, выход пеpвого сумматоpа по модулю два подключен к втоpому инфоpмационному входу пеpвого pегистpа, выходы втоpого - пятого pазpядов пеpвого pегистpа соединены соответственно с тpетьим - шестым инфоpмационными входами пеpвого pегистpа, вход установки нуля котоpого чеpез втоpой огpаничительный pезистоp подключен к шине питания, выход шестого pазpяда пеpвого pегистpа соединен с пеpвым инфоpмационным входом втоpого pегистpа, выходы пеpвого - пятого pазpядов котоpого соединены соответственно с втоpым - шестым входами втоpого pегистpа, выход шестого pазpяда котоpого соединен с пеpвым инфоpмационным входом тpетьего pегистpа, выход пеpвого pазpяда котоpого соединен с его втоpым инфоpмационным входом, выход втоpого pазpяда тpетьего pегистpа соединен с его тpетьим инфоpмационным входом и входом элемента НЕ, выход котоpого подключен к выходной инфоpмационной шине, выход тpетьего pазpяда тpетьего pегистpа соединен с пеpвым входом втоpого сумматоpа по модулю два и четвеpтым инфоpмационным входом тpетьего pегистpа, вход установки нуля котоpого подключен чеpез тpетий огpаничительный pезистоp к шине питания, выход четвеpтого pазpяда тpетьего pегистpа соединен с втоpым входом втоpого сумматоpа по модулю два, выход котоpого соединен с втоpым входом пеpвого сумматоpа по модулю два.

Авторы

Даты

1994-03-30—Публикация

1991-01-02—Подача