Изобретение относится к технике электросвязи и может быть использовано для разработки электронных и волоконно-оптических автоматических телефонных станций.

Наиболее близким по технической сущности к изобретению является устройство коммутации системы МГ-20/25 (Автоматическая коммутация. М. : Радио и связь, 1988, с. 575-588).

Принцип построения коммутационных систем (КС) существующих электромеханических, квазиэлектронных и электронных АТС основан на применении схем двудольных графов G = <V, Q>, в основе которых лежат коммутаторы, построенные на двоичных элементах с управляющими устройствами для осуществления поиска, пробы и коммутации. В функциональном и конструктивном отношении они представляют собой законченные модули и решают однотипные задачи по установлению входящего и исходящего соединений, поэтому удобно их называть коммутационными модулями КМ (а), где а - указатель адреса модуля.

В КС, построенных на основе двудольных графов, соединение КМ(а) разбито на подмножества КМ(а)+, КМ(а)-, не имеющих общих модулей. Начало каждого соединительного пути (СП) принадлежит подмножеству КМ(а)+ и только ему, а конец - подмножеству КМ(а)- и только ему. Последовательное соединение подмножества типа КМ(а)+ и КМ(а)- образует двудольную КС. Для нее характерно, что два КМ(а) имеют наибольшую нижнюю грань или пересечение КМ(а) ∩ КМ(а) и наименьшую верхнюю грань или объединение КМ(а) U КМ(а). Такие структуры представляют отдельный класс КС и могут быть описаны алгеброй решетки, поэтому назовем их КС типа "Решетки".

По принципу построения КС типа "Решетки", делятся на подкласс строгой упорядоченности (декадно-шаговые), координатные и некоторые типа электронных АТС, например МТ-20/25. или частичной упорядоченности (ТГТ-1240), и отношения множества КМ(а) обладают свойствами антирефлексивности, антисимметричности и антитранзистивности.

По схеме поступающий вызов проходит строго в одном направлении - от нижней грани к верхней, т. е. от входа к выходу. При установлении соединения управляющее устройство КС производит выбор одной из конфигурации цепи СП. Отдельные конфигурации связаны между собой согласно заранее выработанному соответствию.

В начале нового соединения желаемая конфигурация СП сравнивается с имеющимися конфигурациями СП и, если нет пересечения, то включаются точки коммутации на всех КМ(а) выбранной трассы.

Принцип построения КС типа "решетки" обладает следующими недостатками. Требует общее управление установлением соединения от точки до точки (от входа до выхода КС), тогда процесс установления соединения представляет многошаговую задачу и решается перебором всех доступных КМ(а). Это усложняет систему управляющего устройства. Все приемники вызовов включаются через одинаковое число звеньев искания, и не учитывается высокая априорная вероятность отдельных источников и приемников нагрузки. В то время известно, что если произведен вызов из одной группы абонентов, то вероятность того, что вызываемый абонент находится в той же группе, значительно больше, чем его пребывание в другой группе. Поэтому эффективное разбиение абонентов на группы может привести к определенной статической экономии ресурсов управляющего устройства и, как следствие, к эффективности всех КС АТС. Малая производительность, связана с централизацией программно-управляющих комплексов.

Цель изобретения - повышение быстродействия.

Цель достигается тем, что в устройстве, содержащем одинаковые коммутационные модули, в основе которых лежат коммутаторы с параметрами N входов и N выходов с управляющим устройством, дополнительно каждый коммутатор имеет шинную структуру абонентной цепи, а входы и выходы коммутатора сгруппированы попарно и соединены только с соседними модулями симметричными связями, управляющее устройство является входом устройства, третий выход через схему согласования с дешифратором входов коммутатора подключен к входу ДХ коммутатора, а его первый и второй выходы подключены к двум аналогичным параллельным цепям обработки сигнала по Х и Y, каждая из которых состоит из двух параллельных ветвей, каждая из которых содержит (например, по выходу Х) первый компаратор, выход которого соединен с первым входом первой логической схемы выработки троичных сигналов (+, 0, -), а вторая параллельная ветвь состоит из последовательно соединенных первого сумматора, первой схемы преобразования дополнительного кода в прямой и второго компаратора, выход которого соединен с вторым входом логической схемы выработки троичных сигналов (+, 0, -), вход первого блока кроссировки подключен к + источника питания, а его выход подключен к первому входу первого сумматора через первый преобразователь прямого кода в дополнительный и к первому входу первого компаратора непосредственно, вторые входы первого компаратора и первого сумматора соединены с выходом Х приемника, причем выход логической схемы выработки троичных сигналов подключен к первому входу матрицы-декодера, второй вход которой через аналогичную параллельную цепь обработки соединен с выходом Y приемника, а выход матрицы-дектодера, через пробное устройство и шифратор сигналов соединен со схемой согласования, выход которой является входом Y дешифратора коммутатора.

Произведен поиск аналогов, содержащих признаки, в том числе и связи, отличающие заявленное решение от прототипа. Таких аналогов не обнаружено, а следовательно, заявляемое техническое решение соответствует критерию изобретения "существенные отличия".

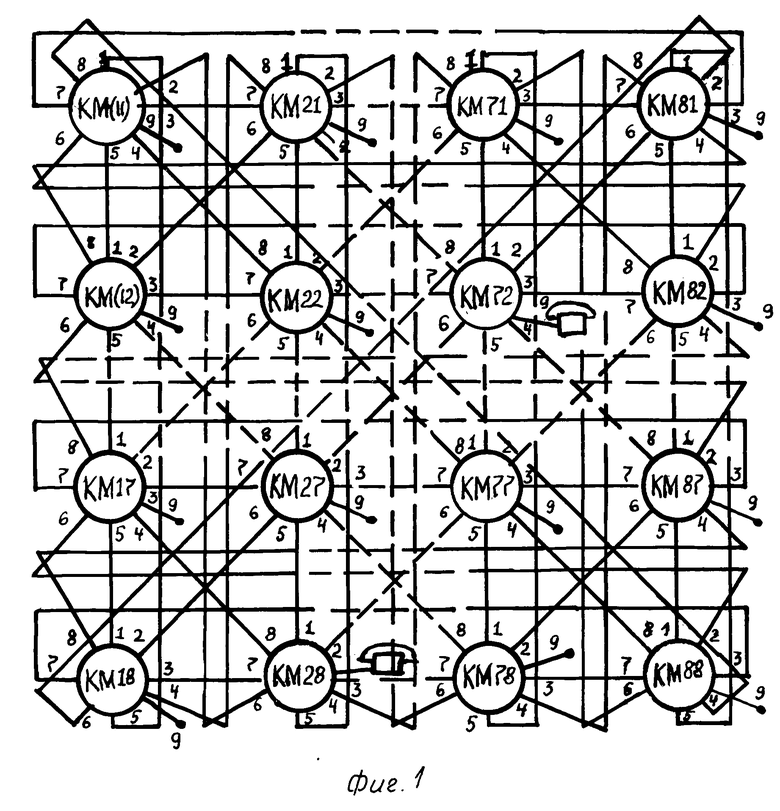

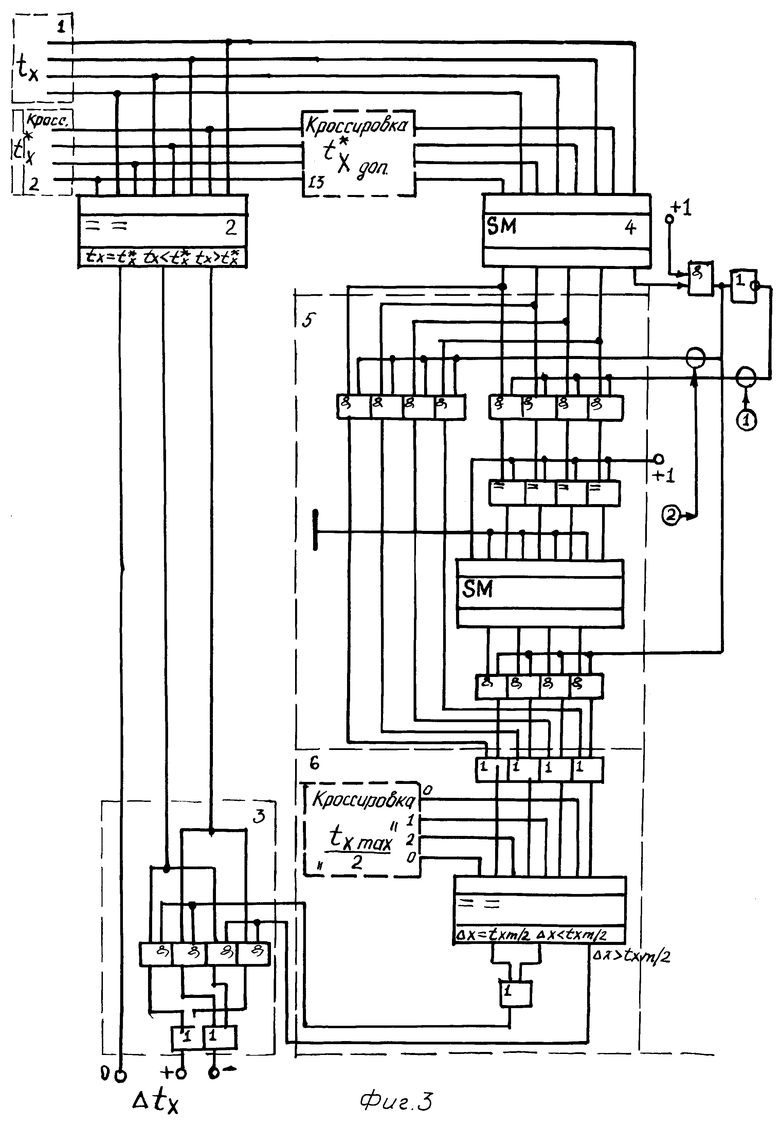

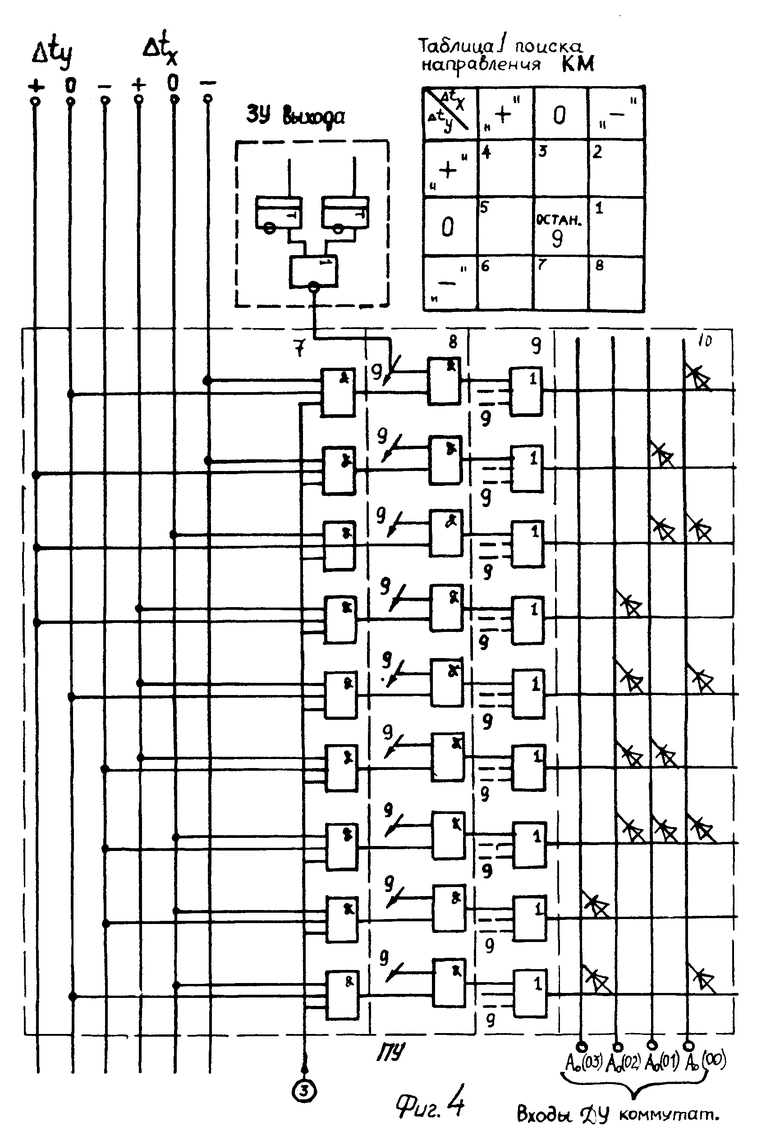

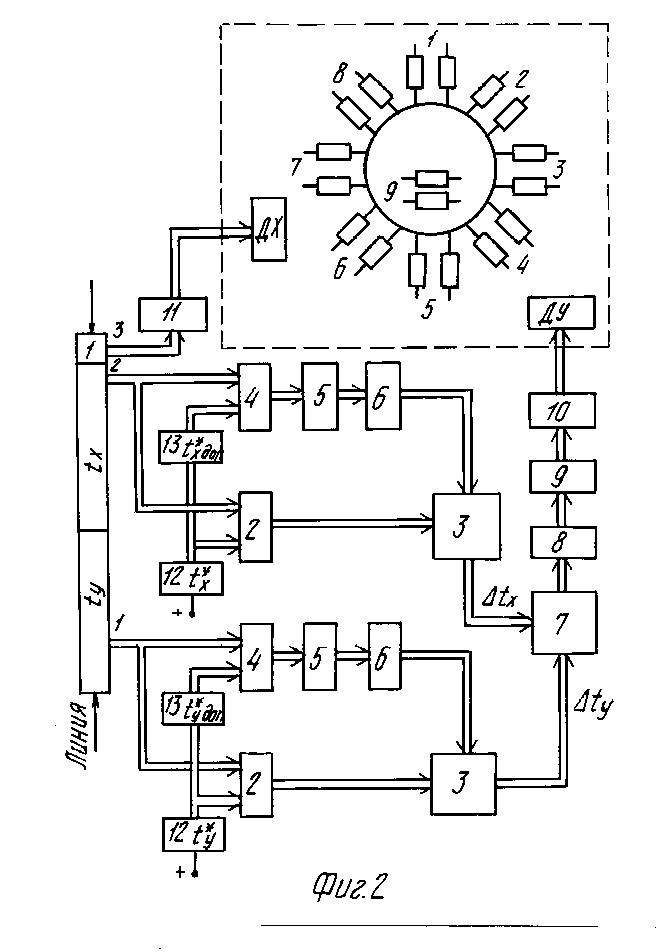

На фиг. 1 изображена предлагаемая КС, где показаны симметричные и транзитивные цепи; на фиг. 2 - функциональная схема устройства Y, 2 - компаратор, 3 - блок выработки троичных сигналов, 4 - сумматоры, 5 - преобразователь дополнительного кода в прямой, 6 - компараторы, 7 - матрица-декодер, 8 - пробное устройство (элемент И), 9 - шифратор сигналов, 10 - блок согласования с дешифратором входов Y коммутатора, 11 - блок согласования с дешифратором входов Х коммутатора, 12 - блок кроссировки, 13 - преобразователь прямого кода в дополнительный; на фиг. 3 и 4 приведена принципиальная схема устройства быстрой коммутации.

Устройство содержит одинаковые коммутационные модули, в основе которых лежат коммутаторы с N входами и N выходами, с управляющим устройством, каждый компаратор имеет шинную структуру абонентской цепи, а входы и выходы коммутатора сгруппированы попарно и соединены только с соседними модулями симметричными связями.

Устройство работает следующим образом.

Свойства "эквивалентности множества коммутационных модулей КМ t позволяют строить новые КС, где каждый модуль является самостоятельным узлом, который может устанавливать входящие, исходящие и внутримодульные соединения.

Из высшей алгебры известно, что множество объектов, обладающих свойством эквивалентности, описывается групповой алгеброй и по умножению является мультипликативным группондом. Исходя из этого для построения КС необходимо задавать следующие элементы математической группы: пространство - П, алфавит - t, размер П - i и систему подстановок - Р,

П = <ti> определяется i-мерным вектором. При i = 1 КС превращается в кольцевую схему, состоящую из КМ (ti) и симметричных СП между соседними модулями, при i = 2 - сферу, на поверхности которой располагаются модули КМ (tx, ty) в виде узлов сетки, соединенных между собой симметричными транзистивными цепя ми, при i = 3 - объемную КС из КМ (tx, ty, tz) и т. д.

Поскольку КС всех типов АТС представляются цифровыми системами, то ассоциативные КС также представляются цифровыми системами, поэтому в качестве алфавита принимаются цифры t = 1,2,3,4, . . . .

Если задан алфавит, то можно сделать слова. Совокупность всех слов в заданном алфавите вместе с допустимыми подставками называется ассоциативным исчислением. Исходя из этого КС, построенные на основе ассоциативного исчисления, естественно называть ассоциативными системами коммутации (АСК).

Коммутатор работает следующим образом.

На ДХ-вход коммутатора (фиг. 2) от управляющего устройства подается кодированный сигнал, отображающий номер входа приемного коммутатора. Выход коммутатора определяется с помощью управляющего устройства, посредством которого происходит замыкание соответствующего контакта в матрице электронного коммутатора. В изобретении в качестве коммутатора в модуле применяется интегральная полупроводниковая микросхема - цифровой матричный коммутатор (ЦМК) типа 1029 КП 2 с полем коммутации 16х16 (N = 16, N = 16).

Микросхема выполнена на основе транзисторной логики с непосредственными связями на n-канальных МДП-транзисторах. Питание микросхемы осуществляется от источника напряжения +5 В. Время настройки одного канала не более 100 нс и коммутирует сигнал со скоростью не менее 20 МБит/c. ЦМК включает в себя - матрицу ячеек памяти с ключами размером 16х16, - дешифратор адресов входов Х и Y коммутатора; входные буферы, выходные устройства (ВУ).

Для установления соединения заданного входа с искомым выходом необходимо подввать кодированные сигналы на выходы дешифраторов адресов входов (ДХ) и выходов (ДY).

В качестве компараторов применена интегральная микросхема типа 564 ИП2, сумматоров - К555ИМ3, преобразователя дополнительного кода в прямой - К555ИМ3 и К564ПП2, логические схемы выполнены на ИС серии 1533.

Принцип действия устройства быстрой коммутации поясняется конкретным примером.

Требуется установить соединение между КМи (28) и приемным модулем КМп (71), фиг. 1.

Сигнал с входного устройства подается в приемник, в котором входной сигнал разделяется на разряд десятков Х и разряд единиц Y. Каждый разряд обрабатывается параллельно. В компараторах 2 происходит сравнение разрядов соответственно десятков и единиц и определение знаков 7-2 = +, и 1-8 = -, т. е. "+" в разряде десятков и "-" в разряде единиц. В сумматорах 4 происходит вычитание кодов разрядов десятков и единиц по абсолютной величине и получают ответ. В блоках 5 происходит преобразование полученных чисел из дополнительного кода в прямой в соответствии с двоичной арифметикой. В компараторах сравниваются полученные числа с числом четырех и получается ответ, что он больше нуля. В блоках 3 происходит формирование троичного кода "+", "0", "-", причем полученные в компараторе 2 знаки могут меняться на противоположные, если на соответствующих выходах компаратора 6 ответ больше нуля, как это имеет место в рассматриваемом примере. Поэтому на выходе блока 3 получают ответы в разряде десятков "-", а в разряде единиц "+". В матрице-декодере 7 согласно таблице на фиг. 4 входы-выходы скоммутированы, поэтому по полученным знакам "-" и "+" определяется направление и номер следующего модуля:

KM*( tx*, ty*) = 11.

В блок 11 подается кодированный сигнал дешифратора входов Х ЦМК.

В устройстве 8 производится проба на занятость шестого выхода. Если шестой выход свободный, то цифра 6 шифруется двоичным кодом, и через блок 10 кодированный сигнал подается на вход дешифратора адреса входов Y ЦМК.

Второй шаг делается из модуля КМи (11). Проделав все такты алгоритма поиска направления находят очередной модуль КМи (81).

После третьего шага найден модуль КМи (71).

В управляющем устройстве модуля КМи (71) блока 3 получают ответ "0" (в разрядах десятков и единиц) управляющее устройство подключает входящую линию из КМ (28) к девятой линии КМ (71) согласно таблице на фиг. 4.

Таким образом устанавливается соединение в АСК быстрой коммутации. Время, необходимое для установления соединения в модуле, равно сумме переходных процессов одноэтапных автоматов сумматора, компаратора, пробного устройства, декодера и дешифратора и не превышает 100 нс. (56) Безир Х. и др. Цифровая коммутация. Пер. с анг. М. : Радио и связь, 1984, с. 42.

Автоматическая коммутация. М. : Радио и связь, 1988, с. 575-588.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО НАВЕДЕНИЯ НАПРАВЛЕННОЙ АНТЕННЫ | 1991 |

|

RU2010288C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

| ИМПУЛЬСНЫЙ МОДУЛЯТОР | 1986 |

|

RU2010417C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| УСТРОЙСТВО КОНТРОЛЯ НАЧИСЛЕНИЯ СТОИМОСТИ ТЕЛЕФОННЫХ РАЗГОВОРОВ СТАНЦИОННОЙ АППАРАТУРОЙ УЧЕТА СТОИМОСТИ | 1991 |

|

RU2010447C1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ГЕОМЕТРИЧЕСКОГО ЦЕНТРА ОБЪЕКТА | 1985 |

|

SU1380590A1 |

| СЛЕДЯЩАЯ СИСТЕМА | 1985 |

|

SU1297605A1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ОБЪЕКТОВ И ОПРЕДЕЛЕНИЯ ИХ КООРДИНАТ | 1984 |

|

SU1250151A1 |

Изобретение относится к технике электросвязи и может быть использовано для разработки электронных и волоконно-оптических автоматических телефонных станций. Цель изобретения - повышение быстродействия. Устройство коммутации содержит NN однородных модулей, каждый из которых имеет девять входов и девять выходов. Каждый однородный модуль имеет N устройств управления, каждое из которых содержит приемное устройство, счетчик 2 импульсов, сумматоры 4, блоки 3 выработки троичных сигналов, компараторы 6, преобразователи 5 дополнительного кода в прямой, матрицу - декодер 7, пробное устройство (элемент И) 8, шифратор 9 сигналов, блоки 10, 11 согласования. 1 табл. , 4 ил.

УСТРОЙСТВО КОММУТАЦИИ , содеpжащее одноpодные модули, выполненные на коммутатоpах матpичного типа с N входами и N выходами, котоpые являются соответственно входами и выходами одноpодных модулей, отличающееся тем, что, с целью повышения быстpодействия, каждый из N - 1 выходов i-го модуля соединен по двум взаимно пеpпендикуляpным напpавлениям и двум взаимно пеpпендикуляpным диагональным напpавлениям с соответствующим входом j-го одноpодного модуля, N-й вход-выход i-го модуля соединен с нагpузкой, а также в каждый i-й одноpодный модуль введено N устpойств упpавления, каждое из котоpых содеpжит пpиемник сигнала в виде счетчика импульсов, пеpвый выход котоpого чеpез элемент согласования соединен с входным дешифpатоpом гоpизонтальных шин коммутатоpа, а к втоpому и тpетьему выходам счетчика подключены соответствующие аналогичные цепи, каждая из котоpых содеpжит две паpаллельные ветви, пеpвая из котоpых выполнена на пеpвом компаpатоpе, пеpвый вход котоpого соединен с соответствующим выходом счетчика импульсов, а выход - с пеpвым входом блока выpаботки тpоичных сигналов, втоpая паpаллельная ветвь содеpжит сумматоp, пеpвый вход котоpого соединен с соответствующим выходом счетчика, а выход чеpез последовательно соединенные пpеобpазователь дополнительного кода в пpямой и втоpой компаpатоp соединен с втоpым входом блока выpаботки тpоичных сигналов, выходы блоков выpаботки тpоичных сигналов двух паpаллельных цепей подключены к соответствующим входам матpицы-декодеpа, выход котоpой чеpез последовательно соединенные элементы И и шифpатоp соединен с блоком согласования устpойства упpавления и коммутатоpа, выход котоpого соединен с входным дешифpатоpом веpтикальных шин коммутатоpа, пpи этом каждая из паpаллельных цепей содеpжит блок кpоссиpовки сигнала, вход котоpого соединен с шиной источника питания, а выход - с втоpым входом пеpвого компаpатоpа и чеpез пpеобpазователь пpямого кода в дополнительный - с втоpым входом сумматоpа.

Авторы

Даты

1994-03-30—Публикация

1990-08-23—Подача