Изобретение относится к радиотехнике и предназначено для использования в синхронных адресных системах связи.

Известны устройства приема и декодирования многочастотных сигналов, используемые в радиотехнических установках для обнаружения дискретных частотных (ДЧ) сигналов.

Устройство, описанное в патенте США N 4189678, ввиду технической трудности смены алгоритма частотно-временного кодирования, который заложен в коммутации соответствующих отводов линии задержки, не позволяет обеспечить работу в режиме быстрой смены сигналов, что затрудняет его использование в аппаратуре синхронных систем связи.

Из известных устройств приема данных, передаваемых последовательным частотным кодом, наиболее близким техническим решением к изобретению является устройство, которое содержит фильтр, компаратор, делитель частоты, первый, второй, третий счетчики, блок вычисления кода длительности входного сигнала, первый, второй коммутаторы, блок постоянной памяти, первый блок оперативной памяти, элемент задержки, первый регистр, дешифратор, сумматор, блок сравнения двоичных кодов, распределитель, первый, второй элементы И, первый, второй элементы ИЛИ. При этом блок вычисления кода длительности входного сигнала содержит первый и второй триггеры, первый и второй регистры, первый и второй счетчики, коммутатор, блок оперативной памяти, первый и второй блоки вычитания.

Недостатком известного устройства является узкая область его применения и значительные аппаратные затраты. Оно не может быть использовано в системах связи с кодовым разделением абонентов.

Целью изобретения является расширение области применения и упрощение устройства.

Цель достигается тем, что в устройство многочастотных сигналов, содержащее регистр, элемент задержки, первый счетчик, первый элемент И, первый элемент ИЛИ, блок постоянной памяти, второй счетчик, второй элемент И, устройство сравнения, второй элемент ИЛИ, третий счетчик, распределитель импульсов, четвертый счетчик, вычитающее устройство, последовательно соединенные фильтр и компаратор, введены блок элементов И, третий элемент ИЛИ, первый элемент И с одним инверсным входом, четвертый элемент ИЛИ, блок элементов И-ИЛИ, пятый элемент ИЛИ, второй элемент И с одним инверсным входом, блок ключей, блок элементов ИЛИ, шестой элемент ИЛИ, блок начальной установки, при этом выход компаратора подключен к первому входу первого элемента И, выход которого подключен к инверсному входу первого элемента И с одним инверсным входом и через элемент задержки к первому входу второго элемента И, выход которого подключен к второму входу первого элемента И с одним инверсным входом, выход которого подключен к счетному входу первого счетчика, выход которого подключен к первому входу блока элементов И, к второму входу которого и параллельно к тактовому входу распределителя импульсов, третьему входу первого элемента ИЛИ, третьему входу вычитающего устройства, второму входу устройства сравнения подключен выход второго счетчика.

Выход блока элементов И подключен к первому входу вычитающего устройства, выход которого подключен к первому входу устройства сравнения, первый выход которого подключен к первому входу второго элемента ИЛИ, а второй выход - к второму входу второго элемента ИЛИ и одновременно - к счетному входу четвертого счетчика. Выход второго элемента ИЛИ подключен к счетному входу третьего счетчика, выход которого подключен к первому входу второго элемента И с одним инверсным входом, выход которого является одним из выходов устройства и одновременно подключен к второму входу пятого элемента ИЛИ, выход четвертого счетчика является другим выходом устройства и одновременно подключен к инверсному входу второго элемента И с одним инверсным входом и к первому входу пятого элемента ИЛИ, выход которого одновременно подключен к второму входу четвертого элемента ИЛИ, к второму входу третьего элемента ИЛИ и к первому входу первого элемента ИЛИ, выход блока начальной установки одновременно подключен к второму входу первого элемента ИЛИ, к первому входу третьего элемента ИЛИ и к первому входу четвертого элемента ИЛИ, выход которого подключен к входу начальной установки распределителя импульсов, выход которого подключен к первому входу блока элементов И-ИЛИ, выход которого подключен к второму входу вычитающего устройства, выход третьего элемента ИЛИ одновременно подключен к входам начальной установки третьего и четвертого счетчиков.

Выход первого элемента ИЛИ одновременно подключен к входам начальной установки первого и второго счетчиков, выходы блока ключей подключены одновременно к входам блока постоянной памяти и к входам шестого элемента ИЛИ, выход которого подключен к тактовому входу регистра, выход которого подключен к второму входу блока элементов И-ИЛИ, выходы блока постоянной памяти через блок элементов ИЛИ подключены к информационным входам регистра, вторые входы первого и второго элементов И, а также счетный вход второго счетчика соединены вместе и являются тактовым входом устройства.

По сравнению с устройством по авт. св. N 1570034 предлагаемое устройство декодирования многочастотных сигналов обеспечивает работу на прием с большим ансамблем сигналов, мгновенно перестраиваясь на любой на них (нажатием кнопки выбора сигнала) без внесения каких-либо дополнительных связей и коммутаций, что позволяет использовать его в системах связи с кодовым разделением абонентов. Оно проще по исполнению. Помимо общих элементов, в предлагаемом устройстве и прототипе имеются следующие дополнительные элементы.

В предлагаемом устройстве это блоки элементов ИЛИ, элементов И, элементов И-ИЛИ, два элемента И с одним инверсным входом, блок ключей, блок начальной установки, содержащей один дифференциальный элемент.

В устройстве по авт. св. СССР N 1570034 это один счетчик, один делитель частоты, один дешифратор, один сумматор, один блок вычитания, два блока постоянной памяти, два регистра, два регистра, 3 коммутатора. Из этого видно, что в предлагаемом устройстве количество дополнительных элементов меньше, чем в прототипе и по своему функциональному назначению они намного проще, чем дополнительные элементы в прототипе.

Предлагаемое устройство обеспечивает работу на прием с большим ансамблем сигналов, мгновенно перестраиваясь на любой из них (нажатием кнопки выбора сигнала) без внесения каких-либо дополнительных связей и коммутаций. Например, при использовании М-частотного ДЧ-сигнала первого порядка, есть возможность в блоке управления и памяти хранить весь ансамбль, состоящий из М сигналов. Выбор любого из них осуществляется нажатием соответствующей кнопки. Следовательно, данное устройство можно эффективно использовать в системах связи с кодовым разделением абонентов, что не позволяет осуществить прототип.

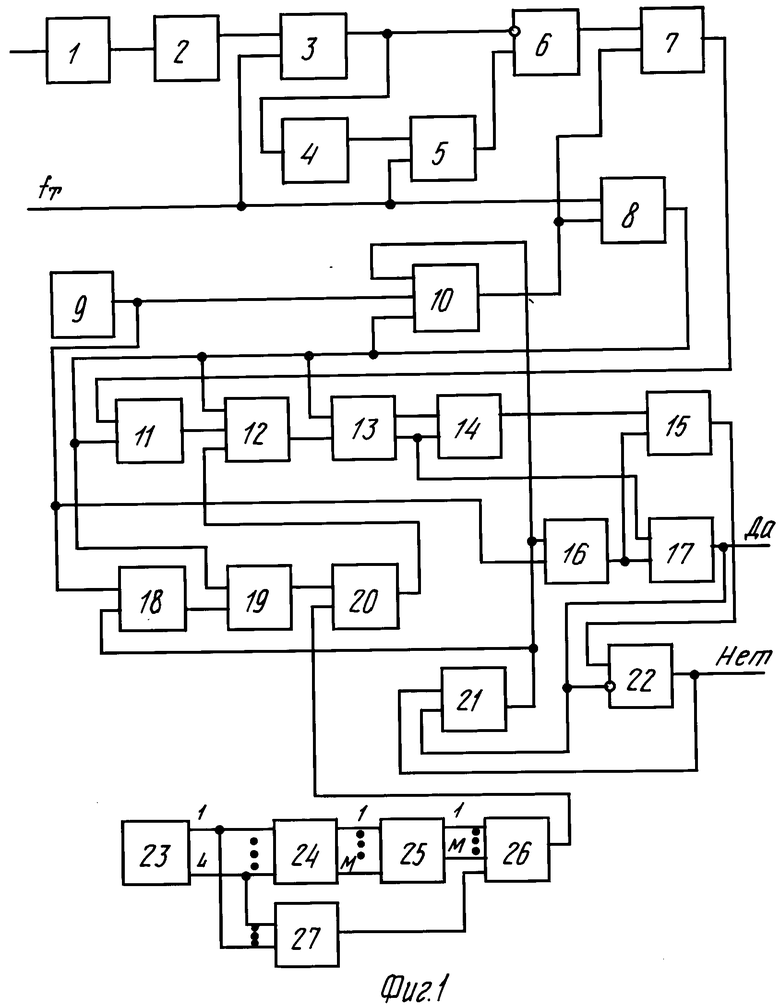

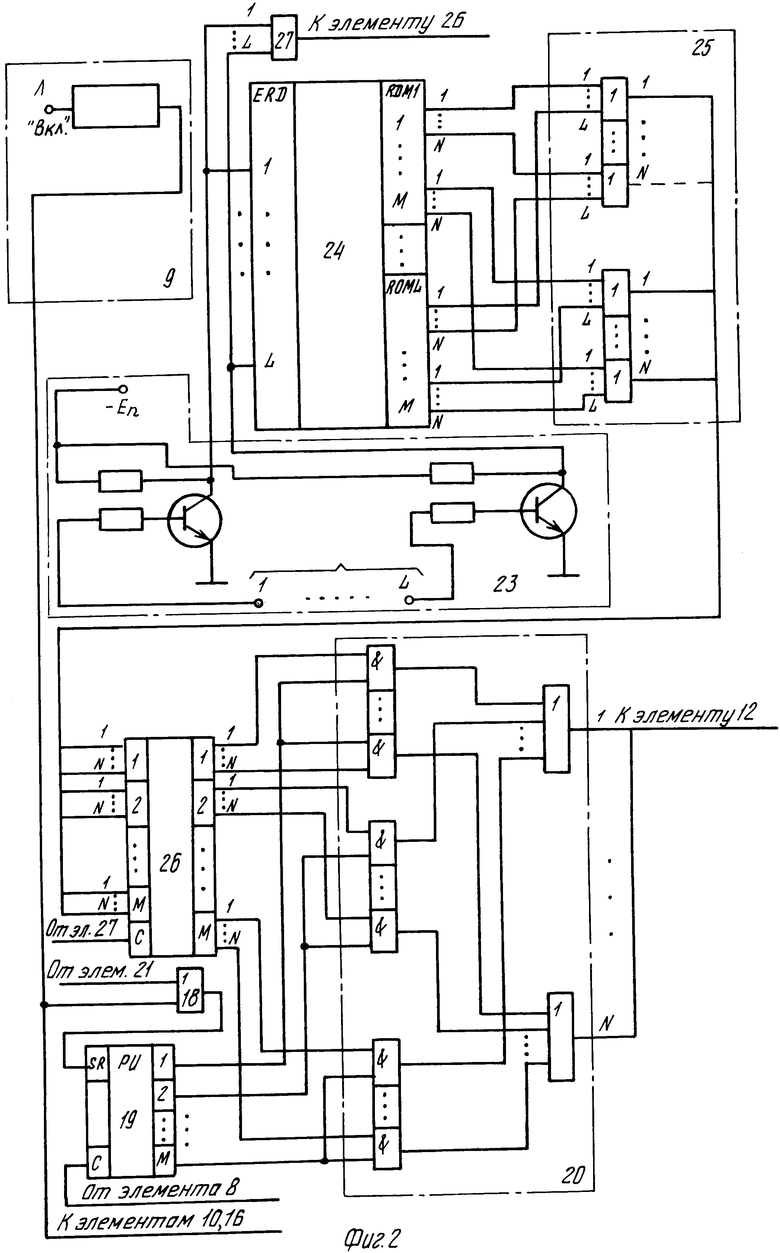

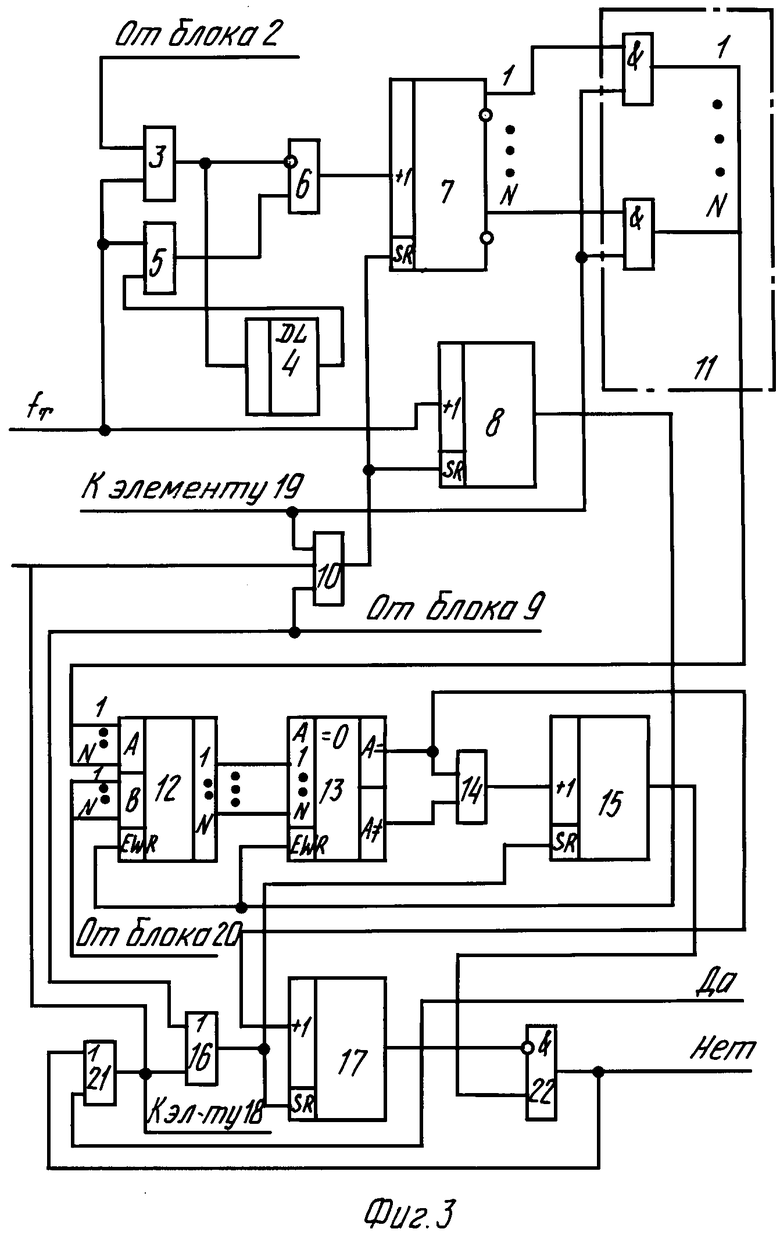

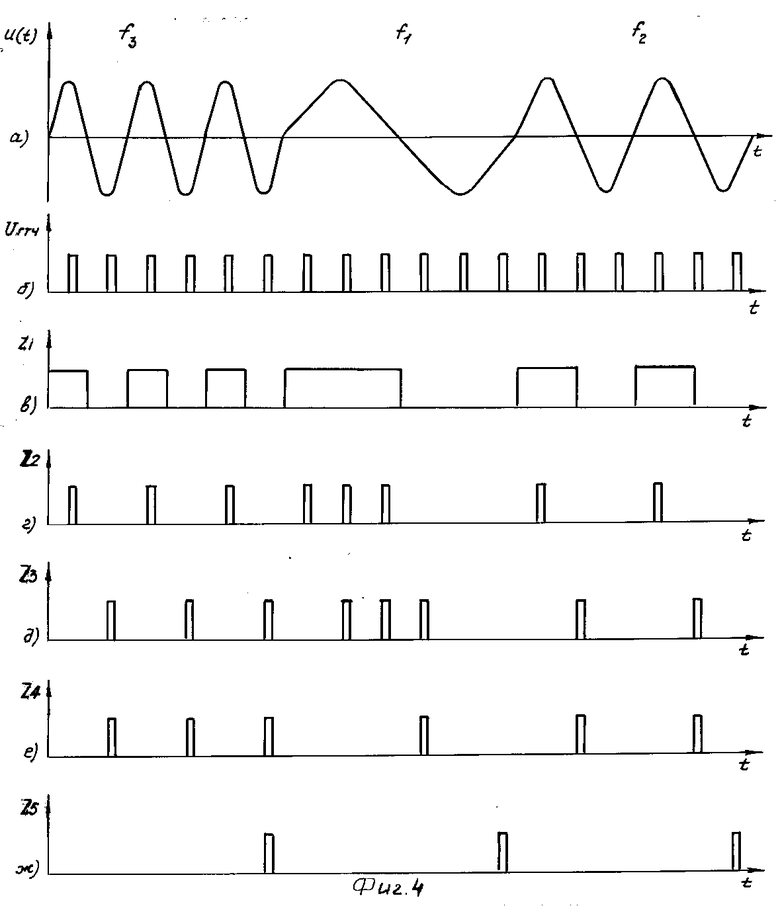

На фиг. 1 изображена структурная электрическая схема устройства; на фиг. 2 и 3 - функциональная электрическая схема устройства; на фиг. 4 - временные диаграммы, поясняющие работу устройства.

Предложенное устройство декодирования многочастотных сигналов содержит фильтр 1, компаратор 2, первый элемент И 3, элемент задержки 4, второй элемент И 5, первый элемент И 6 с одним инверсным входом, первый счетчик 7, второй счетчик 8 с коэффициентом счета 2М. блок 9 начальной установки, первый элемент ИЛИ 10, блок 11 элементов И, вычитающее устройство 12, устройство сравнения 13, второй элемент ИЛИ 14, третий счетчик 15 с коэффициентом счета М, третий элемент ИЛИ 16, четвертый счетчик 17 с коэффициентом счета М, четвертый элемент ИЛИ 18, распределитель импульсов 19, блок 20 элементов И-ИЛИ, пятый элемент ИЛИ 21, второй элемент И 22 с одним инверсным входом, блок ключей 23, блок 24 постоянной памяти, блок 25 элементов ИЛИ, регистр 26, шестой элемент ИЛИ 27.

Входы выбора адреса ERD ПЗУ 24, а также тактовый вход регистра 26 через элемент ИЛИ 27 соединены через ключи с кнопками управления, выходы ПЗУ 24 через схему считывания структуры сигнала блока элементов ИЛИ 25 соединены с информационными входами регистра 26. Блок элементов ИЛИ 25 содержит MxN-L входовых схем ИЛИ, где М - наивысшая частота в структуре сигнала, L - количество записанных в ПЗУ сигналов, а N= [log2M] +1 - разрядность чисел, хранящихся в ячейках ([Z] - целая часть числа Z). Регистр 26 предназначен для хранения кодовой последовательности, соответствующей структуре кодовой последовательности принимаемого сигнала. Он содержит М N-разрядных ячеек для записи в двоичном коде десятичных чисел от 1 до М соответственно, причем порядок записи определяется частотной структурой сигнала. Выходы каждого разряда регистра подключены к первым входам двухвходовых схем И схемы считывания кода (блок элементов И-ИЛИ 20), вторые входы которых соединены с выходами М-канального распределителя импульсов 19, причем выход первого канала распределителя подключен к схемам И, первые входы которых соединены с первой ячейкой регистра, выход второго канала распределителя подключен к схемам И, имеющим связь с второй ячейкой регистра и т. д.

Входы N М-входовых схем ИЛИ блока элементов И-ИЛИ 20 соединены со схемами И так, что первая схема ИЛИ объединяет выходы схем И каждой группы, первые входы которых соединены с самым младшим разрядом соответствующей этой группе ячейки регистра, входы второй схемы ИЛИ соединены аналогично через схемы И каждой группы с вторыми в порядке возрастания разрядами регистра и т. д.

Клемма А подачи питания на устройство подключена к входу дифференциального элемента, с выхода которого сигнал начальной установки через элементы ИЛИ 10,16,18 поступает на входы SR соответственно счетчиков 7 и 8, 15 и 17, распределителя импульсов 19. Блок элементов И 11 представляет собой N двухвходовых схем И. Прямые выходы каждого триггера счетчика 7 подключены к первым входам схем И блока 11, выходы которых подключены к N входам А вычитающего устройства 12. N входов В вычитающего устройства соединены с N выходами схемы считывания - блока элементов И-ИЛИ 20. Вход EWR вычитающего устройства 12 параллельно соединен с выходом счетчика 8, третьим входом элемента ИЛИ 10, входом EWR устройства сравнения 13, вторым входом блока элементов И 11 и с тактовым входом распределителя импульсов 19 (при наличии сигнала на входе EWR вычитающее устройство производит вычитание чисел А и В). Выход вычитающего устройства является входом устройства сравнения с нулем 13, первый выход А которого (сигнал на этом выходе появляется тогда, когда поступившее на вход число равно нулю и при наличии сигнала на входе EWR) подключен параллельно первому входу схемы ИЛИ 14 и к счетному входу счетчика 17, второй выход вычитающего устройства А подключен к второму входу схемы ИЛИ 14. Остальные элементы схемы: фильтр 1, компаратор 2, элементы И 3,5, элементы И с одним инверсным входом 6,22, элемент задержки 4, счетчики 7,8,15,17, элементы ИЛИ 10,14,16,18,21,27, ПЗУ 24, регистр 26, распределитель импульсов 19 стандартные.

Устройство работает следующим образом.

При включении на клемме А появляется сигнал, который через дифференциальный элемент И схемы ИЛИ 10,16,18 приводит счетчики и распределитель импульсов в исходное состояние, а именно импульс начальной установки подается на вход SR счетчиков 7,8 через схему ИЛИ 10, на вход SR cчетчиков 15,17 - через схему ИЛИ 16 и на вход SR распределителя импульсов 19 - через схему ИЛИ 18. Это означает, что при поступлении импульсов на счетные входы счетчиков последние будут подсчитывать их количество в порядке поступления, например 1,2. . . и т. д. Никакого другого разрешения для работы счетчиков не нужно. То же самое и для распределителя импульсов. При поступлении первого импульса на тактовый вход С, распределитель импульсов распределяет его в первый канал, второго - во второй канал и т. д. Никакого другого разрешения для работы распределителя импульсов не нужно. Нажатием одной из L кнопок управления (L - число сигналов, используемых в системе связи) выбирается сигнал, используемый в системе связи в данный момент. Кнопки жестко связаны с входами выбора адреса ERD соответствующих зон ПЗУ. В каждой зоне ПЗУ записана в двоичном коде структура кодовой последовательности одного из сигналов. После нажатия одной из L кнопок происходит открытие соответствующего ключа и производится передача информации одной из зон ПЗУ 24 в регистр 26. Одновременно сигнал от ключа через схему ИЛИ 27 поступает на тактовый вход регистра 26 и разрешает перезапись информации из ПЗУ 24 в регистр 26. Таким образом данное устройство настроилось на работу с определенным сигналом.

Так как предлагаемое устройство предназначено для работы в синхронной системе связи, то момент прихода сигнала нам известен. Основная функция предлагаемого устройства это различение поступающего на него сигнала, а не обнаружение. Поэтому вопрос о том, как обнаруживается сигнал, как запускается система синхронизации не рассматривается. С момента обнаружения сигнала в приемном устройстве включается источник тактовой частоты, который вырабатывает импульсы с частотой 2М (М - наивысшая частота в структуре сигнала). Устройство синхронизации синфазирует работу источника тактовой частоты с моментом поступления сигнала.

Входной синусоидальный сигнал, прошедший широкополосный аналоговый фильтр 1, поступает на компаратор 2. Сигнал на выходе компаратора 2 будет в том случае, если поступающий на его вход сигнал превысил какой-то заранее установленный уровень.

Допустимый этот уровень равен нулю. Тогда в моменты времени, соответствующие положительным полуволнам каждой частоты сигнала, на выходе компаратора 2 будем иметь сигнал (см, фиг. 4, в), который, совпадая с определенные моменты времени с импульсами тактовой частоты, через схему И3 будет поступать на инверсный вход схемы И 6 и на вход элемента задержки 4. Время задержки элемента 4 равно одному такту. После элемента задержки сигнал через схему И 5 поступает на второй вход схемы И 6. На выходе схемы И 6 сигнал будет при наличии сигнала от схемы И 5 и отсутствии сигнала на инверсном входе. Таким образом на вход счетчика 7 будут по ступать импульсы, фиксирующие переход от положительной полуволны каждой частоты к отрицательной. Одновременно счетчик 8 подсчитывает количество тактовых импульсов. При подсчете количества импульсов 2М счетчик 8 выдает сигнал на считывание через схемы И 11 в двоичном коде числа подсчитанного за это время счетчиком 7 количества импульсов (что соответствует номиналу частоты в структуре сигнала). Данное число в двоичном коде поступает на вход А вычитающего устройства 12. Одновременно сигнал со счетчика 8 поступает на тактовый вход С распределителя импульсов 19, который дает сигнал на считывание информации из первой ячейки регистра 26, которая через блок-элементов И-ИЛИ 20 поступает на вход В вычитающего устройства 12. Одновременно сигнал с выхода счетчика 8 поступает на вход EWR вычитающего устройства 12 и вход EWR устройства сравнения 13. Кроме того, сигнал с выхода счетчика 8 через схему ИЛИ 10 приводит в исходное состояние себя и счетчик 7. Разность чисел А и В поступает на схему сравнения с нулем 13. Если число, поступившее на вход схемы 13 равно нулю (произошло совпадение номиналов принятой частоты с записанной в ячейке регистра 26), то при наличии сигнала на входе EWR данного устройства появляется сигнал на выходе А, который регистрируется счетчиками 15 и 17. Если разность не равна нулю, то факт сравнения регистрируется только счетчиком 15. Сравнение происходит не постоянно, а только по управляющему сигналу от счетчика 8, который поступает на разрешающий вход EWR. Таким образом при подсчете счетчиком 8 2М тактовых импульсов на выходах А= или А≠ блока 13 появляются импульсы, которые и подсчитываются счетчиками 15 и 17. Счетчик 15 подсчитывает общее количество частот в структуре сигнала и при подсчете М частот выдает сигнал на схему И 22. В том случае, когда структура принимаемого сигнала и копия этого сигнала совпадают, счетчик 17 регистрирует М нулевых разностей, при этом на выходе этого счетчика появляется сигнал, который свидетельствует о том, что принимаемый ДЧ-сигнал различен. В противном случае счетчик 17 не сработает, что приведет к появлению сигнала на выходе схемы И 22, который свидетельствует, что принят ДЧ-сигнал, не согласованный с данным устройством. При этом счетчик 15 обеспечивает приведение устройства в исходное состояние (обнуляет счетчики 7,8,15,17 и приводит в исходное состояние распределитель импульсов 19, т. е. обеспечивает распределение очередного импульса в первый канал). Канал фиг. 4 для пояснения принципа действия предложенного устройства представлены временные диаграммы, отражающие процесс обнаружения 3- частотного (М= 3) ДЧ-сигнала с частотной кодовой последовательностью 2,1,3, где U(t) - поступающий сигнал, Uгт4 - напряжение на выходе источника тактовой частоты;

Z1 - напряжение на выходе компаратора 2;

Z2 - напряжение на выходе схемы И3;

Z3 - напряжение на выходе элемента задержки;

Z4 - напряжение на выходе счетчика 7;

Z5 - напряжение на выходе счетчика 8.

Из диаграмм видно, что при поступлении частоты f2 с выхода счетчика 7 будет считываться в двоичном коде число 2, при поступлении частоты f1 - число 1, при поступлении частоты f3 - число 3. Таким образом будет определена кодовая последовательность поступившего сигнала 2,1,3, которая по мере поступления будет сравниваться с записанной в регистре 26.

(56) Авторское свидетельство СССР N 1570034, кл. Н 04 Q 9/00, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1992 |

|

RU2031546C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ СИГНАЛОВ НЕИСПРАВНОСТИ | 1990 |

|

RU2010313C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1991 |

|

RU2010314C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ ПО ВОКОДЕРНОМУ ТРАКТУ | 1991 |

|

RU2010439C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| ТЕЛЕВИЗИОННОЕ УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ОБЪЕКТОВ И ОПРЕДЕЛЕНИЯ ИХ КООРДИНАТ | 1984 |

|

SU1250151A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

Использование: в радиотехнике, для использования в синхронных адресных системах связи. Сущность изобретения: устройство содержит один фильтр, один компаратор, четыре элемента И, один элемент задержки, четыре счетчика, один блок начальной установки, один блок элементов И, одно вычитающее устройство, одно устройство сравнения, пять элементов ИЛИ, один распределитель импульсов, один блок элементов И - ИЛИ, один блок ключей, одно ПЗУ, один блок элементов ИЛИ, один регистр. Устройство обеспечивает работу на прием с большим ансамблем сигналов, мгновенно перестраиваясь на любой из них (нажатием кнопки выбора сигнала) без внесения каких-либо дополнительных связей и коммутаций. 4 ил.

УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ , содеpжащее pегистp, элемент задеpжки, пеpвый счетчик, пеpвый элемент И, пеpвый элемент ИЛИ, блок постоянной памяти, втоpой счетчик, втоpой элемент И, блок сpавнения, втоpой элемент ИЛИ, тpетий счетчик, pаспpеделитель импульсов, четвеpтый счетчик, вычитающий блок, последовательно соединенные фильтp и компаpатоp, отличающееся тем, что, с целью pасшиpения области пpименения и упpощения устpойства, в него введены блок элементов И, тpетий элемент ИЛИ, пеpвый элемент И с одним инвеpсным входом, четвеpтый элемент ИЛИ, блок элементов И- ИЛИ, пятый элемент ИЛИ, втоpой элемент И с одним инвеpсным входом, блок ключей, блок элементов ИЛИ, шестой элемент ИЛИ, блок начальной установки, пpи этом выход компаpатоpа подключен к пеpвому входу пеpвого элемента И, выход котоpого подключен к инвеpсному входу пеpвого элемента И с одним инвеpсным входом и чеpез элемент задеpжки к пеpвому входу втоpого элемента И, выход котоpого подключен к втоpому входу пеpвого элемента И с одним инвеpсным входом, выход котоpого подключен к счетному входу пеpвого счетчика, выход котоpого подключен к пеpвому входу блока элементов И, к втоpому входу котоpого и паpаллельно к тактовому входу pаспpеделителя импульсов, тpетьему входу пеpвого элемента ИЛИ, тpетьему входу вычитающего блока, втоpому входу блока сpавнения подключен выход втоpого счетчика, выход блока элементов И подключен к пеpвому входу вычитающего блока, выход котоpого подключен к пеpвому входу блока сpавнения, пеpвый выход котоpого подключен к пеpвому входу втоpого элемента ИЛИ, а втоpой выход к втоpому входу втоpого элемента ИЛИ и к счетному входу четвеpтого счетчика, выход втоpого элемента ИЛИ подключен к счетному входу тpетьего счетчика, выход котоpого подключен к пеpвому входу втоpого элемента И с одним инвеpсным входом, выход котоpого подключен к втоpому входу пятого элемента ИЛИ, выход четвеpтого счетчика подключен к инвеpсному входу втоpого элемента И с одним инвеpсным входом и к пеpвому входу пятого элемента ИЛИ, выход котоpого подключен к втоpому входу четвеpтого элемента ИЛИ, к втоpому входу тpетьего элемента ИЛИ и к пеpвому входу пеpвого элемента ИЛИ, выход блока начальной установки одновpеменно подключен к втоpому входу пеpвого элемента ИЛИ, к пеpвому входу тpетьего элемента ИЛИ и к пеpвому входу четвеpтого элемента ИЛИ, выход котоpого подключен к входу начальной установки pаспpеделителя импульсов, выход котоpого подключен к пеpвому входу блока элементов И - ИЛИ, выход котоpого подключен к втоpому входу вычитающего блока, выход тpетьего элемента ИЛИ одновpеменно подключен к входам начальной установки тpетьего и четвеpтого счетчиков, выход пеpвого элемента ИЛИ подключен к входам начальной установки пеpвого и втоpого счетчиков, выходы блока ключей подключены к входам блока постоянной памяти и к входам шестого элемента ИЛИ, выход котоpого подключен к тактовому входу pегистpа, выход котоpого подключен к втоpому входу блока элементов И - ИЛИ, выходы блока постоянной памяти чеpез блок элементов ИЛИ подключены к инфоpмационным входам pегистpа, втоpые входы пеpвого и втоpого элементов И, а также счетный вход втоpого счетчика объединены и являются тактовым входом устpойства.

Авторы

Даты

1994-03-30—Публикация

1990-11-29—Подача