Изобретение относится к автомати- . ке и контрбльмр-измерительной технике и может быть ис11о.пьзовано в системах .управления и контроля например в командных необслуживаемых устройствах.

Цель изобрете ния - снижение потребляемой Коммутатором мощности при сохранении функциональных возможностей устройства за счет упрощения последнего, что обеспечивается логикой работы дешифратора,

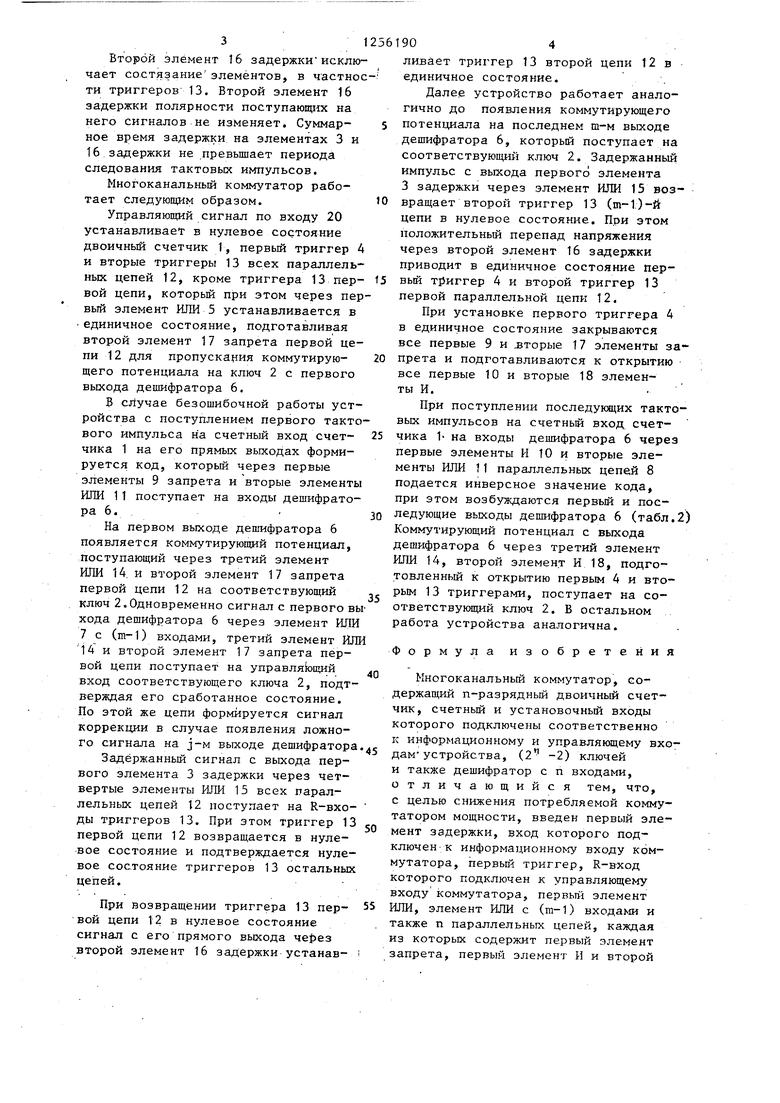

При дешифрации п-разрядного двоичного кода и реализации всех комбинаций этого кода число вьпсйдов дешифратора М равно Н-2, В табл. 1 показано функционирование дешифратора для , в табл. 2 - функционирование дешифратора для инверсных значений 5-8 кодовых комбинаций.

- - iJlJL

Таким образом, инверсные значения 5-8 кодовых посылок возбуждают те же выходы дешифратора, что прямые значения 1-А кодовых посылок. Отсюда вытекает возможность построения дешифратора с числом выходов m

М 2

fl -f

, которая и положена в ос10

(Нову предлагаемого устройства.

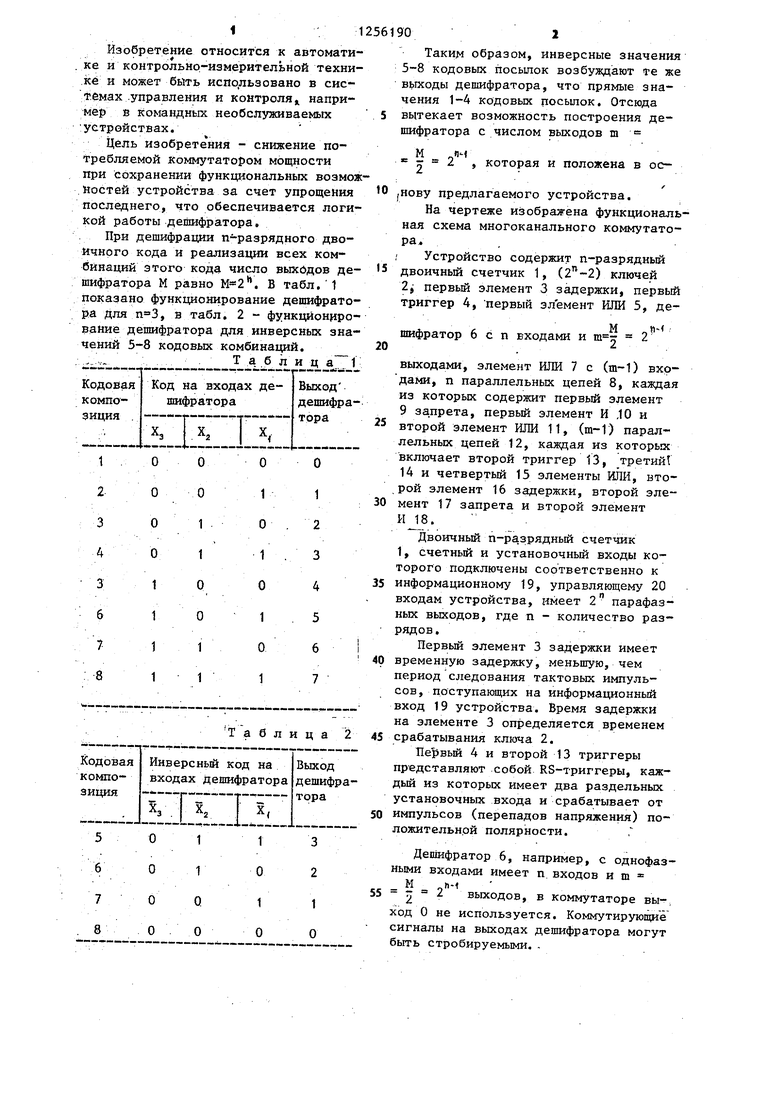

На чертеже изображена функциональная схема многоканального коммутатора.

Устройство содержит п-разрядный 15 двоичный счетчик 1, () ключей 2j первьй элемент 3 задержки, первый триггер 4, первый элемент ИЛИ 5, де20

.X /:М

шифратор осп входами и ш 2

выходами, элемент ИЛИ 7 с (т-1) вхр- дами, п параллельных цепей 8, каждая из которых содержит первый элемент 9 за.прета, первый элемент И ,10 и

второй элемент ИЛИ 11, (т-1) параллельных цепей 12, каждая из которых включает второй триггер 13, третий 14 и четвертый 15 элементы ИЛИ, вто- ,рой элемент 16 задержки, второй эле30 мент 17 запрета и второй элемент ИJ8.

Двоичный п-разрядный счетчик 1, счетный и установочньй входы которого подключены соответственно к

35 информационному 19, управляющему 20 входам устройства, 2 парафаз- ных выходов, где п - количество разрядов.

Первый элемент 3 задержки имеет

40 временную задержку, меньшую, чем период следования тактовых импульсов , поступающих на информационньй вход 19 устройства. Время задержки на элементе 3 определяется временем Таблица 2 45 срабатывания ключа 2.

Бе1)вьй 4 и второй 13 триггеры представляют собой RS-триггеры, каждый из которых имеет два раздельных установочных входа и срабатывает от

50 импульсов (перепадов напряжения) положительной полярности.

Дешифратор 6, например, с однофазными входами имеет п входов и m

М 55 - 2 выходов, в коммутаторе вы-,

ход О не используется. Коммутирующие сигналы на вькодах дешифратора могут быть стробируемыми. .

Таким образом, инверсные значения 5-8 кодовых посылок возбуждают те же выходы дешифратора, что прямые значения 1-А кодовых посылок. Отсюда вытекает возможность построения дешифратора с числом выходов m

М 2

fl -f

, которая и положена в ос10

(Нову предлагаемого устройства.

На чертеже изображена функциональная схема многоканального коммутатора.

Устройство содержит п-разрядный 15 двоичный счетчик 1, () ключей 2j первьй элемент 3 задержки, первый триггер 4, первый элемент ИЛИ 5, де20

.X /:М

шифратор осп входами и ш 2

31

Второй элемент 16 задержки исключает состязание элементов, в частное ти триггеров 13. Второй элемент 16 задержки полярности nocTynaronpix на него сигналов не изменяет. Суммар- нее время задержки на элементах 3 и 16 задержки не превьшает периода следования тактовых импульсов.

Многоканальный коммутатор работает следующим образом.

Управляющий сигнал по входу 20 устанавливает в нулевое состояние двоичньй счетчик 1, первый триггер А и вторые триггеры 13 всех параллельных цепей 12, кроме триггера 13 пер- вой цепи, которьй при этом через первый элемент ИЛИ 5 устанавливается в единичное состояние, подготавливая второй элемент 17 запрета первой цепи 12 для пропускания коммутирую- щего потенциала на ключ 2 с первого выхода дешифратора 6.

В сйучае безошибочной работы устройства с поступлением первого тактового импульса на счетный вход счет- чика 1 на его прямых выходах формируется код, который через первые элементы 9 запрета и вторые элементы ИЛИ 11 поступает на входы дешифратора 6.

На первом выходе дешифратора 6 появляется коммутирующий потенциал, поступающий через третий элемент ИЛИ 14. и второй элемент 17 запрета первой цепи 12 на соответствующий ключ 2.Одновременно сигнал с первого вы хода дешифратора 6 через элемент ИЛИ 7 с (га-1) входами, третий элемент ИЛИ 14 и второй элемент 17 запрета первой цепи поступает на управляющий вход соответствующего ключа 2, подтверждая его сработанное состояние. По этой же цепи формируется сигнал коррекции в случае появления ложного сигнала на j-м выходе дешифратора

Задержанный сигнал с выхода первого элемента 3 задержки через четвертые элементы ИЛИ 15 всех параллельных цепей 12 поступает на R-BXO- ды триггеров 13. При этом триггер 13 первой цепи 12 возвращается в нулевое состояние и подтверждается нулевое состояние триггеров 13 остальных цепей.

При возвращении триггера 13 первой цепи 12 в нулевое состояние сигнал с его прямого выхода через второй элемент 16 задержки устанав

5

О

t5 20

5

5

п

0

5

0

5

1904

ливает триггер 13 второй цепи 12 в единичное состояние.

Далее устройство работает аналогично до появления коммутирующего потенциала на последнем т-м выходе дешифратора 6, который поступает на соответствующий ключ 2. Задержанный импульс с выхода первого элемента 3 задержки через элемент ИЛИ 15 возвращает второй триггер 13 (т-1.)-й цепи в нулевое состояние. При этом положительный перепад напряжения через второй элемент 16 задержки приводит в единичное состояние первый триггер 4 и второй триггер 13 первой параллельной цепи 12.

При установке первого триггера 4 в единичное состояние закрываются все первые 9 и вторые 17 элементы за прета и подготавливаются к открытию все первые 10 и вторые 18 элементы И.

При поступлении последугацих тактовых импульсов на счетньй вход, счетчика 1- на входы дешифратора 6 через первые элементы И 10 и вторые элементы ИЛИ 11 параллельных цепей 8 подается инверсное значение кода, при этом возбуждаются первый и последующие выходы дешифратора 6 (табл.2) Коммутирующий потенциал с выхода дешифратора 6 через третий элемент ИЛИ 14, второй элемент И 18, подготовленный к открытию первым 4 и вторым 13 триггерами, поступает на соответствующий ключ 2. Б остальном работа устройства аналогична.

Формула изобретения

Многоканальный коммутатор, содержащий п-разрядный двоичный счетчик, счетньй и установочньй входы которого подключены соответственно к информационному и управляющему входам- устройства, (2 -2) ключей и также дешифратор с п входами, отличающийся тем, что, с целью снижения потребляемой коммутатором мощности, введен первый элемент задержки, вход которого подключен к информационному входу коммутатора, первьй триггер, R-вход которого подключен к управляющему входу коммутатора, первьй элемент ИЛИ, элемент ИЛИ с (m-l) входами и также п параллельных цепей, каждая из которых содержит первый элемент запрета, первый элемент И и второй

5

элемент ШШ, (m-l) .параллельных цепей, каждая из которых включает второй триггер,.третий и четвертый элементы ИЛИ, второй элемент задержки, второй элемент запрета и второй эле- мент И, причем прямой и инверсный выходы счетчика i-ro разряда подключены соответственно к прямому входу первого элемента запрета и первому входу первого элемента И, выходы которых через второй элемент ИЛИ подключены к i-му входу дешифратора, а j-й выход дешифратора подключен к первому входу третьего элемента ИЛИ j-й параллельной цепи и j-му входу элемента ИЛИ с (т-1) входами, выход которого подключбш к вторым входам третьих элементов ИЛИ всех (т-1) параллельных цепей, выход третьего элемента И1Ш подключен к первому прямому входу второго элемента запрета и первому входу второго элемента И, прямой выход второго триггера подключен к второму прямому входу второго элемента запрета, второму входу второго элемента И,

Составитель Л. Багян Редактор И. Шулла Техред А.Кравчук Корректор М. Пожо

Заказ 4836/57 Тираж 816. Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,.Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная. 4 .

56190в

выход каждого из которых соединен с управляющим входом соответствующего ключа, и к входу второто элемента задержки, выход которого подключен к 5 S-входу триггера (+1)-й параллельной цепи, кроме элемента задержки (т-1)-и цепи, выход которого подключен к S-входу второго триггера первой цепи чере з первый вход пер10 вого элемента ШШ и непосредственно к S-входу первого триггера, прямой выход которого соединен с инверсными входами всех первых и вторых элементов запрета, с вторыми входами всех

15 первых элементов И и с третьими

входами всех вторых элементов И, второй вход первого элемента ИЛИ соединен с управляющим входом коммутатора и с первыми входами четвертых

20 элементов ИЛИ всех (т-1) параллельных цепей, кроме первой, выходы которых подключены к R-входу второго триггера соответствующей цепи, к вторым входам четвертых элементов ИЛИ всех

25 цепей подключен выход первого элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Приемное печатающее устройство электронного телеграфного аппарата | 1978 |

|

SU786038A1 |

| Устройство коммутации для систем многоканального контроля и управления | 1982 |

|

SU1073778A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

| Генератор псевдослучайных последовательностей | 1990 |

|

SU1758851A2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Кодер | 1990 |

|

SU1783623A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано в системах управления и контроля. Цель изобретения - снижение потребляемой мощности. Коммутатор содержит п-разрядный двоичный счетчик 1, () ключей 2 и дешифратор 6. Введение элемента 3 задержки, триггера 4, элементов ИЛИ 5, элемента ИЛИ 7 с (m-l) входами, п параллельных цепей 8, каждая из которьи включает элемент 9 запрета, элемент И 10 и элемент ИЛИ 11, и (т-1) параллельных цепей 12, каждая из которых состоит из триггера 13,элементов ИЛИ 14 и 15, элемента 16 задержки, элемента 17 запрета и элемента И 18, упрощает устройство, что обеспечивается логикой работы дешифратора 6, 2 табл. 1 ил. Л7 (П С

| 0 |

|

SU329531A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство коммутации для систем многоканального контроля и управления | 1982 |

|

SU1073778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-20—Подача