Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах и контрольно-измерительной аппаратуре.

Известно устройство для выделения остатка по переменному модулю [1] содержащее второй регистр числа и входной регистр модуля, причем входы входного регистра числа и входного регистра модуля образуют соответственно первую и вторую группу входов устройства, дешифратор числа, коммутатор, дешифратор модуля и шифратор. Выход входного регистра числа и входного регистра модуля соединены соответственно с входами дешифратора числа и входного регистра модуля, соединены соответственно с входами дешифратора числа и дешифратора модуля, выход которого соединен с управляющим входом коммутатора, выходы дешифратора числа соединены с информационными входами коммутатора, выходы которого соединены с входами шифратора, выходы шифратора образуют группу выходов устройства.

Недостатком этого устройства является его низкая контролепригодность, т. е. в случае появления неисправности в устройстве она может быть установлена только в момент прекращения рабочей программы и прогонки контрольной программы, при этом в случае прогонки контрольной программы можно установить факт наличия неисправности, а место неисправности с точностью до функционально законченной единицы установить невозможно. В этом случае коэффициент глубины поиска, являющийся одним из показателей контролепригодности, равен нулю. Коэффициент глубины поиска Кгп согласно ГОСТ 23563-79 определяется соотношением

Kг.п=  , где F число однозначно различимых составных частей на принятом уровне деления, т. е. число обнаруживаемых неисправностей заданного типа и класса;

, где F число однозначно различимых составных частей на принятом уровне деления, т. е. число обнаруживаемых неисправностей заданного типа и класса;

R общее число составных частей изделия, т.е. общее число неисправностей заданного типа и класса.

Известно устройство для выделения отказа по переменному модулю [2] содержащее входной регистр числа, дешифратор числа, коммутатор, входной регистр модуля, дешифратор модуля, шифратор, пороговые элементы, первый элемент И, группу дешифраторов, элемент ИЛИ, узел сравнения, первую группу элементов НЕ, дешифратор остатка, элемент НЕ, второй элемент И, вторую группу элементов НЕ, первую группу элементов И, группу элементов ИЛИ, группу сумматоров по модулю два, элемент И-НЕ, третью группу элементов НЕ, вторую группу элементов И, выходы дешифратора числа и дешифратора модуля соединены соответственно с входами первого и второго пороговых элементов, информационные входы дешифраторов группы объединены с информационными входами входного регистра числа, стробирующие входы дешифраторов группы соединены с соответствующими входами дешифратора модуля, выходы дешифратора соединены с информационными входами дешифратора остатка, первая и вторая группы информационных входов узла сравнения соединены соответственно с группами выходов коммутатора и дешифратора остатка, выходы дешифратора, кроме младшего разряда, через соответствующие элементы НЕ первой группы соединены с соответствующими входами первого элемента И, выход младшего разряда шифратора соединен с соответствующим входом первого элемента И, выход которого через элемент НЕ соединен с первым входом второго элемента И, второй вход которого соединен с выходом элемента ИЛИ, входы элементов НЕ второй группы объединены с соответствующими информационными входами входного регистра модуля, выходы каждого элемента НЕ второй и третьей группы соединены соответственно с первым и вторым входами соответствующего элемента И первой группы, выход которого соединен с первым входом соответствующего элемента ИЛИ группы, выход которого соединен с первым входом соответствующего сумматора по модулю два группы, выходы всех сумматоров по модулю два группы соединены с соответствующими входами элемента И-НЕ, прямой выход каждого разряда входного регистра модуля соединен с третьим входом соответствующего элемента И первой группы и первым входом соответствующего элемента И второй группы, выход которого соединен с вторым входом соответствующего элемента ИЛИ группы, инверсный выход каждого разряда входного регистра модуля соединен с вторым входом соответствующего сумматора по модулю два группы, второй вход каждого разряда входного регистра модуля соединен с вторым входом соответствующего сумматора по модулю два группы, второй вход каждого элемента И второй группы объединен с третьим входом соответствующего элемента ИЛИ группы и входом соответствующего элемента НЕ второй группы, третьи входы всех элементов И второй группы и входы всех элементов НЕ третьей группы объединены и подключены к входу записи входного регистра модуля, выходы первого и второго пороговых элементов, узлы сравнения, второго элемента И и элемента И-НЕ образуют вторую группы выходы неисправности устройства.

Недостатком устройства является низкая достоверность функционирования, которая обусловлена тем, что в процессе функционирования не обнаруживаются одиночные неисправности типа const 0 и типа const 1 элементов.

Таким образом можно сказать, что коэффициент глубины поиска дефекта при функциональном диагностировании равен 0,57.

Целью изобретения является повышение достоверности функционирования, т. е. увеличение значения коэффициента глубины поиска дефекта при функциональном диагностировании устройства.

Для достижения цели используются теоретические результаты по парафазной логике.

Цель достигается тем, что устройство сверки по переменному модулю, содержащее регистр числа, триггер, сумматор по модулю два, парафазный дешифратор, коммутатор, элемент сравнения, два элемента И, два элемента ИЛИ, причем вход задания модуля устройства соединен с S-входом триггера, R-вход которого соединен с входом сброса устройства, а инверсный выход с первым информационным входом сумматора по модулю два, входы числа устройства соединены с информационными входами регистра числа, вход установки в начальное состояние которого соединен с входом сброса устройства, прямые выходы регистра числа подключены к прямым информационным входам первой группы парафазного дешифратора, выход контроля которого соединен с первым выходом обнаружения неисправности устройства, дополнительно содержит регистр самопроверки, с третьего по седьмой элементы И, с третьего по пятый элементы ИЛИ, с второго по пятый элементы сравнения, коммутатор выполнен парафазным, причем прямой выход триггера соединен с вторым информационным входом сумматора по модулю два и с первыми входами первого и второго элементов И, инверсный выход триггера подключен к первым входам третьего и четвертого элементов И, входы контрольного кода устройства соединены с информационными входами регистра самопроверки, вход установки в начальное состояние которого соединен с входом сброса устройства, первый инверсный выход подключен к управляющему входу сумматора по модулю два, а инверсные выходы со второго по пятый с входами с первого по четвертый второй группы парафазного дешифратора, прямые и инверсные выходы которого соединены с соответствующими информационными входами парафазного коммутатора, выход контроля которого является вторым выходом обнаружения неисправности устройства, выход сумматора по модулю два подключен к вторым входам элементов И с первого по четвертый, выходы которых соединены с соответствующими управляющими входами парафазного коммутатора, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента сравнения, выход которого подключен к первому входу первого элемента ИЛИ, выход которого является третьим выходом обнаружения неисправности устройства, выходы четвертого и второго элементов И соединены соответственно с первым и вторым входами второго элемента сравнения, выход которого подключен к второму входу первого элемента ИЛИ, первый, второй и третий прямые выходы парафазного коммутатора соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с первым входом третьего элемента сравнения, второй вход которого подключен к выходу пятого элемента И, входы которого соединены с первым, вторым и третьим инверсными выходами парафазного коммутатора, третий, четвертый и пятый прямые выходы парафазного коммутатора соединены с входами третьего элемента ИЛИ, выход которого подключен к первому входу четвертого элемента сравнения, второй вход которого подключен к входу седьмого элемента И, входы которого соединены с третьим, четвертым и пятым инверсными выходами парафазного коммутатора, второй, пятый и шестой прямые выходы парафазного коммутатора соединены с входами четвертого элемента ИЛИ, выход которого соединен с первым входом пятого элемента сравнения, второй вход которого соединен с выходом седьмого элемента И, входы которого соединены с вторым, пятым и шестым инверсными выходами парафазного коммутатора, выходы третьего, четвертого и пятого элементов сравнения соединены с входами пятого элемента ИЛИ, выход которого является четвертым выходом обнаружения неисправности устройства, выходы элементов ИЛИ с второго по четвертый и элементов И с пятого по седьмой являются информационными парафазными выходами устройства.

Парафазный коммутатор содержит с первого по тринадцатый парафазные элементы ИЛИ, с первого по десятый парафазные элементы И, элементы сравнения с первого по десятый и выходной элемент ИЛИ, причем входы с первого по десятый парафазных элементов ИЛИ соединены с информационными входами коммутатора в соответствии с выбранным модулем контроля, прямой выход каждого парафазного элемента ИЛИ с первого по десятый соединен с первым информационным входом соответствующего парафазного элемента И, инверсный выход каждого парафазного элемента ИЛИ соединен с вторым информационным входом соответствующего парафазного элемента И с первого по десятый, прямой и инверсный выходы которого соединены с первым и вторым входами соответствующего элемента сравнения, выходы которых соединены с входами выходного элемента ИЛИ, выход которого является выходом контроля парафазного коммутатора, прямой и инверсный выходы первого парафазного элемента И подключен к первому и второму входам одиннадцатого парафазного элемента ИЛИ, третий и четвертый входы которого подключены соответственно к прямому и инверсному выходам четвертого парафазного элемента И, прямой и инверсный выходы второго парафазного элемента И подключены к первому и второму входам двенадцатого парафазного элемента ИЛИ, третий и четвертый входы которого соответственно соединены с прямым и инверсным выходами пятого парафазного элемента И, прямой и инверсный выходы третьего парафазного элемента И подключены соответственно к первому и второму входам тринадцатого парафазного элемента ИЛИ, третий и четвертый входы которого соединены соответственно с прямым и инверсным выходами шестого парафазного элемента И, первый управляющий вход коммутатора соединен с первыми управляющими входами первого, второго и третьего парафазного элемента И, второй управляющий вход коммутатора с вторыми управляющими входами парафазных элементов И с четвертого по десятый, третий управляющий вход коммутатора с вторыми управляющими входами первого, второго и третьего парафазных элементов И, четвертый управляющий вход с первыми управляющими входами парафазных элементов И с четвертого по десятый.

Введенные элементы и связи между ними обеспечивают выполнение поставленной цели, что иллюстрируется таблицами функций неисправностей, представленных на фиг.3-11 и фиг.13-17.

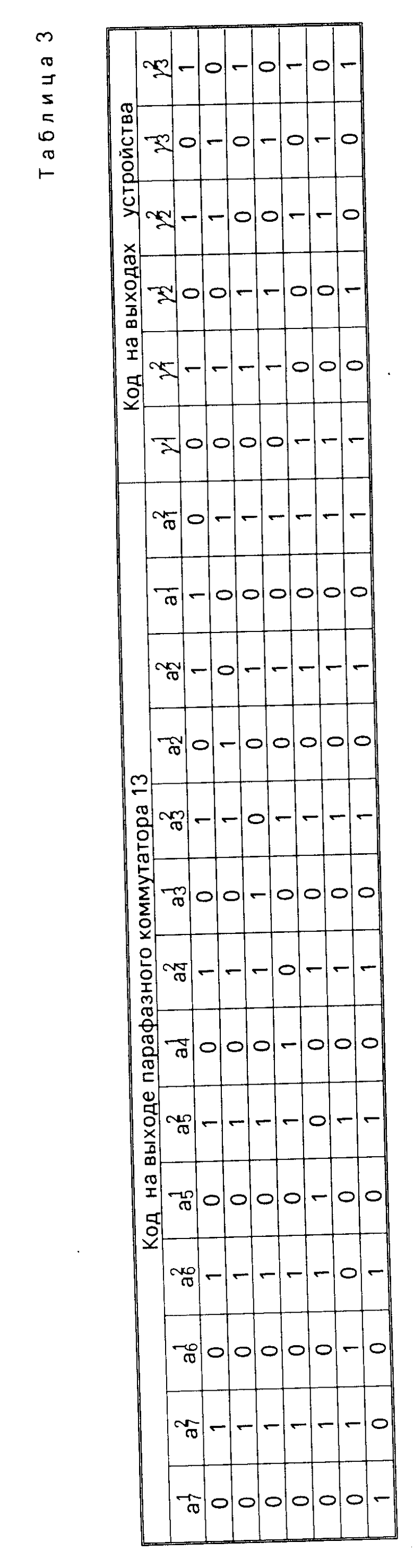

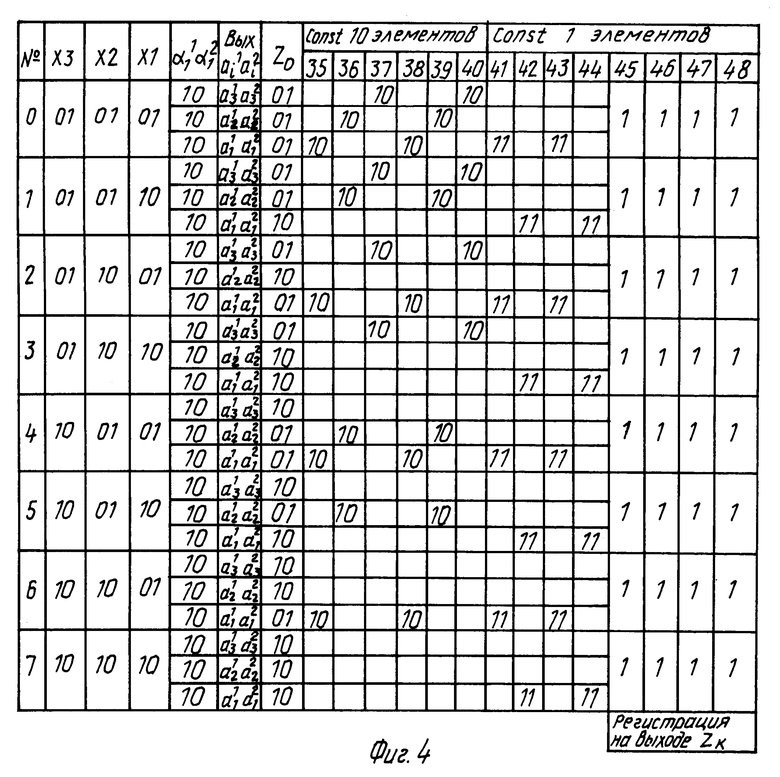

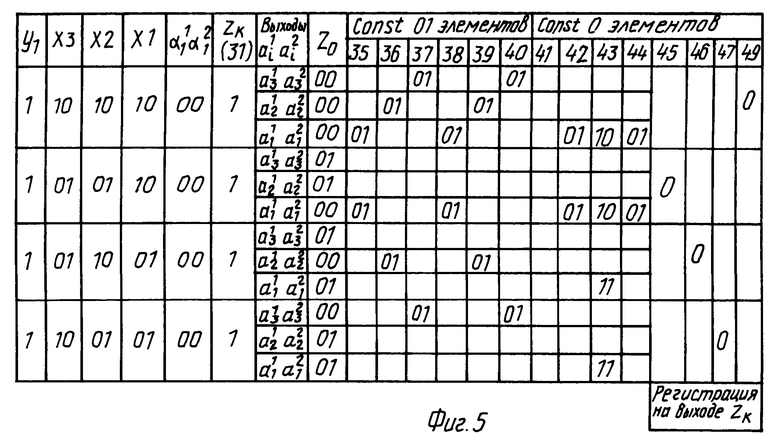

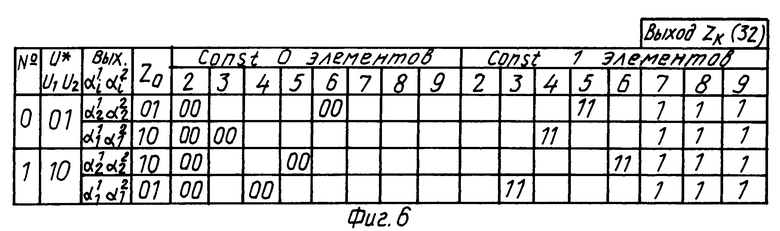

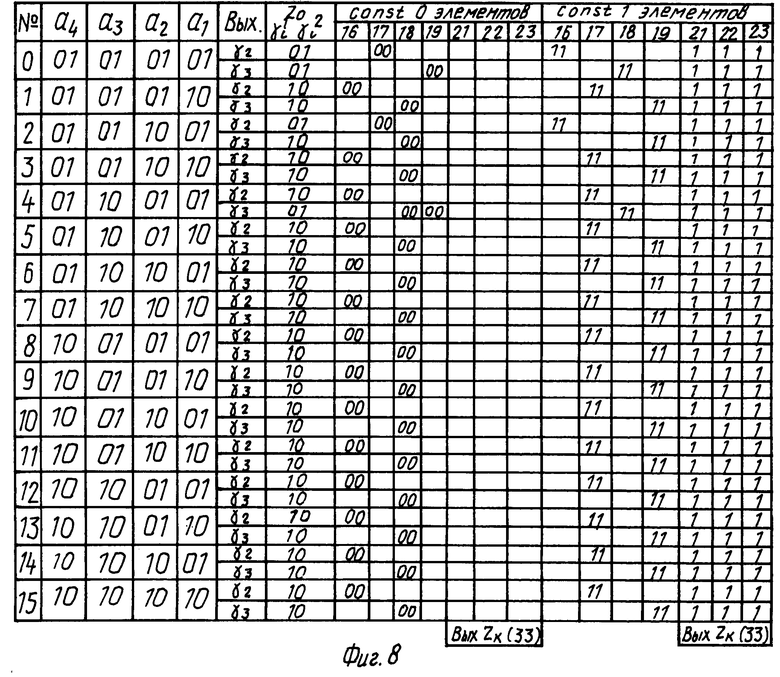

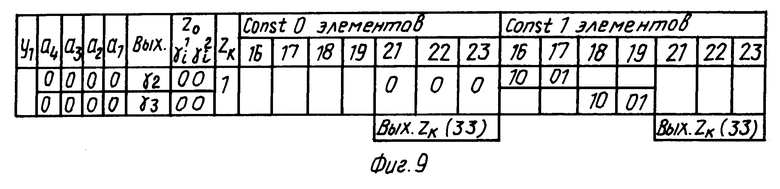

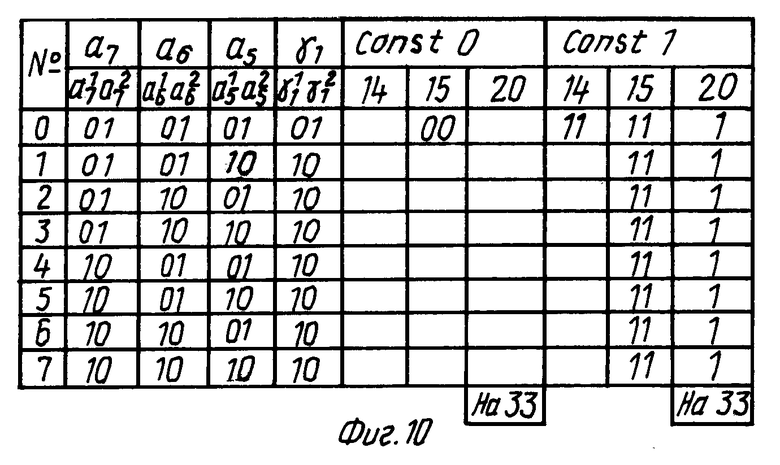

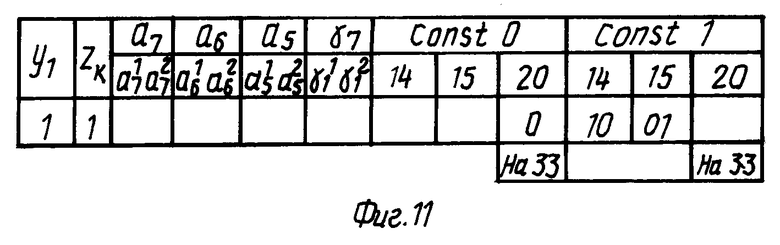

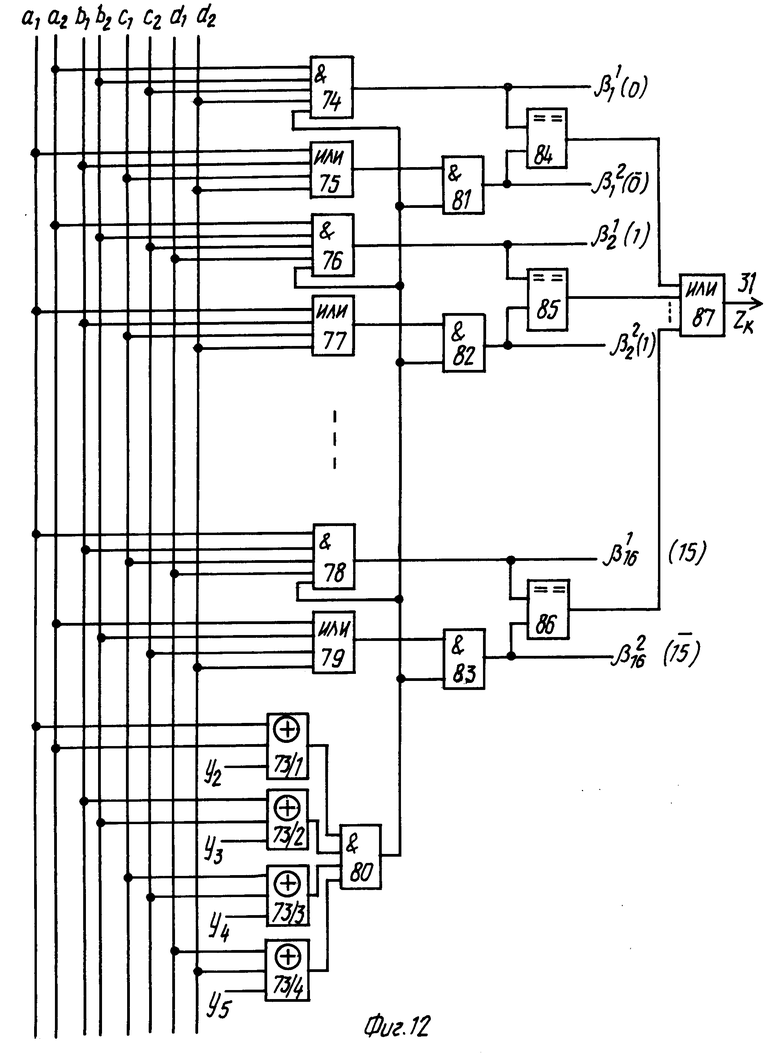

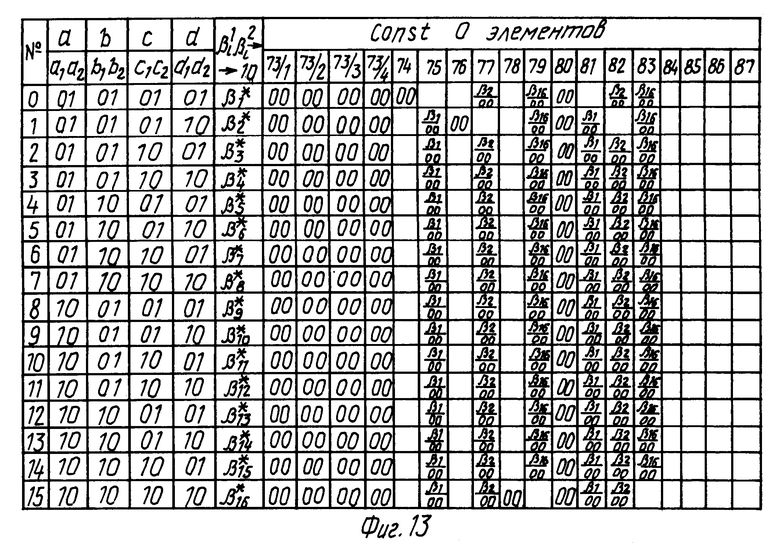

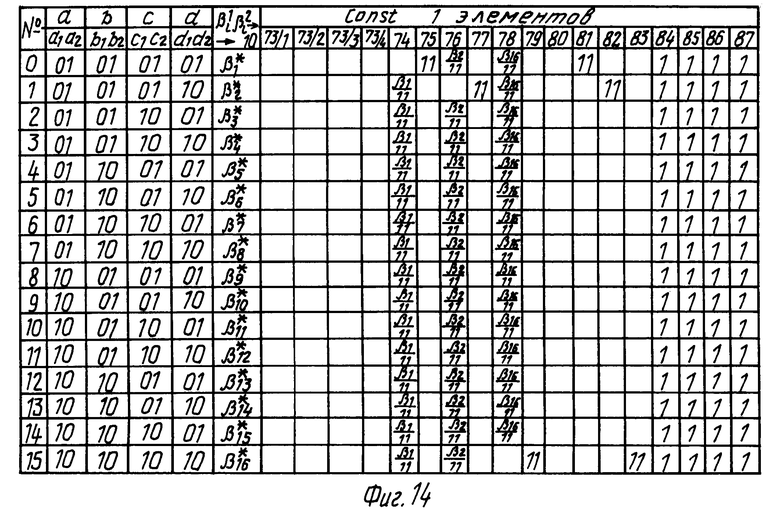

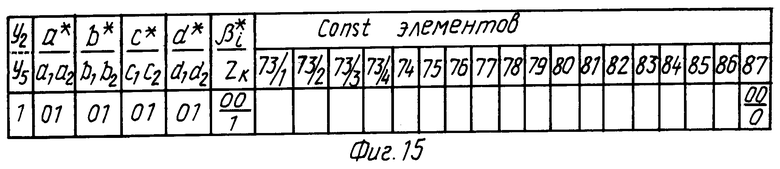

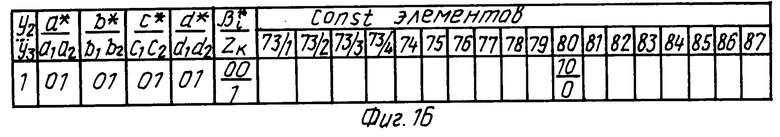

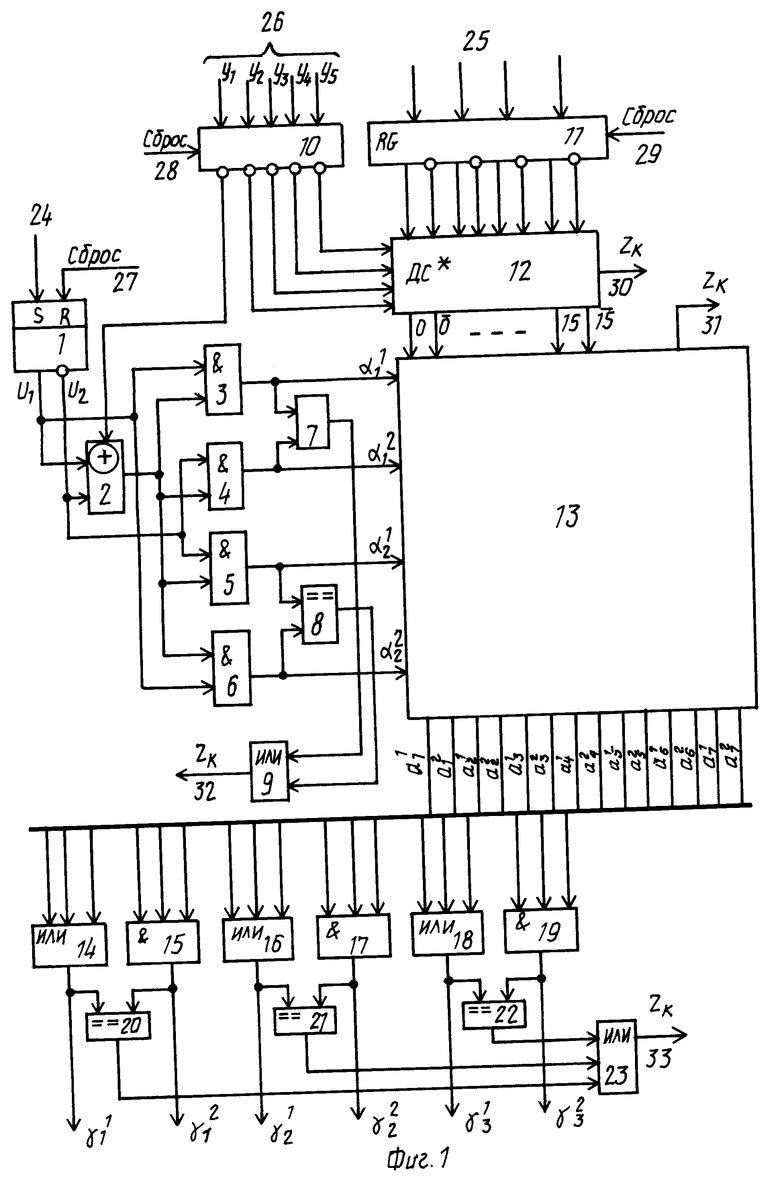

На фиг.1 представлена структурная схема устройства, на фиг.2 парафазный коммутатор; на фиг.3-5 таблица функций неисправностей парафазного коммутатора; на фиг.6 и 7 таблица функций неисправностей элементов 2-9; на фиг.8 и 9 таблица функций неисправностей элементов 16-19 и 21-23; на фиг.10 и 11 таблица функций неисправностей элементов 14, 15 и 20; на фиг.12 парафазный дешифратор; на фиг. 13-17 таблица функций неисправностей парафазного дешифратора; на фиг.18 сумматор по модулю два.

Устройство свертки по переменному модулю (фиг.1) содержит триггер 1, сумматор 2 по модулю два, элементы И 3-6, элементы 7 и 8 сравнения, элементы ИЛИ 9, 14, 16, 18 и 23, регистр 10 самопроверки, регистр 11 числа, парафазный дешифратор 12, парафазный коммутатор 13, элементы И 15, 17 и 19, элементы 20-22 сравнения, вход 24 задания модуля, вход 25 числа, управляющий вход 26 самопроверки, входы 27-29 сброса, выходы 30-33 обнаружения неисправностей, информационные парафазные выходы 34.

Парафазный коммутатор (фиг. 2) содержит парафазные элементы ИЛИ 35-37, парафазные элементы И 38, 39 и 40, элементы ИЛИ 41 и 44, элементы И 42 и 43, элементы 45-47 сравнения, парафазные элементы ИЛИ 48-54, парафазные элементы И 55-61, элементы 62-68 сравнения, элемент ИЛИ 69 и парафазные элементы ИЛИ 70-72.

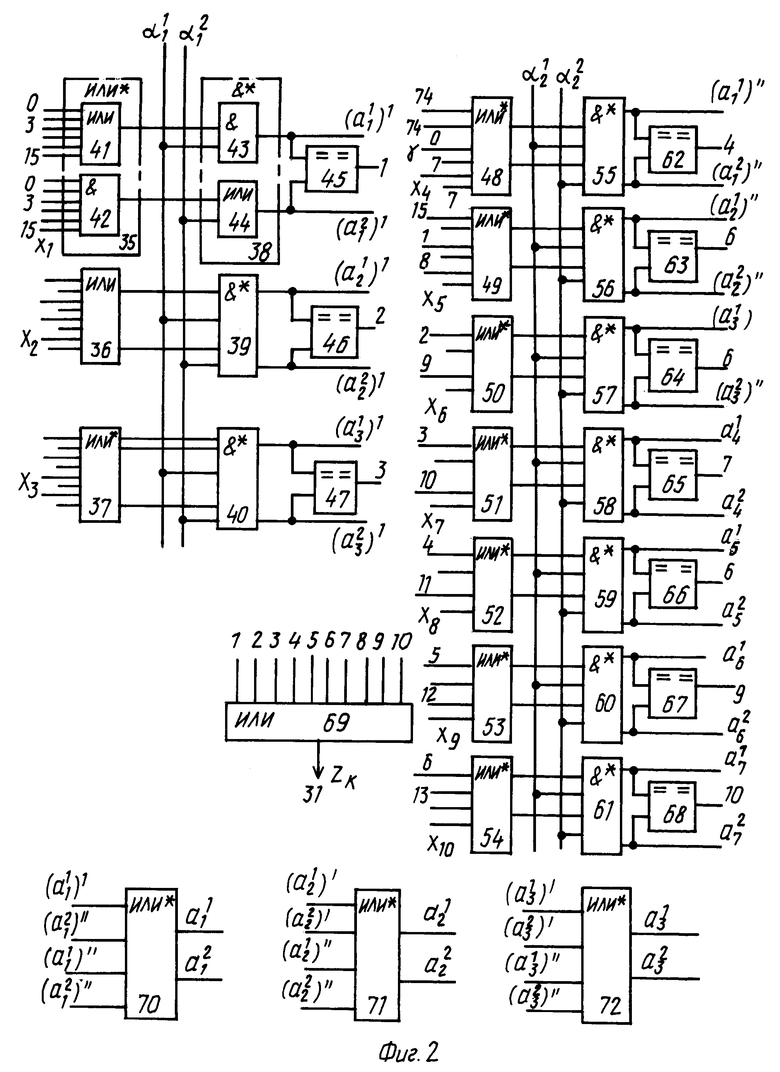

На фиг.3, 4 представлена таблица функций неисправностей для парафазного коммутатора 13 при управляющем воздействии y1 0.

На фиг.5 представлена таблица функций неисправностей для парафазного коммутатора 13 при управляющем воздействии у1 1.

На фиг. 6 представлена таблица функций неисправностей для элементов 2-9 при управляющем воздействии у1 0.

На фиг.7 представлена таблица функций неисправностей для элементов 2-9, при управляющем воздействии у1 1.

На фиг. 8 представлена таблица функций для элементов 16-19 и 21-23 при управляющем воздействии у1 0.

На фиг. 9 представлена таблица функций для элементов 16-19 и 21-23 при управляющем воздействии у1 1.

На фиг.10 представлена таблица функций неисправностей для элементов 14, 15 и 20 при управляющем воздействии у1 0.

На фиг.11 представлена таблица функций неисправностей для элементов 14, 15 и 20 при управляющем воздействии у1 1.

Парафазный дешифратор 12 (фиг.12) содержит сумматоры 73 по модулю два, элементы И 74, 76, 78, 80, 81, 82 и 83, элементы ИЛИ 75, 77, 79 и 87, элементы 84-86 сравнения.

На фиг.13 и 14 представлена таблица функций неисправностей для парафазного дешифратора 12 при управляющих воздействиях у2 у3 у4 у5 0.

На фиг.15 и 16 представлена таблица функций неисправностей для парафазного дешифратора 12 при управляющих воздействиях у2 у5 1.

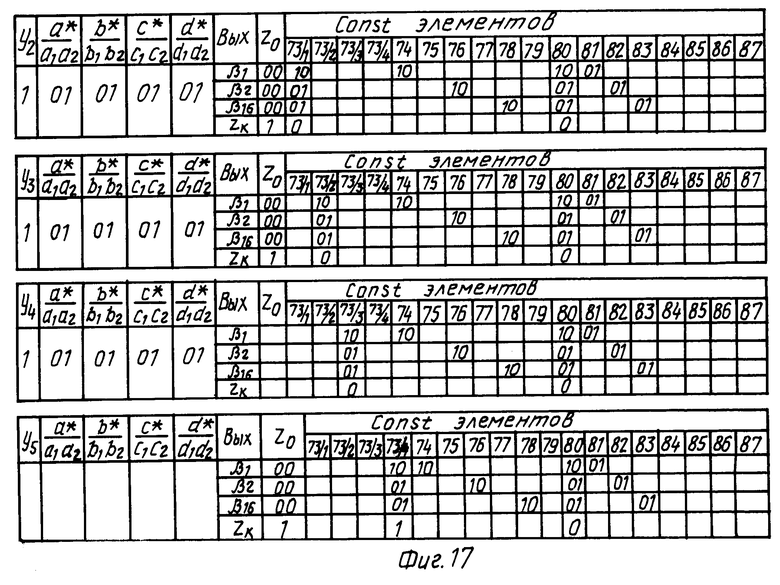

На фиг. 17 представлена таблица функций неисправностей для парафазного дешифратора 12 при условии, что одно из управляющих воздействий уi(i  ) принимает единичное значение, а все остальные нулевые.

) принимает единичное значение, а все остальные нулевые.

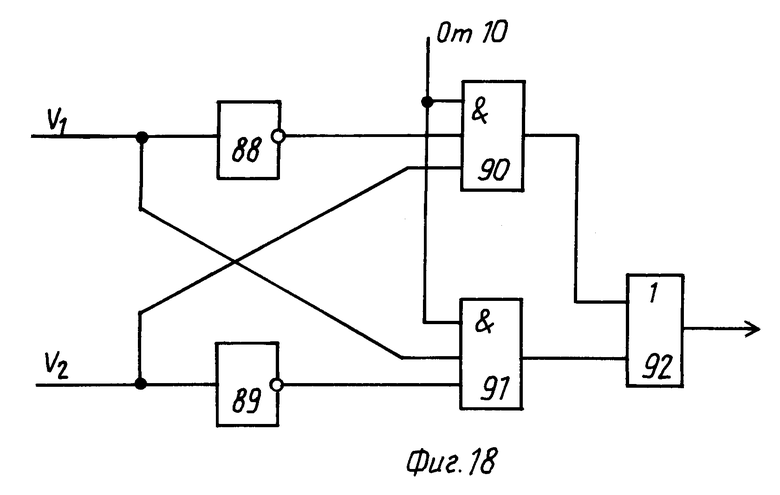

Сумматор (элементы 2, 70-73) по модулю два (фиг.18) содержит элементы НЕ 88 и 89, элементы И 90 и 91 и элемент ИЛИ 92.

Вход 24 задания модуля устройства соединен с входом S триггера 1, а вход R последнего с входом 27 сброса устройства, инверсный выход с вторым входом сумматора 2 по модулю два, информационный вход 25 устройства соединен с информационными входами регистра 11 числа, управляющий вход которого соединен с входом 29 сброса устройства, прямые выходы регистра 11 числа подключены к прямым информационным входам парафазного дешифратора 12, контрольный выход которого соединен с первым контрольным выходом 30 устройства. Прямой выход триггера 1 соединен с первым входом сумматора 2 по модулю два, с первым входом первого элемента И 3, с вторым входом четвертого элемента И 6. Инверсный выход триггера 1 подключен к первому входу второго 4 и третьего 5 элементов И. Управляющие входы 26 самопроверки устройства соединены с информационными входами регистра 10 самопроверки. Управляющий вход регистра самопроверки соединен с входами 28 сброса устройства, а первый инверсный выход с управляющим входом сумматора 2 по модулю два, с второго по пятый инверсные выходы с первого по четвертый соответственно входом парафазного дешифратора 12, прямые и инверсные выходы которого соединены с информационными входами парафазного коммутатора 13. Выход сумматора 2 по модулю два подключен к второму входу первого 3, второго 4, третьего 5 элементов И и к первому входу четвертого элемента И 60, выходы элементов И 3-6 соединены соответственно с первым инверсным управляющим входом парафазного коммутатора 13. Выход первого 3 и второго 4 элементов И соединены соответственно с первым и вторым входом первого элемента 7 сравнения, выход которого подключен к первому входу первого элемента ИЛИ 9, выход которого соединен с третьим контрольным выходом 32 устройства. Выходы третьего 5 и четвертого 6 элементов И соединены соответственно с первым и вторым входом второго элемента 8 сравнения, выход которого подключен к второму входу первого элемента ИЛИ 9. Контрольный выход парафазного коммутатора соединен с вторым контрольным выходом 31 устройства. Первый, шестой и седьмой прямые выходы парафазного коммутатора 13 соединены соответственно с первым, вторым и третьим входом второго элемента ИЛИ 14. Пятый, шестой и седьмой инверсные выходы парафазного коммутатора 13 соединены соответственно с первым, вторым и третьим входом пятого элемента И 15. Выход второго элемента ИЛИ 14 и выход пятого элемента И 15 подключены соответственно к первому и второму входу третьего элемента 20 сравнения, выход которого соединен с третьим входом пятого элемента ИЛИ 23. Третий, четвертый и седьмой выход парафазного коммутатора 13 соединены соответственно с первым, вторым и третьим входом третьего элемента ИЛИ 16, третий, четвертый и седьмой инверсный выходы парафазного коммутатора 13 соединены соответственно с первым, вторым и третьим входом шестого элемента И 17. Выход третьего элемента ИЛИ 16 и шестого элемента И 17 подключены соответственно к первому и второму входу четвертого элемента 21 сравнения, выход которого подключен к второму входу пятого элемента ИЛИ 23. Второй, четвертый и шестой прямые выходы парафазного коммутатора 13 соединены соответственно с первым, вторым и третьим входом четвертого элемента ИЛИ 18. Второй, четвертый и шестой инверсный выходы парафазного коммутатора 13 соединены соответственно с первым, вторым, и третьим входом седьмого элемента И 19. Выход четвертого элемента ИЛИ 18 и седьмого элемента И 19 подключены соответственно к первому и второму входу пятого элемента 22 сравнения, выход которого подключен к первому входу пятого элемента ИЛИ 23, выход которого соединен с четвертым контрольным выходом 33 устройства. Выходы элементов ИЛИ 14, 16 и 18 и элементов И 15, 17 и 19 соединены с информационными парафазными выходами 34 устройства.

Входы парафазных элементов ИЛИ 35-37 и 48-54 соединены с информационными входами блока, причем входы этих элементов подключаются к входам блока в соответствии с выбранным модулем контроля. Прямой выход каждого парафазного элемента ИЛИ 35-37 и 48-54 соединен соответственно с первым входом парафазных элементов И 38-40 и 55-62. Инверсный выход каждого парафазного элемента ИЛИ 35-37 и 48-54 соединен соответственно с третьим входом парафазных элементов И 38-40 и 55-62, прямой и инверсный выход каждого из которых соединен с первым и вторым входом соответственно элемента 45-47 и 63-68 сравнения, выходы которых соединены с соответствующим входом элемента ИЛИ 69, выход которого соединен с контрольным выходом парафазного коммутатора. Прямой и инверсный выход первого парафазного элемента И 38 подключен к первому и второму входу одиннадцатого парафазного элемента ИЛИ 70, третий и четвертый входы которого подключены соответственно к прямому и инверсному выходу четвертого парафазного элемента И 55. Прямой и инверсный выход второго парафазного элемента И 39 подключен к первому и второму входу двенадцатого парафазного элемента ИЛИ 71, третий и четвертый входы которого соединены соответственно с прямым и инверсным выходом пятого парафазного элемента И 56. Прямой и инверсный выход третьего парафазного элемента И 40 подключены соответственно к первому и второму входу тринадцатого парафазного элемента ИЛИ 72, третий и четвертый входы которого соединены соответственно с прямым и инверсным выходом шестого парафазного элемента И 57. Первый управляющий вход парафазного коммутатора соединен с вторым входом элементов 38-40, второй управляющий вход с четвертым входом элементов И 38-40, третий управляющий вход с вторым входом элементов И 55-62, четвертый управляющий вход с четвертым входом элементов И 55-62.

Работа устройства основана на теории остаточных классов и на теории парафазной логики. В парафазной логике логическому нулю соответствует код <01> а логической единице <10> Состояния <00> и <11> являются запрещенными при работе устройства. Они фиксируются с помощью элементов сравнения.

Все целые числа распределяются относительно данного модуля m на m классов, так что все числа одного и того же класса сравнимы друг с другом по модулю m, тогда как числа разных классов не сравнимы друг с другом по модулю m. Если у каждого из m классов, на которые распадаются все целые по модулю m, взять по одному числу, то эти m взятых чисел составляют полную систему вычетов по модулю m.

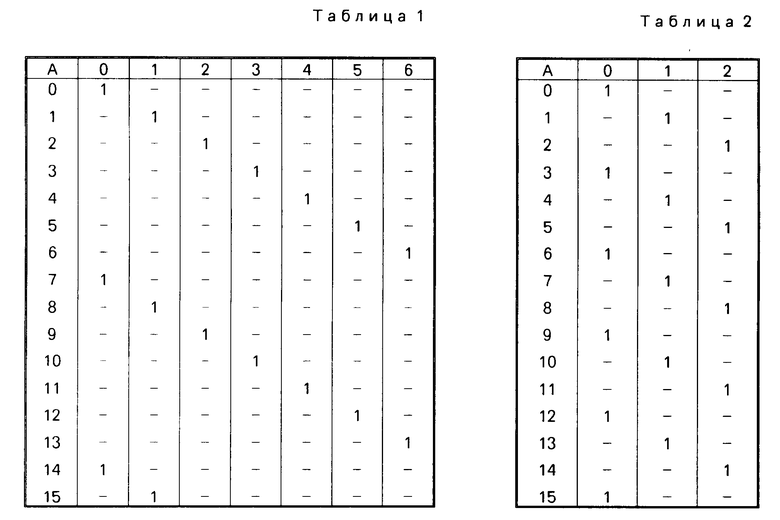

Так как предел уменьшения величины числа, от которого выделяется остаток, определяется разрядностью регистра 11, то этот предел известен заранее. Поэтому известны в этом диапазоне чисел и остатки по выбранным модулям, которые определяются по классам. Так, например, для числа А, изменяющегося от 0 до 15, остатки по модулю три разбиваются на три класса, а по модулю семь на семь классов. Распределение остатков по данным модулям представлено в табл. 1 и 2. Единица на пересечении i-ой строки и j-го столбца говорит о том, что данное i-е число входит в j-ый класс с остатком rАд.

В качестве парафазного дешифратора используется дешифратор, структура которого представлена на фиг.12.

Устройство работает в двух режимах.

Первый режим режим определения остатка по одному из двух выбранных модулей, по модулю три или по модулю семь.

Второй режим режим самопроверки устройства.

Величина остатка формируется в парафазном коде на выходе 34.

Перед началом работы устройства на входы 27-29 подается импульс сброса для приведения устройства в исходное состояние.

Исходное (нулевое) состояние триггера 1 обеспечивает формирование остатка по модулю три, а единичное по модулю семь. Со всех инверсных выходов (в исходном состоянии) регистра 10 снимаются единичные сигналы, которые обеспечивают выполнение функций, возложенных на сумматоры по модулю два, на которые поступают эти управляющие воздействия. При записи единицы в тот или иной разряд регистра 10 сумматор по модулю два, на который поступает это воздействие, выдает сигнал, эквивалентный нулю (рис.8). На информационные входы 25 поступает число, от которого необходимо определить остаток. Число поступает в монофазном коде. После каждой записи числа подается сигнал сброса на вход 29.

С выхода регистра 11 снимается уже парафазный код поступившего числа. Состояние выходов, т.е. наличие запрещенной кодовой комбинации <11> или <00> на выходах регистра, контролируется с помощью сумматоров 73/1-73/4 по модулю два в парафазном дешифраторе, наличие запрещенных кодовых комбинаций на его выходе контролируется с помощью элементов 84-86 сравнения. О наличии запрещенных кодовых комбинаций на входе или выходе дешифратора свидетельствует сигнал на выходе 31.

Таблица функций для неисправностей типа const 0 и const 1 дешифратора в режиме определения остатка приведена на фиг.13 и 14. Незаполненные клетки таблицы свидетельствуют о совпадении функции исправной работы с функцией неисправности.

Анализ неисправностей в таблицах, изображенных на фиг.13 и 14, показывает, что в процессе функционирования не обнаруживают восемь константных неисправностей и коэффициент глубины поиска дефекта при функциональном диагностировании парафазного дешифратора равен 0,77.

В соответствии с поступившим парафазным кодом на входы a1a2b1b2c1c2d1d2 возбуждается один из парафазных выходов βi1βi2 (i  ) или сокращенное их обозначение k,

) или сокращенное их обозначение k,  (где k

(где k  ), т.е. на одном из выходов формируется код <10>, а на остальных выходах код <01> Этот сигнал поступает на парафазный коммутатор 13, который в зависимости от выбранного модуля (модулю три соответствует: α11,α12_→ <10> а α21α22 _→ <01> модулю семь соответствует: α11α12 _→ <01> a α21α22 _→ <10> ) формирует остаток. Неисправности элементов 2-9 типа const 0 и const 1, обнаруживаемые в процессе их функционирования, представлены в таблице на фиг.6. Коэффициент глубины поиска дефекта для этих элементов при функциональном диагностировании равен 0,75. Сигнал, формируемый на выходе 32, будет сигнализировать о наличии данного класса неисправностей в элементах 2-9.

), т.е. на одном из выходов формируется код <10>, а на остальных выходах код <01> Этот сигнал поступает на парафазный коммутатор 13, который в зависимости от выбранного модуля (модулю три соответствует: α11,α12_→ <10> а α21α22 _→ <01> модулю семь соответствует: α11α12 _→ <01> a α21α22 _→ <10> ) формирует остаток. Неисправности элементов 2-9 типа const 0 и const 1, обнаруживаемые в процессе их функционирования, представлены в таблице на фиг.6. Коэффициент глубины поиска дефекта для этих элементов при функциональном диагностировании равен 0,75. Сигнал, формируемый на выходе 32, будет сигнализировать о наличии данного класса неисправностей в элементах 2-9.

Выходы парафазного дешифратора 12 в парафазном коммутаторе 13 подключены в соответствии с вышеприведенными табл.1 и 2.

В парафазном коммутаторе 13 (фиг.2) парафазные элементы 35-40 (звездочка означает, что это парафазный элемент) обеспечивают формирование кода по модулю три при α11α12 _→ <10> На парафазный элемент ИЛИ 35 поступают сигналы множества Х1, которое соответствует выходам дешифратора 120,  , 3,

, 3,  , 6,

, 6,  , 9,

, 9,  , 15,

, 15,  } На парафазный элемент ИЛИ 36 поступают сигналы множества Х2, которое соответствует выходам дешифратора 121,

} На парафазный элемент ИЛИ 36 поступают сигналы множества Х2, которое соответствует выходам дешифратора 121,  , 4,

, 4,  , 7,

, 7,  , 10,

, 10,  , 13,

, 13,  } На парафазный элемент ИЛИ 37 поступают сигналы множества Х3, которое соответствует выходам дешифратора 122,

} На парафазный элемент ИЛИ 37 поступают сигналы множества Х3, которое соответствует выходам дешифратора 122,  , 5,

, 5,  , 8,

, 8,  , 11,

, 11,  , 14,

, 14,  }

}

Парафазные элементы 48-61 обеспечивают формирование остатка по модулю семь при α21α22 _→ <10>

На парафазный элемент ИЛИ 48 поступают сигналы множества Х4, которое соответствует выходам дешифратора0,  , 7,

, 7,  , 14,

, 14,  }

}

На парафазный элемент ИЛИ 49 поступают сигналы множества Х5, которые соответствуют выходам дешифратора1,  , 8,

, 8,  , 15,

, 15,  }

}

На парафазный элемент ИЛИ 50 поступают сигналы множества Х6, которые соответствуют выходам дешифратора2,  , 9,

, 9,  }

}

На парафазный элемент ИЛИ 51 поступают сигналы множества Х7, которые соответствуют выходам дешифратора3,  , 10,

, 10,  }

}

На парафазный элемент ИЛИ 52 поступают сигналы множества Х8, которые соответствуют выходам дешифратора4,  , 11,

, 11,  }

}

На парафазный элемент ИЛИ 53 поступают сигналы множества Х9, которые соответствуют выходам дешифратора5,  , 12,

, 12,  }

}

На парафазный элемент ИЛИ 54 поступают сигналы множества Х10, которое соответствуют выходам дешифратора6,  , 13,

, 13,  }

}

Структура парафазного элемента ИЛИ и элемента И показана на примере парафазных элемента ИЛИ 35 и элемента И 38. Выходы парафазных элементов И 38-40 и 55-57 объединяются через парафазные элементы ИЛИ 70-72.

Работа парафазных элементов контролируется с помощью элементов 45-47 и 62-68 сравнения, выходы которых объединяются элементом ИЛИ 69, выходной сигнал которого будет свидетельствовать о наличии запрещенной кодовой комбинации <11> или <00>, а также о наличии неисправности самого элемента ИЛИ 69.

На фиг. 3 и 4 представлены таблицы функций неисправностей для одиночных неисправностей типа const 0 и const 1 для элементов 40, 41, 43 и 44 парафазного элемента ИЛИ 35 и элемента И 38, все одиночные неисправности которых обнаруживаются. В таблицах на фиг.3 и 4 представлены единичные неисправности элементов 45-69 сравнения. Неисправности типа const 1 обнаруживаются на контрольном выходе 31. Неисправности типа const 0 в процессе функционирования не обнаруживаются.

В таблицах на фиг.3 и 4 представлены неисправности типа const 01 и const 10 парафазных элементов 35-40.

Коэффициент глубины поиска дефекта для одиночных неисправностей типа const 0 и const 1 элементов 41-47 и 69, при функциональном диагностировании равен 0,75.

Одиночные неисправности типа const 0 и const 1 на выходе парафазных элементов 70-72 обнаруживаются в процессе функционирования элементами 21 и 22 сравнения.

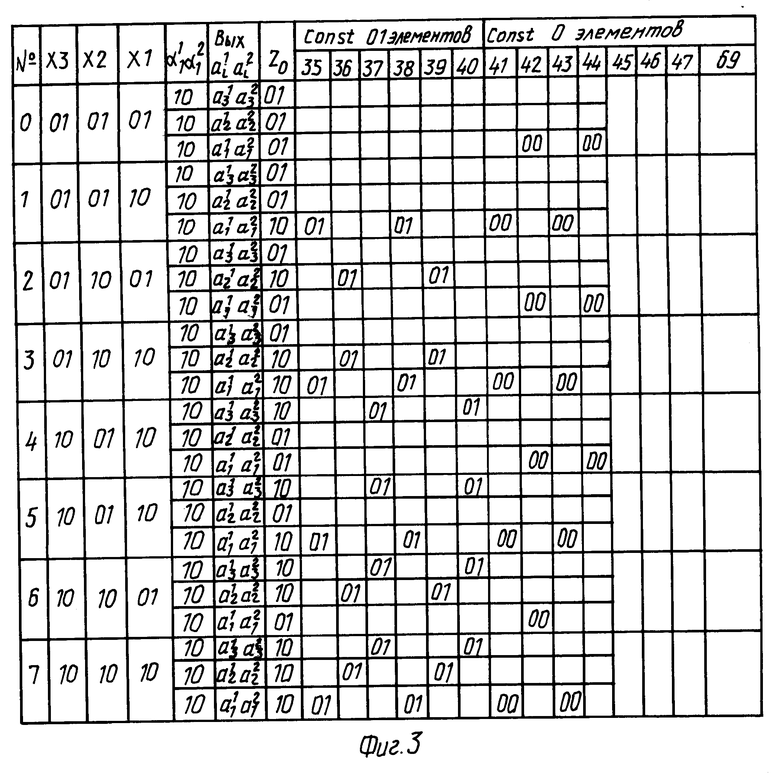

Выделенный остаток с парафазного коммутатора 13 поступает на элементы 14-19, которые обеспечивают формирование остатка в парафазном коде. Его формирование осуществляется в соответствии с табл.3.

Неисправности элементов 14-23, которые выявляются в процессе функционирования устройства представлены в таблицах на фиг.8 и 10. Коэффициент глубины поиска дефекта для этих элементов при функциональном диагностировании равен 0,8.

Второй режим функционирования устройства режим самопроверки. Он предназначен для выявления тех неисправностей устройства, которые не выявляются в процессе функционирования. С этой целью в регистр 10 самопроверки поочередно подается одно из управляющих воздействий у1,у5 на вход 26, после подачи каждого управляющего воздействия сигнал сброса на вход 28. Все управляющие воздействия с регистра 10 поступают на сумматоры 73 по модулю два 2. При поступлении управляющего воздействия на сумматор по модулю 2 на его выходе формируется сигнал, эквивалентный логическому нулю. Так при поступлении управляющего воздействия у1 1 на выходе сумматора 2 по модулю два формируется нулевой сигнал. В этом случае α11=α12=α21=α22=0 Это позволяет определить одиночные неисправности типа const 0 элементов 7 и 8 сравнения, а также элементов 45-47 и 62-68 сравнения. Это показано в таблице функций неисправностей, представленных на фиг.5 и 7, а для элементов 20-23 на фиг.9 и 11.

Для выделения невыявленных в процессе функционирования одиночных неисправностей в парафазном дешифраторе 12 подаются управляющие воздействия у2, у5, которые позволяют выявить эти неисправности. Это демонстрируется в таблицах на фиг.15-17. На фиг.15 и 16 показано, как будет реагировать устройство, если будут поданы одновременно все управляющие воздействия у2,у5 на парафазный дешифратор.

Таким образом, преимуществом предлагаемого устройства является то, что совместное использование двух указанных выше режимов позволяет добиться коэффициента глубины поиска дефекта, равного единице, причем при функциональном диагностировании коэффициент глубины поиска дефекта больше 0,7. При реализации самопроверки информационные воздействия на вход 25 не поступают, т.е. в регистре 11 записан нулевой код, и самопроверка осуществляется за счет подачи управляющих воздействий у1,у5 на входы 26. Указанный подход позволяет повысить общую контролепригодность устройства, сократить время на локализацию места неисправности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2051409C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| РЕТРАНСЛЯТОР | 1991 |

|

RU2010431C1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| Устройство для контроля состояния работоспособности центрального ядра вычислительного комплекса | 1990 |

|

SU1756891A1 |

| УСТРОЙСТВО ДЛЯ ОТСЛЕЖИВАНИЯ КОНТУРОВ ДВУМЕРНЫХ ОБЪЕКТОВ | 1991 |

|

RU2050594C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| Многоканальный коммутатор | 1985 |

|

SU1256190A1 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных машинах и контрольно-измерительной аппаратуре. Цель изобретения повышение достоверности функционирования, т.е. увеличение значения коэффициента глубины поиска дефекта при функциональном диагностировании устройства. Устройство содержит триггер 1, сумматор 2 по модулю два, элементы И 3-6, 15, 17, 19, элементы 7, 8, 20 и 21 сравнения, элементы ИЛИ 9, 14, 16, 18 и 23, регистр 10 самопроверки, регистр 11 числа, парафазный дешифратор 12 и парафазный коммутатор 13. Повышение достоверности функционирования достигается за счет построения устройства на основе положений парафазной логики. В парафазной логике логическому нулю соответствует код <01>, а логической единице <10>. Состояния <00> и <11> являются запрещенными при работе устройства. Устройство работает в двух режимах. Первый режим режим определения остатка по одному из двух выбранных модулей. Второй режим режим самопроверки устройства. Величина модуля задается подачей сигнала на триггер 1. Число, от которого определяется остаток, подается на входы регистра 11 числа. Значение остатка по выбранному модулю выдается в парафазном коде. 1 з. п. ф-лы, 18 ил. 3 табл.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выделения остатка по переменному модулю | 1984 |

|

SU1270774A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-12-27—Публикация

1991-05-16—Подача