Изобретение относится к техническим средствам обучения операторов АСУ и может быть использовано для практической подготовки операторов систем управления.

Известно устройство для обучения операторов, содержащее последовательно соединенные регистр адреса микрокоманды, блок памяти микропрограммы и регистр микрокоманды, первые выходы которого подключены к органам панели индикации, а вторые выходы регистра микрокоманды связаны с вторыми входами первого блока сравнения, первые входы которого соединены с выходами блока ответных действий, выходы регистра адреса микрокоманды разделены на три группы: выходы первой и третьей групп связаны непосредственно с блоком памяти, а второй - кроме блока памяти, через элемент ИЛИ группы - к R-входам триггеров группы, выходы блока памяти подключены к первым входам элементов И первой группы, вторые входы которых соединены с S- входом триггера, R-вход которого связан через элемент задержки с первыми входами элементов И второй группы и вторым выходом второго блока сравнения, первые входы которого подключены к выходам элементов И первой группы, вторые входы второго блока сравнения соединены с выходами блока ответных действий, первый выход второго блока сравнения связан через первый вход второго элемента ИЛИ с первым входом регистра адреса микрокоманды, второй вход которого соединен с выходом первого элемента ИЛИ, первый вход которого подключен к первому выходу первого блока сравнения, второй вход которого связан с вторым входом триггера, вторым входом первого элемента ИЛИ и первыми входами элементов И третьей группы, выходы которых соединены с S-входами триггеров группы, R-входы которых подключены к вторым входам элементов И третьей группы, единичные выходы триггеров группы через вторые входы элементов И второй группы связаны с третьими входами регистра адреса, второй вход второго элемента ИЛИ является входом запуска устройства[1] .

Недостатком данного устройства является отсутствие возможности оценки качества деятельности оператора.

Известно устройство для обучения операторов, содержащее регистр адреса, установочный вход которого является входом устройства, выход переполнения соединен с входом останова генератора, а информационные выходы подключены к соответствующим адресным входам блока памяти микропрограммы, выходы которого соединены с соответствующими информационными входами регистра микрокоманды, управляющий вход регистра микрокоманды подключен к выходу первого элемента ИЛИ и входу первого элемента задержки, выходы первой группы - к соответствующим входам информационного табло, а выходы второй группы - к соответствующим входам второй группы первого блока сравнения, управляющий вход которого соединен с выходом первого элемента задержки, а входы первой группы - с соответствующими выходами блока ввода ответных действий оператора, подключенного к соответствующим входам первого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом второго элемента задержки, выходы первого счетчика подключены к соответствующим входам шестого элемента ИЛИ и к соответствующим входам первой группы блоков сравнения первой группы, входы второй группы которых соединены с выходами соответствующих регистров первой группы, первые выходы - с входами соответствующих регистров первой группы, а вторые выходы - с входами соответствующих регистров второй группы, вход первого регистра первой группы подключен к выходу третьего элемента задержки, вход которого соединен с выходом переполнения регистра адреса, подключенным к входу четвертого элемента задержки и входу считывания первого счетчика, установочный вход которого соединен с выходом шестого элемента ИЛИ, а информационный вход - с первым выходом первого блока сравнения, второй выход которого подключен к информационному входу регистра адреса, один из информационных выходов которого соединен с входом запуска генератора, информационный вход второго счетчика подключен к выходу генератора, вход считывания - к выходу четвертого элемента задержки и входу пятого элемента задержки, установочный вход - к выходу седьмого элемента ИЛИ, а выходы - к соответствующим входам седьмого элемента ИЛИ и к соответствующим входам первой группы блоков сравнения второй группы, входы второй группы которых соединены с выходами соответствующих регистров четвертой группы, первые выходы - с входами соответствующих регистров четвертой группы, а вторые выходы - с входами соответствующих регистров третьей группы, вход первого регистра четвертой группы подключен к выходу пятого элемента задержки, выходы регистров второй и третьей групп соединены с соответствующими входами первой и второй групп соответственно сумматора и с соответствующими входами второго элемента ИЛИ, управляющий вход сумматора подключен к выходу второго элемента задержки, а выходы - к соответствующим входам дешифратора, первый выход которого соединен с входом первого индикатора, второй и третий выходы - с первым и вторым входами соответственно третьего элемента ИЛИ, четвертый и пятый выходы - с первым и вторым входами четвертого элемента ИЛИ соответственно, а шестой и седьмой выходы - с первым и вторым входами соответственно пятого элемента ИЛИ, выходы третьего, четвертого и пятого элементов ИЛИ подключены к входам соответственно второго, третьего и четвертого индикаторов [2] . Данное устройство позволяет оценить качество деятельности оператора по комплексному показателю безошибочности и своевременности, однако только по истечении тренировки, что снижает его дидактические возможности, поскольку не позволяет получить такой оценки по каждой отдельной операции алгоритма деятельности оператора.

Цель изобрения - расширение дидактический возможностей.

Поставленная цель достигается тем, что в устройство для обучения операторов, содержащее блок задания программы обучения, первый вход которого является входом устройства, первая группа выходов подключена к входам информационного табло, а вторая - к группе вторых входов блока сравнения, первая группа входов которого связана с выходами блока ввода ответных действий оператора, первый выход блока сравнения связан со счетным входом первого счетчика, выходы которого подключены к первым входам первой группы блоков сравнения, вторые входы которых связаны с выходами первого блока памяти, входы которых соединены с вторыми выходами первой группы блоков сравнения, первые входы которых подключены к управляющим входам первой группы регистров числа, выходы которых связаны через первый элемент ИЛИ и третьей задержки и непосредственно с одной группой входов сумматора, выходы которого подключены к входам дешифратора, один из выходов которого непосредственно, а три группы других - через три элемента ИЛИ связаны с индикаторами оценок, другая группа входов сумматора связана с входами первого элемента ИЛИ и выходами второй группы регистров числа, управляющие входы которых соединены с первыми выходами блоков сравнения второй группы, первая группа входов которых подключена к группам выходов блока памяти, управляющие входы которых связаны с вторыми выходами блоков сравнения второй группы, другие группы входов которых подключены к выходам второго счетчика, счетный вход которого соединен с выходом генератора, а управляющий - с выходом элемента задержки, дополнительно содержит элемент задержки, элемент ИЛИ, третий счетчик и второй дешифратор, выходы которого подключены к управляющим входам первого и второго блоков памяти, а входы - к выходам третьего счетчика, установочный вход которого соединен с входом шестого элемента ИЛИ и выходом переполнения блока задания программы обучения, который связан с входом седьмого элемента ИЛИ, выход которого подключен к управляющим входам блоков сравнения первой и второй групп, а второй вход соединен с выходом первого элемента задержки и сдвигающим входом блока задания программы обучения, третья группа выходов которого через пятый элемент ИЛИ связана с входом запуска генератора, вход останова которого подключен к выходу пятого элемента ИЛИ, вход которого соединен с входом четвертого элемента задержки, счетным входом третьего счетчика, входом первого элемента задержки, вторым выходом блока сравнения, управляющим входом первого счетчика, входом второго элемента задержки, выход которого соединен с управляющими входами первых блоков сравнения первой и второй групп.

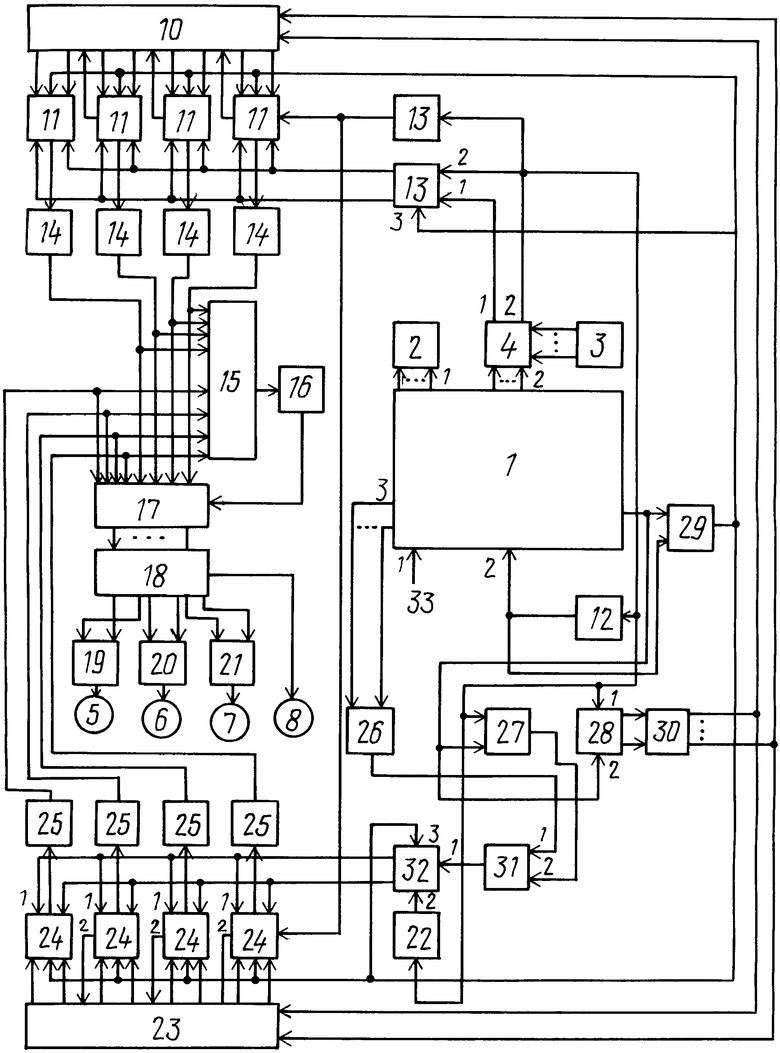

На чертеже представлена схема предлагаемого устройства.

Устройство содержит блок 1 задания программы обучения, панель 2 индикации, блок 3 ввода ответных действий оператора, блок 4 сравнения, первый 5, второй 6, третий 7 и четвертый 8 индикаторы, первый 9 счетчик, первый блок 10 памяти, первая группа 11 блоков сравнения, первый элемент 12 задержки, второй 13 элемент задержки, первая группа 14 регистров числа, первый элемент 15 ИЛИ, третий элемент 16 задержки, сумматор 17, первый дешифратор 18, второй 19, третий 20, четвертый 21 элементы ИЛИ, четвертый 22 элемент задержки, второй блок 23 памяти, вторую группу 24 блоков сравнения, вторую группу 25 регистров числа, пятый элемент ИЛИ 26, шестой элемент ИЛИ 27, третий счетчик 28, седьмой элемент ИЛИ 29, второй дешифратор 30, генератор 31 импульсов, второй счетчик 32, вход 33 сигнала запуска устройства.

Блок 1 предназначен для хранения параметров отрабатываемых алгоритмов управления и содержит последовательно соединенные регистр адреса микрокоманды, блок памяти микропрограммы и регистр микрокоманды. Каждая микрокоманда имеет две микрооперации, в первой хранится код органа панели 2, который изменяет свое состояние в данной операции; во второй - код органа блока 3, на который оператор обязан воздействовать в этой же операции, их выходы соответствуют по первой и второй групп выходов блока 1. Третья группа выходов связана с выходами регистра адреса микрокоманды. Выход блока 1 связан с выходом переполнения регистра адреса микрокоманды. Первый вход блока 1 установочный, а второй - сдвигающий вход регистра адреса микрокоманды. Панель 2 и блок 3 ввода ответных действий оператора являются физической моделью пульта оператора - его рабочего места в АСУ.

Блок 6 сравнения предназначен для определения степени безошибочности действий оператора за счет сравнения задействованного и требуемого органов блока 3 ответных действий оператора.

Индикаторы 5-8 предназначены для предъявления обучаемому соответственно "неудовлетворительной", "удовлетворительной", "хорошей" и "отличной" оценок за каждое выполненное действие.

Первый счетчик 9 предназначен для подсчета числа допущенных оператором ошибок в каждой элементарной операции. При поступлении сигнала на его второй вход содержимое счетчика переписывается по первым входам в блоке 11 сравнения первой группы.

Первый блок 10 памяти количества ошибок предназначен для хранения в ячейках памяти количества ошибок.

В первой ячейке записано такое количество ошибок первой элементарной операции, которые соответствуют оценке "отлично". Во второй ячейке записано такое количество ошибок первой элементарной операции, которые соответствуют оценке "хорошо". В третьей и четвертой ячейках записаны количества ошибок первой элементарной операции, соответствующие оценкам "удовлетворительно" и "неудовлетворительно" соответственно.

С пятой по восьмую ячейках записаны количества ошибок для второй элементарной операции аналогично первым. В первом блоке 10 памяти заполняются столько четырехкратных ячеек, сколько элементарных операций имеется в алгоритме управления.

В первой группе блоков 11 эти значения сравниваются с содержимым первого счетчика 9. Первая группа 14 регистров служит для хранения двоичных кодов оценок, в частности, "отлично" - 101, "хорошо" - 100, "удовлетворительно" - 011, "неудовлетворительно" - 010.

Сумматор 17 предназначен для суммирования кодов оценок, поступающих с первой 14 и второй 25 групп регистров. Первый дешифратор 18 позволяет по сумме оценок за безошибочность и своевременность определить общую оценку обучаемому. Второй блок 23 памяти хранит соответствующие временные нормативы в четырехкратных ячейках аналогично первому блоку 10 памяти.

Вторая группа блоков 24 сравнения служит для хранения затраченного оператором времени при выполнении заданного алгоритма с нормативными значениями времени соответствующих выставлению отличной, хорошей, удовлетворительной и неудовлетворительной оценок. Вторая группа 25 регистров хранит коды оценок за своевременность действий оператора. Их информация аналогична содержимому первой группы 14 регистров. Второй счетчик 32 с помощью генератора 31 подсчитывает время, затраченное оператором на выполнение каждой элементарной операции. Третий счетчик 28 служит для подсчета элементарных операций. Второй дешифратор 30 служит для нахождения в соответствии с номером элементарной операции ячеек памяти в первом 10 и во втором 23 блоках памяти. Генератор 31 служит для преобразования времени, затраченного на выполнение операции в цифровой код - в количестве тактовых импульсов.

Устройство функционирует следующим образом.

С включением тренажера за счет появления сигнала на входе 33 управляющий сигнал поступает на первый вход блока 1 задания программы обучения. Из регистра адреса считывается адрес первой микрокоманды в блок памяти микропрограммы, а также через пятый элемент 26 ИЛИ запускается генератор 31, импульсы с выхода которого поступают на первый вход второго счетчика 32. Содержимое первой микрокоманды поступает в регистр микрокоманды блока 1. С первых его выходов код органа индикации поступает на панель 2, где требуемый орган изменяет свое состояние. Человек-оператор, воспринимая это изменение состояния органа индикации, выполняет соответствующее воздействие на орган блока 3. Код задействованного органа поступает на первый вход блока 4 сравнения, по этой команде содержимое второй микрооперации микрокоманды (код требуемого органа индикации) считывается из регистра микрокоманды по вторым входам в блок 4 сравнения, в котором происходит сравнение поступивших кодов.

Если совпадение кодов не происходит, то фиксируется ошибка оператора и сигнал с первого выхода блока 4 сравнения поступает на первый вход первого 9 счетчика. Каждый раз при наличии ошибки содержимое счетчика увеличивается на единицу. При совпадении кодов в блоке 4 сигнал с второго выхода блока 4 сравнения поступает на входы второго 13, первого 12, четвертого 22 элементов задержек, а на второй вход считывания первого счетчика 9 для считывания содержимого его в блоки 11 сравнения первой группы по первым входам на первый вход шестого элемента ИЛИ 27.

Управляющий сигнал с выхода шестого элемента ИЛИ 27 поступает на второй вход генератора 32 для его останова и на первый вход третьего счетчика 28, увеличивая тем самым его содержимое на единицу, которая считывается во второй дешифратор 30. По признаку первой элементарной операции с первого 10 и второго 23 блоков памяти с первых четырех ячеек количества ошибок и нормативное время считывается соответственно по вторым входам блоков сравнения первой 11 и второй 24 группы.

Сигнал с выхода второго элемента 13 задержки поступает на третий вход первого блока первой группы 11 блоков сравнения, где происходит сравнение числа допущенных оператором ошибок с числом, которое было считано с первой ячейки первого 10 блока памяти и соответствует выставлению оценки "отлично".

Если совпадение происходит, то сигнал с первого выхода первого блока первой группы 11 поступает на управляющий вход регистра 14 первой группы и код отличной оценки переписывается в сумматор 17.

Если совпадения не происходит, то сигнал с второго выхода первого блока первой группы 11 поступает на управляющий третий вход второго блока первой группы 11, где число ошибок, допущенных оператором, сравнивается с числом, которое было считано с второй ячейки первого 10 блока памяти и соответствует выставлению хорошей оценки и т. д. до четвертых блоков первой группы 11 и регистров 14 первых групп при неудовлетворительной оценке действий обучаемого.

Сигнал с выхода четвертого элемента 22 задержки поступает на второй вход второго счетчика 31. По этой команде его содержимое переписывается по первым входам в блоки сравнения 27 второй группы.

Сигнал с выхода пятого элемента 13 задержки поступает на управляющий третий вход первого блока 24 сравнения второй группы. Если при сравнении коды требуемого (временной норматив для отличной оценки) и затраченного времени совпадают, то сигнал с первого выхода первого блока 27 сравнения второй группы поступает на первый регистр 25 второй группы и с его выхода код отличной оценки (по времени) поступает на соответствующий вход сумматора 17.

Если совпадение кодов требуемого и затраченного времени в первом блоке 24 сравнения второй группы не происходит, то управляющий сигнал с последнего поступает на третий вход второго блока 24 сравнения второй группы, где сравнивается код требуемого времени, соответствующий хорошей оценке, и затраченного оператором времени и т. д. до четвертого блока 24 сравнения и регистра 25 вторых групп при неудовлетворительной оценке действий обучаемого.

В сумматоре 17 происходит сложение кодов оценок за безошибочность и своевременность действий обучаемого. Если сумма равняется "10", то сигнал появляется на соответствующем выходе первого дешифратора 18 и поступает на индикаторы 8, засвечивая его, что соответствует получению оператором комплексной отличной оценки. Если сумма баллов составляет "8" или "9", то оператору выставляется хорошая оценка, если "6" или "7" - то удовлетворительная, а если меньше "6" - неудовлетворительная.

Сигнал с выхода первого элемента 12 задержки поступает на второй вход блока 1 задания программы обучения и на второй вход седьмого элемента ИЛИ 29, с выхода которого управляющий сигнал поступает на третьи входы первого 9 и второго 32 счетчиков и на четвертые входы блоков 11 и 24 сравнения первой и второй групп соответственно для их обучения.

При поступлении сигнала на второй вход блока 1 задания программы обучения производится сдвиг к следующей ячейке и считывание адреса очередной микрокоманды из блока памяти микропрограммы и устройство функционирует аналогично описанному выше порядку, причем, когда содержимое третьего счетчика 28 увеличивается на единицу, то с первого 10 и второго 23 блоков памяти считываются количества ошибок и нормативное время с пятых по восьмую ячейкам.

По окончании работы сигнал с последней ячейки регистра адреса микрокоманды блока 1 поступает на вход элемента ИЛИ 29 для обнуления первого 9 второго 32 счетчиков и блоков 11 и 24 сравнения первой и второй групп соответственно, на входы счетчика 28 и элемента ИЛИ 27 для обнуления счетчика 28 и останова генератора 31 соответственно.

Предлагаемое устройство расширяет дидактические возможности за счет пооперационной комплексной оценки обучаемого по показателям безошибочности и своевременности каждого выполняемого действия, что особенно важно на заключительных тренировках для выработки навыков исполнительской основы деятельности оператора АСУ. (56) 1. Авторское свидетельство СССР N 1336084, кл. G 09 B 9/00, 1986.

2. Авторское свидетельство СССР N 1425762, кл. G 09 B 9/00, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011226C1 |

| Устройство для обучения операторов | 1989 |

|

SU1695363A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011229C1 |

| Устройство для обучения операторов | 1988 |

|

SU1711220A1 |

| Устройство для обучения операторов | 1990 |

|

SU1797139A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011227C1 |

| Устройство для обучения операторов | 1987 |

|

SU1425762A1 |

| Устройство для обучения операторов | 1987 |

|

SU1587560A1 |

| Устройство для обучения операторов | 1986 |

|

SU1361604A1 |

Использование: технические средства обучения операторов АСУ. Сущность изобретения: устройство содержит блок задания программы обучения, панель индикации, блок ввода ответных действий оператора, блок сравнения, четыре элемента задержки, три счетчика, сумматор, два дешифратора, две группы блоков сравнения, две группы регистров числа, два блока памяти, семь элементов ИЛИ, генератор импульсов, четыре индикатора оценок. 1 ил.

УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ, содержащее блок сравнения, с первого по седьмой элементы ИЛИ, с первого по четвертый элементы задержки, первый счетчик, генератор импульсов, блок задания программы, установочный вход которого является входом сигнала запуска устройства, выходы первой группы которого подключены к входам панели индикации, выходы второй группы - к входам первой группы блока сравнения, входы второй группы которого соединены с выходами блока ввода ответных действия оператора, первый выход блока сравнения соединен со счетным входом первого счетчика, выходы которого подключены к первым и вторым входам блоков сравнения первой группы, входы группы которых подключены к выходам первого блока памяти, информационные входы которого соединены с первыми выходами блоков сравнения первой группы, вторые выходы которых подключены к управляющим входам регистров числа первой группы, выходы которых соединены с информационными входами первой группы сумматора и входами первой группы первого элемента ИЛИ, выход которого соединен с входом третьего элемента задержки, выход которого подключен к управляющему входу сумматора, выходы которого соединены с входами дешифратора, одни из выходов которого подключены к входам соответственно второго, третьего и четвертого элементов ИЛИ, выходы которых и другой выход дешифратора соединены с индикаторами оценок, входы второй группы первого элемента ИЛИ и информационные входы второй группы сумматора подключены к выходам регистров числа второй группы, управляющие входы которых соединены с первыми выходами блоков сравнения второй группы, входы группы которых соединены с выходами второго блока памяти, вторые выходы блоков сравнения второй группы соединены с информационными входами второго блока памяти, отличающееся тем, что, с целью расширения дидактических возможностей устройства, оно содержит второй и третий счетчики и второй дешифратор, выходы которого соединены с управляющими входами первого и второго блоков памяти, а входы - с выходами третьего счетчика, установочный вход которого и первый вход шестого элемента И соединены с выходом блока задания программы обучения, подключенным к первому входу седьмого элемента И, выход которого соединен с первыми управляющими входами блоков сравнения первой и второй групп, второй вход седьмого элемента И соединен с выходом первого элемента задержки, подключенным к управляющему входу блока задания программы обучения, выходы третьей группы которого подключены к входам пятого элемента ИЛИ, выход которого соединен с входом запуска генератора импульсов, вход останова которого подключен к выходу шестого элемента ИЛИ, второй вход которого подключен к одному из выходов блока сравнения, соединенному с входами второго, первого и четвертого элементов задержки, счетным входом третьего и установочным входом первого счетчиков, выход второго элемента задержки соединен с вторыми управляющими входами блоков сравнения первой и второй групп, выход генератора импульсов подключен к счетному входу второго счетчика , установочный вход которого подключен к выходу четвертого элемента задержки, входы сброса первого и второго счетчиков подключены к выходу седьмого элемента ИЛИ, соединенному с управляющими входами блоков сравнения первой и второй групп, выход второго элемента задержки подключен к установочным входам первых блоков сравнения первой и второй групп, выходы второго счетчика соединены с первыми и вторыми входами блоков сравнения второй группы.

Авторы

Даты

1994-04-15—Публикация

1991-04-01—Подача