Изобретение относится к техническим средствам обучения операторов АСУ и может быть использовано для практической подготовки операторов систем управления.

Известны устройства обучения, см. RU N 2024067 30.11.94 "Тренажер операторов систем управления" МПК G 09 B 9/00; RU N 2051420 27.12.95 "Устройство для контроля профессиональных навыков оператора" МПК G 09 9/00. В каждое из указанных устройств входят блок ввода информации, блок ввода эталонов, счетчик, блок памяти, сумматор, счетчики ошибок, блок формирования адреса. Данные устройства позволяют оценить качество деятельности оператора по комплексному показателю зрительно-двигательных навыков, однако только по истечении тренировки, что снижает их дидактические возможности.

Из известных устройств наиболее близким к заявленному устройству (прототипом) по своей технической сущности является известное устройство для обучения операторов, см. изобретение RU N 2011228 от 01.04.91 "Устройство для обучения операторов" МПК G 09 B 9/00, опубликованное 15.04.94, бюллетень N 7. Устройство-прототип состоит из блока задания программы обучения, панели индикации, блока ввода ответных действий оператора, блока сравнения, счетчика, блока памяти, элемент задержки, регистр числа, элемент ИЛИ, сумматор, дешифратор, генератор импульсов.

Это устройство по сравнению с вышеназванными устройствами расширяет их дидактические возможности путем введения дополнительного показателя - своевременности выполнения операций.

Однако устройство - прототип имеет следующие недостатки:

- не позволяет оценивать знания обучаемых как способность отвечать на поставленные вопросы, в том числе и в виде предложений естественного языка;

- не задает программу обучения в виде последовательности контрольных заданий и соответствующих им эталонных ответов.

Целью изобретения является разработка устройства обучения операторов с более широкими дидактическими возможностями. Поставленная цель достигается тем, что в известное устройство обучения операторов, содержащее блок задания программ обучения, панель индикации, блок ввода ответных действий оператора, блок сравнения, счетчик, блок памяти, элемент задержки, регистр числа, элемент ИЛИ, сумматор, дешифратор, генератор импульсов, добавлены блок сравнения семантических элементов, дополнительный блок первой группы элементов сравнения, дополнительный блок первой группы регистров числа, блок второй группы индикаторов, дополнительный блок второй группы регистров числа, блок второй группы элементов сравнения, второй блок расширения памяти. При этом входы блока сравнения соединены с соответствующими выходами блока задания программ обучения, первые четыре выхода которого соединены с соответствующими входами панели индикации. Третий вход первого счетчика соединен в параллель с первыми выходами блока сравнения и блока сравнения семантических элементов, второй выход которого соединен с входом соответствующего элемента задержки. Пятый и шестой выходы блока задания программ обучения соединены с первым и вторым входами блока сравнения, а седьмой и восьмой выходы блока задания программ обучения соединены с соответствующими входами блока сравнения семантических элементов, третий и четвертый входы которого соединены соответственно с пятым и шестым выходами блока ввода ответных действий оператора, первый и второй выходы которого соединены соответственно с третьим, четвертым и пятым входами блока сравнения, а четвертый выход блока ответных действий оператора соединен с первым входом блока задания программ обучения. Выходы первого и пятого элементов задержки соединены с соответствующими водами управления первого и дополнительного блоков первой группы элементов сравнения, соответственно N и K выходов которых соединены с одноименными входами первого и дополнительного блоков первой группы регистров числа. N и K выходов первого и дополнительного блоков первой группы регистров числа соединены в параллель с соответствующими входами первого элемента ИЛИ и сумматора, первые N и вторые K выходов которого соединены с соответствующими входами первого дешифратора, N выходов которого соединены с одноименными входами блока первой группы элементов ИЛИ, выходы которого подключены к соответствующим входам первой и второй группы индикаторов. Соответственно N и K выходов второго блока памяти и второго блока расширения памяти подключены к одноименным входам основного и дополнительного блоков второй группы элементов сравнения, N и K выходов которых соединены с соответствующими входами основного и дополнительного блоков второй группы регистров числа. Соответственно N и K выходов основного и дополнительного блоков второй группы регистров числа подключены в параллель с одноименными входами сумматора и первого элемента ИЛИ, выход которого соединен с входом третьего элемента задержки, выход которого подключен к управляющему входу сумматора. N и K входов соответствующих второго блока памяти и второго блока расширения памяти соединены с одноименными входами первого блока памяти и первого блока расширения памяти, а также с одноименными выходами второго дешифратора, первый и второй входы которого подключены к соответствующим входам третьего счетчика, первый вход которого соединен с девятым выходом блока задания программ обучения и одновременно с первыми входами шестого элемента ИЛИ и четвертого элемента задержки. Второй вход шестого элемента ИЛИ подключен одновременно к второму входу третьего счетчика и девятому выходу блока задания программ обучения, а выход шестого элемента ИЛИ соединен с входом "останов." генератора импульсов, первый вход которого подключен к выходу пятого элемента ИЛИ. Выход генератора импульсов соединен с третьим входом второго счетчика, выход которого соединен одновременно со всеми входами основного и дополнительного блоков второй группы регистров числа. Первый и второй входы второго счетчика соединены соответственно с первым входом первого счетчика и выходом четвертого элемента задержки. Выход седьмого элемента ИЛИ соединен одновременно с первым входом второго счетчика и со всеми входами основного и дополнительного блоков второй группы элементов сравнения. Десятый и одиннадцатый выходы блока задания программ обучения подключены к соответствующим входам пятого элемента ИЛИ. Второй вход блока задания программ обучения соединен одновременно с выходом первого элемента задержки и первым входом седьмого элемента ИЛИ, второй вход которого подключен к девятому выходу блока задания программ обучения.

Предлагаемое устройство позволяет оценить как сенсорно-моторные навыки обучаемого, так и проконтролировать его знания с помощью контрольных заданий, требующих ответов в виде предложений естественного языка.

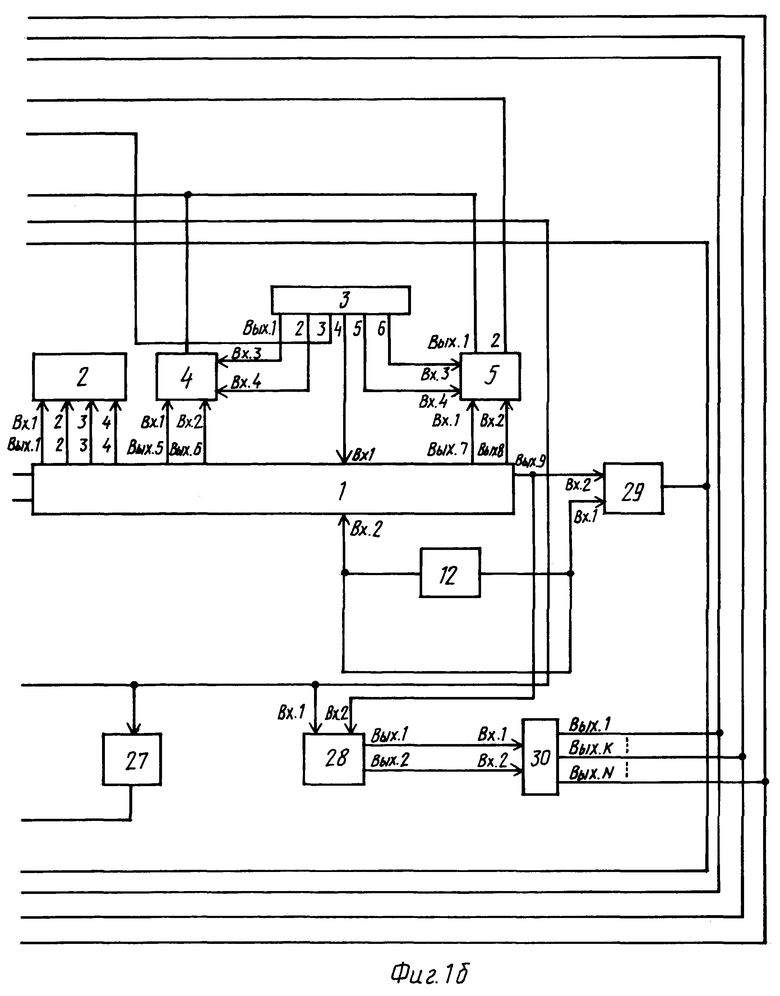

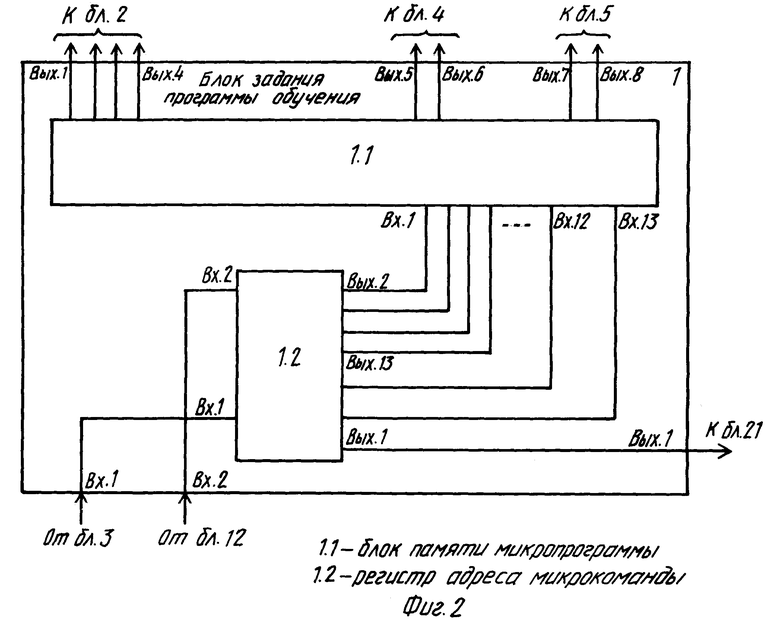

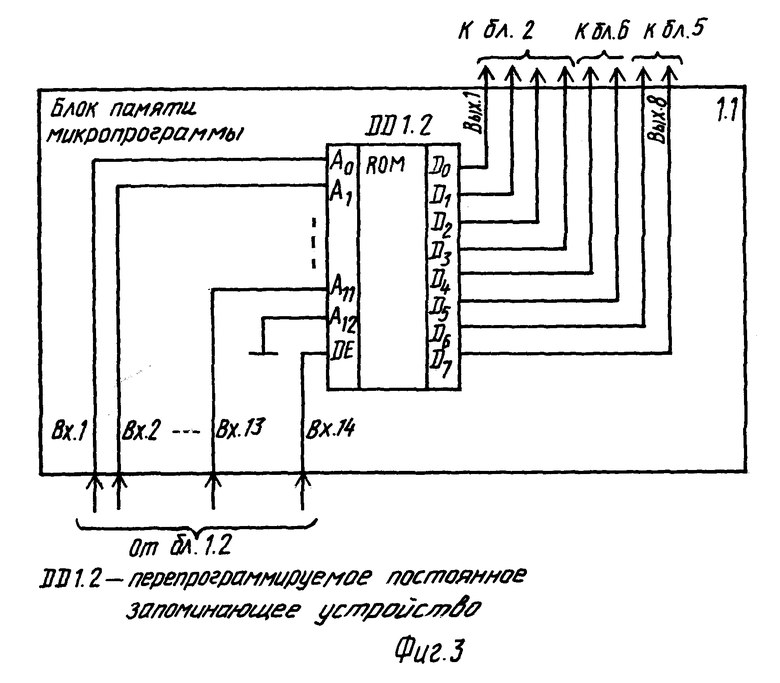

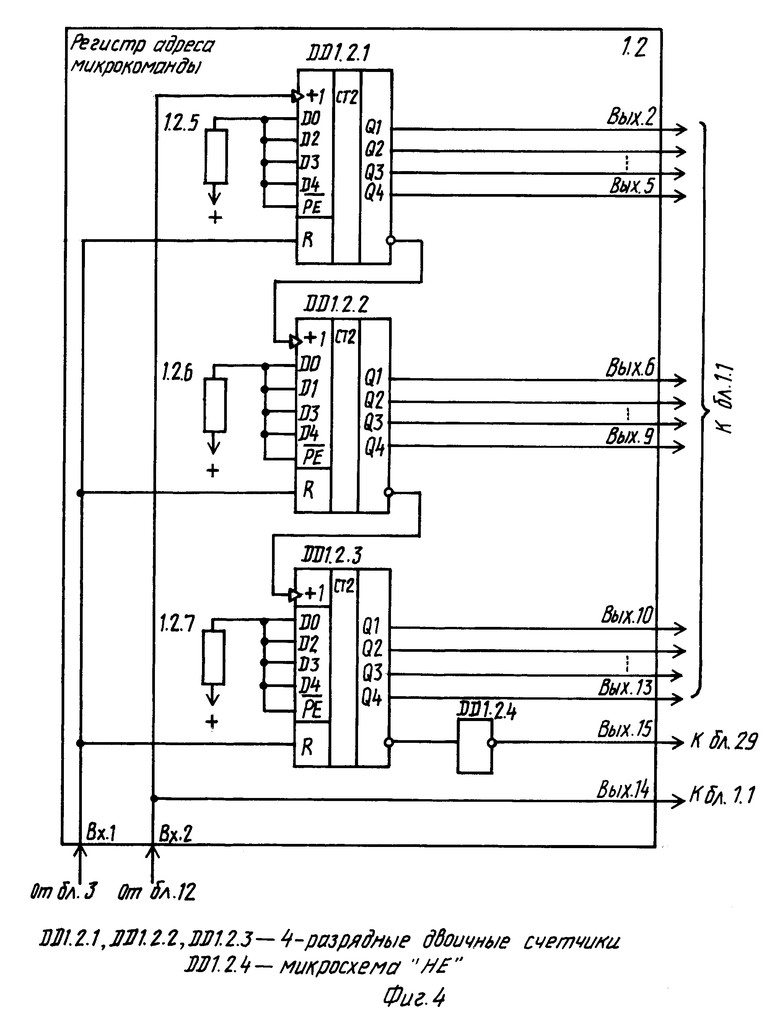

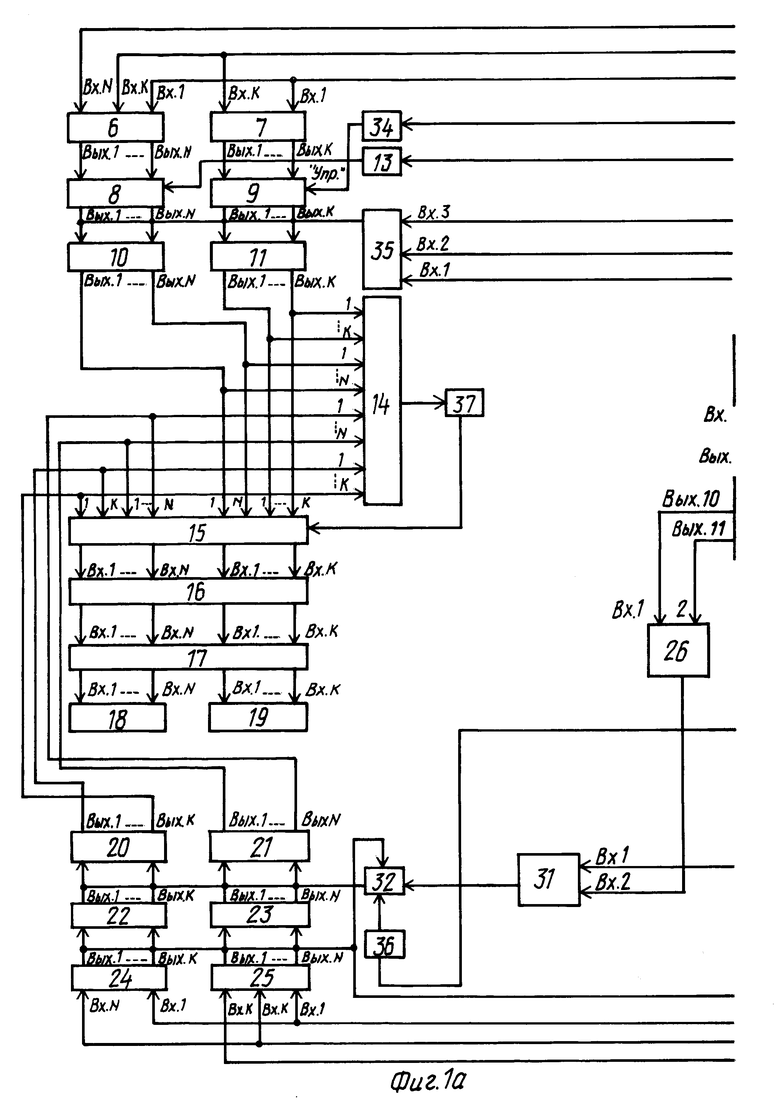

Заявленное устройство поясняется чертежами, на которых показаны:

- фиг. 1а и фиг. 1б - структурная схема заявленного устройства обучения операторов;

- фиг. 2 - структурная схема блока задания программ обучения;

- фиг. 3 - вариант структурной схемы блока памяти микропрограмм;

- фиг. 4 - структурная схема регистра адреса микропрограммы;

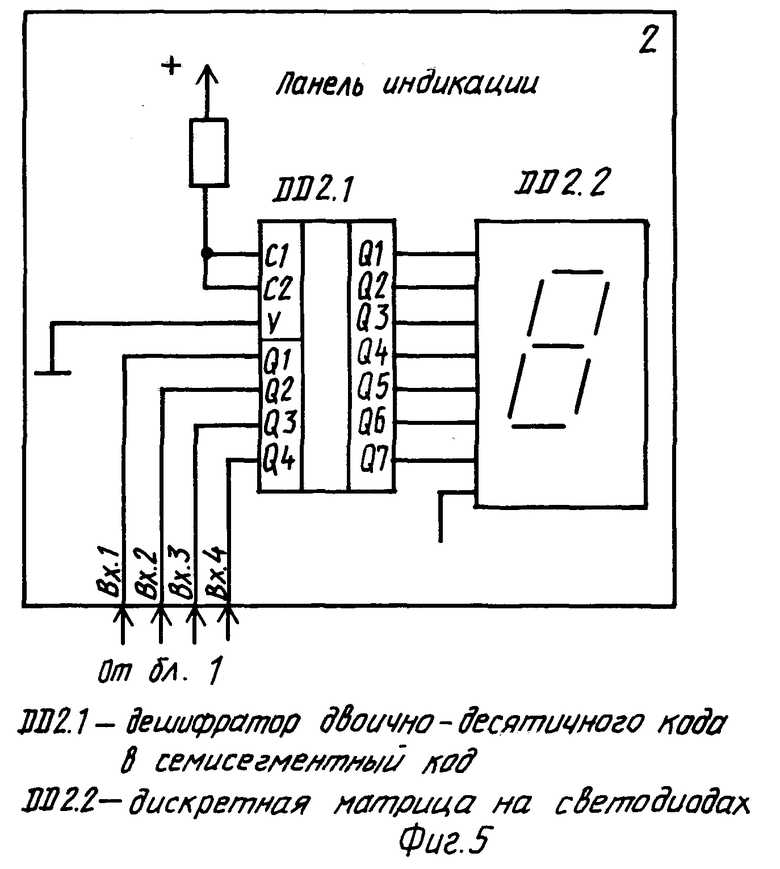

- фиг. 5 - структурная схема панели индикации;

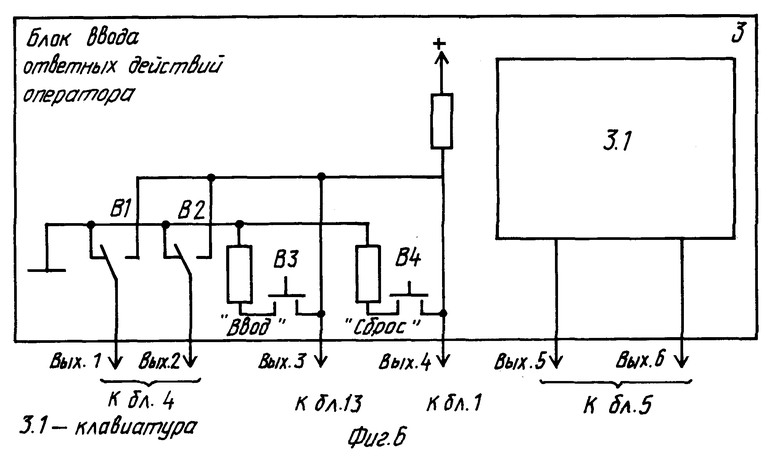

- фиг. 6 - структурная схема блока ответных действий оператора;

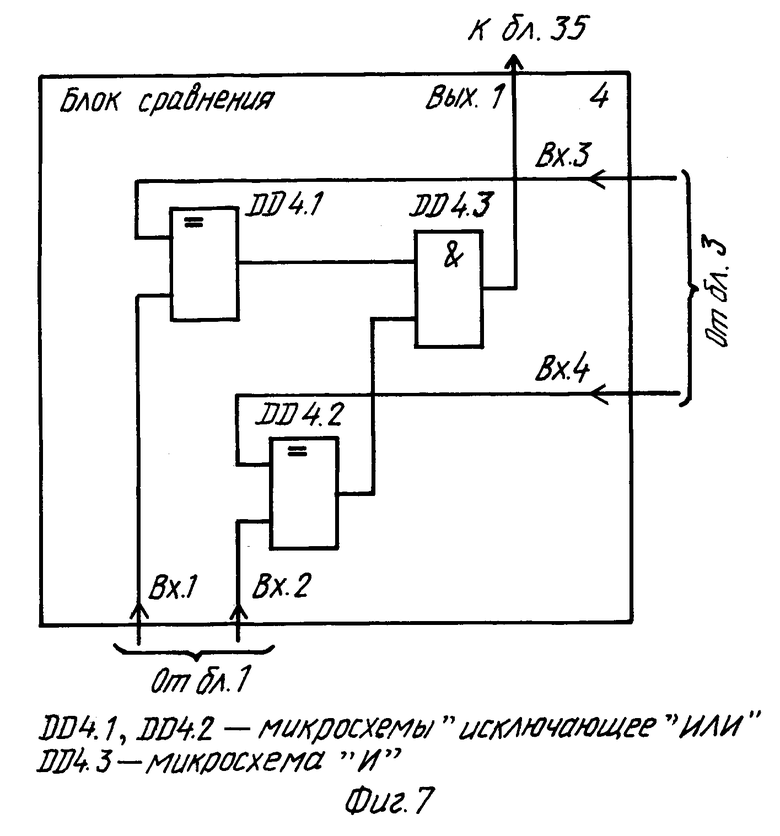

- фиг. 7 - структурная схема блока сравнения;

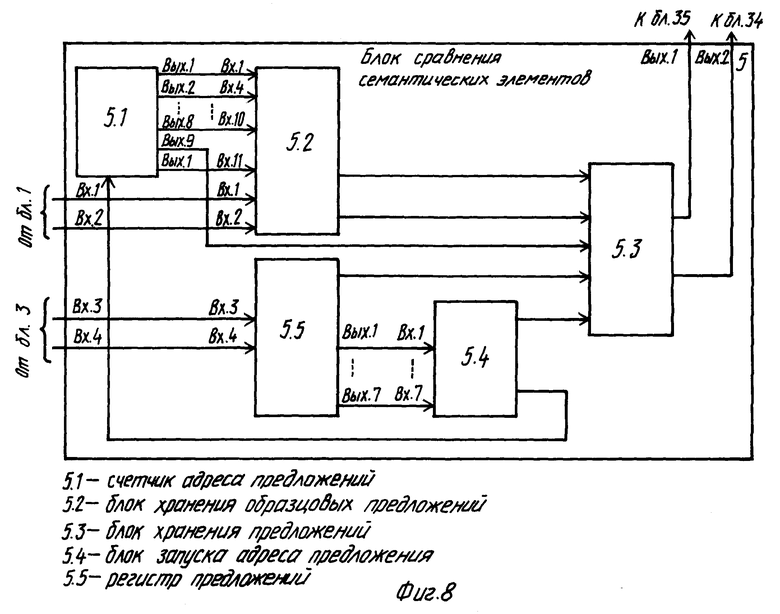

- фиг. 8 - структурная схема блока сравнения семантических элементов;

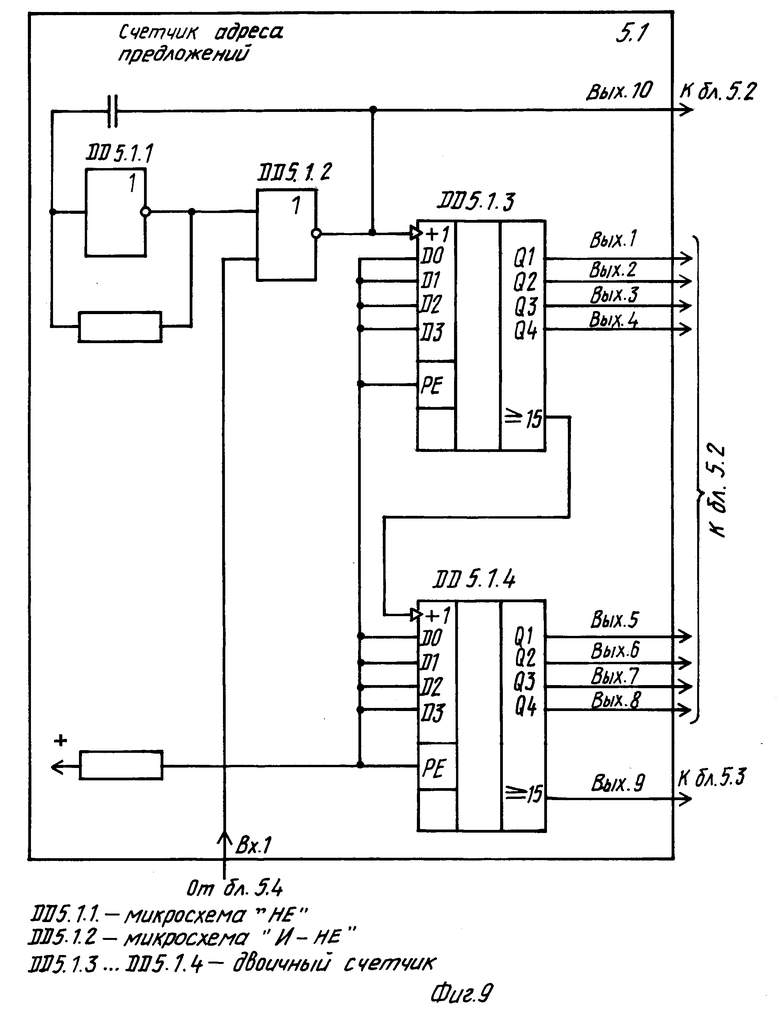

- фиг. 9 - структурная схема счетчика адреса предложений;

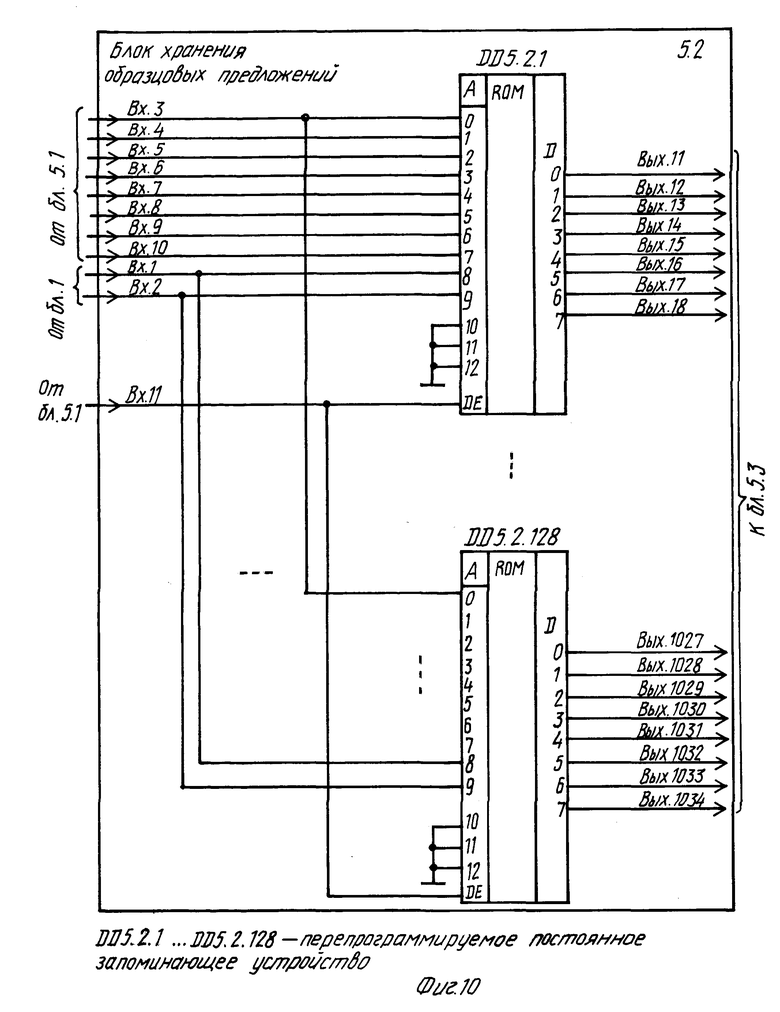

- фиг. 10 - вариант структурной схемы блока хранения эталонных предложений;

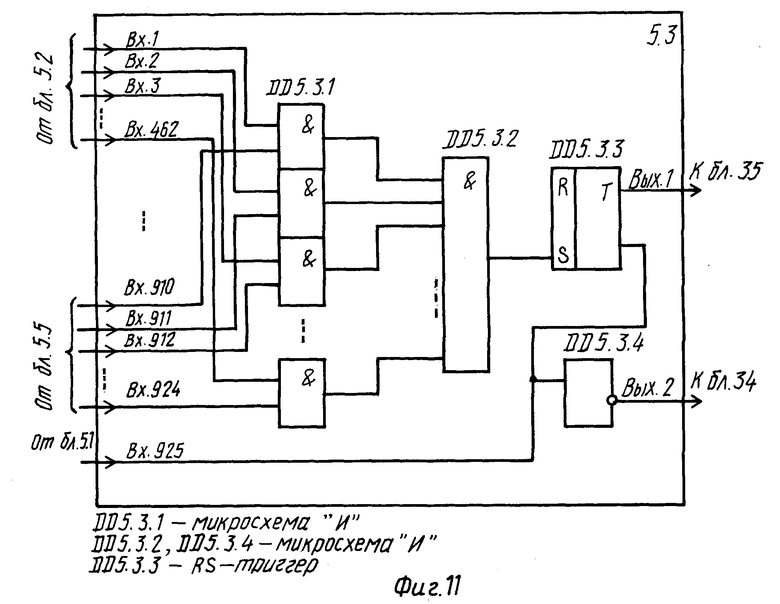

- фиг. 11 - структурная схема блока сравнения предложений;

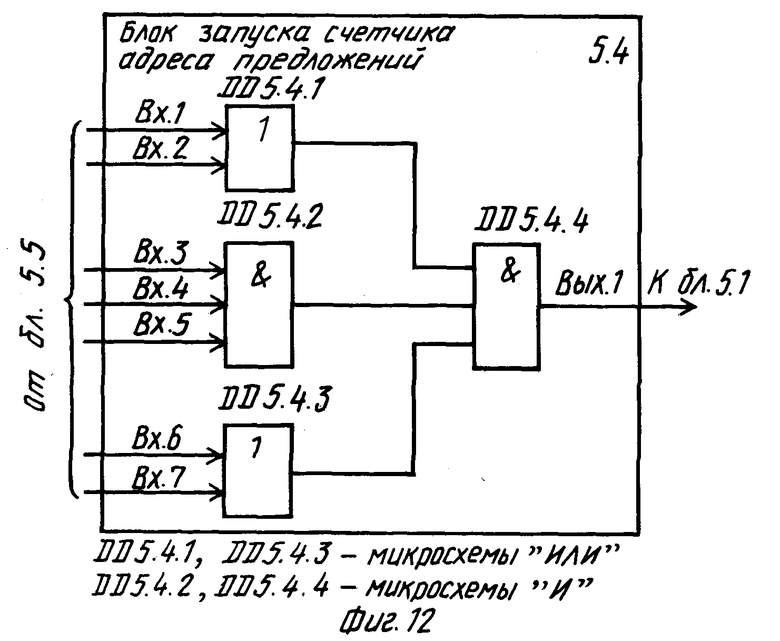

- фиг. 12 - вариант структурной схемы блока запуска счетчика адреса эталонных предложений;

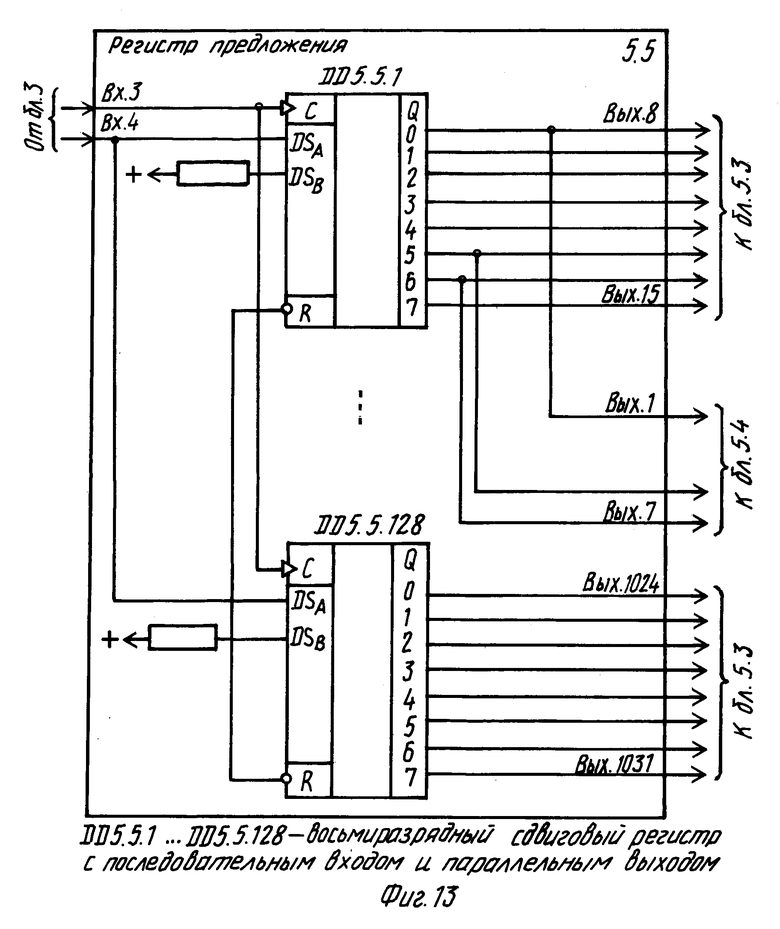

- фиг. 13 - вариант структурной схемы регистра предложений;

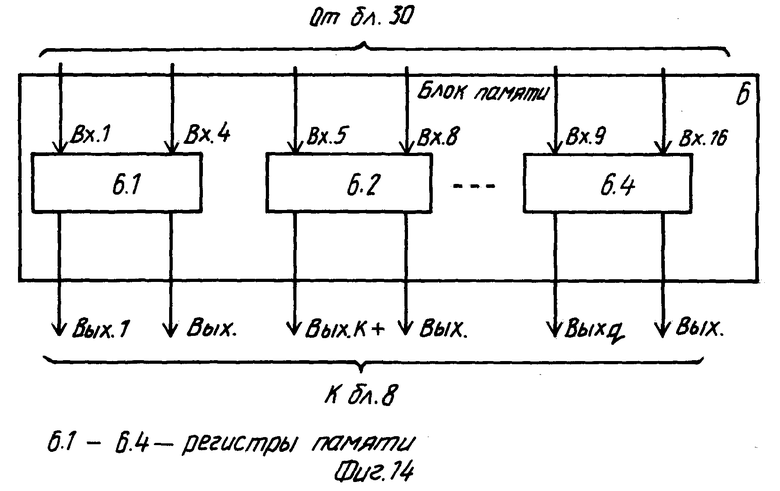

- фиг. 14 - структурная схема блока памяти;

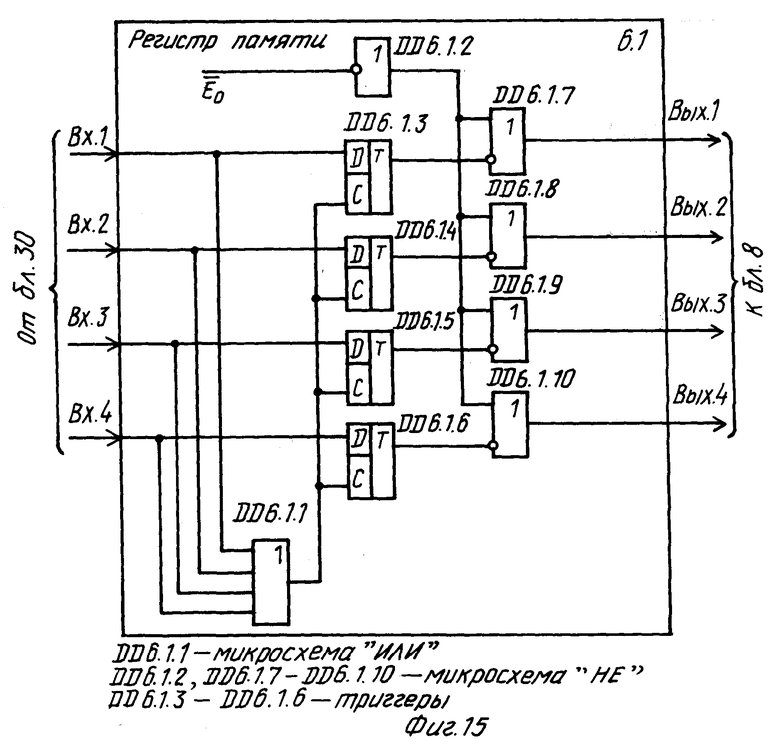

- фиг. 15 - вариант структурной схемы регистра памяти;

- фиг. 16 - структурная схема блока элементов сравнения;

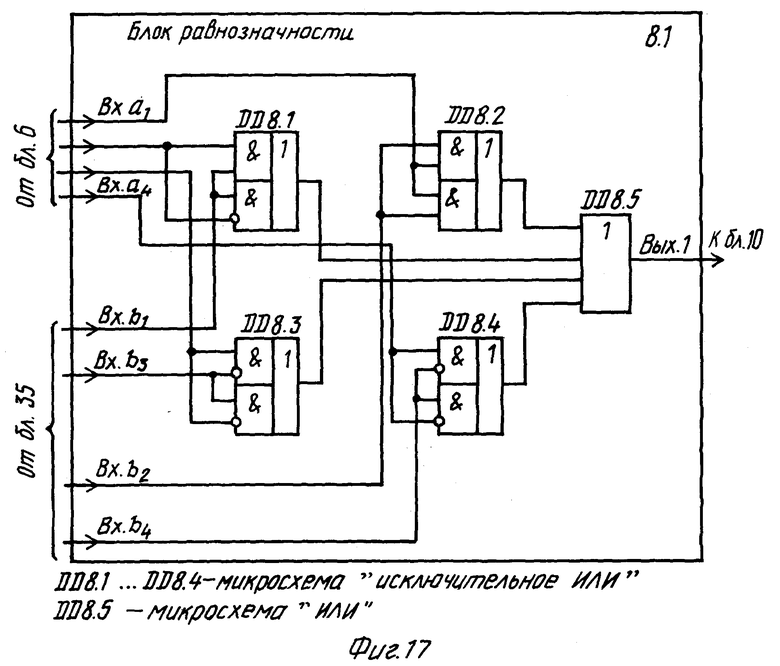

- фиг. 17 - вариант структурной схемы равнозначности;

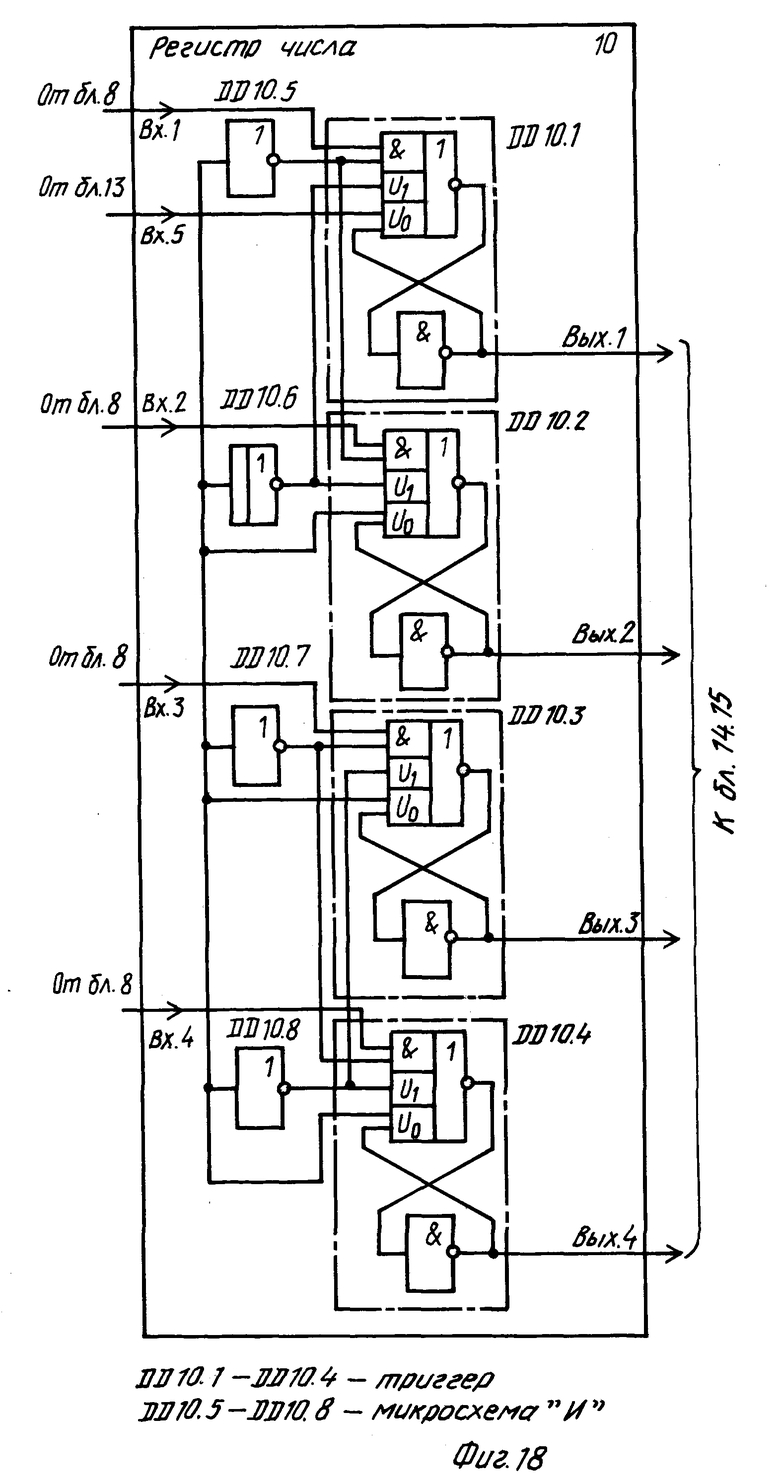

- фиг. 18 - вариант структурной схемы регистра числа;

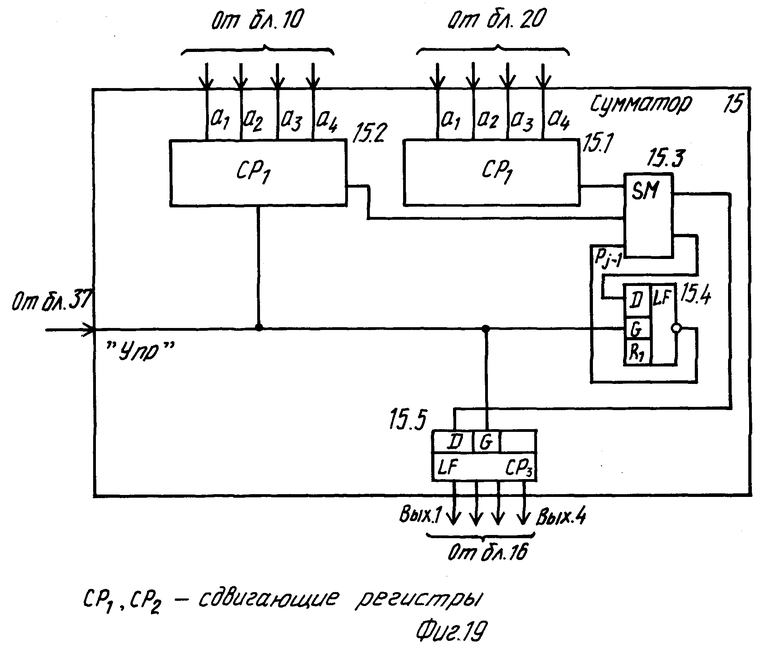

- фиг. 19 - вариант структурной схемы сумматора;

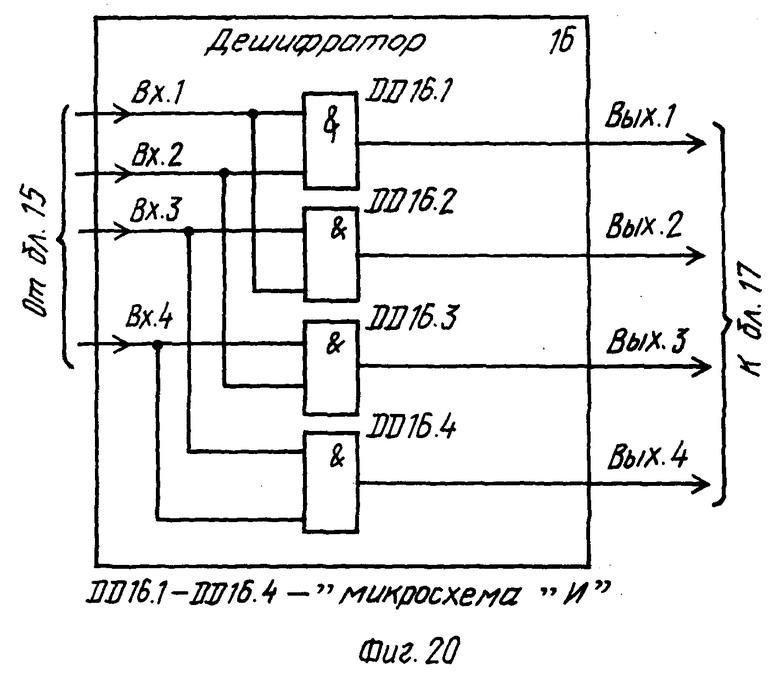

- фиг. 20 - вариант структурной схемы дешифратора;

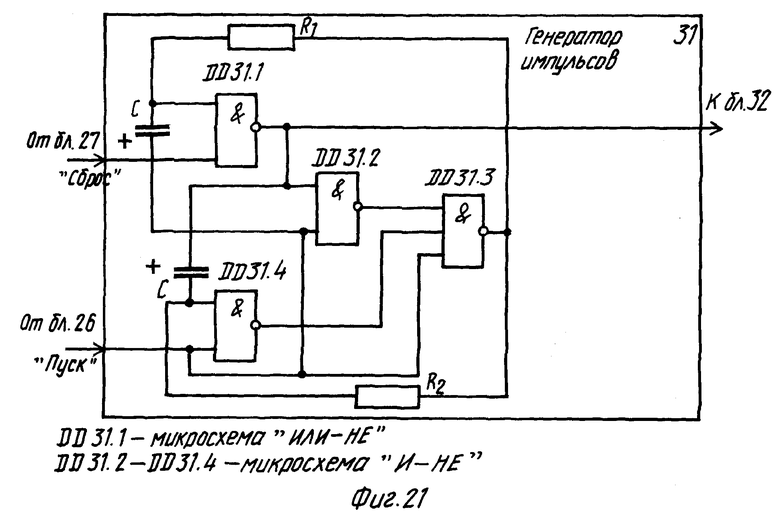

- фиг. 21 - структурная схема генератора импульсов;

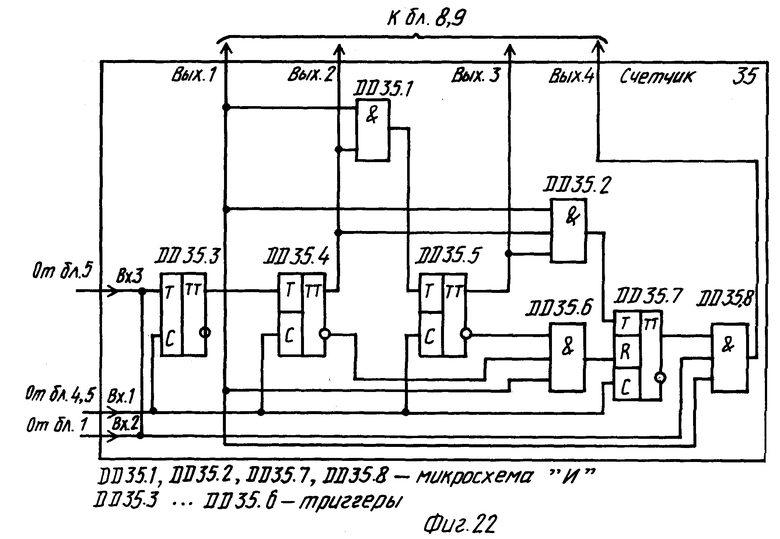

- фиг. 22 - вариант структурной схемы счетчика.

Устройство обучения операторов, показанное на фиг. 1а и 1б, включает блок задания программ обучения 1, панель индикации 2, блок ввода ответных действий оператора 3, блок сравнения 4, блок сравнения семантических элементов 5, первый блок памяти 6, первый блок расширения памяти 7, первый блок группы элементов сравнения 8, дополнительный блок первой группы элементов сравнения 9, первый блок группы регистров числа 10, дополнительный блок первой группы регистров числа 11, первый элемент 12 задержки, второй элемент 13 задержки, первый элемент 14 ИЛИ, сумматор 15, первый дешифратор 16, блок первой группы элементов ИЛИ 17, блок первой группы индикаторов 18, блок второй группы индикаторов 19, дополнительный блок второй группы регистров числа 20, блок второй группы регистров числа 21, дополнительный блок второй группы элементов сравнения 22, блок второй группы элементов сравнения 23, второй блок расширения памяти 24, второй блок памяти 25, пятый элемент ИЛИ 26, шестой элемент ИЛИ 27, третий счетчик 28, седьмой элемент ИЛИ 29, второй дешифратор 30, генератор импульсов 31, второй счетчик 32, пятый элемент задержки 34, первый счетчик 35, четвертый элемент задержки 36, третий элемент задержки 37. Первый и второй входы блока сравнения 4 соединены с соответствующими информационными выходами блока задания программ обучения 1, первые четыре выхода которого соединены с соответствующими входами управления сегментами индикации панели индикации 2. Третий информационный вход первого счетчика 35 соединен в параллель с первыми выходами блока сравнения 4 и блока сравнения семантических элементов 5, первые выходы которых соединены с входами соответствующих элементов задержки 34, 13. Пятый и шестой выходы блока задания программ обучения 1 соединены с первым и вторым входами блока сравнения 4, а седьмой и восьмой информационные выходы блока задания программ обучения 1 соединены с соответствующими входами блока сравнения семантических элементов 5, третий и четвертый входы которого соединены соответственно с пятым и шестым выходами блока ввода ответных действий оператора 3, первый, второй, третий выходы которого соединены соответственно с третьим, четвертым и пятым входами блока сравнения 4. Управляющие выходы первого 12 и пятого 13 элементов задержки соединены с соответствующими входами управления первого 8 и дополнительного 9 блоков первой группы элементов сравнения, соответственно N и K информационных выходов которых соединены с одноименными входами первого 10 и дополнительного 11 блоков первой группы регистров числа. N и K выходов первого 10 и дополнительного 11 блоков первой группы регистров числа соединены в параллель с соответствующими входами первого элемента ИЛИ 14 и сумматора 15, первые N и вторые K выходов которого соединены с соответствующими входами первого дешифратора 16, N выходов которого соединены с одноименными входами блока первой группы элементов ИЛИ 17, управляющие выходы которого подключены к соответствующим входам первой 18 и второй 19 группы индикаторов. Соответственно N и K выходов второго блока памяти 25 и второго блока расширения памяти 24 подключены к одноименным входам основного 23 и дополнительного 22 блоков второй группы элементов сравнения, N и K выходов которых соединены с соответствующими входами основного 21 и дополнительного 20 блоков второй группы регистров числа. Соответственно N и K выходов основного 21 и дополнительного 22 блоков второй группы регистров числа подключены в параллель с одноименными информационными входами сумматора 15 и первого 14 элемента ИЛИ, выход которого соединен с входом третьего элемента задержки 37, выход которого подключен к управляющему входу сумматора 15. N и K входов соответствующих второго 25 блока памяти и второго 24 блока расширения памяти соединены с одноименными входами первого 6 блока памяти и первого 7 блока расширения памяти, а также с одноименными выходами второго дешифратора 30, первый и второй входы которого подключены к соответствующим входам третьего счетчика 28, первый управляющий вход которого соединен с девятым выходом блока задания программ обучения 1 и одновременно с первыми входами шестого 27 элемента ИЛИ и четвертого 36 элемента задержки. Второй вход шестого 27 элемента ИЛИ подключен одновременно к второму входу третьего 28 счетчика и девятому выходу блока задания программ обучения 1, а выход шестого 27 элемента ИЛИ соединен с входом "останов." генератора импульсов 31, первый вход которого подключен к выходу пятого 26 элемента ИЛИ. Выход генератора импульсов 31 соединен с третьим входом второго счетчика 32, выход которого соединен одновременно со всеми входами основного 21 и дополнительного 20 блоков второй группы регистров числа. Первый и второй входы второго счетчика 32 соединены соответственно с первым входом первого счетчика 35 и выходом четвертого 36 элемента задержки. Выход седьмого элемента ИЛИ 29 соединен одновременно с первым входом второго счетчика 32 и со всеми входами основного 23 и дополнительного 22 блоков второй группы элементов сравнения. Десятый и одиннадцатый выходы блока задания программ обучения 1 подключены к соответствующим входам пятого 26 элемента ИЛИ. Второй вход блока задания программ обучения 1 соединен одновременно с выходом первого элемента задержки 12 и первым входом седьмого 29 элемента ИЛИ, второй вход которого подключен к девятому выходу блока задания программ обучения 1.

Блок задания программы обучения 1, представленный на фиг. 2, предназначен для хранения и последовательной выдачи контрольных заданий, совокупность которых определяет программу обучения. Данный блок содержит блок памяти микропрограммы 1.1, представляющий собой перепрограммируемое постоянное запоминающее устройство, в котором последовательно записаны микрокоманды, и регистр адреса микрокоманды 1.2, формирующего адрес следующей микрокоманды. В свою очередь перепрограммируемое постоянное запоминающее устройство 1.1, предназначенное для хранения контрольных заданий и их последовательности предъявления обучаемому, может быть реализовано, как показано на фиг. 3. Регистр адреса микрокоманды 1.2, предназначенный для определения очередного адреса программы обучения, может быть реализован, как показано на фиг. 4. Причем выходы четырехразрядных счетчиков регистра адреса микрокоманды соединены с соответствующими входами перепрограммируемого постоянного запоминающего устройства, информационные выходы которого подключены к управляющим входам панели индикации 2, информационным входам блока сравнения 4 и блока сравнения семантических элементов 5. Информационные выходы N 1-N 8 блока памяти микропрограммы и управляющий выход N 15 регистра адреса микрокоманды являются выходами блока задания программ обучения. Перепрограммируемое постоянное запоминающее устройство может быть реализовано на микросхеме К155КП5, а четырехразрядные двоичные счетчики на микросхеме К500ИЕ136.

Панель индикации 2, представленная на фиг. 5, предназначена для отображения номера задания, считываемого из блока задания программ обучения 1, и содержит дешифратор двоично-десятичного кода в семисегментный код, выходы которого подключены к соответствующим входам дискретной матрицы на светодиодах. Информационные входы N 1-N 4 дешифратора являются входами панели индикации. Дешифратор может быть реализован на микросхеме К176ИЕ2.

Блок ввода ответных действий оператора 3, представленный на фиг 6, содержит ключи B1, B2, используемые обучаемым при проверке его сенсорно-моторных навыков, и клавиатуру для ввода ответов на естественном языке при проверке знаний обучаемого понятий предметной области. Ключи B4 и B5 предназначены соответственно для выдачи управляющего импульса на элемент задержки 13, "сигнализирующего" о выполнении ответного действия на пульте оператора на представленное задание (вых. 3) и завершению выполнения программы обучения и обнуления регистра адреса микрокоманды 1.2 (вых. 4). При этом выходы N 1, 2, 4, 5, 6 подключены к соответствующим блокам сравнения 4 и 5, а вход N3 подключен к управляющему входу второго элемента задержки 13. Клавиатура 3.1 предназначена для ввода команд и ответов на предъявленные задания и представляет собой стандартную клавиатуру персонального компьютера (Альбом принципиальных схем персональных компьютеров. - М.: Машиностроение, 1992. - С. 321). Скан-код нажатой клавиши в последовательном виде вместе с синхропоследовательностью поступает в блок сравнения 5 семантических элементов для анализа правильности введенных ответов и команд (вых. 5, 6).

Блок сравнения 4, предназначенный для сравнения эталонов ответов на контрольные задания по проверке сенсорно-моторных навыков обучаемого с вариантами ответов, вводимых обучаемым, представлен на фиг. 7 и содержит две микросхемы "Исключающее ИЛИ" и одну микросхему "И". Причем информационные входы N 1, 2 соединены с соответствующими выходами блока задания программ обучения 1, а входы N 3, 4 подключены к соответствующим выходам блока ввода ответных действий оператора 3. Реализован блок 4 может быть на микросхемах К555ЛИ1, К555ЛН1.

Блок сравнения семантических элементов 5, предназначенный для сравнения эталонов ответов на контрольные задания, требующие от обучаемого ввода предложений естественного языка с вариантами ответов обучаемого, представлен на фиг. 8. Блок содержит счетчик адреса предложений 5.1, блок хранения образцовых предложений 5.2, блок сравнения предложений 5.3, блок запуска счетчика адреса предложений 5.4 и регистр предложений 5.5. Адрес предложения поступает с выходов N 1-N 9 счетчика адреса предложений, представленного на фиг. 9, на выходы N 3 - N 11 блока хранения образцовых предложений, представленного на фиг. 10, выходы которого подключены к соответствующим входам блока сравнения предложений 5.3, представленного на фиг. 11. Вторая группа входов блока сравнения предложений 5.3 подключена к соответствующим выходам регистра предложений 5.5, представленного на фиг. 13, информационные входы N 3, 4 которого подключены к соответствующим выходам блока ввода ответных действий оператора 3, а управляющие выходы N 1-N 7 регистра предложений 5.5 соединены с соответствующими входами блока запуска счетчика адреса эталонных предложений 5.4, представленного на фиг. 12. Причем информационные входы N 3, 4 регистра предложений 5.5 и N 1, 2 блока хранения образцовых предложений являются входами блока сравнения семантических элементов 5, управляющие выходы N 1, 2 блока сравнения предложений 5.3 являются выходами блока сравнения семантических элементов 5. Схемы данного блока могут быть реализованы на нижеперечисленных микросхемах:

двоичный счетчик - К500ИЕ60

микросхема "НЕ" - К555ЛИ1

микросхема "И-НЕ" - К555ЛЛ1

микросхема "И" - К555ЛН1

RS-триггер - К500ТВ5

микросхема "ИЛИ" - К555ЛН1

восьмиразрядный сдвиговый регистр - К500ИР141

Первый блок памяти 6 предназначен для хранения числа ошибок выполнения сенсорно-моторных операций, соответствующего определенной оценке выбранной оценочной шкалы. Второй блок памяти 25 предназначен для хранения значения времени выполнения сенсорно-моторных операций, соответствующего определенной оценке. Первый блок расширения памяти 7 предназначен для хранения числа ошибок выполнения семантических операций, соответствующего определенной оценке, выбранной оценочной шкалы. Второй блок расширения памяти 24 предназначен для хранения значения времени выполнения семантических операций, соответствующего определенной оценке. На фиг. 14 представлен вариант структурной схемы блока памяти, на основе которой выполняются блоки 6, 7, 24, 25. Схема представлена вариантом четырехразрядного блока памяти с максимальным суммарным числом ошибок, равным 15, и включает четыре регистра памяти, структурная схема которых представлена на фиг. 15. Данные регистры памяти построены с использованием D триггеров и, в частности, могут быть реализованы на микросхемах: К555ТМ7, КМ155ТМ8 и др.

Первый блок группы элементов сравнения 8, представленный на фиг. 16, содержит четыре схемы равнозначности 8.1, представленных на фиг. 17, входы которых соединены с соответствующими выходами блока памяти 6 и первого счетчика 35. Выходы схем сравнения соединены с информационными входами первого блока группы регистров числа 10. Функция равнозначности является дизъюнкцией пар слагаемых, каждое из которых является конъюнкцией прямого и инверсного значений одноименных разрядов сравниваемых чисел:

R = (a1 • b1 + a1 • b1) + ... + (an • bn + an • bn).

Схемы равнозначности могут быть реализованы, например, на микросхемах К531ИР19, К555ИР22.

Первый блок группы регистров числа 10, предназначенный для кратковременного хранения оценки обучаемого за выполнение контрольного задания, определенной по показателю безошибочности, представлен на фиг. 18. На данной схеме представлена реализация однотактного параллельного однофазного регистра с применением CLD-триггеров, число входов которых соответствует числу входов регистра. Запись числа A(a1, a2,...,an) осуществляется при поступлении тактирующего импульса на вход 5 от второго 13 элемента задержки без предварительной установки разрядов в состояние 0. После окончания действия тактирующего импульса вначале откроются вентили обратных связей V0 всех триггеров и зафиксируется новый код в его разрядах, а затем через tне закроются вентили записи числа A. Регистр перейдет в режим хранения информации. Одним из вариантов реализации такого регистра является микросхема К555ИР30.

Сумматор 15, представленный на фиг. 19, состоит из сдвигающих регистров 15.1, 15.2, двоичного сумматора 15.3, триггера ClfD типа 15.4 и выходного регистра числа 15.5. Выходы сдвигающих регистров подключены к соответствующим информационным входам двоичного сумматора 15.3, вход переноса которого соединен с инверсным выходом триггера 15.4, счетный вход которого соединен с соответствующим выходом двоичного счетчика 15.3. Второй информационный выход двоичного счетчика 15.3 соединен с информационным входом выходного регистра числа 15.5, выходы которого соединены с соответствующими входами первого 14 элемента ИЛИ. Данная схема сумматора позволяет проводить сложение чисел, записанных в двух сдвигающих регистрах. Такое суммирование выполняется с помощью одноразрядного сумматора SM, а результат суммы заносится в третий сдвигающий регистр CP3. Данная схема построена по рекомендациям из [2].

Дешифратор 16, представленный на фиг. 20, предназначен для определения итоговой оценки в пятибальной шкале путем линейной дешифрации суммы оценок за безошибочность и своевременность выполнения контрольного задания. Дешифратор состоит из четырех элементов И, выходы которых соединены с соответствующими входами блока 17 первой группы элементов ИЛИ. Дешифратор 16 может быть реализован на микросхемах ИМС К555ЛИ1, ИМС К555ЛЛ1.

Генератор импульсов 31, представленный на фиг. 21, выполнен на четырех элементах TTL-типа, двух конденсаторах и двух резисторах. При этом для стабильной работы генератора необходимо выполнение условия: R1 = R2 = 1,3...1,6 кОм. Данная схема генератора позволяет обеспечить скважность Q = 2, т.е. длительность импульса равна длительности паузы. Вход генератора импульсов "Пуск" соединен с выходом управления пятого 26 элемента ИЛИ, а вход генератора импульсов "Сброс" подключен к выходу шестого 27 элемента ИЛИ. Схему данного генератора можно реализовать на микросхеме ИМС К555ЛН1.

Счетчик 35, представленный на фиг. 22, выполнен на элементах И и RS триггерах. Данный счетчик позволяет вести счет правильно выполненных обучаемым контрольных заданий в десятичной системе счисления и выдает показания в параллельном двоично-десятичном коде, поступающем на блок элементов сравнения 8. Каждый разряд представленного десятичного счетчика имеет Kсч = 10 и для его построения используется четыре двоичных разряда. Реализовать данный двоично-десятичный счетчик можно на микросхеме ИС 500ИЕ137.

Заявленное устройство работает следующим образом. Работа устройства начинается с подачи управляющего сигнала на вход N1 блока задания программ обучения. Из регистра адреса считывается адрес первой микрокоманды в блок памяти микропрограммы, а также через пятый элемент 26 ИЛИ запускается генератор 31, импульсы с выхода которого поступают на первый вход второго счетчика 32. Содержимое первой микрокоманды поступает в регистр микрокоманды блока 1. Микрокоманда включает в себя:

четырехразрядный условный номер задания, который поступает на панель индикации 2 для индикации оператору (вых. 1...4);

двухразрядный код соответствующей правильной комбинации ключей блока 3 ввода ответных действий оператора, который поступает в блок сравнения 4 (вых. 5, 6);

двухразрядный код правильной команды или ответа, который поступает в блок 5 сравнения семантических элементов (вых. 7, 8).

С первых выходов блока 1 формирования программ обучения код органа индикации поступает на панель 2, где требуемый орган изменяет свое состояние. Человек-оператор, воспринимая это изменение состояния органа индикации, выполняет соответствующее воздействие на орган блока 3. Код задействованного органа поступает на первый вход блока 4 сравнения, если выполняется сенсорно-моторная операция или на блок 5 сравнения семантических элементов, если ответ вводится в виде предложения естественного языка. По этой команде содержимое второй микрооперации микрокоманды (код требуемого органа индикации) считывается из регистра микрокоманды по вторым входам в блоки 4 или 5 сравнения, в которых происходит сравнение поступивших кодов.

В заявленном устройстве наибольший интерес представляет блок 5 сравнения семантических элементов, поэтому его работа представлена более подробно. Блок 5 сравнения семантических элементов предназначен для определения правильности поданной команды или ответа на задание. Необходимость анализа семантики введенного сообщения предъявляет дополнительные требования к построению данного блока. В связи с тем, что команда или ответ, имеющие одинаковый смысл, могут быть выражены различными комбинациями слов, возникает необходимость последовательного сравнения введенной фразы с образцовыми предложениями, выражающими один и тот же необходимый смысл. Однако построение команды имеет типовую фразеологию [3]. Это связано с необходимостью точного выражения требования действий. Запрещается использование элементов вежливости. Поэтому совокупность возможных фраз ограничена и может быть учтена в запоминающем устройстве достаточного объема. Блоке 5.2 хранения образцовых предложений представляет собой перепрограммируемое постоянное запоминающее устройство (ППЗУ). В ППЗУ блоками записаны ответы на все задания. Фразы в блоке представляют собой полную совокупность возможных ответов или команд для определенного задания. Каждая фраза представлена в двоичном коде, соответствующем скан-коду клавиатуры. Разрядность данного ППЗУ определяется максимально возможной длиной фразы. Сигналы от блока (вх. 1, 2) интерпретируются как начальный адрес блока образцовых предложений и определяют старшие разряды адреса предложений. Скан-коды ответа или команды, набранные на клавиатуре 3.1 (вх. 3, 4), поступают в блок 5.5 регистра предложений и преобразуются из последовательного в параллельный вид. Блок 5.5 представляет собой сдвиговый регистр. Параллельный код набранного ответа или команды поступает в блок 5.3 сравнения предложений (вых. 8...264). Одновременно из блока 5.5 в блок 5.4 запуска счетчика адреса предложений поступает скан-код последней нажатой клавиши (вх. 1...4). Если данный скан-код соответствует клавише "Ввод", то в блок 5.1 счетчика адреса предложений выдается сигнал (вых. 1), разрешающий работу счетчика. Блок 5.1 представляет собой мультивибратор и двоичный счетчик. Счетчик адреса предложений начинает работу и выдает в блок 5.2 адрес образцового предложения в блоке правильных команд и ответов на данное задание. После окончания перебора адресов образцовых предложений блок 5.1 выдает в блок 5.3 сигнал, что предъявление образцовых предложений закончено (вых. 9). Параллельные коды образцовых предложений последовательно выдаются в блок 5.3 для сравнения (вых. 11...267). Блок 5.3 сравнивает введенное предложение с образцовыми. В случае их совпадения блок вырабатывает и подает в блок 35 сигнал правильности ответа или команды (вых. 1, 2). В случае отсутствия совпадения набранного ответа с одним из образцовых предложений и поступлении от блока 5.1 сигнала окончания перебора адресов (вх. 925) блок 5.3 вырабатывает для блока 34 сигнал неправильного ответа (вых. 2), счетчик.

Если совпадение кодов не происходит, то фиксируется ошибка оператора, и сигнал с первого выхода блока 4 (или соответственно 5) поступает на первый вход первого счетчика 35. Каждый раз при наличии ошибки содержимое счетчика увеличивается на единицу. При совпадении кодов в блоке 4 (или 5) сигнал со вторых выходов указанных блоков поступает на входы второго 13 или пятого 35 элемента задержки соответственно.

Управляющий сигнал с выхода шестого элемента ИЛИ 27 поступает на второй вход генератора 32 для его останова и на первый вход третьего счетчика 28, увеличивая тем самым его содержимое на единицу, которая считывается во второй дешифратор 30. По признаку первой элементарной операции с первого 6 и второго 24 блоков памяти с первых четырех ячеек количество ошибок и нормативное время считываются соответственно по вторым входам блоков сравнения первой 8 и второй 22 группы.

Сигнал с выхода второго элемента 13 задержки поступает на информационные входы первого блока группы элементов сравнения, где происходит сравнение числа допущенных оператором ошибок с числом, которое было считано с первой ячейки первого 6 блока памяти и соответствует выставлению оценки "отлично".

Если совпадение происходит, то сигнал с первого выхода первой группы элементов сравнения 8 поступает на управляющий вход 10 первой группы регистров числа, и код отличной оценки переписывается в сумматор 17.

Если совпадение не происходит, то сигнал с выхода первого блока элементов сравнения 8 поступает на управляющий третий вход второго блока первой группы 9, где число ошибок, допущенных оператором, сравнивается с числом, которое было считано с второй ячейки первого 6 блока памяти и соответствует выставлению хорошей оценки и т.д. до четвертых блоков первой группы 8 элементов сравнения и регистров 10 при неудовлетворительной оценке действий обучаемого.

Сигнал с выхода четвертого элемента 36 задержки поступает на второй вход второго счетчика 32. По этой команде его содержимое переписывается по первым входам в блоки сравнения 27 второй группы.

Сигнал с выхода пятого 34 элемента задержки поступает на управляющий третий вход блока 22 второй группы элементов сравнения. Если при сравнении коды требуемого (временной норматив для отличной оценки) и затраченного времени совпадают, то сигнал с первого блока 27 сравнения второй группы поступает на первый регистр 25 второй группы, и с его выхода код отличной оценки (по времени) поступает на соответствующий вход сумматора 17.

Если совпадение кодов требуемого и затраченного времени в первом блоке 24 сравнения второй группы не происходит, то управляющий сигнал с последнего поступает на третий вход второго блока 24 сравнения второй группы, где сравнивается код требуемого времени, соответствующий хорошей оценке, и затраченного оператором времени и т.д. до четвертого блока 24 сравнения и регистра 25 вторых групп при неудовлетворительной оценке действий обучаемого. В сумматоре 17 происходит сложение кодов оценок за безошибочность и своевременность действий обучаемого. Если сумма равняется "10", то сигнал появляется на соответствующем выходе первого дешифратора 16 и поступает на индикаторы 18, засвечивая его, что соответствует получению оператором комплексной отличной оценки. Если сумма баллов составляет "8" или "9", то оператору выставляется хорошая оценка, если "6" и "7", - то удовлетворительная, а если меньше "6", - неудовлетворительная.

Сигнал с выхода первого элемента 12 задержки поступает на второй вход блока 1 задания программ обучения и на второй вход седьмого элемента ИЛИ 29, с выхода которого управляющий сигнал поступает на третьи входы первого 9 и второго 32 счетчиков и на четвертые входы блоков 8 и 22 сравнения первой и второй групп соответственно для их обучения.

При поступлении сигнала на второй вход блока 1 задания программ обучения производятся сдвиг к следующей ячейке и считывание адреса очередной микрокоманды из блока памяти микропрограммы, и устройство функционирует аналогично описанному выше порядку, причем, когда содержимое третьего счетчика 28 увеличивается на единицу, то с первого 6 и второго 24 блоков памяти считываются количество ошибок и нормативное время с пятых по восьмую ячейку.

По окончании работы сигнал с последней ячейки регистра адреса микрокоманды блока 1 поступает на вход элемента ИЛИ 29 для обнуления первого 9, второго 32 счетчиков и блоков 11 и 24 сравнения первой и второй групп соответственно, на входы счетчика 28 и элемента ИЛИ 27 для обнуления счетчика 28 и останова генератора 31 соответственно.

Предлагаемое устройство расширяет дидактические возможности за счет пооперационной комплексной оценки обучаемого по показателям безошибочности и своевременности каждого выполняемого действия, что особенно важно на заключительных тренировках для выработки навыков исполнительской основы деятельности оператора АСУ, а также расширяет интеллектуальные возможности автоматизированных систем обучения за счет введения в устройство блока анализа семантических элементов.

При оценке эффективности заявленного технического решения одним из определяющих является требование по достоверности оценки ответов обучаемых, вводимых в виде предложений естественного языка. Для повышения достоверности оценки в предлагаемом устройстве реализован структурный метод распознавания семантических элементов. Особенность данного метода заключается в том, что априорными описаниями классов являются структурные описания - формальные конструкции, при получении которых последовательно проводится принцип учета иерархичности структуры объекта и учета отношений, существующих между отдельными элементами этой иерархии, в пределах одних и тех же уровней и между ними.

В предлагаемом варианте устройство реализовано на ИМС ТТЛ. Справочные данные на примененные ИМС, узлы и схемы взяты из следующих источников информации.

Источники информации

1. В. Л. Шило. Популярные цифровые микросхемы. Справочник. - 2-е изд., исправленное. - М.: Радио и связь, 1989, с. 352.

2. Б. В. Шевкопляс. Микропроцессорные структуры. Инженерные решения. Справочник. - 2-е изд., перераб. и доп. - М.: Радио и связь, 1990 с. 512.

3. Правила и фразеология радиообмена при выполнении полетов и управлении воздушным движением. Министерство гражданской авиации. - М.: Воздушный транспорт, 1987, с. 86.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011229C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011227C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011228C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011226C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 2005 |

|

RU2281560C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 2005 |

|

RU2281561C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

Устройство содержит блок задания программ обучения, панель индикации, блок ввода ответных действий оператора, блок сравнения, блок сравнения семантических элементов. Первый блок памяти и первый блок расширения памяти через первый блок группы элементов сравнения и дополнительный блок первой группы элементов сравнения подключены к первому блоку группы регистров числа и дополнительному блоку первой группы регистров числа. Устройство также содержит элементы задержки, элементы ИЛИ, сумматор, дешифраторы, блоки группы элементов ИЛИ, блоки группы индикаторов. Имеются дополнительный блок второй группы регистров числа, блоки второй группы элементов сравнения, блоки расширения памяти, второй блок памяти, счетчики, генератор импульсов. Заявленное устройство позволяет за счет введения дополнительной возможности обработки семантических элементов оценивать креативные свойства обучаемых. 22 ил.

Устройство обучения операторов, содержащее первый блок памяти, N выходов которого подключены к соответствующим N входам первого блока группы элементов сравнения, где N = 3, 4, ..., N выходов которого подключены к соответствующим N входам первого блока группы регистров числа, N выходов первого блока регистров числа подключены к первым группам из N входов в каждой группе сумматора и первого элемента ИЛИ, N выходов сумматора подключены к соответствующим N входам первого дешифратора, N выходов которого подключены к N входам блока первой группы элементов ИЛИ, N выходов которого подключены к N входам блока первой группы индикаторов, блок второй группы регистров числа, N выходов которого подключены ко вторым группам входов по N входов в каждой первого элемента ИЛИ и сумматора, а N входов блока второй группы регистров числа подключены к соответствующим N выходам блока второй группы элементов сравнения, N входов которого подключены к N выходам второго блока памяти, N входов которого подключены к соответствующим N входам первого блока памяти и одновременно к N выходам второго дешифратора, первый и второй входы которого подключены к соответствующим выходам третьего счетчика, а его первый и второй входы третьего счетчика подключены соответственно к первому и второму входам шестого элемента ИЛИ и одновременно к второму входу первого счетчика и второму входу седьмого элемента ИЛИ, выход которого подключен одновременно к первым входам первого и второго счетчиков и к N выходам второго блока памяти, второй вход второго счетчика подключен к выходу четвертого элемента задержки, вход которого подключен к первым входам шестого элемента ИЛИ, третьего счетчика, второму входу первого счетчика и входу первого элемента задержки, выход первого элемента задержки подключен в параллель к первому входу блока задания программы обучения и первому входу седьмого элемента ИЛИ, второй вход которого подключен к первому выходу блока задания программы обучения, первая и вторая группы по N входам в каждой блока задания программы обучения подключены соответственно к N входам панели индикации и блока сравнения, первый и второй выходы блока сравнения подключены соответственно к третьему входу первого счетчика и входу первого элемента задержки, а его первый и второй входы подключены к первому и второму выходам блока ввода ответных действий оператора, второй и третий выходы блока задания программ обучения подключены соответственно к первому и второму входам пятого элемента ИЛИ, выход которого подключен к первому входу генератора импульсов, второй вход которого подключен к выходу шестого элемента ИЛИ, а выход генератора импульсов подключен к третьему входу второго счетчика, выход которого подключен к каждому из N выходов блока второй группы элементов сравнения, выход первого элемента ИЛИ подключен к входу третьего элемента задержки, выход которого связан с дополнительным входом сумматора, причем выход первого счетчика подключен к каждому из N выходов первого блока группы элементов сравнения, а выход первого элемента задержки подключен к дополнительному входу первого блока группы элементов сравнения, отличающееся тем, что введены первый блок расширения памяти, дополнительный блок первой группы элементов сравнения, дополнительный блок первой группы регистров числа, блока второй группы индикаторов, дополнительный блок второй группы регистров числа, дополнительный блок второй группы элементов сравнения, второй блок расширения памяти, пятый элемент задержки, блок сравнения семантических элементов, причем первая и вторая группы входов, по К входов в каждой, блока сравнения семантических элементов подключены соответственно к дополнительным К выходам блока задания программ обучения, где К ≥ 3, и дополнительным К выходам блока ввода ответных действий оператора, где К < 3, а первый и второй выходы блока сравнения семантических элементов подключены соответственно к третьему входу первого счетчика и входу пятого элемента задержки, выход которого подключен к управляющему входу дополнительного блока первой группы элементов сравнения, К входов которого подключены к соответствующим К выходам первого блока расширения памяти, а К входов первого блока расширения памяти подключены к первым К входам первого блока памяти, К выходов дополнительного блока первой группы элементов сравнения подключены к соответствующим К входам дополнительного блока первой группы регистров числа и, кроме того, каждый из К выходов дополнительного блока первой группы элементов сравнения подключен к выходу первого счетчика, К выходов дополнительного блока первой группы регистров числа подключены в параллель к первой группе из К входов первого элемента ИЛИ и первой группе из К входов сумматора, а вторые группы из К входов первого элемента ИЛИ сумматора подключены в параллель к соответствующим К входам дополнительного блока второй группы регистров числа, К входов которого подключены к соответствующим К выходам дополнительного блока второй группы элементов сравнения и каждый из К входов дополнительного блока второй группы регистров числа подключен к выходу второго счетчика, К входов дополнительного блока второй группы элементов сравнения подключены к соответствующим К выходам второго блока расширения памяти, каждый из К входов дополнительного блока второй группы элементов сравнения подключен к первому входу второго счетчика, а К входов второго блока расширения памяти подключены к первым К входам второго блока памяти, причем К дополнительных выходов сумматора подключены к соответствующим дополнительным К входам первого дешифратора, к дополнительным выходам которого подключены К дополнительных входов блока первой группы элементов ИЛИ и дополнительные выходы которого подключены к соответствующим К входам блока второй группы индикаторов, а четвертый вход блока задания программы обучения является запускающим входом устройства.

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 1991 |

|

RU2011228C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОФЕССИОНАЛЬНЫХ НАВЫКОВ ОПЕРАТОРА | 1991 |

|

RU2024067C1 |

| ТРЕНАЖЕР ОПЕРАТОРОВ СИСТЕМ УПРАВЛЕНИЯ | 1991 |

|

RU2051420C1 |

| Устройство для обучения операторов | 1990 |

|

SU1709375A1 |

| JP 06052249 A, 25.02.94 | |||

| JP 03225389 A, 04.10.91 | |||

| WO 9318958 A1, 16.09.93. | |||

Авторы

Даты

1999-04-27—Публикация

1997-01-23—Подача