Изобретение относится к системам цифроаналогового преобразования и может быть использовано в функциональных генераторах, применяемых в испытательной технике для формирования различных законов нагружения, имеющих как периодическую, так и псевдопериодическую структуру сигналов.

Известна схема сглаживания сигнала цифроаналогового преобразователя, содержащая цифроаналоговый преобразователь, два устройства выборки-хранения, два разностных усилителя, суммирующий усилитель, пять электронных ключей, интегрирующую RC-цепь и элементы управляющей ложки [1] .

Устройство, выполненное на основе положительного решения на заявку N 4710364/24, позволяет устранить эти недостатки.

Известно устройство сглаживания сигнала цифроаналогового преобразователя, содержащее цифроаналоговый преобразователь, D-триггер, блок интегрирования, первый и второй ключи, первое и второе устройство выборки-хранения, при этом блок интегрирования выполнен в виде операционного усилителя, первого и второго резисторов и конденсатора [2] .

Однако, известные устройства имеют ряд недостатков, устраненные в предлагаемом устройстве.

Цель изобретения - повышение точности формы выходного сигнала.

Для достижения цели предлагается запись в цифроаналоговый преобразователь задержать на один такт преобразования, используя для этого двойную буферизацию данных, причем запись данных в первый буферный регистр производится сигналом вычислительного устройства, а перезапись в буферный регистр цифроаналогового преобразователя - сигналом таймера, формирующим одновременно временной интервал интерполяции и выставляющий сигнал "готовность" для записи данных во входной буфер.

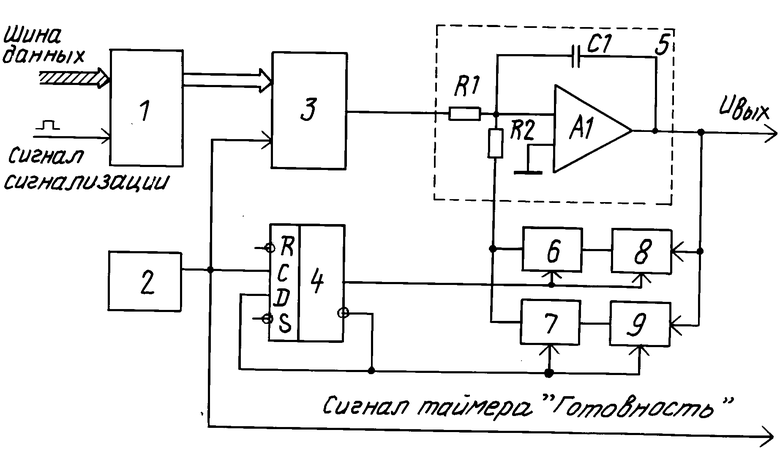

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит буферный регистр 1, таймер 2, цифроаналоговый преобразователь 3, D-триггер 4, блок 5 интегрирования, электронные ключи 6 и 7 и устройства 8 и 9 выборки-хранения.

Буферный регистр 1 предназначен для временного хранения данных и может быть выполнен на интегральных микросхемах регистров, входящих в состав серий микросхем К561, К155, К555, К580 и т. д.

Таймер 2 в зависимости от требований к точностным характеристикам выходного сигнала, может быть выполнен либо на основе генератора с кварцевой стабилизацией частоты, либо на микросхеме КР1006ВИ1.

Цифроаналоговый преобразователь предназначен для преобразования цифровых данных в аналоговый сигнал и может быть выполнен как на дискретных элементах, так и на базе серийно выпускаемых интегральных микросхем серий КР572, К594, КР 1108 и т. д.

D-триггер 4 предназначен для управления режимом работы устройств выборки-хранения, а также для их поочередного подключения посредством электронных ключей к входу блока интегрирования и может быть реализован на любой из микросхем К 155ТМ2, К555ТМ2, К561ТМ2 и т. д.

Блок 5 интегрирования может быть выполнен на базе операционного усилителя, имеющего малый входной ток, температурный и временной дрейфы, охваченного емкостной отрицательной обратной связью.

Электронные ключи 6 и 7 предназначены для поочередного подключения выходов устройств 8 и 9 выборки-хранения к входу блока 5 и могут быть реализованы на микросхемах серии КР590, КР 190 и т. д.

Устройства 8 и 9 выборки-хранения предназначены для временного хранения в течение времени квантования Δ t напряжения с выхода блока интегрирования и могут быть выполнены на базе серийно выпускаемых микросхем КР100СК2, КР11, , СК3.

Предлагаемое устройство работает следующим образом.

По переднему фронту импульса, формируемого таймером 2, происходит перезапись данных из буферного регистра 1 в регистр данных цифроаналогового преобразователя 3, а D-триггер 4 изменяет свое состояние (например на его прямом выходе формируется уровень лог. 0). При этом первое устройство 8 выборки-хранения переводится в режим хранения информации, первый ключ 6 замыкается, второй ключ 7 размыкается, а второе устройство 9 выборки-хранения переводится в режим слежения за выходным сигналом блока 5 интегрирования. Сигнал с выхода цифроаналогового преобразователя 3, соответствующий новому значению преобразуемого кода, поступает на первый вход блока 5 интегрирования, на второй вход которого поступает сигнал, соответствующий предыдущему значению преобразуемого кода. Таким образом, блок 5 интегрирования формирует на своем выходе и выходе всего устройства в целом сигнал, пропорциональный разности напряжений, соответствующих текущему и предыдущему значениям преобразуемого кода. Этот разностный сигнал интерполируется и на выходе устройства за интервал квантования Δt формируется линейно-изменяющееся напряжение.

Постоянная времени блока 5 интегрирования, выполненного на основе операционного усилителя с конденсатором в цепи обратной связи, выбирается такой, что за интервал квантования напряжение на его выходе линейно изменяется на величину, пропорциональную разности входных напряжений. Эта постоянная времени обеспечивается соответствующим выбором входных сопротивлений. Напряжение с выхода блока 5 через поочередно работающие устройства 8 и 9 выборки-хранения и электронные ключи 6 и 7 подаются на второй его вход. Таким образом, замыкается отрицательная обратная связь, действующая с запаздыванием на величину квантования цифроаналогового преобразователя.

Сигнал таймера 2, кроме синхронизации работы всего устройства, уведомляет сигналом "Готовность" вычислительное устройство о начале отсчета нового интервала интерполяции. Вычислительное устройство реагирует на этот сигнал пересылкой в буферный регистр 1 новых данных и сбросом сигнала "Готовность". Эти данные переписываются в буферный регистр цифроаналогового преобразователя 3 только про истечении данного интервала интерполяции. Таким образом, данные на формирование выходного сигнала устройства попадают как бы с запаздыванием на один такт интерполяции и временные задержки формирования новых данных, если они не превышают интервал интерполяции, не искажают выходной сигнал.

Данное устройство предполагается использовать в качестве задающего устройства в системе управления и измерения электрогидравлических испытательных систем, в частности в универсальной испытательной машине ИК 6038-500.3.

(56) 1. Патент США N 4573033, кл. 340/347 ДА, 1983.

2. Авторское свидетельство СССР N 1695506, кл. Н 03 М 1/68, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

| Программный регулятор | 1989 |

|

SU1654796A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| СЕЙСМИЧЕСКИЙ ВИБРАТОР | 2001 |

|

RU2204846C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| Устройство сглаживания сигнала цифроаналогового преобразователя | 1989 |

|

SU1695506A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах преобразования цифровой информации в аналоговую. Цель изобретения - повышение точности формы выходного сигнала. Это достигается тем, что запись в цифроаналоговый преобразователь предлагается задержать на один такт преобразования, используя для этого двойную буферизацию данных, причем запись данных в первый буферный регистр производится сигналом от внешнего вычислительного устройства, а перезапись в буферный регистр цифроаналогового преобразователя - сигналом таймера, формирующим односременно временной интервал интерполяции и выступающий сигнал "Готовность" для записи следующих данных во входной буфер. 1 ил.

УСТРОЙСТВО СГЛАЖИВАНИЯ СИГНАЛА ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ, содержащее цифроаналоговый преобразователь, информационный выход которого подключен к первому входу блока интегрирования, D-триггер, вход синхронизации которого объединен с входом синхронизации цифроаналогового преобразователя, информационный вход соединен с его инверсным выходом, а инверсный и прямой выходы соединены с управляющими входами соответственно первого и второго устройств выборки-хранения и первого и второго электронных ключей, информационные выходы которых объединены и соединены с вторым входом блока интегрирования, выход которого является выходной шиной и соединен с информационными входами первого и второго устройств выборки-хранения, выходы которых подключены к информационным входам первого и второго ключей соответственно, отличающееся тем, что, с целью повышения точности формы выходного сигнала, в него дополнительно введены таймер и буферный регистр, информационные входы и вход синхронизации которого являются соответственно входной шиной преобразуемого кода и шиной стробирования данных, информационные выходы подключены к информационным входам цифроаналогового преобразователя, вход синхронизации которого соединен с выходом таймера, который является шиной "Готовность".

Авторы

Даты

1994-04-15—Публикация

1991-07-17—Подача