ю

00

ы а

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления при моделировании сложных ди- намических процессов с помощью цифровых вычислительных машин в реаяь- ном масштабе времени„

Известен функциональный преобразователь многих переменных, содержащий блок синхронизации, группу блоков аналого-цифрового преобразования, цифровые выходы которых под- ключены к запоминающему устройству, а аналоговые выходы сигнала рассогласования - к входам блока формирования интерполирующих функций, регистры, умножающие цифроаналоговые преобразователи и суммирующий усилитель.

Недостатками известного устройства являются ограниченные функциональные возможности из-за отсутствия возможности оперативной перестройки на другое количество переменных, на новые функции без изменения структуры преобразователя, а также недостаточная точность преобразования, обусловленная аналоговой интерполяцией заданной функции из-за увелике- ния инструментальной погрешности воспроизведения функции

Наиболее близким к изобретению является цифровой функциональный преобразователь, содержащий группу реверсивных счетчиков, блоки управления, памяти, регистры, коммутаторы, сумматор, умножитель и преобразователи прямого кода в дополнительный,, Указанный преобразователь обеспечивает необходимую точность преобразования за счет использования при вычислениях цифровой интерполяции заданной функции„

К числу недостатков известного преобразователя относится необходимость представления аналоговых переманных в цифровой форме, что требует дополнительных аппаратных затрат для реализации поставленной задачи, а также ограниченные функциональные возможности из-за отсутствия возможности оперативной перестройки на другое количество переменных, на новые функции без изменения структуры преобразователя„

Целью изобретения является расширение области применения функционального преобразователя многих переменных путем оперативного изменени

S

количества преобразуемых переменных и преобразования переменных, представленных в аналоговой форме,,

Поставленная цель достигается тем, что в функциональный преобразователь многих переменных, содержащий два блока коммутации, первый (БК1) из которых подключен управляющим входом к первому выходу блока синхронизации (БС), а второй блок коммутации (БК2) соединен информационными входами с выходами регистров группы, блок памяти ординат (БПО), подключенный входом

5 выборки к второму выходу БС, и группу реверсивных счетчиков, суммирующие и вычитающие входы которых соединены с выходами первой и второй групп БС соответственно, введены блок вычисления сплайнов (БВС) , блок микропрограммного управления, выходной цифро-аналоговый преобразователь и группа аналого-цифровых преобразователей, подключенных аналоговыми входами к входам соответствующих переменных преобразователя, выходами старших разрядов - к информационным входам соответствующих реверсивных счетчиков группы, выходами младших разрядов - к информационным входам соответствующих регистров группы, а выходами окончания преобразования - к соответствующим входам первой группы блока синхронизации и входам записи соответствующих реверсивных счетчиков группы и регистров группы, причем выходы реверсивных счетчиков группы соединены с информационными входами первой группы первого блока коммутации, подключенного информационными входами второй группы к входу задания адреса ординат преобразователя, а выходом - к адресному входу блеска памяти ординат, соединенного информационным входом с вхо5 дом задания значений ординат преобразователя, входом управления записью и считыванием - с первым выходом блока синхронизации, а выходом - с внутренней шиной данных преобразователя, причем блок микропрограмнного управления подключен входами адреса ветвления к выходам третьей группы блока синхронизации, первой группой выходов - к второй группе входов блока синхронизации, второй группой выходов - к управляющим входам второго блока коммутации, третьей группой выходов - к входам микропрограммного

0

5

0

O

5

управления блока вычисления сплайнов, а входом тактовых импульсов - к третьему выходу блока синхронизации и входу тактовых импульсов блока вычисления сплайнов, информационные входы, выходы которого, выход второ- го блока коммутации и информационный вход выходного цифроаналогового преобразователя соединены с внутренней шиной данных преобразователя, причем бло синхронизации подключен четвертым внходом к входу записи выходного цифроаналогового преобразователя, пятым выходом - к входам тактовых импульсов аналого-цифровых преобразователей группы, входы запуска которых соединены с выходами четвертой группы блока синхронизации, подключенного входами третьей группы к входу задания количества преобразуемых переменных преобразователя, а первым и вторым входами - к входам управления записью и сбросом преобразователя,, Блок микропрограммного управления (БМУ), выходной цифро- аналоговый преобразователь (ЦАП) и группа аналого-цифровых преобразователей (АЦП), подключенных аналоговыми входами к входам соответствующих переменных преобразователя, выходами старших разрядов - к информационным входам соответствующих реверсивных счетчиков группы, выходами младших разрядов - к информационным входам соответствующих регистров группы, а выходами окончания преобразования - к соответствующим входам первой группы БС и входам записи соответствующи реверсивных счетчиков группы и регистров группы, причем выходы реверсивных счетчиков группы соединены с информационными входами первой группы БК1, подключенного информационными входами второй группы к входу задания адреса ординат преобразователя, а выходом - к адресному входу БПО, соединенного информационным входом с входом задания значений ординат преобразователя, входом управления записью и считыванием - с первым выходом БС, а выходом - с внутренней шиной данных преобразователя, причем БМУ подключен входами адреса ветвления к выходам третьей группы БС, первой группой выходов - к второй группе входов БС, второй группой выходов - к второй группе входов БС, второй группой выходов 836

к управляющим входам БК2, третьей группой выходов - к входам микропрограммного управления ВВС, а входом тактовых импульсов - к третьему выходу БС и входу тактовых импульсов ВВС, информационные входы - выходы которого,выход БК2 и информационный вход ЦАП соединены с внутренней шиJQ ной данных преобразователя, причем БС подключен четвертым выходом к входу записи ЦАП, пятый выходом - к входам тактовых импульсов АЦП, входы запуска которых соединены с выходами

15 четвертой группы БС, подключенного входами третьей группы к входу задания количества преобразуемых переменных преобразователя, а первым и вторым входами - к входам управления

20 записью и сбросом преобразователя

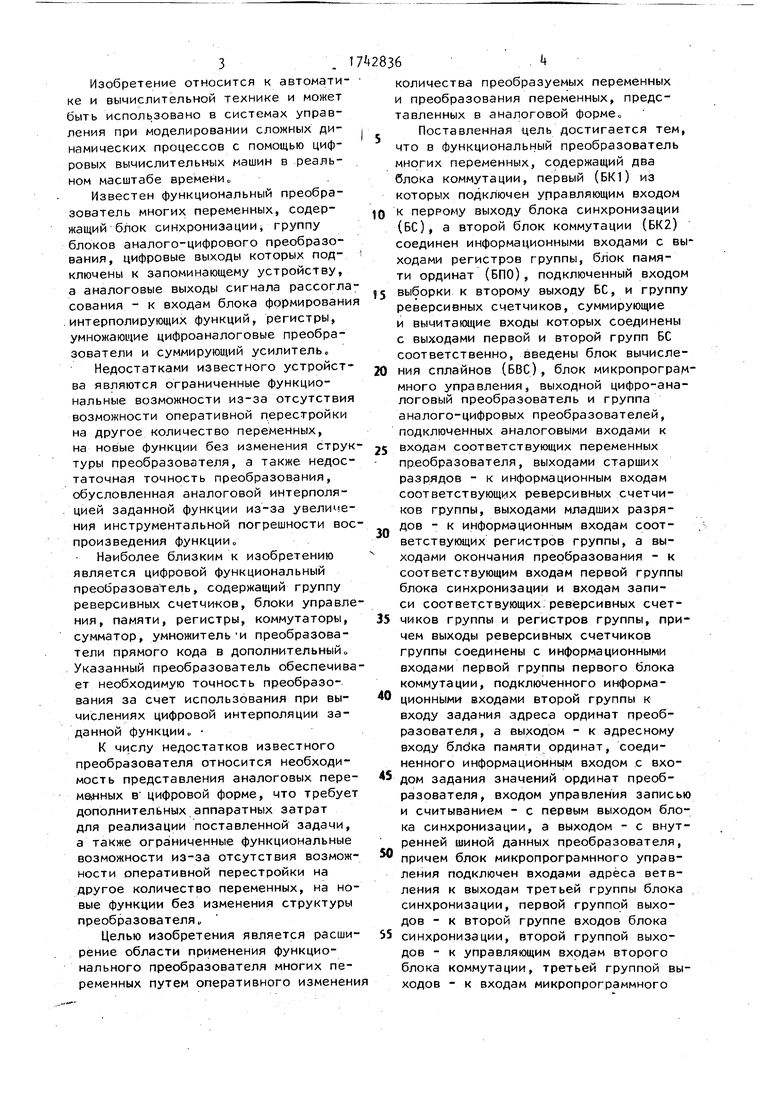

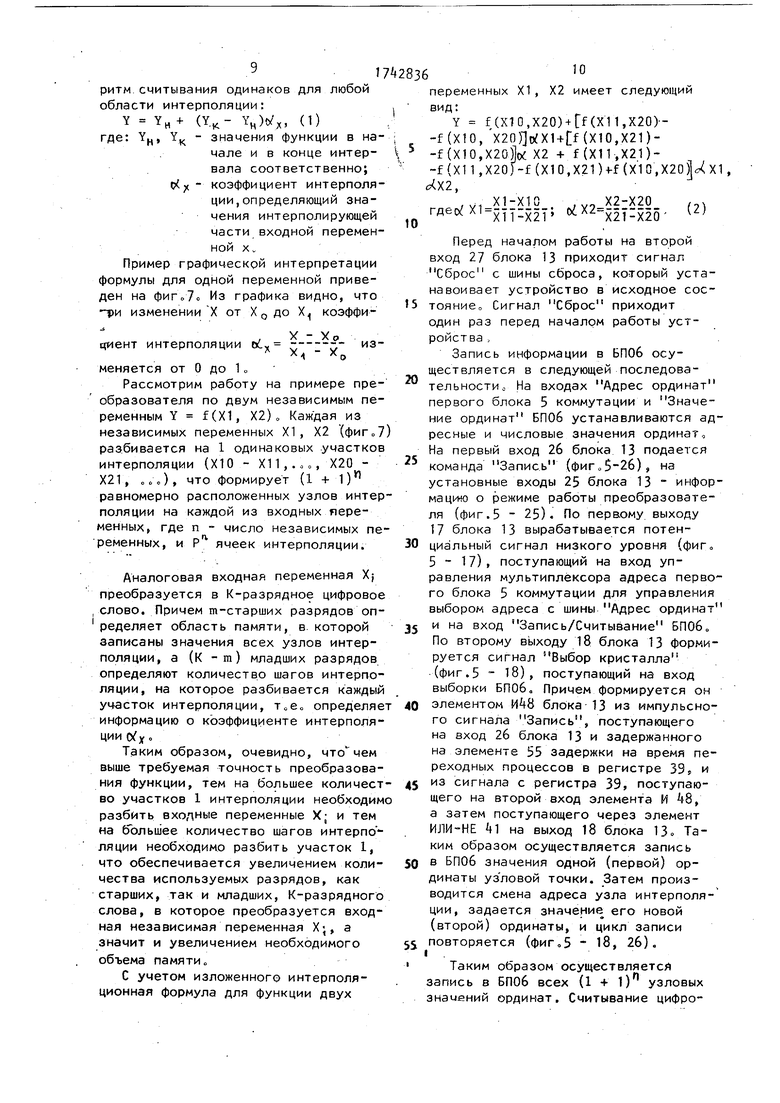

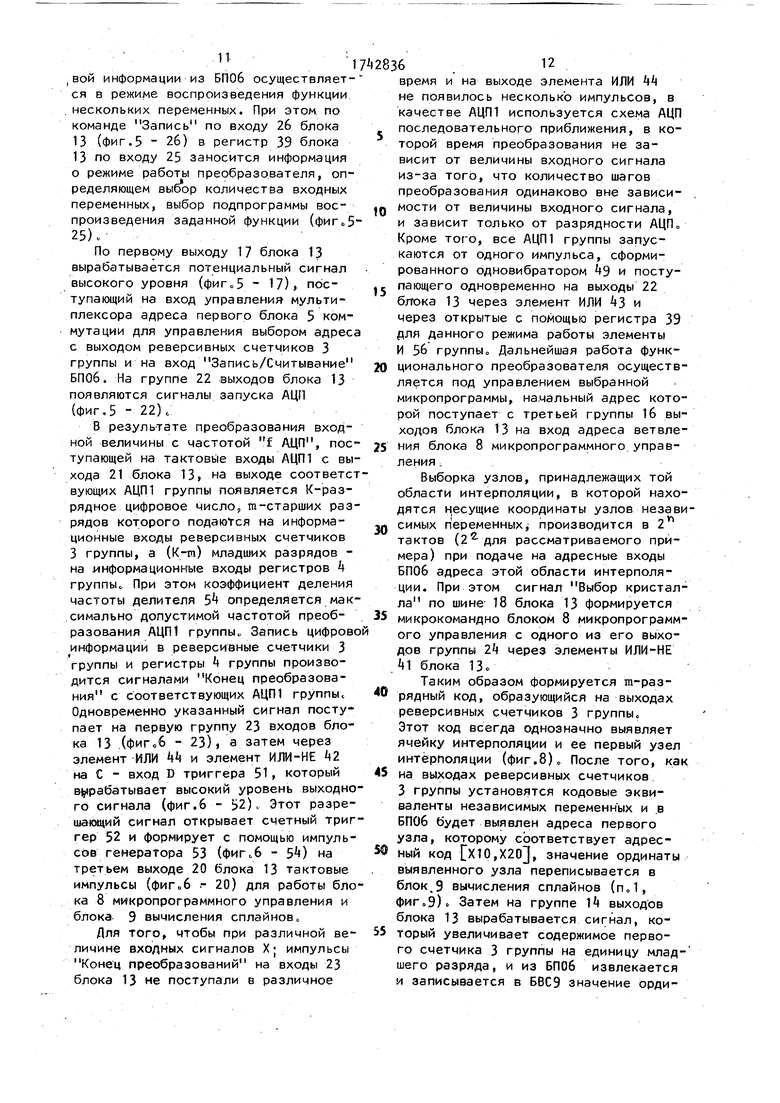

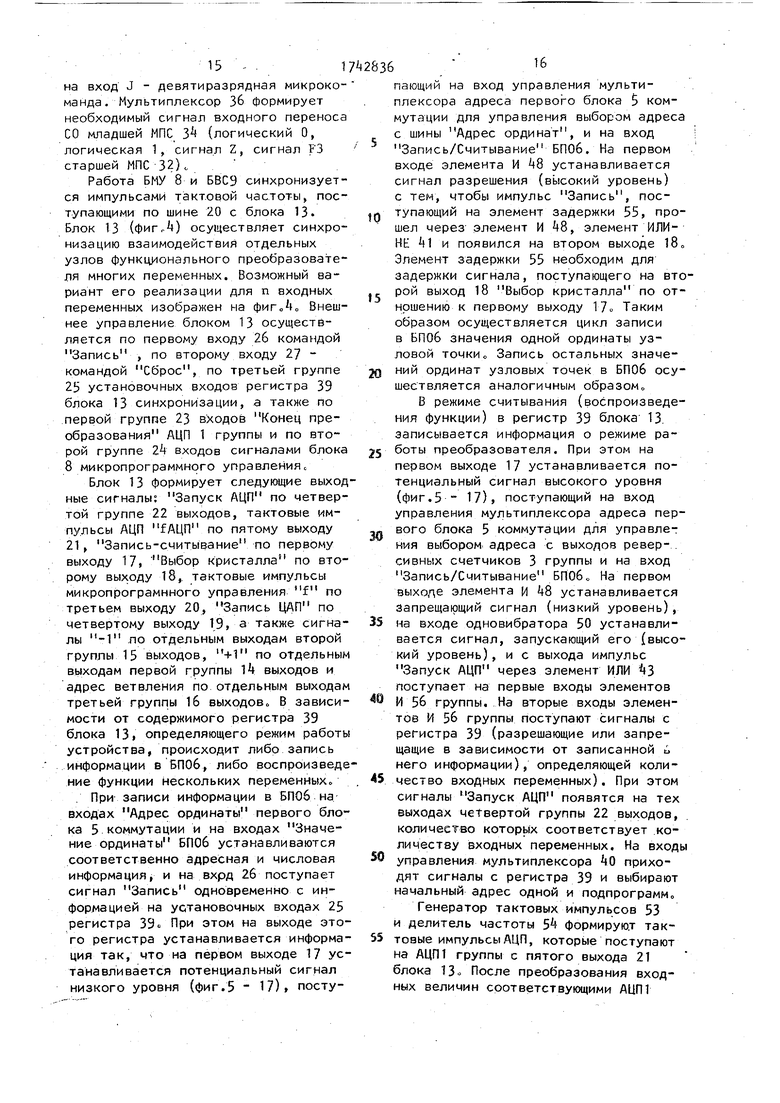

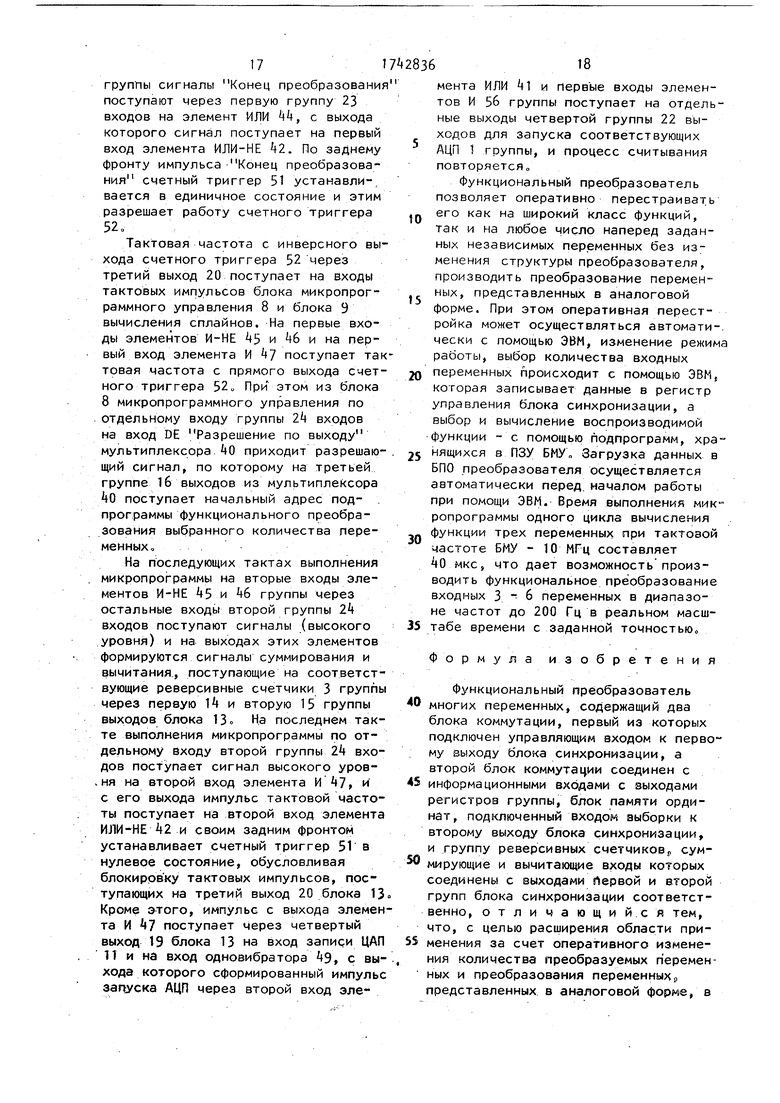

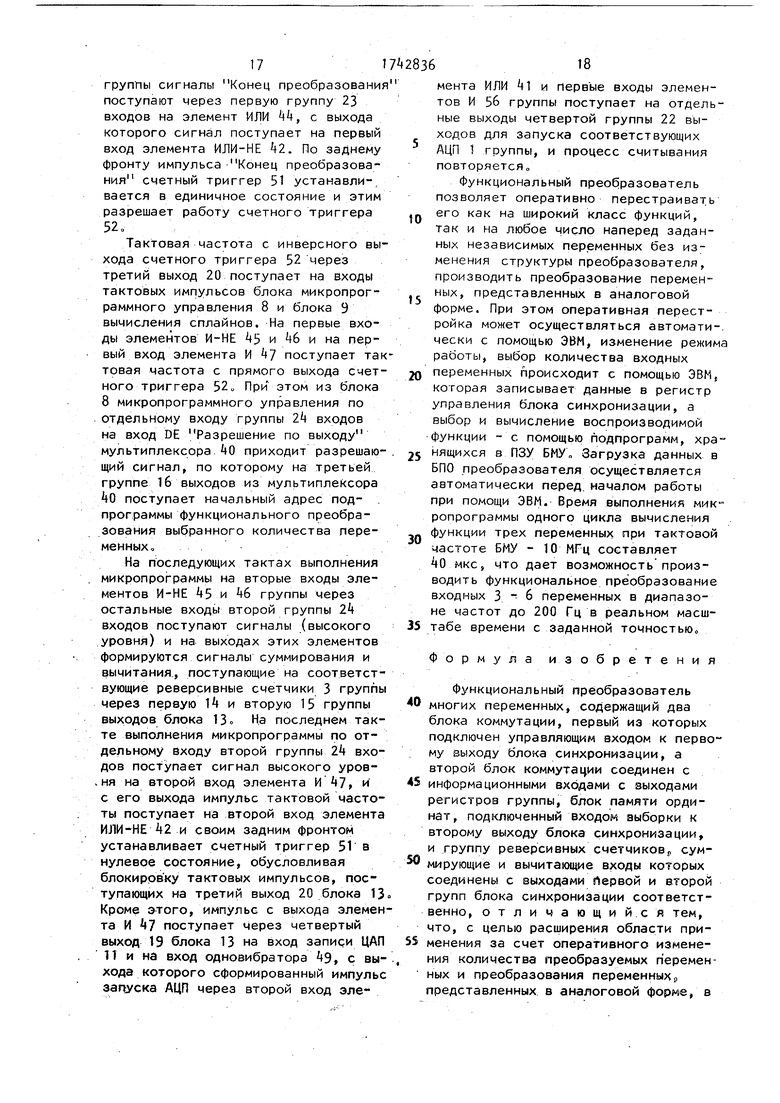

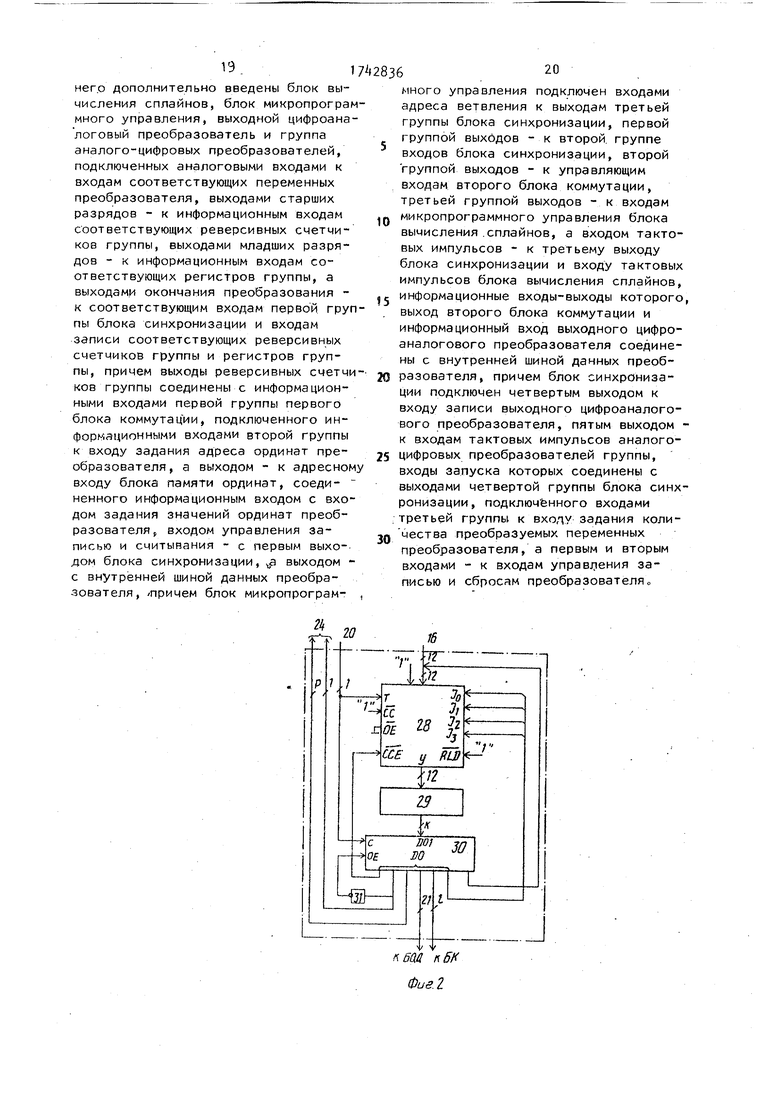

На фиг.,1 приведена функциональная схема устройства; на фиг.2 - функциональная схема БМУ; на - i функциональная схема-ВВС; на 25 функциональная схема БС для п переменных; на фиг,5 и 6 - временные диаграммы работы БС; на фиг„7 - график интерполяционной формулы для одной переменной; на фиг„8 - график,

Зо«характеризующий алгоритм считывания узловых значений; на фиг.9 - алгоритм вычисления функции двух переменных в ВВС

Функциональный преобразователь многих переменных (фиг.1) содержит группу АЦП1, подключенных аналоговыми входами к шинам 2 ввода соответствующих переменных, цифровыми выходами старших разрядов - к информационным входам реверсивных счетчиков 3 группы, а цифровыми выходами младших разрядов - к информационным входам регистров k группы. Первый блок 5 коммутации соединен информационными входами с выходом реверсивных счетчиков 3 группы, а выходами - с адресными входами БПО 6„ Второй блок коммутации 7 информационными входами соединен с выходами регистров А

группы, а входами управления - с

второй группой выходов блока 8 микропрограммного управления, который соединен третьей группой выходов с блоком 9 вычисления сплайнов. Внут- ренняя шина 10 данных соединяет соответственно информационные выходы БПО 6, информационные выходы второгс блока 7 коммутации, входы - выходы

блока 9 вычисления сплайнов и цифро- вые входы ЦЛП 11, аналоговый выход которого соединен с выходной шиной 12 устройства. Блок 13 синхронизации первой группой 14, второй группой 15, третьей группой 16, четвертой группой 22 выходов подключен к суммирующим, вычитающим входам реверсивных счетчиков 3, к входам адреса ветвления блока 8 микропрограммного управления и входам запуска АЦП 1 группы соответственно, первым выходом 17 к входу управления первого блока коммутации 5 и к входу управления записью считывания БПО 6, вторым 18, четвертым 19, пятым 21 выходами - к входу выборки БПО 6, к входу записи ЦАП 11 и входам тактовых импульсов АЦП 1 группы соответственно, третьим выходом 20 - к входам тактовых импульсов блока 8 микропрограммного управления и блока 9 вычисления сплайнов, первой группой 23 входов - к входам записи реверсивных счетчиков 3 группы и регистров 4, и к выходам конца преобразования АЦП 1 группы соответственно, второй 24, третьей 25 группами входов - к первой группе выходов блока 8 микропрограммного управления и к шине данных соответственно, а первым 26 и вторым 27 входами - к шине записи и к шине сброса соответственно

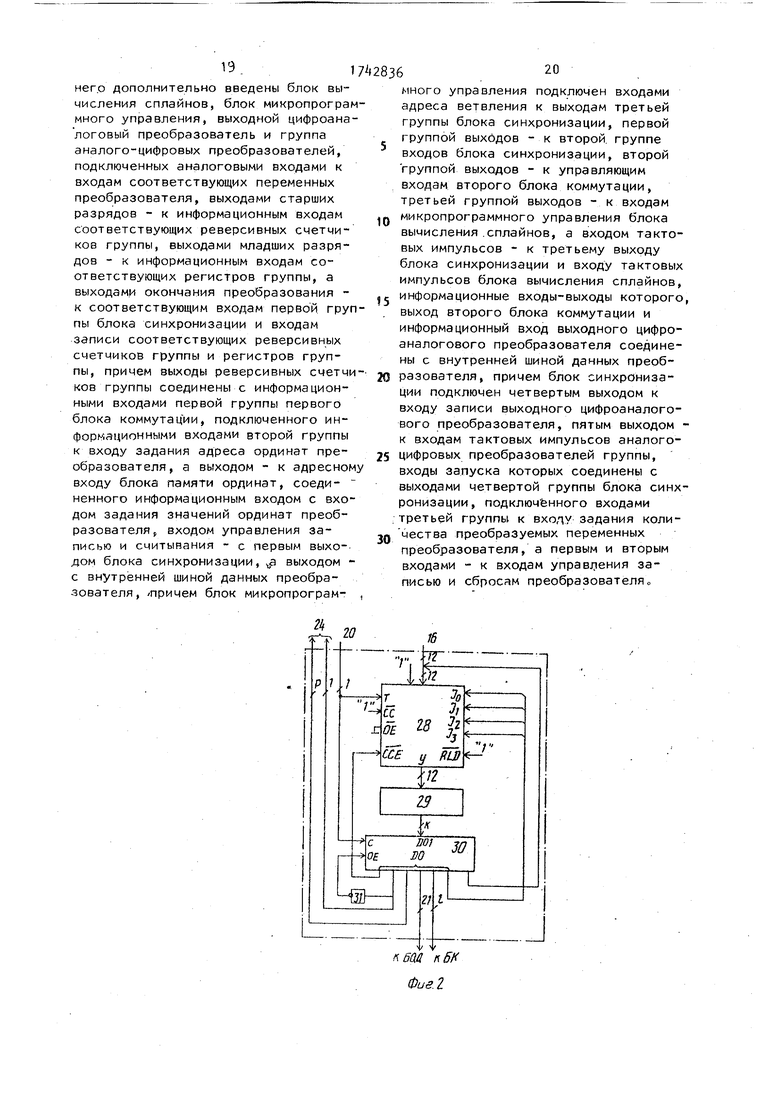

Блок 8 микропрограммного управления (фиго2) может быть выполнен, например, содержащим схему 28 управления последовательностью микрокоманд (УПМ), микропрограммную память 29 (МП), регистр микрокоманд 30 (Pr MK), элемент НЕ 31, выход которого соединен с входом ОЕ регистра микрокоманд 30, а вход - с первым выходом D, регистра микрокоманд 30 и первым выходом первой группы выходов блока 8 микропрограммного управления,остальные выходы первой группы выходов соединены с первой группой выходов D0 регистра микрокоманд 30,-вторая и третья группы выходов D регистра микрокоманд 30 соединены с вторыми третьим выходами блока 8 микропрограммного управления соответственно, четвертая группа выходов D0- с входами J схемы 28 управления последовательностью микрокоманд, второй выход - с входом СТЁ схемы 28 управления последовательностью микрокоманд, выходы DY - с входами D схемы 28 управления последовательностью микрокоманд и вхо

5

5

0

5

0

5

0

5

дами адреса ветвления блока 8 микропрограммного управления, вход тактовых импульсов - с входом тактовых импульсов схемы 28 управления последовательностью микрокоманд и с входом тактовых импульсов блока 8 микропрограммного управления, а входы D1 - с выходами микропрограммной памяти 29, - входы которой соединены с выходами Y схемы 28 управления последователь- ностыо микрокоманд, входы которого СО, ОС, KLD соединены с шиной логической единицы, а вход ОЕ - с общей шиной.

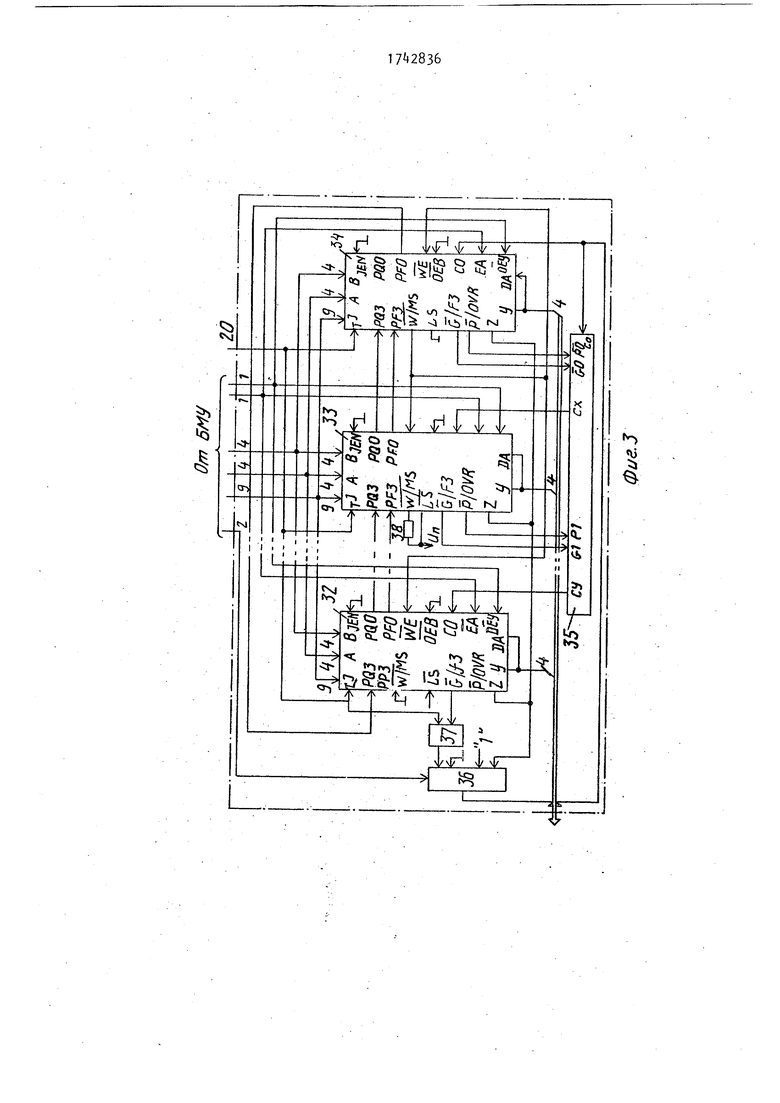

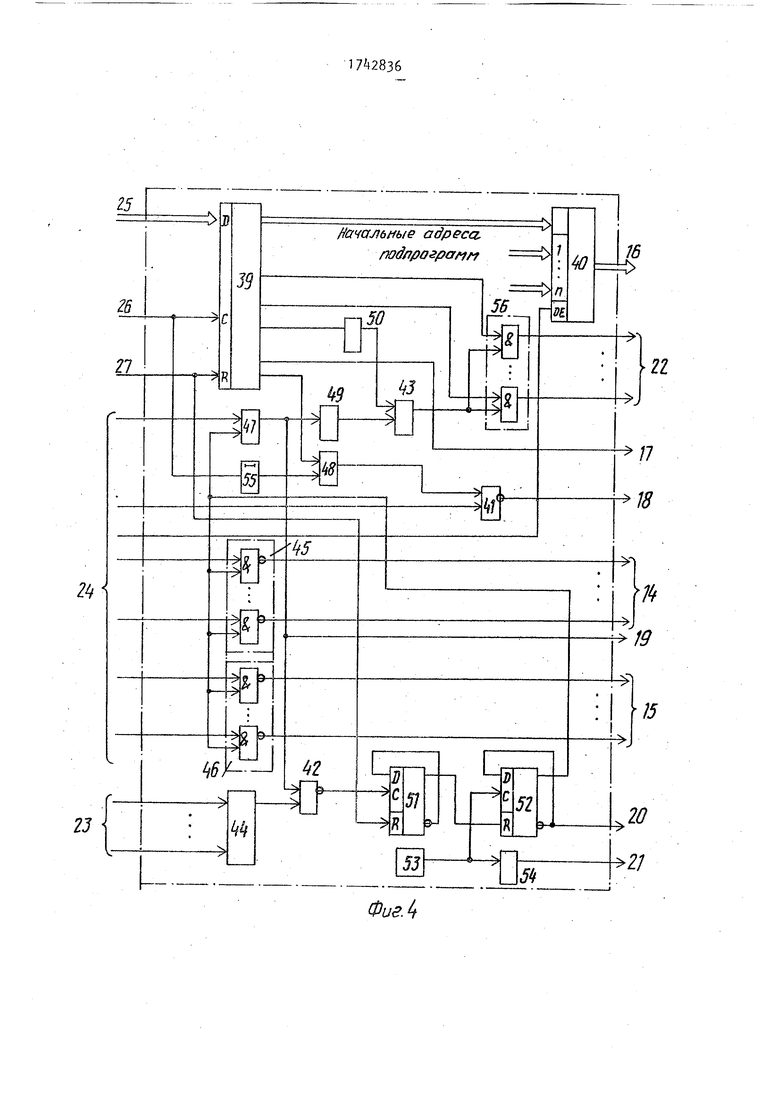

Блок 9 вычисления сплайнов выполнен, например (фиг,3), содержащим первую 32, вторую 33, третью 34 микропроцессорные секции (МПС), схему ускоренного переноса 35 (СУП), мультиплексор 36, D - триггер 37, резистор 38, а блок 13 синхронизации () - регистр 39, мультиплексор 40, элементы ИЛИ-НЕ 41 и 42, элементы ИЛИ 43 и 44, группы элементов И-НЕ 45 и 46, элементы И 47 и 48, одновибрато- ры 49 и 50, триггеры 51 и 52, генератор 53 тактовых импульсов, делитель 54, линию 55 задержки, группу элементов И 56

В качестве АЦП1 использованы АЦП последовательного приближения. В качестве реверсивного счетчика 3 может быть использована микросхема К555 ИЕ7, регистров 4 - К555 ТМ8, блоков 5 адресации и блока 7 коммутации - К555 КП11, запоминающего устройства в - К537 РУЗ, ЦАП11 - К572 ПА2А, схемы 28 управления последовательностью микрокоманд - К1804 ВУ4, микропрограммной памяти 29 - «573 РФ2, регистра 30 микрокоманд - К1804 ИР1, элементов И, НЕ, И-НЕ, ИЛИ-НЕ - микросхемы серий К155, К531 и др,, в качестве микропроцессорных секций 32 - 34 - К1804 ВС2, схемы 35 ускоренного переноса - К1804 ВР1„

Функциональный преобразователь многих переменных работает следующим образом

В основу алгоритма вычисления функции многих переменных положена разностная интерполяционная формула для одного интервала,, Переход от одной области интерполяции функции к другой следует рассматривать как перенос начала координат из одной точки в другую, информацию с которой предстоит сосчитать, а значит алгоритм считывания одинаков для любой области интерполяции:

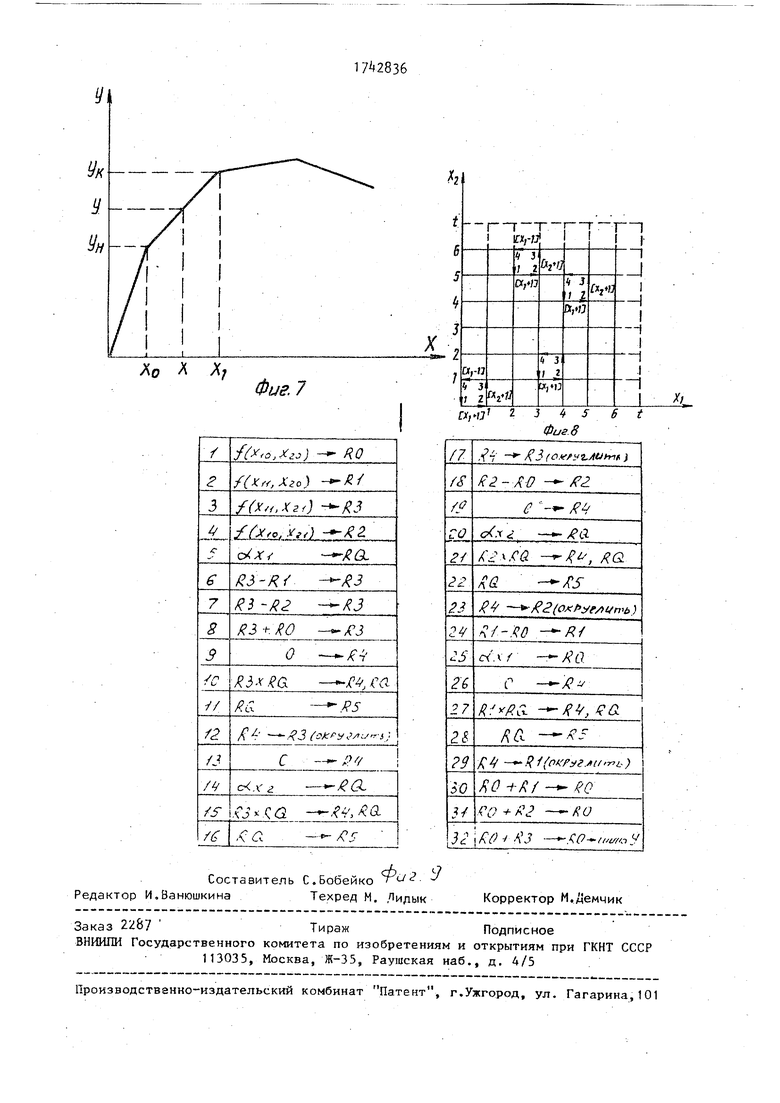

Y YH + (YK- YH)X, (1) где: YH, YK - значения функции в начале и в конце интервала соответственно; (Xj( - коэффициент интерполяции, определяющий значения интерполирующей части входной переменной х„

Пример графической интерпретации формулы для одной переменной приведен на фиг„7о Из графика видно, что -ри изменении X от X0 до X. коэффициент интерполяции

x

1

хТ

изменяется от 0 до 1 о

Рассмотрим работу на примере преобразователя по двум независимым переменным Y f(X1, X2)„ Каждая из независимых переменных Х1, Х2 (фиг„7) разбивается на 1 одинаковых участков интерполяции (Х10 - Х11,.о„, Х20 - Х21, о о о), что формирует (1 + I)1 равномерно расположенных узлов интерполяции на каждой из входных переенных, где п - число независимых пееменных, и Р ячеек интерполяции.

Аналоговая входная переменная X; преобразуется в К-разрядное цифровое слово. Причем m-старших разрядов оп- ределяет область памяти, в которой записаны значения всех узлов интерполяции, а (К -т) младших разрядов определяют количество шагов интерполяции, на которое разбивается каждый участок интерполяции, т0е0 определяет информацию о коэффициенте интерполяции (Ух „

Таким образом, очевидно, что1 чем выше требуемая точность преобразования функции, тем на большее количество участков 1 интерполяции необходимо разбить входные переменные X; и тем на большее количество шагов интерпо - яции необходимо разбить участок 1, что обеспечивается увеличением количества используемых разрядов, как старших, так и младших, К-разрядного слова, в которое преобразуется входная независимая переменная X;, а значит и увеличением необходимого объема памяти о

С учетом изложенного интерполяционная формула для функции двух

2836

10Х1, Х2 имеет следующий

переменных вид:

Y f(X10,X20)(X11.X20)- -f (X10, x20j tfX1 + f (X10.X21)- -f(X10,X20)k X2 + f(X11,X21)- -f (X11,X20)-f (X10,X21)+f (X10,X20)XX1, c(X2,

X2-X20

X1-X10

to

где° Х1 хТТ:Х2 Т X2 X2T:X20

(2)

15

20

25

30

Перед началом работы на второй вход 27 блока 13 приходит сигнал Сброс с шины сброса, который уста- навои вает устройство в исходное сос- тояние„ Сигнал Сброс приходит один раз перед началом работы устройства ,

Запись информации в БПОб осуществляется в следующей последовательности На входах Адрес ординат первого блока 5 коммутации и Значение ординат БПОб устанавливаются адресные и числовые значения ординат, На первый вход 26 блока 13 подается команда Запись (фиг„5-2б), на установные входы 25 блока 13 информации о режиме работы преобразователя (фиг.5 - 25). По первому выходу 17 блока 13 вырабатывается потенциальный сигнал низкого уровня (фиг 5 - 17), поступающий на вход управления мультиплексора адреса первого блока 5 коммутации для управления выбором адреса с шины Адрес ординат

35 и на вход Запись/Считывание БПОб, По второму выходу 18 блока 13 формируется сигнал Выбор кристалла (фиг.5 - 18), поступающий на вход выборки БПОб, Причем формируется он

40 элементом И48 блока 13 из импульсного сигнала Запись, поступающего на вход 26 блока 13 и задержанного на элементе 55 задержки на время переходных процессов в регистре 39, и

45 из сигнала с регистра 39, поступающего на второй вход элемента И 48, а затем поступающего через элемент ИЛИ-НЕ 41 на выход 18 блока 13. Таким образом осуществляется запись

50 в БПОб значения одной (первой) ординаты узловой точки. Затем производится смена адреса узла интерполяции, задается значение его новой (второй) ординаты, и цикл записи

55 повторяется (фиг„5 18, 26).

1 Таким образом осуществляется запись в БПОб всех (1 + 1) узловых значений ординат. Считывание цифро11

,вой информации из БПОб осуществляет- ся в режиме воспроизведения функции нескольких переменных. При этом по команде Запись по входу 26 блока 13 (фиг.5 - 26) в регистр 39 блока 13 по входу 25 заносится информация о режиме работы преобразователя, определяющем выбор количества входных переменных, выбор подпрограммы воспроизведения заданной функции (фиг„5 25).

По первому выходу 17 блока 13 вырабатывается потенциальный сигнал высокого уровня (фиг о 5 - 17), поступающий на вход управления мультиплексора адреса первого блока 5 коммутации для управления выбором адреса с выходом реверсивных счетчиков 3 группы и на вход Запись/Считывание БПОб. На группе 22 выходов блока 13 появляются сигналы запуска АЦП (фиг.5 - 22)о

В результате преобразования входной величины с частотой f АЦП, поступающей на тактовые входы АЦП1 с выхода 21 блока 13, на выходе соответствующих АЦП1 группы появляется К-раз- рядное цифровое число, m-старших разрядов которого подаются на информационные входы реверсивных счетчиков 3 группы, а (К-m) младших разрядов - на информационные входы регистров 4 группы При этом коэффициент деления частоты делителя 5 определяется максимально допустимой частотой преобразования АЦП1 группы. Запись цифрово информации в реверсивные счетчики 3 группы и регистры группы производится сигналами Конец преобразования с соответствующих АЦП1 группы. Одновременно указанный сигнал поступает на первую группу 23 входов блока 13 (фигсб - 23), а затем через элемент ИЛИ № и элемент ИЛИ-НЕ Ь2 на С - вход D триггера 51, который вырабатывает высокий уровень выходного сигнала (фиг.6 - S2), Этот разрешающий сигнал открывает счетный триггер 52 и формирует с помощью импульсов генератора 53 (фиг,.6 - на третьем выходе 20 блока 13 тактовые импульсы (фиг о6 .- 20) для работы блока 8 микропрограммного управления и блока 9 вычисления сплайнов.,

Для того, чтобы при различной величине входных сигналов X; импульсы Конец преобразований на входы 23 блока 13 не поступали в различное

й12

10

15

20

25

836

время и на выходе элемента ИЛИ й не появилось несколько импульсов, в качестве АЦП1 используется схема АЦП последовательного приближения, в которой время преобразования не зависит от величины входного сигнала из-за того, что количество шагов преобразования одинаково вне зависимости от величины входного сигнала, и зависит только от разрядности АЦП„ Кроме того, все АЦП1 группы запускаются от одного импульса, сформированного одновибратором 4э и поступающего одновременно на выходы 22 блока 13 через элемент ИЛИ 43 и через открытые с помощью регистра 39 для данного режима работы элементы И 56 группы. Дальнейшая работа функционального преобразователя осуществляется под управлением выбранной микропрограммы, начальный адрес которой поступает с третьей группы 16 выходов блока 13 на вход адреса ветвления блока 8 микропрограммного управления .

Выборка узлов, принадлежащих той области интерполяции, в которой находятся цесущие координаты узлов независимых переменных, производится в 2П тактов (2 для рассматриваемого примера) при подаче на адресные входы БПОб адреса этой области интерполяции. При этом сигнал Выбор кристалла по шине 18 блока 13 формируется микрокомандно блоком 8 микропрограмм- ого управления с одного из его выходов группы 2 и через элементы ИЛИ-НЕ 1 блока 13

Таким образом формируется т-раз- рядный код, образующийся на выходах реверсивных счетчиков 3 группы, Этот код всегда однозначно выявляет ячейку интерполяции и ее первый узел интерполяции (фиг.8)„ После того, как на выходах реверсивных счетчиков 3 группы установятся кодовые эквиваленты независимых переменных и в БПОб будет выявлен адреса первого узла, которому соответствует адрес- ® ный код Х10,Х20, значение ординаты выявленного узла переписывается в блок.9 вычисления сплайнов (п„1, фиг.ЭК Затем на группе I4 выходов блока 13 вырабатывается сигнал, который увеличивает содержимое первого счетчика 3 группы на единицу млад- шего разряда, и из БПОб извлекается и записывается в БВС9 значение орди30

35

40

45

55

13

маты второго узла (п.2 ) с адресным кодом ЈX11,X20J0

Далее на группе 14 выходов выраба-j тывается сигнал, увеличивающий на | единицу содержимое второго счетчика 3 группы и значение ординаты третьего узла, которому соответствует адресный код ЈХ11,Х21, переписывается в БВС9 (п,3 фиг„9) Затем на группе 15 выходов появляется сигнал, вычитающий на единицу первого счетчика 3 группы, и значение четвертой ординаты с адресом СХ10,Х21 переписывается в БВС9 (пЖфиГоЭК При этом значения коэффициентов интерполяции оЈХ1,о(Х2, находящиеся в соответствующих регистрах 4 группы, заносятся на внутреннюю шину 10 данных через блок 7 коммутации. Далее в этом блоке осуществляется функциональное пре- образ&вание согласно алгоритму вычисления функции двух переменных (фиг„9) по формуле (2).

Результат функционального преобразования в цифровом виде поступает с БВС9 на внутреннюю шину 10 и на последнем такте микропрограммы переписывается в ЦАП 11 сигналом записи с выхода 19 блока 13 о С выхода ЦАП 11 в аналоговом виде выводится значение функции двух переменных Х1 и Х2 в пределах интерполяционной ячейки, ограниченной значениями четырех смежных узлов ординат Таким образом осуществляется цикл вычисления одной ячейки интерполяции После этого на группе 22 выходов блока 13 вновь вырабатываются сигналы Запуск АЦП, происходит опять аналого-цифровое преобразование входных переменных Х1 и Х2, занесение новых значений в реверсивные счетчики 3 группы, регистры 4 группы, и цикл вычислений повторяется согласно алгоритму

10

20

17 2836Й

нулевая микрокоманда, по которой на первом такте в Pr MK 30 заносится микрокоманда из нулевой ячейки микро программной памяти 29° В результате на первый выход первой группы выходов БМУ8 поступает разрешающий (низ кий) потенциал для мультиплексора блока 13i а на вход ОЕ Pr MK30 чере инвертор 31 поступает разрешающий (высокий) потенциал, переводящий вых ды DY в третье состояние,, При этом на входы DYRM 28 поступает начальный адрес выбранной подпрограммы, а

J5 на входы J0-J.J УПМ 28 - микрокоманда устанавливающая на его выходах Y адрее с входов D, Таким образом, начиная с второго такта начинается выпол нение заданной микропрограммы вычисления функции по блок-схеме алгоритма (фиг.8). На последнем такте выпол нения микропрограммы на одном из дру гих выходов первой Р группы выходов Р0 БМУ8 устанавливается высокий уровень, поступающий на первый вход элемента , и открывает его. Тактовый импульс, поступающий с выхода счетного триггера 52 на второй вход элемента , появляется на его выходе и затем на выходе 19 блока 13 для записи результата вычисления в ЦАП Ib

С Pr MK 30 по второй группе 1 выходов D0 осуществляется управление вторым блоком 7 коммутации, с выхода

35 которого через общую шину 10 в

БВС9 поступают значения коэффициенто интерполяции , записанные в регистрах 4 группы, С Pr MK 30 по третьей группе выходов D0 осуществляется по соответствующим входам микропрограммное управление БВС9. Блок 9 вычисления сплайнов (фиг.З) предназначен для воспроизведения фун ции многих переменных (двух пёремен25

30

40

(фиг„9)о Аналогичным образом строится ных) по заданному алгоритму (фиг.9).

работа и в случае функционального преобразования по трем и более независимым переменным. Блок 8 микро- программного управления (фиг.2) осуществляет микропрограммное управление по первой группе выходов - отдельными узлами блока 13, по второй группе выходов - вторым блоком 7 коммутации, по третьей группе выходов - блоком 9 вычисления сплайнов„

В исходном состоянии регистр 30 микрокоманд (Pr MK) БМУ 8 обнулен, и на входы Jp - J3 УПМ 28 подается

50

Значения ординат, находящиеся в БПОб, заносятся в регистры общего назначения (РОН) микропроцессорных секций 32 - 3 через их двунаправленные входы Y, значения коэффициентов интерполяции X: в регистр QMI1C 32-3 через их входы DA.

Результаты функционального преобразования в цифровом виде поступают 55 с выходов Y МПС 32-3 на внутреннюю шину 10 о На входы А и В этих МПС подаются адреса РОН-ов, участвующих в выполнении данной микрокоманды,

j |

10

20

7 2836Й

нулевая микрокоманда, по которой на первом такте в Pr MK 30 заносится микрокоманда из нулевой ячейки микропрограммной памяти 29° В результате на первый выход первой группы выходов БМУ8 поступает разрешающий (низкий) потенциал для мультиплексора 0 блока 13i а на вход ОЕ Pr MK30 через инвертор 31 поступает разрешающий (высокий) потенциал, переводящий выходы DY в третье состояние,, При этом на входы DYRM 28 поступает начальный адрес выбранной подпрограммы, а

J5 на входы J0-J.J УПМ 28 - микрокоманда 1 устанавливающая на его выходах Y ад рее с входов D, Таким образом, начиная с второго такта начинается выполнение заданной микропрограммы вычисления функции по блок-схеме алгоритма (фиг.8). На последнем такте выполнения микропрограммы на одном из других выходов первой Р группы выходов Р0 БМУ8 устанавливается высокий уровень, поступающий на первый вход элемента , и открывает его. Тактовый импульс, поступающий с выхода счетного триггера 52 на второй вход элемента , появляется на его выходе и затем на выходе 19 блока 13 для записи результата вычисления в ЦАП Ib

С Pr MK 30 по второй группе 1 выходов D0 осуществляется управление вторым блоком 7 коммутации, с выхода

35 которого через общую шину 10 в

БВС9 поступают значения коэффициентов интерполяции , записанные в регистрах 4 группы, С Pr MK 30 по третьей группе выходов D0 осуществляется по соответствующим входам микропрограммное управление БВС9. Блок 9 вычисления сплайнов (фиг.З) предназначен для воспроизведения функции многих переменных (двух пёремен25

30

40

ных) по заданному алгоритму (фиг.9).

Значения ординат, находящиеся в БПОб, заносятся в регистры общего назначения (РОН) микропроцессорных секций 32 - 3 через их двунаправленные входы Y, значения коэффициентов интерполяции X: в регистр QMI1C 32-3 через их входы DA.

Результаты функционального преобразования в цифровом виде поступают с выходов Y МПС 32-3 на внутреннюю шину 10 о На входы А и В этих МПС подаются адреса РОН-ов, участвующих в выполнении данной микрокоманды,

15 - 1 на вход J - девятиразрядная микроко- манда. Мультиплексор 36 формирует необходимый сигнал входного переноса СО младшей МПС (логический О, логическая 1, сигнал Z, сигнал КЗ старшей МПС 32)с

Работа БМУ 8 и БВС9 синхронизуется импульсами тактовой частоты, поступающими по шине 20 с блока 13. Блок 13 (фигЛ) осуществляет синхронизацию взаимодействия отдельных узлов функционального преобразователя многих переменных. Возможный вариант его реализации для п входных переменных изображен на фиг« и Внешнее управление блоком 13 осуществляется по первому входу 26 командой

Запись1

по второму входу 27 а также по Конец прекомандой Сброс, по третьей группе 25 установочных входов регистра 39 блока 13 синхронизации, первой группе 23 входов образования АЦП 1 группы и по второй группе 24 входов сигналами блока 8 микропрограммного управленияс

Блок 13 формирует следующие выходные сигналы: Запуск АЦП по четвертой группе 22 выходов, тактовые импульсы АЦП по пятому выходу 21, Запись-считывание по первому выходу 17, Выбор кристалла по второму выходу 18, тактовые импульсы микропрограмнного управления f по третьем выходу 20, Запись ЦАП по четвертому выходу 19, а также сигналы -1 по отдельным выходам второй группы 15 выходов, +1 по отдельным выходам первой группы 14 выходов и адрес ветвления по отдельным выходам третьей группы 16 выходов В зависимости от содержимого регистра 39 блока 13 определяющего режим работы устройства, происходит либо запись информации в БПОб, либо воспроизведение функции нескольких переменных

При записи информации в БПОб на входах Адрес ординаты первого блока 5 коммутации и на входах Значение ординаты БПОб устанавливаются соответственно адресная и числовая информация, и на вхрд 26 поступает сигнал Запись одновременно с информацией на установочных входах 25 регистра 39° При этом на выходе этого регистра устанавливается информация так, что на первом выходе 17 устанавливается потенциальный сигнал низкого уровня (фиг.5 - 17), посту

0

16

пающий на вход управления мультиплексора адреса первого блока 5 коммутации для управления выбором адреса с шины Адрес ординат, и на вход Запись/Считывание БПОб. На первом входе элемента И 48 устанавливается сигнал разрешения (высокий уровень) с тем, чтобы импульс Запись, поступающий на элемент задержки 55, прошел через элемент И 48, элемент ИЛИ- НЕ 41 и появился на втором выходе 18„ Элемент задержки 55 необходим для

5

5

0

5

0

5

0

рой выход 18 Выбор кристалла по отношению к первому выходу 17о Таким образом осуществляется цикл записи в ЬПОб значения одной ординаты узловой точки Запись остальных значений ординат узловых точек в БПОб осуществляется аналогичным образом,

В режиме считывания (воспроизведения функции) в регистр 39 блока 13 записывается информация о режиме работы преобразователя. При этом на первом выходе 17 устанавливается потенциальный сигнал высокого уровня (фиг.5 - 17), поступающий на вход управления мультиплексора адреса первого блока 5 коммутации для управления выбором адреса с выходов реверсивных счетчиков 3 группы и на вход Запись/Считывание БПОб„ На первом выходе элемента И 48 устанавливается запрещающий сигнал (низкий уровень), на входе одновибратора 50 устанавливается сигнал, запускающий его (высокий уровень), и с выхода импульс Запуск АЦП через элемент ИЛИ 43 поступает на первые входы элементов И 56 группы. На вторые входы элементов И 56 группы поступают сигналы с регистра 39 (разрешающие или запре- щащие в зависимости от записанной и него информации), определяющей количество входных переменных). При этом сигналы Запуск АЦП появятся на тех выходах четвертой группы 22 выходов, количество которых соответствует количеству входных переменных. На входы управления мультиплексора 40 приходят сигналы с регистра 39 и выбирают начальный адрес одной и подпрограмм.

Генератор тактовых импульсов 53 и делитель частоты 54 формируют так- 5 товые импульсы АЦП, которые поступают на АЦП1 группы с пятого выхода 21 блока 13 После преобразования входных величин соответствующими АЦП1

171

группы сигналы Конец преобразования поступают через первую группу 23 входов на элемент ИЛИ 44, с выхода которого сигнал поступает на первый вход элемента ИЛИ-НЕ 42. По заднему фронту импульса Конец преобразования счетный триггер 51 устанавливается в единичное состояние и этим разрешает работу счетного триггера 52.

Тактовая частота с инверсного выхода счетного триггера 52 через третий выход 20 поступает на входы тактовых импульсов блока микропрограммного управления 8 и блока 9 вычисления сплайнов. На первые входы элементов И-НЕ 45 и 46 и на первый вход элемента И 47 поступает тактовая частота с прямого выхода счетного триггера 52„ При этом из блока 8 микропрограммного управления по отдельному входу группы 2k входов на вход DE Разрешение по выходу мультиплексора 40 приходит разрешающий сигнал, по которому на третьей группе 16 выходов из мультиплексора 40 поступает начальный адрес подпрограммы функционального преобразования выбранного количества переменных.

На последующих тактах выполнения микропрограммы на вторые входы элементов И-НЕ 45 и 46 группы через остальные входы второй группы 24 входов поступают сигналы (высокого уровня) и на выходах этих элементов формируются сигналы суммирования и вычитания, поступающие на соответствующие реверсивные счетчики 3 группы через первую 14 и вторую 15 группы выходов блока 13 На последнем такте выполнения микропрограммы по отдельному входу второй группы 24 входов поступает сигнал высокого уров- . ня на второй вход элемента И 47, и с его выхода импульс тактовой частоты поступает на второй вход элемента ИЛИ-НЕ 42 и своим задним фронтом устанавливает счетный триггер 51 в нулевое состояние, обусловливая блокировку тактовых импульсов, поступающих на третий выход 20 блока 13 Кроме этого, импульс с выхода элемента И 4 поступает через четвертый выход 19 блока 13 на вход записи ЦАП 11 и на вход одновибратора 49, с выхода которого сформированный импульс запуска АЦП через второй вход эле

o

5

0

836

18

мента ИЛИ 41 и первые входы элементов И 56 группы поступает на отдельные выходы четвертой группы 22 выходов для запуска соответствующих АЦП 1 гоуппы, и процесс считывания повторяется о

Функциональный преобразователь позволяет оперативно перестраивать его как на широкий класс функций, так и на любое число наперед заданных независимых переменных без изменения структуры преобразователя, производить преобразование переменных, представленных в аналоговой форме. При этом оперативная перестройка может осуществляться автоматически с помощью ЭВМ, изменение режима раооты, выбор количества входных переменных происходит с помощью ЭВМ, которая записывает данные в регистр управления блока синхронизации, а выбор и вычисление воспроизводимой функции - с помощью подпрограмм, хра 5 нящихся в ПЗУ БМУ„ Загрузка данных в БПО преобразователя осуществляется автоматически перед началом работы при помощи ЭВМ. Время выполнения микропрограммы одного цикла вычисления функции трех переменных при тактовой частоте БМУ - 10 МГц составляет 40 мкс, что дает возможность производить функциональное преобразование входных 3 6 переменных в диапазоне частот до 200 Гц в реальном масштабе времени с заданной точностью

0

5

Формула изобретения

Функциональный преобразователь многих переменных, содержащий два блока коммутации, первый из которых подключен управляющим входом к первому выходу блока синхронизации, а второй блок коммутации соединен с информационными входами с выходами регистров группы, блок памяти ординат, подключенный входом выборки к второму выходу блока синхронизации, и группу реверсивных счетчиков,, суммирующие и вычитающие входы которых соединены с выходами первой и второй групп блока синхронизации соответственно, отличающийся тем, что, с целью расширения области применения за счет оперативного изменения количества преобразуемых переменных и преобразования переменных„ представленных в аналоговой форме, в

19.1

нег.о дополнительно введены блок вычисления сплайнов, блок микропрограммного управления, выходной цифроана- логовый преобразователь и группа аналого-цифровых преобразователей, подключенных аналоговыми входами к входам соответствующих переменных преобразователя, выходами старших разрядов - к информационным входам соответствующих реверсивных счетчиков группы, выходами младших разрядов - к информационным входам со

ответствующих регистров группы, а выходами окончания преобразования - к соответствующим входам первой группы блока синхронизации и входам записи соответствующих реверсивных счетчиков группы и регистров группы, причем выходы реверсивных счетчи- ков группы соединены с информационными входами первой группы первого блока коммутации, подключенного информационными входами второй группы к входу задания адреса ординат преобразователя, а выходом - к адресному входу блока памяти ординат, соеди- ненного информационным входом с входом задания значений ординат преобразователя,, входом управления записью и считывания - с первым выхо- дом блока синхронизации, ъа выходом - с внутренней шиной данных преобразователя, /причем блок микропрограм- ,

20

много управления подключен входами адреса ветвления к выходам третьей группы блока синхронизации, первой группой выходов - к второй группе входов блока синхронизации, второй группой выходов - к управляющим входам второго блока коммутации, третьей группой выходов - к входам микропрограммного управления блока вычисления .сплайнов, а входом тактовых импульсов - к третьему выходу блока синхронизации и входу тактовых импульсов блока вычисления сплайнов,

r информационные входы-выходы которого, . выход второго блока коммутации и информационный вход выходного цифро- аналогового преобразователя соединены с внутренней шиной данных преобразователя, причем блок синхронизации подключен четвертым выходом к входу записи выходного цифроаналого- вого преобразователя, пятым выходом - к входам тактовых импульсов аналого5 цифровых преобразователей группы, входы запуска которых соединены с выходами четвертой группы блока синхронизации, подключенного входами третьей группы к входу задания количества преобразуемых переменных преобразователя, а первым и вторым входами - к входам управления записью и сбросам преобразователя

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Функциональный преобразователь | 1986 |

|

SU1352476A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в аналоговых и аналого-цифровых вычислительных машинах и системах при моделировании сложных динамических процессов. Цель изобретения - расширение области применения за счет оперативного измене.ния количества преобразуемых переменных и преобразования переменных, представленных в аналоговой форме. Функциональный преобразователь многих переменных содержит группу аналого- цифровых преобразователей 1, группу реверсивных счетчиков 3 группу регистров h, блоки коммутации 5 и 7, блок- памяти ординат 6, блок микропрограммного управления 8, блок вычисления сплайнов 9, цифро-аналоговый преобразователь 11 и блок 13 синхронизации. Введение новых узлов 1,8, 9 и 11 и связей позволяет автоматически перестраивать функциональный преобразователь на воспроизведение широкого класса функциональных зависимостей с изменяющимся числом независимых переменных в реальном масштабе времени, 9 ил. (Л С

к БМ к5/ Фиг. 2

I ч

I

I

t

J)

Начальные адреса, подлрогра/чгг

39

26

50

01

27

W

47

55

№

;

5

tt

:

46

J

ьг

-

ii

23

Ц

i.

16

56

г

21

я

-is

Р

«

11 18

Л

я

51

51

Э-

20

О

л

11

Фиг 4

Режим записи. 8 ЗУ 6

23

Л.

57

53

20 Ю

22

шялллпяти

L.TLJ

Л

Режим чтения из ЗУ 6

Фиг. 5

1

Л

Фиг. 6

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-23—Публикация

1990-04-17—Подача