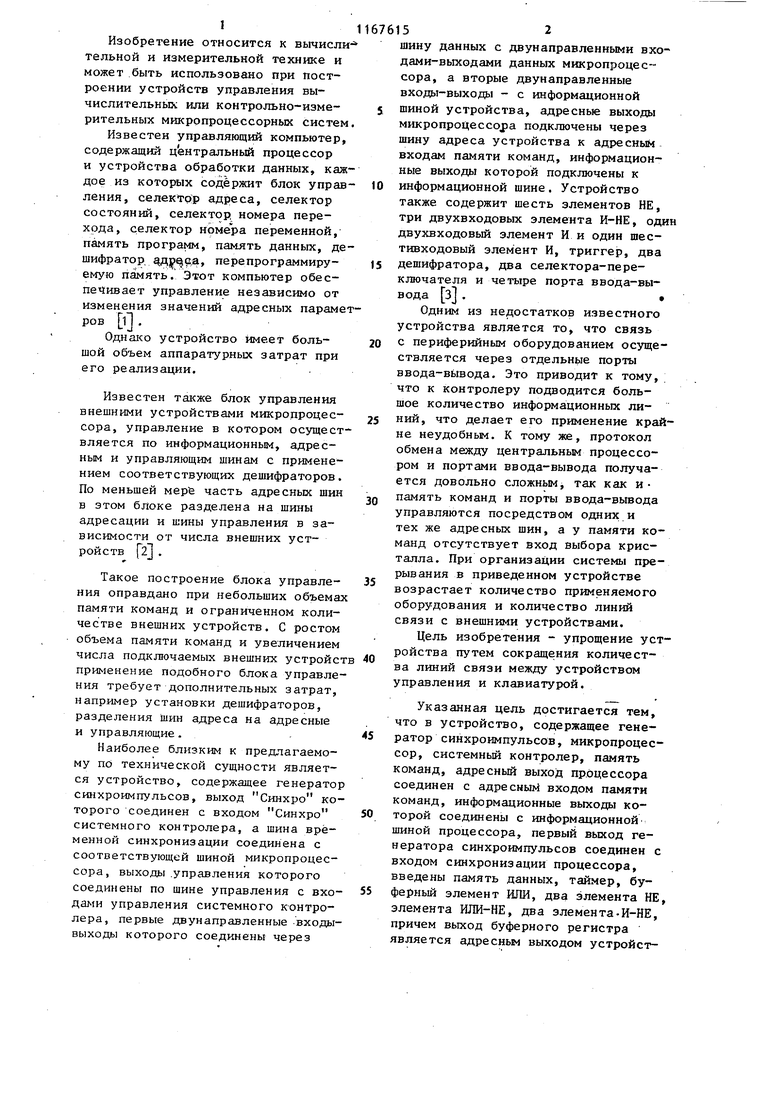

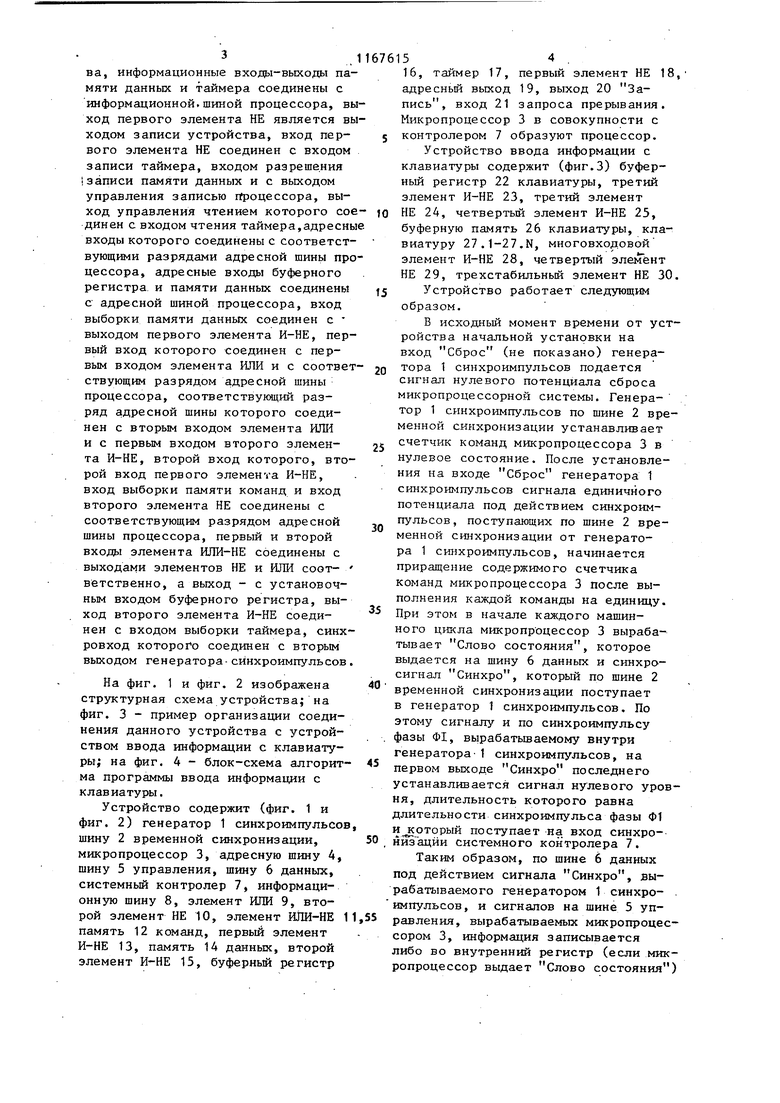

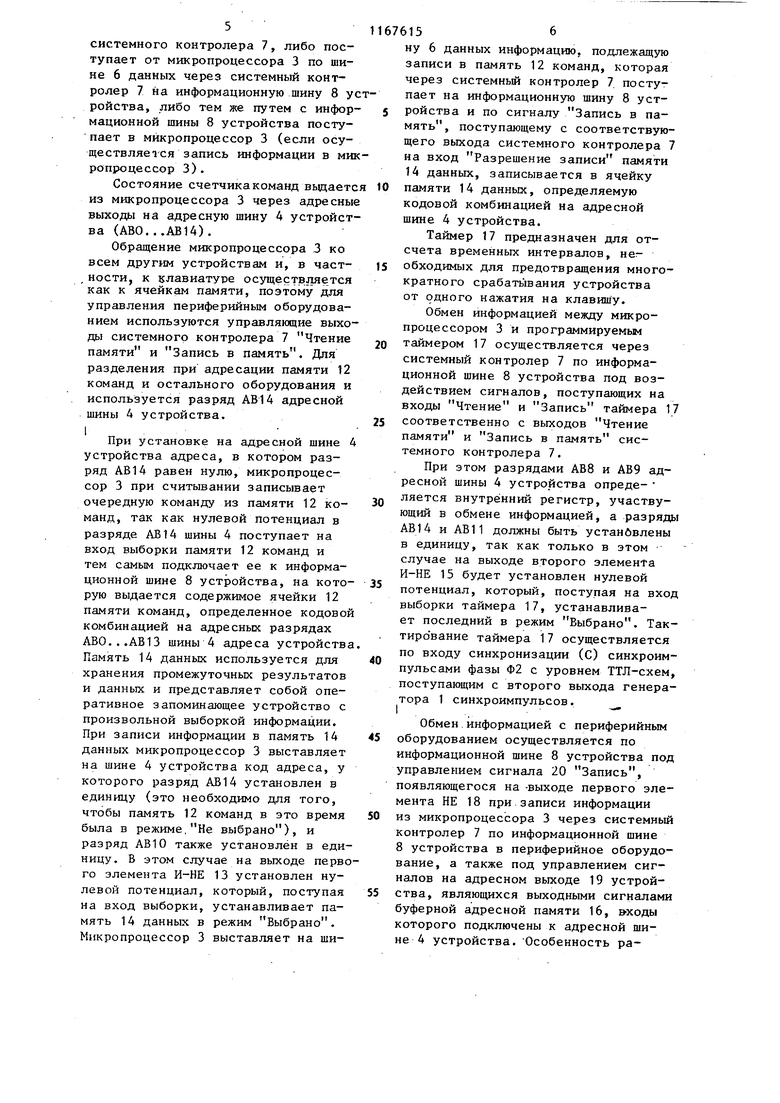

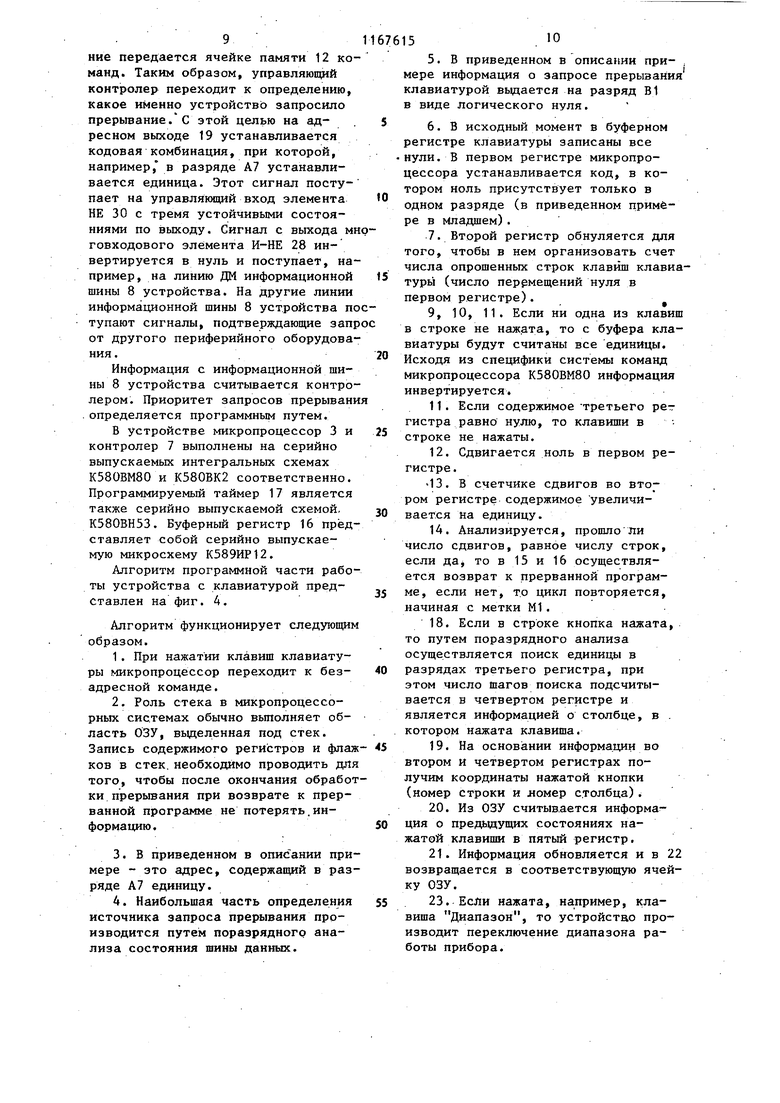

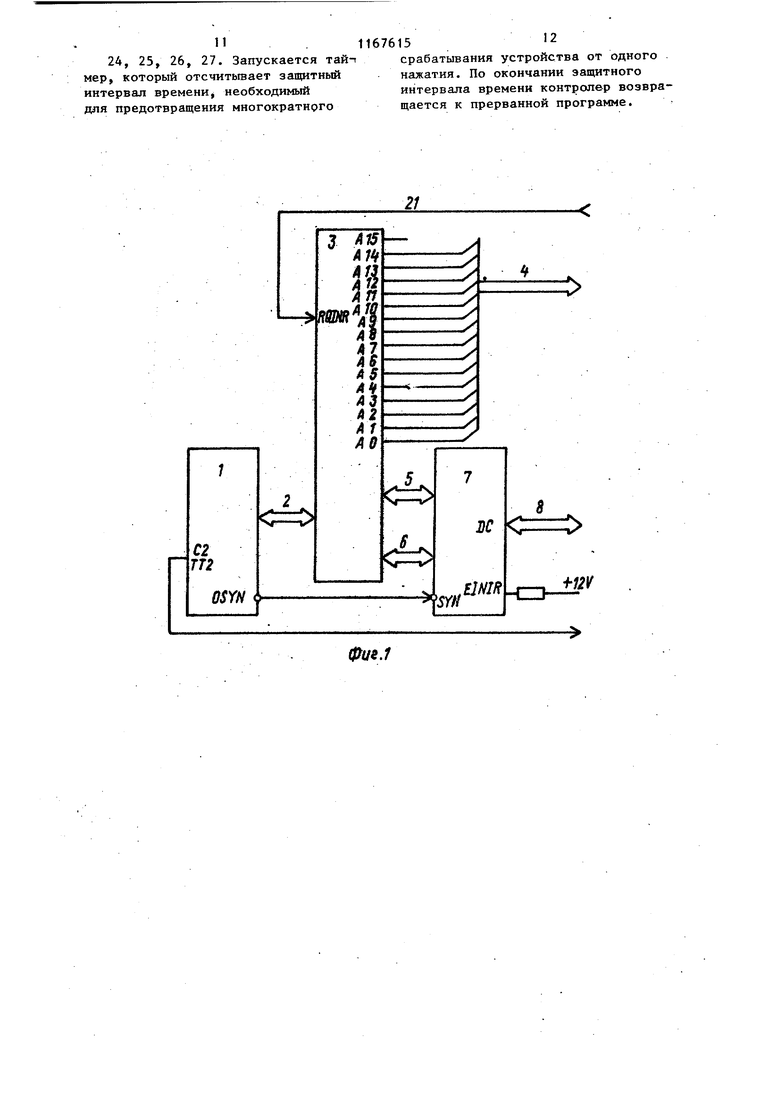

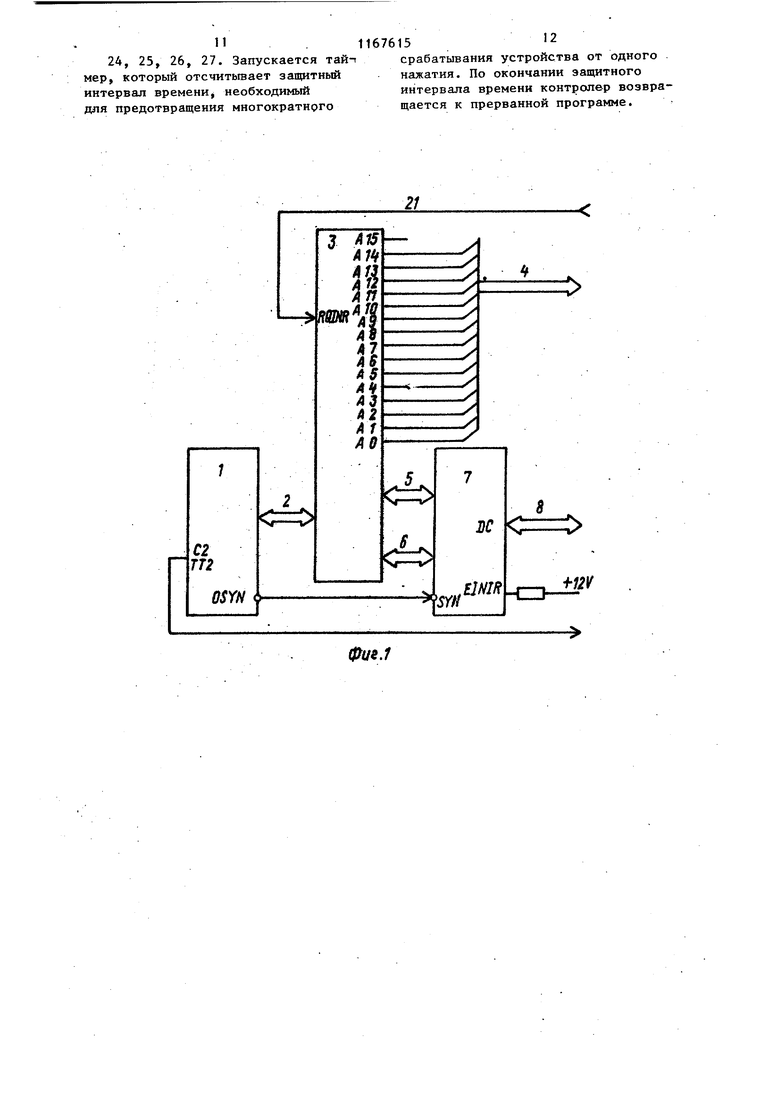

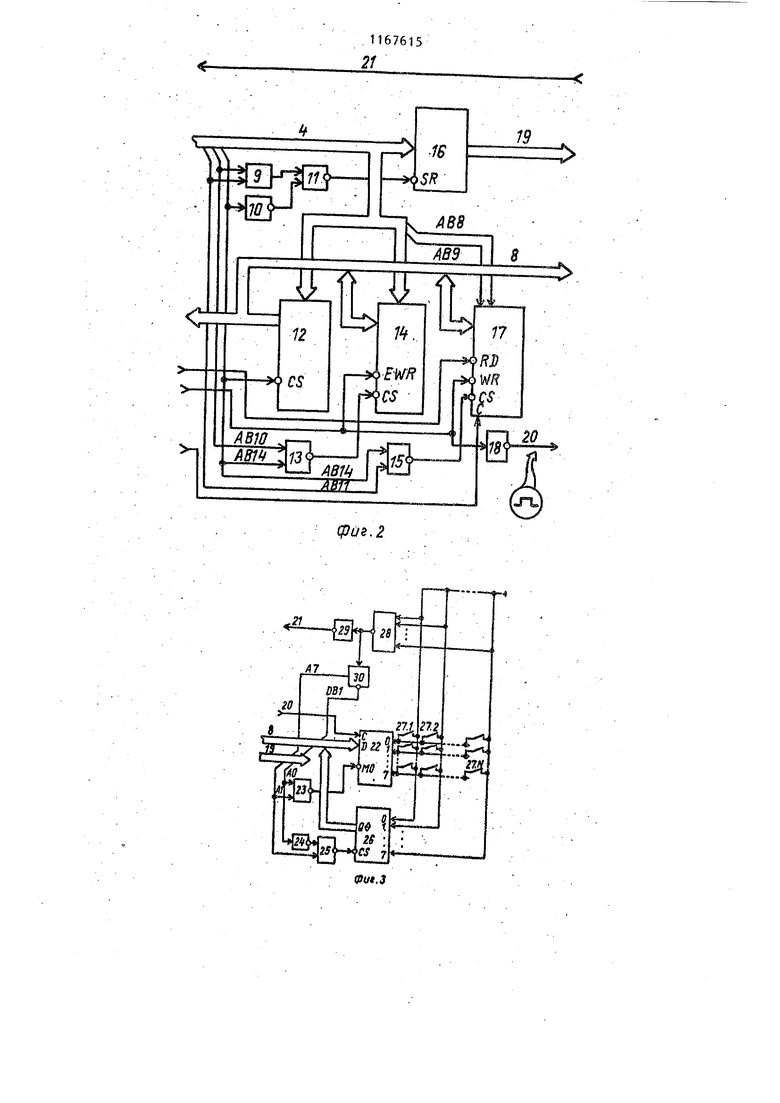

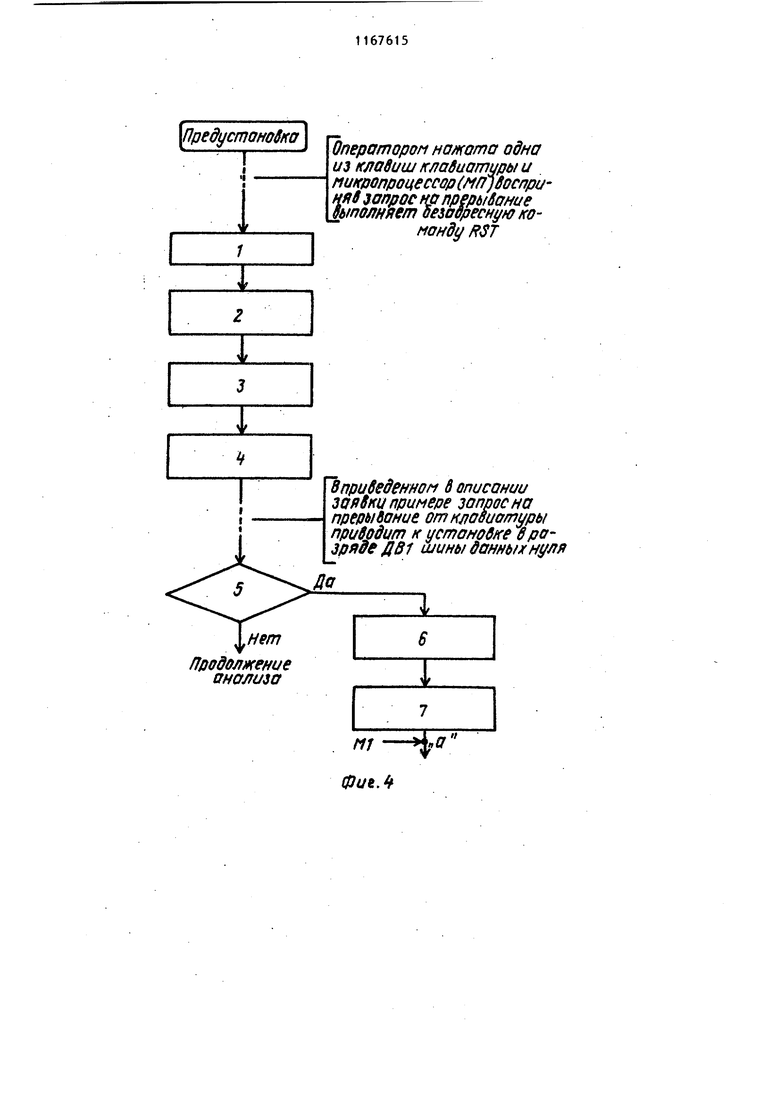

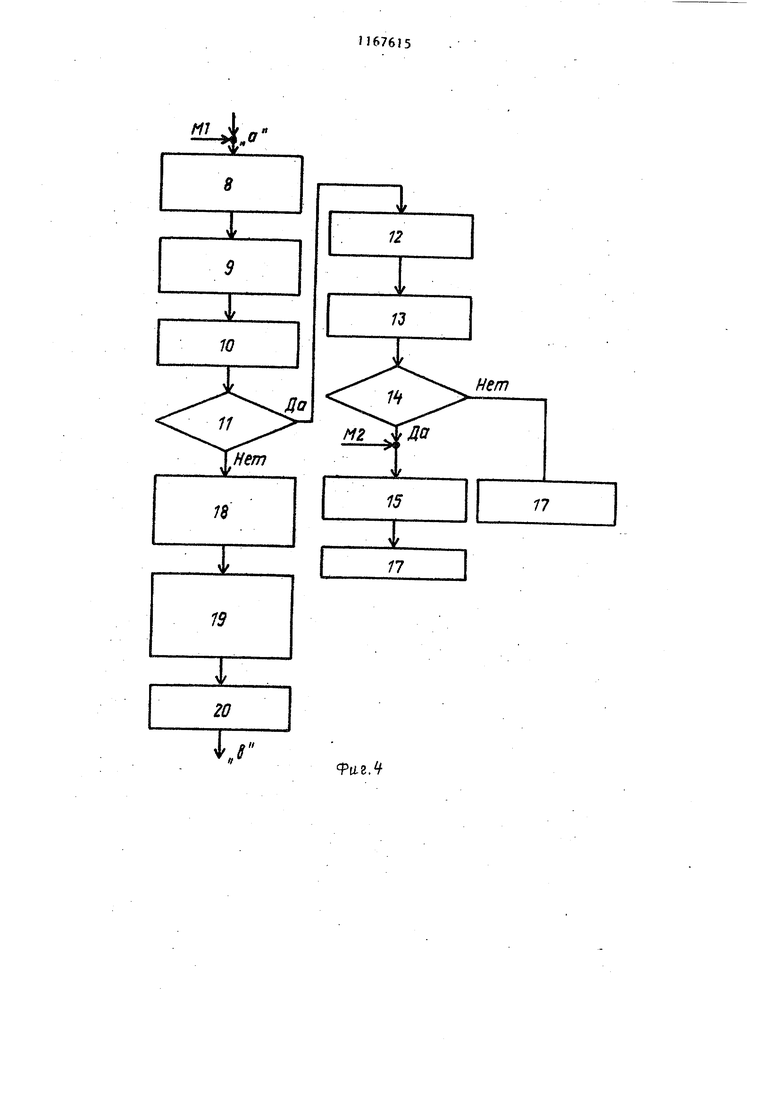

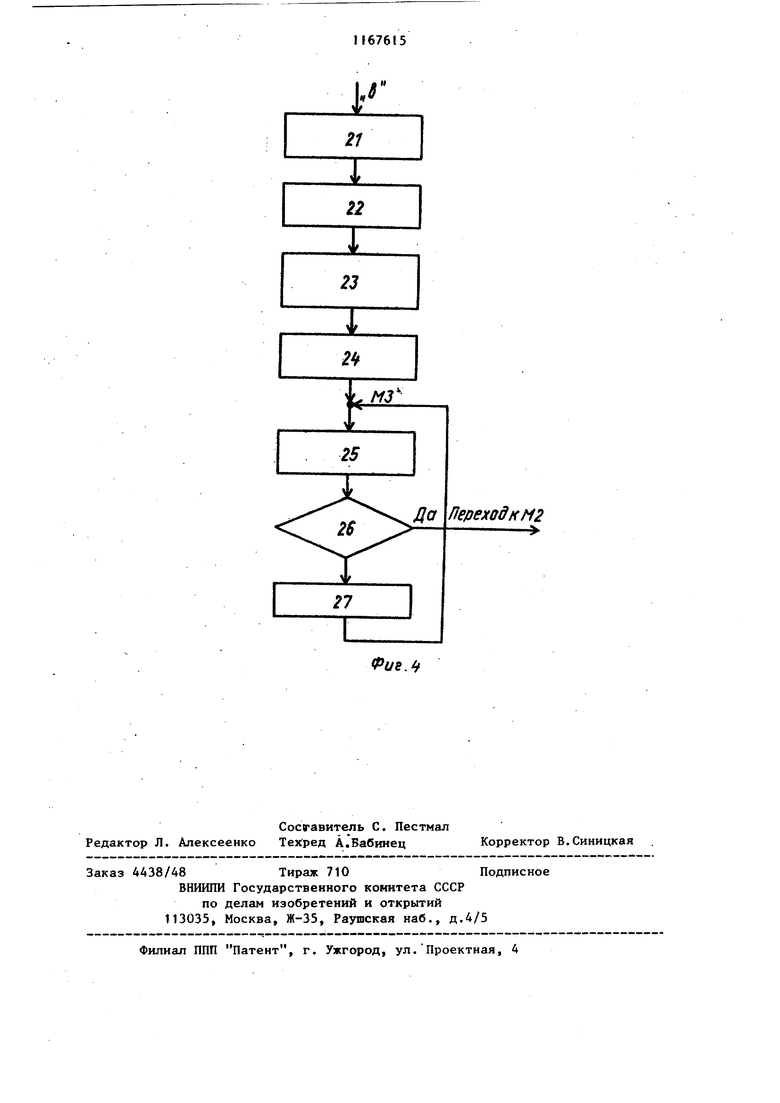

Изобретение относится к вычисли тельной и измерительной технике и может быть использовано при построении устройств управления вычислительных или контрольно-измерительных микропроцессорных систем Известен управляющий компьютер, содержащий центральный процессор и устройства обработки данных, каж дое из которых содержит блок управ Ленин, селектоР адреса, селектор состояний, селектор номера перехода, селектор номера переменной, память программ, память данных, де шифратор , перепрограммируемую память. Этот компьютер обеспечивает управление независимо от изменения значений адресных параме ров l . Однако устройство имеет большой объем аппаратурных затрат при его реализации. Известен также блок управления внешними устройствами микропроцессора, управление в котором осущест вляется по информационным, адресным и управляющим шинам с применением соответствующих дешифраторов. По меньшей мере часть адресных шин в зтом блоке разделена на шины адресации и шины управления в зависимости от числа внешних устройств 2J . Такое построение блока управления оправдано при небольших объема памяти команд и ограниченном количестве внешних устройств. С ростом объема памяти команд и увеличением числа подключаемых внешних устройс применение подобного блока управле ния требует дополнительных затрат, например установки дешифраторов, разделения Шин адреса на адресные и управляющие.. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее генерато синхроимпульсов, выход Синхро ко торого соединен с входом Синхро системного контролера, а шина временной синхронизации соединена с соответствующей шиной микропроцессора, выхода .управления которого соединены по шине управления с вхо даь1и управления системного контролера, первые двунаправленные входы выходы которого соединены через шину данных с двунаправленными входами-выходами данных микропроцессора, а вторые двунаправленные входы-выхода - с информационной шиной устройства, адресные выходы микропроцессора подключены через шину адреса устройства к адресным входам памяти команд, информационные выходы которой подключены к информационной шине. Устройство также содержит шесть элементов НЕ, три двухвходовых элемента И-НЕ, один двухвходовый элемент И и один шестивходовый элемент И, триггер, два дешифратора, два селектора-переключателя и четыре порта ввода-вывода з. Одним из недостатков известного устройства является то, что связь с периферийньш оборудованием осуществляется через отдельные порты ввода-вывода. Это приводит к тому, что к контролеру подводится большое количество информационных линий, что делает его применение крайне неудобньм. К тому же, протокол обмена между центральным процессором и портами ввода-вывода получается довольно сложным, так как ипамять команд и порты ввода-вьгоода управляются посредством одних.и тех же адресных шин, а у памяти команд отсутствует вход выбора кристалла. При организации системы прерывания в приведенном устройстве возрастает количество применяемого оборудования и количество линий связи с внешними устройствами. Цель изобретения - упрощение устройства путем сокращения количества линий связи между устройством управления и клавиатурой. Указанная цель достигается тем, что в устройство, содержащее генератор синхроимпульсов, микропроцессор, системный контролер, память команд, адресный выход процессора соединен с адресным входом памяти команд, информационные выходы которой соединены с информационной шиной процессора, первый выход генератора синхроимпульсов соединен с входом синхронизации процессора, введены память данных, таймер, буферный элемент ИЛИ, два элемента НЕ, элемента ШШ-НЕ, два эле мен та-И-НЕ, причем выход буферного регистра является адресньм выходом устройства, информационные входы-выходы па мяти данных и таймера соединены с информационной.шиной процессора, в ход первого элемента НЕ является в ходом записи устройства, вход первого элемента НЕ соединен с входом записи таймера, входом разрешения 1 записи памяти данных и с выходом управления записью процессора, выход управления чтением которого со динен с входом чтения таймер а, адресн входы которого соединены с соответст вующими разрядами адресной шины пр цессора, адресные входы буферного регистра и памяти данных соединены с адресной шиной процессора, вход выборки памяти данных соединен с выходом первого элемента И-НЕ, пер вый вход которого соединен с первым входом элемента ИЛИ и с соотве ствующим разрядом адресной шины процессора, соответствукиций разряд адресной шины которого соединен с вторым входом элемента ИЛИ и с первым входом второго злемента И-НЕ, второй вход которого, вто рой вход первого элемента И-НЕ, вход выборки памяти команд и вход второго элемента НЕ соединены с соответствующим разрядом адресной шины процессора, первый и второй входы элемента ШШ-НЕ соединены с выходами элементов НЕ и ИЛИ соответственно, а выход - с установочным входом буферного регистра, выход второго элемента И-НЕ соединен с входом выборки таймера, синх ровход которого соединен с вторым выходом генератора-синхроимпульсов На фиг. 1 и фиг. 2 изображена структурная схема устройства; на фиг. 3 - пример организации соединения данного устройства с устройством ввода информации с клавиатуры; на фиг. 4 - блок-схема алгорит ма программы ввода информации с клавиатуры. Устройство содержит (фиг. 1 и фиг. 2) генератор 1 синхроимпульсо шину 2 временной синхронизации, микропроцессор 3, адресную шину 4, шину 5 управления, шину 6 данных, системный контролер 7, информационную шину 8, элемент ИЛИ 9, второй элемент НЕ 10, элемент ИПИ-НЕ память 12 команд, первый элемент И-НЕ 13, память 14 данных, второй элемент И-НЕ 15, буферный регистр 16, таймер 17, первый элемент НЕ 18, адресный выход 19, выход 20 Запись, вход 21 запроса прерывания. Микропроцессор 3 в совокупности с контролером 7 образуют процессор. Устройство ввода информации с клавиатуры содержит (фиг.З) буферный регистр 22 клавиатуры, третий элемент И-НЕ 23, третий элемент НЕ 24, четвертый элемент И-НЕ 25, буферную память 26 клавиатуры, клавиатуру 27.1-27.N, многовходовой элемент И-НЕ 28, четвертый элемент НЕ 29, трехстабильньм элемент НЕ 30. Устройство работает следующим образом. В исходньш момент времени от устройства начальной установки на вход Сброс (не показано) генератора 1 синхроимпульсов подается сигнал нулевого потенциала сброса микропроцессорной системы. Генератор 1 синхроимпульсов по шине 2 временной синхронизации устанавливает счетчик команд микропроцессора 3 в нулевое состояние. После установления на входе Сброс генератора 1 синхроимпульсов сигнала единичного потенциала под действием синхроимпульсов , поступающих по шине 2 временной синхронизации от генератора 1 синхроимпульсов, начинается приращение содержимого счетчика команд микропроцессора 3 после выполнения каждой команды на единицу. При этом в начале каждого машинного цикла микропроцессор 3 вырабатывает Слово состояния, которое выдается на шину 6 данных и синхросигнал Синхро, который по шине 2 временной синхронизации поступает в генератор 1 синхроимпульсов. По этому сигналу и по синхроимпульсу фазы Ф1, вырабатьшаемому внутри генератора-1 синхроимпульсов, на первом выходе Синхро последнего устанавливается сигнал нулевого уровня, длительность которого равна длительности синхроимпульса фазы Ф1 и оторый поступает на. вход синхронизации системного контролера 7. Таким образом, по шине 6 данных под действием сигнала Синхро, вырабатываемого генератором 1 синхро- . импульсов, и сигналов на шине 5 управления, вырабатываемых микропроцессором 3, информация записывается либо во внутренний регистр (если микропроцессор выдает Слово состояния) 5 системного контролера 7, либо поступает от микропроцессора 3 по шине 6 данных через системный контролер 7 на информационную шину 8 у ройства, либо тем же путем с инфор мационной шины 8 устройства поступает в микропроцессор 3 (если осуществляе1ся запись информации в ми ропроцессор 3). Состояние счетчика команд выдаетс из микропроцессора 3 через адресны выходы на адресную шину 4 устройст ва (АВО.,.АВ14). Обращение микропроцессора 3 ко всем другим устройствам и, в част, ности, к клавиатуре осуществляется как к ячейкам памяти, поэтому для управления периферийным оборудованием используются управляющие выхо ды системного контролера 7 Чтение памяти и Запись в память. Для разделения при адресации памяти 12 команд и остального оборудования и используется разряд АВ14 адресной шины 4 устройства. При установке на адресной шине устройства адреса, в котором разряд АВ14 равен нулю, микропроцессор 3 при считывании записывает очередную команду из памяти 12 команд, так как нулевой потенциал в разряде АВ14 шины 4 поступает на вход выборки памяти 12 команд и тем самым подключает ее к информационной шине 8 устройства, на которую выдается содержимое ячейки 12 памяти команд, определенное кодовой комбинацией на адресных разрядах АВО...АВ13 шины 4 адреса устройств Память 14 данных используется для хранения промежуточных результатов и данных и представляет собой оперативное запоминающее устройство с произвольной выборкой информации. При записи информации в память 14 данных микропроцессор 3 выставляет на шине 4 устройства код адреса, у которого разряд АВ14 установлен в единицу (это необходимо для того, чтобы память 12 команд в это время была в режиме.Не выбрано), и разряд АВ10 также установлен в еди ницу. В этом случае на выходе перв го элемента И-НЕ 13 установлен нулевой потенциал, который, поступая на вход выборки, устанавливает память 14 данных в режим Выбрано. Микропроцессор 3 выставляет на ши156ну 6 данных информацию, подлежащую записи в память 12 команд, которая через системньй контролер 7. поступает на информационную шину 8 устройства и по сигналу Запись в память, поступающему с соответствующего выхода системного контролера 7 на вход Разрешение записи памяти 14 данных, записывается в ячейку памяти 14 данных, определяемую кодовой комбинацией на адресной шине 4 устройства. Таймер 17 предназначен для отсчета временных интервалов, необходимых для предотвращения многократного срабатывания устройства от одного нажатия на клавишу. Обмен информацией между микропроцессором 3 и программируемым таймером 17 осуществляется через системный контролер 7 по информационной шине 8 устройства под воздействием сигналов, поступающих на входы Чтение и Запись таймера 17 соответственно с выходов Чтение памяти и Запись в память системного контролера 7. При этом разрядами АВ8 и АВ9 адресной шины 4 устройства опреде- ляется внутренний регистр, участвующий в обмене информацией, а разряды АВ14 и АВ11 должны быть устанбвлены в единицу, так как только в этом случае на выходе второго элемента И-НЕ 15 будет установлен нулевой потенциал, который, поступая на вход выборки таймера 17, устанавливает последний в режим Выбрано. Тактирование таймера 17 осуществляется по входу синхронизации (С) синхроимпульсами фазы Ф2 с уровнем ТТЛ-схем, поступающим с второго выхода генератора 1 синхроимпульсов. Обмен.информацией с периферийным оборудованием осуществляется по информационной шине 8 устройства под управлением сигнала 20 Запись, появляющегося на -выходе первого элемента НЕ 18 при записи информации из микропроцессора 3 через системный контролер 7 по информационной шине 8 устройства в периферийное оборудование, а также под управлением сигналов на адресном выходе 19 устройства, являющихся выходными сигналами буферной адресной памяти 16, входы которого подключены к адресной шине 4 устройства. Особенность ра7 . . боты буферной адресной памяти 16 заключается в том, что когда происходит обмен лнформацией между микропроцессором 3 и одним из внут ренних блоков устройства (памйть 1 команд, память 14 данных или таймер 17), на выходах устанавливаются нулевые потенциалы. При этом ни одно из периферийньи устройств к и формационной шине 8 .устройства не подключается. Это достигается тем, что при установке нулевого потенци .ла в разряде АВ1Л или единичного потенциала хотя бы на одном из разрядов АВ10 и АВ 11шины 4 адреса устройства элемент ИЛИ 9, второй элемент НЕ 10 и элемент ИЛИ-НЕ 11, включенные соответствующим образом, вырабатывают на выходе элемента ИЛИ-НЕ 11 сигнал нулевого потенциала, который поступает на установочный вход буферной адресно памяти 16 и устанавливает на ее выходах сигналы нулевого потенциала, Устройство управления устанавливает на своем адресном выходе 19 адресную комбинацию, достаточную для адресации к конкретному пе риферийному устройству. На информационной, шине 8 устройства устанавливается кодовая комбинация, ко торая в приведенном на фиг. 3 устройстве должна быть записана в буферном регистре 22 клавиатуры, а наадресном выходе 19 устройства устанавливается кодовая комбинация при которой в разрядах, например, АО и А1- установлены единичные поте циалы. . При этом на выходе третьего эле мента И-НЕ 23 устанавливается нуле вой потенциал, который поступает на вход выбора режима буферного регистра 22 клавиатуры и устанав- .ливает последний в режим записи. С появлением управляющего сигна ла на выходе 20 Запись устройств поступающего на вход синхронизации буфера клавиатуры, последний записывает информацию с информационной -Ши.ны 8. устройства в свой внут- ренний регистр. Затем устройство обновляет адресную комбинацию на своем адресном выходе 19, например устанавливает разряды АО в ноль а А1 в единицу. 15.8 При этом на выходе третьего элемента НЕ 24 устанавливается единичный потенциал, который совместно с разрядом А1. поступает на входы четвертого элемента И-НЕ 25 и уста-. навливает на его выходе нулевой потенциал, который-, в свою очередь, поступает на вход выбора кристалла буферной памяти 26 клавиатуры и подключает ее выходы к шине данных. Устройство считывает информацию о состоянии клавиш 27.1...27N. В устройстве организовано одноуровневое прерывание, при построеНИИ которого решалась задача минимизации входных и выходных сигналов, связывающих устройство с периферийным оборудованием, а также минимизация аппаратурных затрат. Механизм прерывания функционирует следующим образом (рассмотрим на примере устройства, приведенного на фиг. 3). При нажатии хотя бы одной клавиши один из входов многовходового элемента И-НЕ 28 будет подключен к одному из входов буферного регйстг ра 22, так как в исходном состояНИИ на выходах буферного регистра 22 установлены нулевые потенциалы, на выходе многовходового элемента и И-НЕ 28 - единичный, который через четвертый элемент НЕ 29 с открытым коллектором поступает на вход 21 Запрос прерывания. К этому же входу По схеме монтажного ИЛИ подключаются выходы всех запрашивающих обслуживание устройств. Микропро-, цессор 3, получив от периферийного оборудования запрос на применение, переходит в режим прерывания.. При . этом он вьщает на шину 6 данных Слово состояния, которое записывается в системный контролер 7, на выходе Подтверждение прерывания которого устанавливается единичный потенциал. Однако схема системного контролера имеет ту особенность, что когда на его выходе Подтвержде.. ние прерывания устанавливается единичный пот.енциал и на этот вывод через ограничивающий резистор подается напряжение +12В, выходы, связанные с шиной 6 данных, переходят в состояние с большим полным сопротивлением, в результате чего микропроцессор воспринимает безадресную комаиду, т.е. управление передается ячейке памяти 12 команд. Таким образом, управляющий контролер переходит к определению, какое именно устройство запросило прерывание. С этой целью на ад- . рееном выходе 19 устанавливается кодовая комбинация, при которой, например, в разряде А7 устанавливается единица. Этот сигнал поступает на управляющий вход элемента НЕ 30 с тремя устойчивыми состояниями по выходу. Сигнал с выхода мн говходового элемента И-НЕ 28 инвертируется в нуль и поступает, например, на линию ДМ информационной шины 8 устройства. На другие линии информационной шины 8 устройства по тупают сигналы, подтверждающие запр от другого периферийного оборудования.. Информация с информационной шины 8 устройства считывается контролером. Приоритет запросов прерывани .определяется программным путем. В устройстве микропроцессор 3 и контролер 7 выполнены на серийно выпускаемых интегральных схемах К580ВМ80 и К580ВК2 соответственно. Программируемый таймер 17 является также серийно выпускаемой схемой, К580ВН53. Буферный регистр 16 представляет собой серийно выпускаемую микросхему К589ИР12. Алгоритм программной части работы устройства с клавиатурой представлен на фиг. 4. Алгоритм функционирует следующим образом. 1.При нажатии клавиш клавиатуры микропроцессор переходит к безадресной команде. 2.Роль стека в микропроцессорных системах обычно вьшолняет область ОЗУ, выделенная под стек. Запись содержимого регистров и флаж ков в стек, необходимо проводить для того, чтобы после окончания обработ ки прерывания при возврате к прерванной программе не потерять,информацию. 3.В приведенном в описании примере - это адрес, содержащий в разряде А7 единицу. А. Наибольшая часть определения источника запроса прерывания производится путем поразрядного анализа состояния шины данных. 5.В приведенном в описании примере информация о запросе прерывания клавиатурой выдается на разряд В1 в виде логического нуля. 6.В исходный момент в буферном регистре клавиатуры записаны все нули. В первом регистре микропроцессора устанавливается код, в котором ноль присутствует только в одном разряде (в приведенном примере в Младшем). 7.Второй регистр обнуляется для того, чтобы в нем организовать счет числа опрошенных строк клавиш клавиатуры (число перемещений нуля в первом регистре). 9, 10, 11. Если ни одна из клавиш в строке не нажата, то с буфера клавиатуры будут считаны все единицы. Исходя из специфики системы команд микропроцессора К580ВМ80 информация инвертируется. 11.Если содержимое третьего рет гистра равно нулю, то клавиши в строке не нажаты. 12.Сдвигается ноль в первом регистре. 13. В счетчике сдвигов во втором регистре содержимое увеличивается на единицу. 14. Анализируется, прошло ли число сдвигов, равное числу строк, если да то в 15 и 16 осуществляется возврат к прерванной программе, если нет, т.о цикл повторяется, начиная с метки Ml. 18.Если в строке кнопка нажата, то путем поразрядного анализа осуществляется поиск единицы в разрядах третьего регистра, при этом число шагов поиска подсчитывается в четвертом регистре и является информацией о столбце, в . котором нажата клавиша. 19.На основании информации во втором и четвертом регистрах получим координаты нажатой кнопки (номер строки и яомер столбца). 20.Из ОЗУ считывается информация о предаиущих состояниях нажатой клавиши в пятый регистр. 21.Информация обновляется и в 22 возвращается в соответствующую ячейку ОЗУ. 23. Если нажата, например, клавиша Диапазон, то устройство производит переключение диапазона работы прибора.

11 . 11676152

24, 25, 26, 27. Запускается тай-i срабатывания устройства от одного мер, который отсчитьгаает защитный нажатия. По окончании защитного интервал времениj необходимыйинтервала времени контролер возврадля предотвращения многократного щается к прерванной программе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1418727A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1474635A1 |

| МНОГОПРОЦЕССОРНАЯ СИСТЕМА ДЛЯ КОММУТАЦИИ КАНАЛОВ | 1992 |

|

RU2069891C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство контроля и управления технологическим комплексом для намотки изделий | 1989 |

|

SU1661721A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| Устройство обработки информации | 1989 |

|

SU1810892A1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ МЕВДУ ПРОЦЕССОРОМ И ПЕРИФЕРИЙ- . НЫМИ УСТРОЙСТВАМИ, содержащее генератор синхроимпульсов, память команд, адресньй выход процессора соединён с адресным входом памяти команд, информационные выходы которой соединены с информационной шиной процессора, первый выход генератора синхроимпульсов соединен с входом синхронизации процессора, о тличающее ся тем,, что, с целью упрощения устройства за счет сокращения линий связи, введены память данных,таймер,буферный регистр, элемент ИЛИ,два элемента НЕ,элемент , два элемента И-НЕ, причем выход буферного регистра является адресным выходом устройства, информационные входы - выходы памяти данных и таймера соединены с информационной шиной процессора, выход первого элемента НЕ является выходом записи устройства, вход первого элемента НЕ соединен с входом записи таймера, входом разрешения записи памяти данных и с выходом управления записью процессора, выход управления чтением которого соединен с входом чтения таймера, адресные входы которого соединены с соответствующими разрядами адресной шины процессора, адресные входы буферного регистра и памяти данных соединены с адресной шиной процессора, вход выборки памяти данных соединен с выходом первого элемента И-НЕ, первый вход которого сое(Л динен с первым входом элемента ИЛИ и с соответствующим разрядом адресной шины процессора, другой разряд адресной шины которого соединен с вторым входом элемента ИЛИ и с первым входом второго элемента И-НЕ, второй вход которого, второй вход первого элемента И-НЕ, вход выборки памяти команд и вход Э5 второго элемента НЕ соединены с соответствующим разрядом адресной Oi шины процессора, первый и второй входы элемента ИЛИ-НЕ соединены с СП выходами элементов НЕ и ИЛИ соответственно, а выход - с установочными входами буферного регистра, вы ход второго элемента И-НЕ соединен с входом выборки таймера, синхровход которого соединен с вторым выходом генератора синхроимпульсов.

t

/ Х У

ftfK

-

Cpus.2

JpedycmoHO$KO

i

Оператором начато одна из клавиш кладиатиры и

I пикропроцессор(мп)восприiНив запрос HCf npm/SoMue §ь1полняет безадресную команду

Продолжение анализа

т-

IB

Vr

мг До

15

17

Ф(1г.

ш

XZ

23

ш

7«

К

у, МЗ

ПереходкМ2

Фиё.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Управляющий компьютер | 1974 |

|

SU772501A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1983-10-19—Подача