Изобретение относится к вычислительной технике и может использоваться как системное устройство для связи цифровых вычислительных машин в многомашинных вычислительных комплексах.

Целью изобретения является расширение функциональных возможностей путем обеспечения возможности осуществлять передачу информации по нескольким адресам.

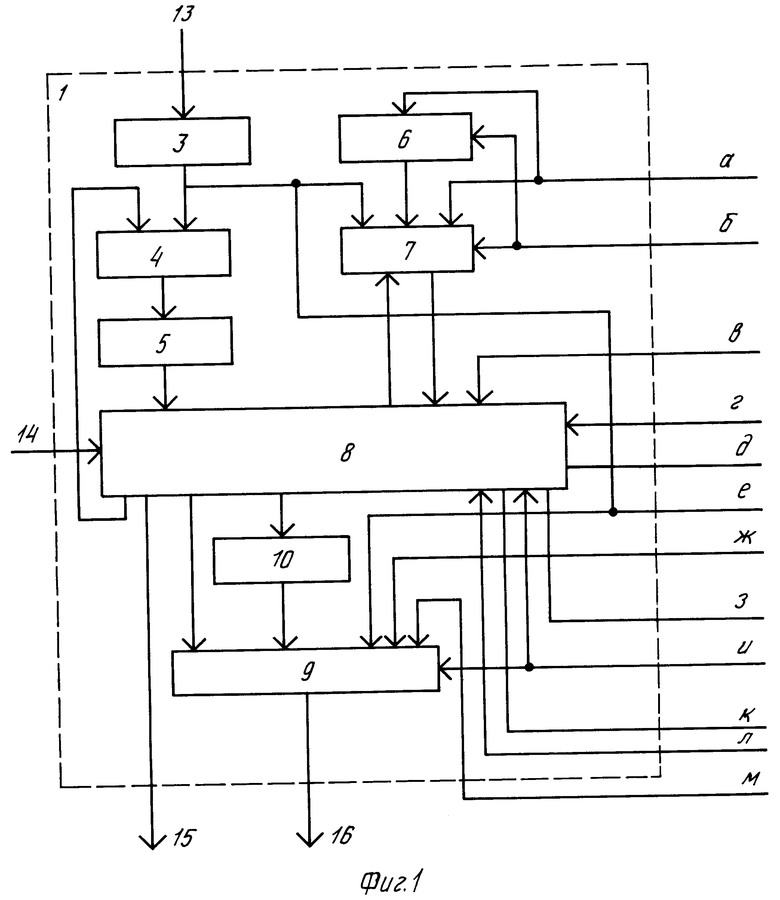

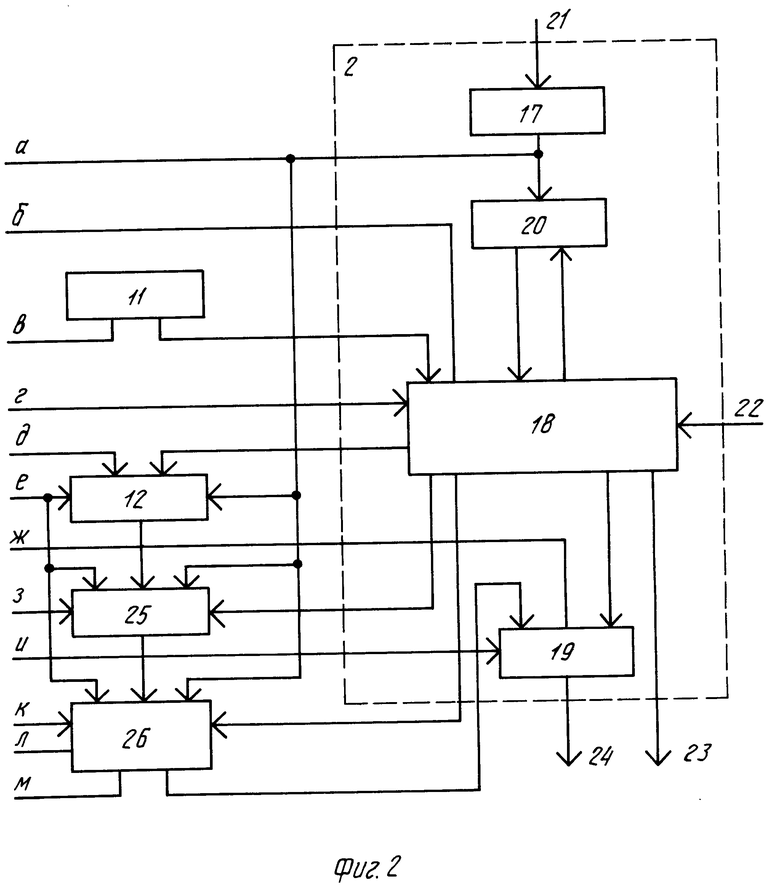

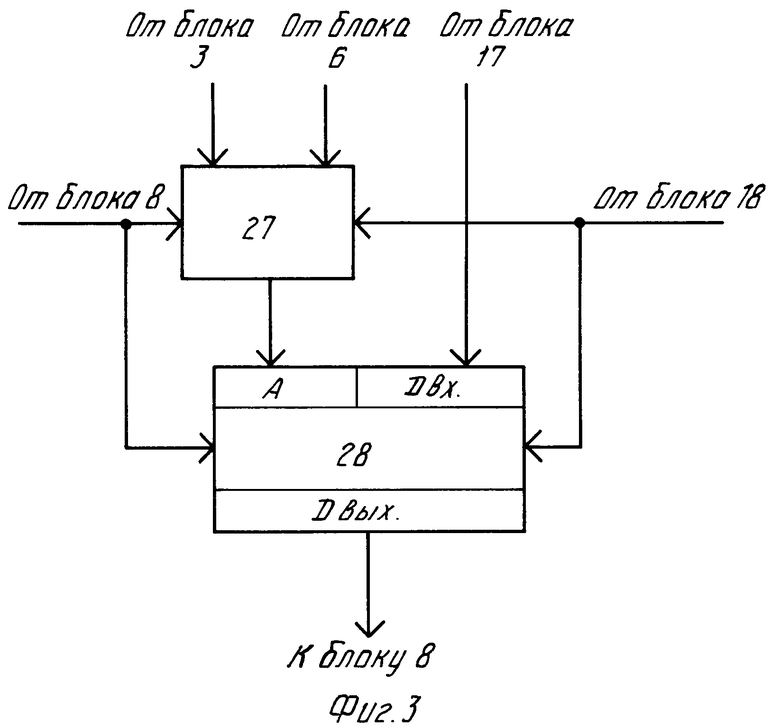

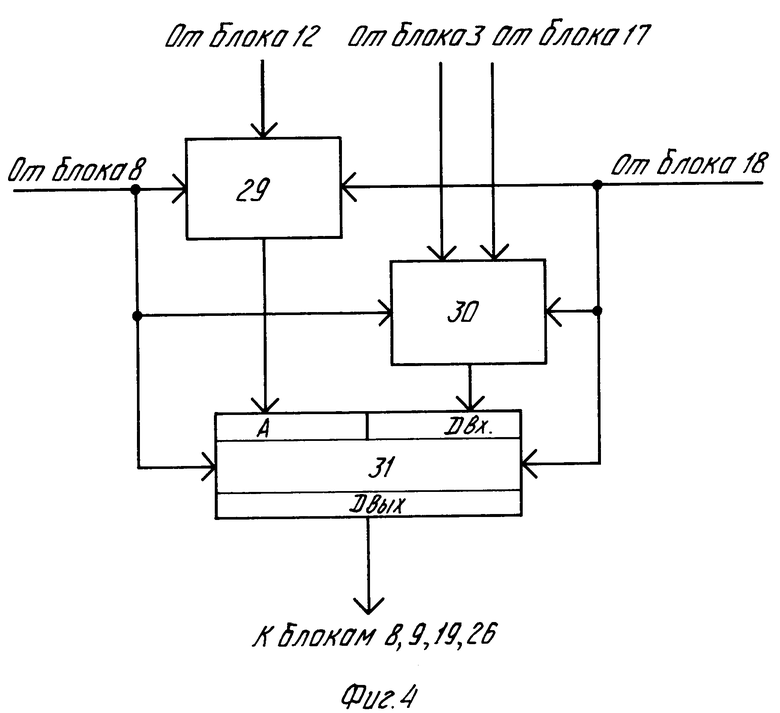

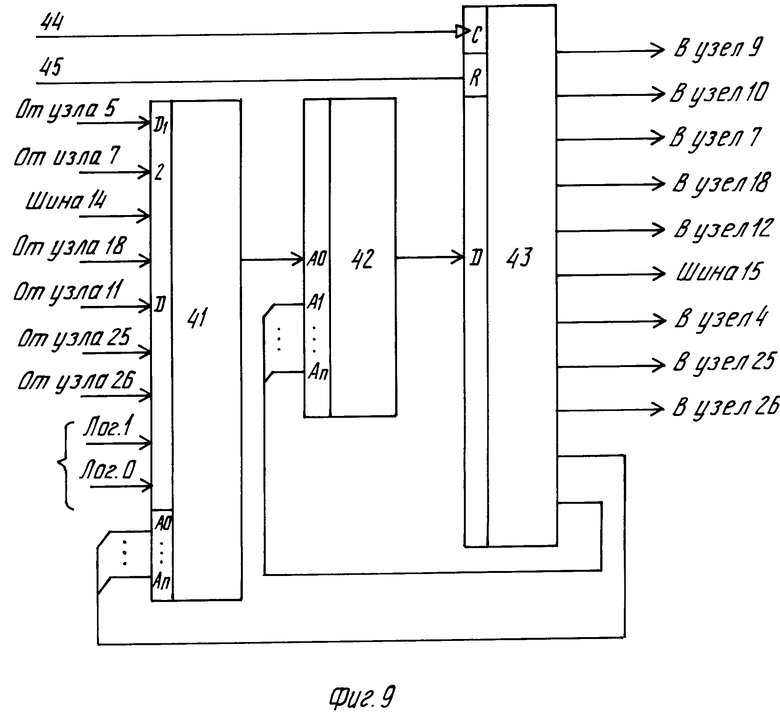

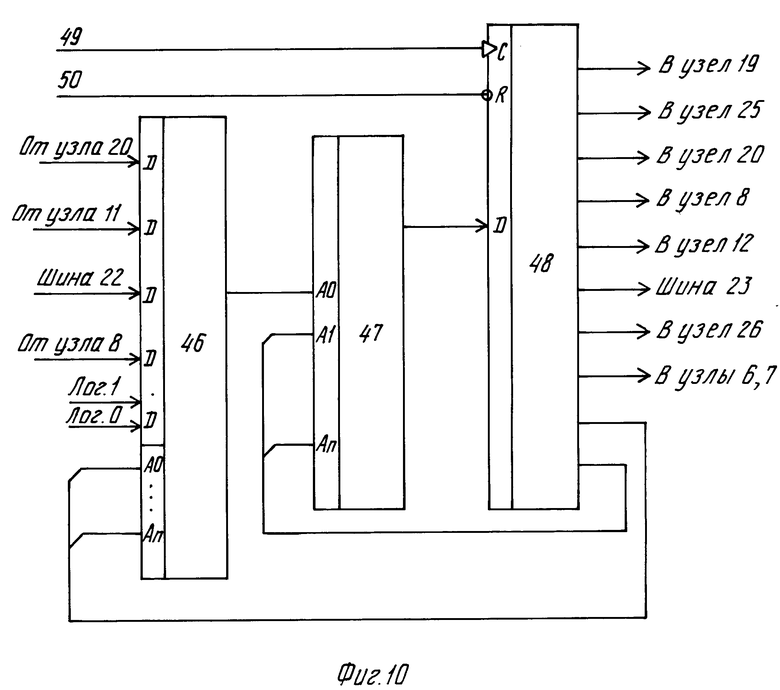

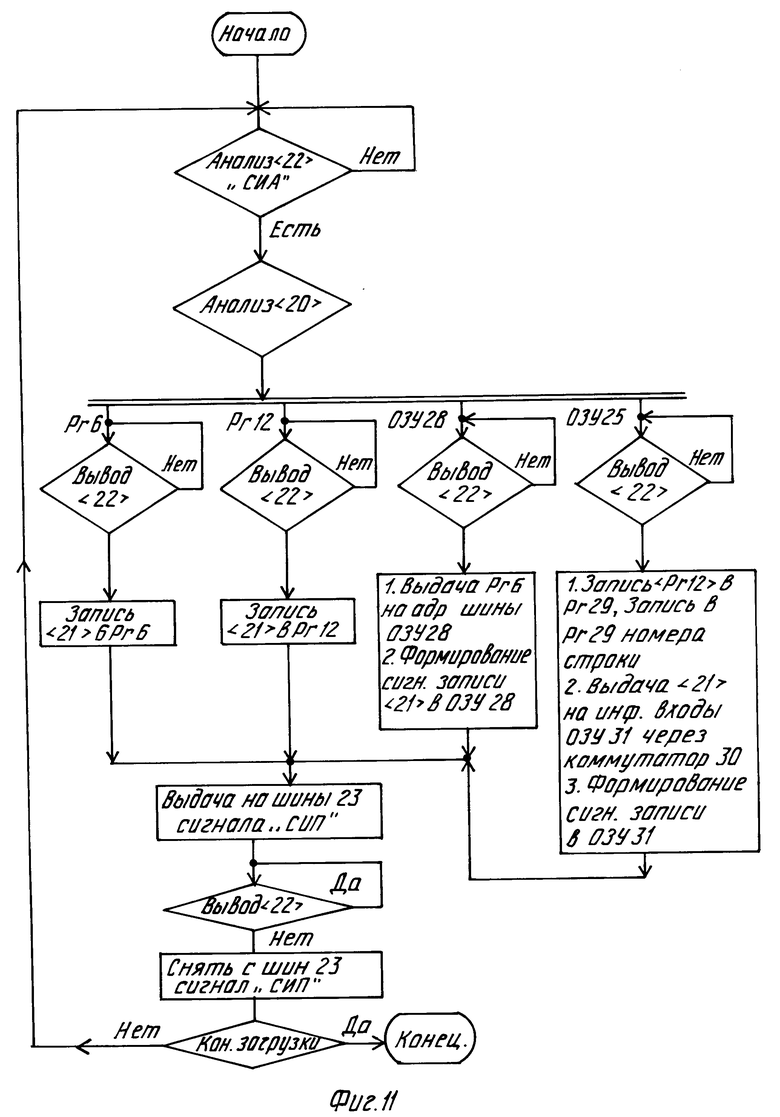

На фиг. 1 и 2 показана функциональная схема адаптера; на фиг. 3 - узла памяти кодов совпадения адресов; на фиг. 4 - ОЗУ состояний внешнего устройства; на фиг. 5 - буферной памяти; на фиг. 6, 7 и 8 - граф-алгоритмы узлов микропрограммного управления; на фиг. 9 и 10 - узлы микропрограммного управления; на фиг. 11 - алгоритм работы.

Адаптер канал-канал содержит два блока 1 и 2 связи с каналом, первый из которых состоит из узла 3 согласования входных сигналов, регистра 4 команд, дешифратора 5 команд, регистра 6 адреса, узла 7 памяти кодов совпадения адресов, узла 8 микропрограммного управления, узла 9 согласования выходных сигналов, регистра 10 байта состояния, а также блок 11 задания режима, буферный регистр 12, информационные 13 и управляющие 14 линии канала, управляющие 15 и информационные 16 линии абонента. Второй блок связи с каналом содержит узел 17 согласования входных сигналов, узел 18 микропрограммного управления, узел 19 согласования выходных сигналов, дешифратор 20 адреса, информационные входные шины 21, управляющие входы 22 и выходные шины 23 и 24. Кроме того, адаптер имеет ОЗУ 25 состояний внешнего устройства (ВУ) и буферную память 26.

Узел 7 памяти кодов совпадения адресов (фиг. 3) содержит коммутатор 27 адреса, ОЗУ 28 адресов.

ОЗУ 25 состояний ВУ (фиг. 4) содержит адресный регистр 29, коммутатор 30 информации, ОЗУ 31.

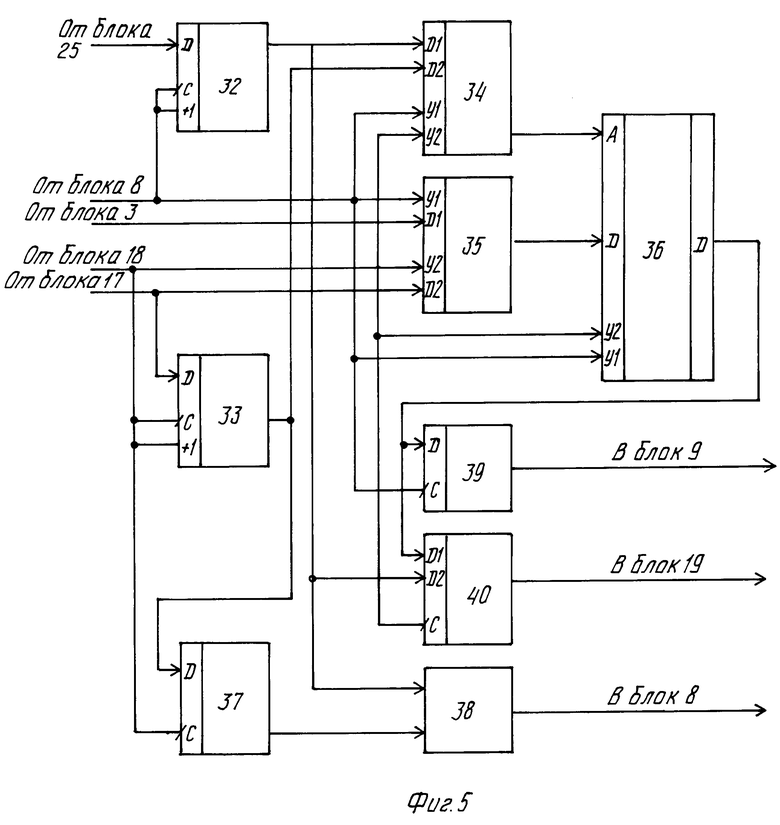

Буферная память 26 (фиг. 5) содержит счетчики 32, 33 адреса, коммутатор 34 адреса, коммутатор 35 информации, память 36, регистр 37 длины массива, схему 38 сравнения и выходные регистры 39, 40.

Узлы 8 и 18 реализованы в виде микропрограммных автоматов. Узел 8 (фиг. 9) включает в себя мультиплексор 41, постоянную память 42, выходной регистр 43, шину 44 сигналов синхронизации, шину 45 начальной установки. Аналогична структура узла 18 (фиг. 10). Мультиплексор 41 (46) предназначен для реализации условных переходов. Постоянная память 42 (47) служит для хранения набора микрокоманд. Выходной регистр 43 (48) предназначен для устранения разброса времени выборки различных адресных разрядов постоянной памяти.

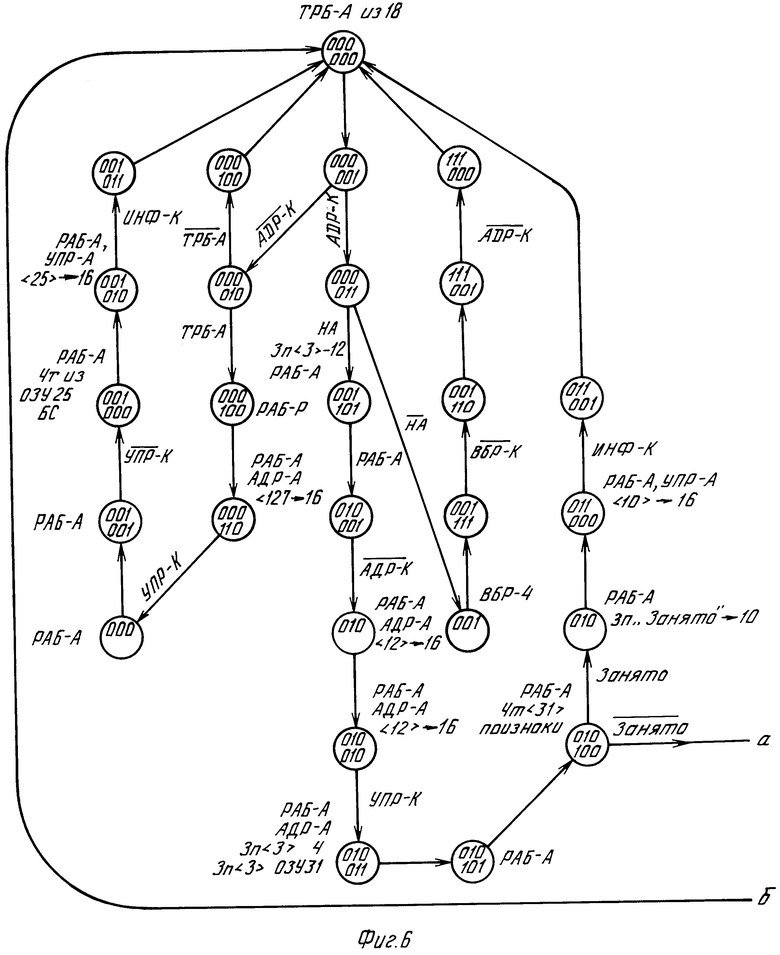

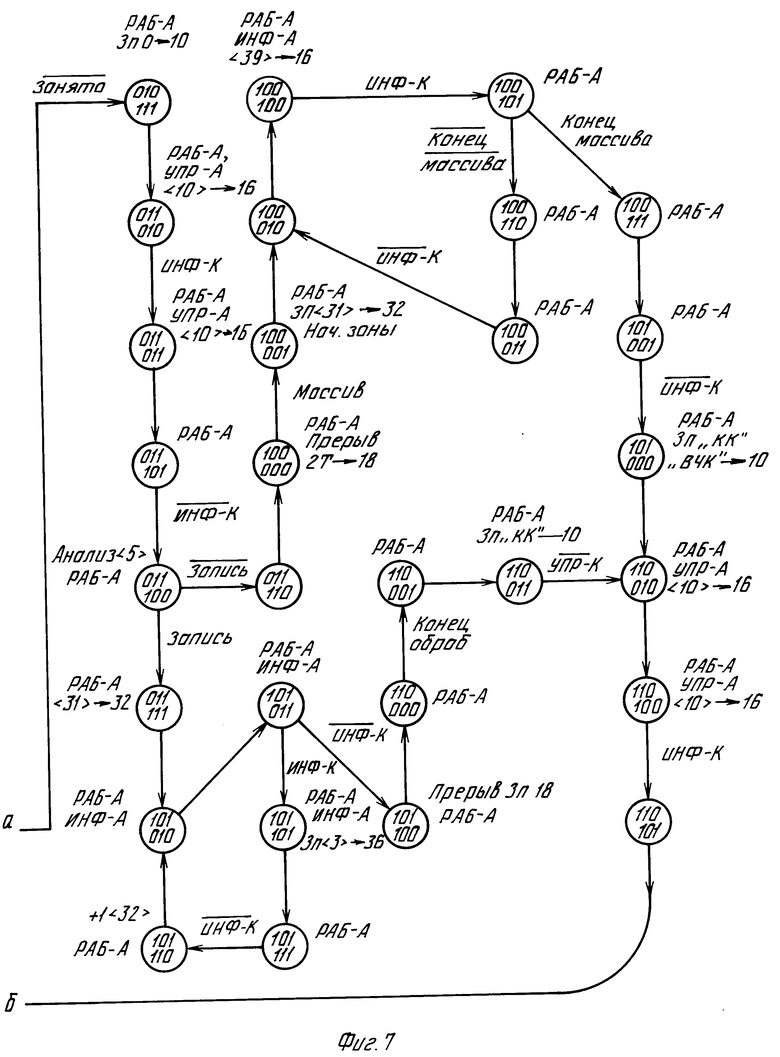

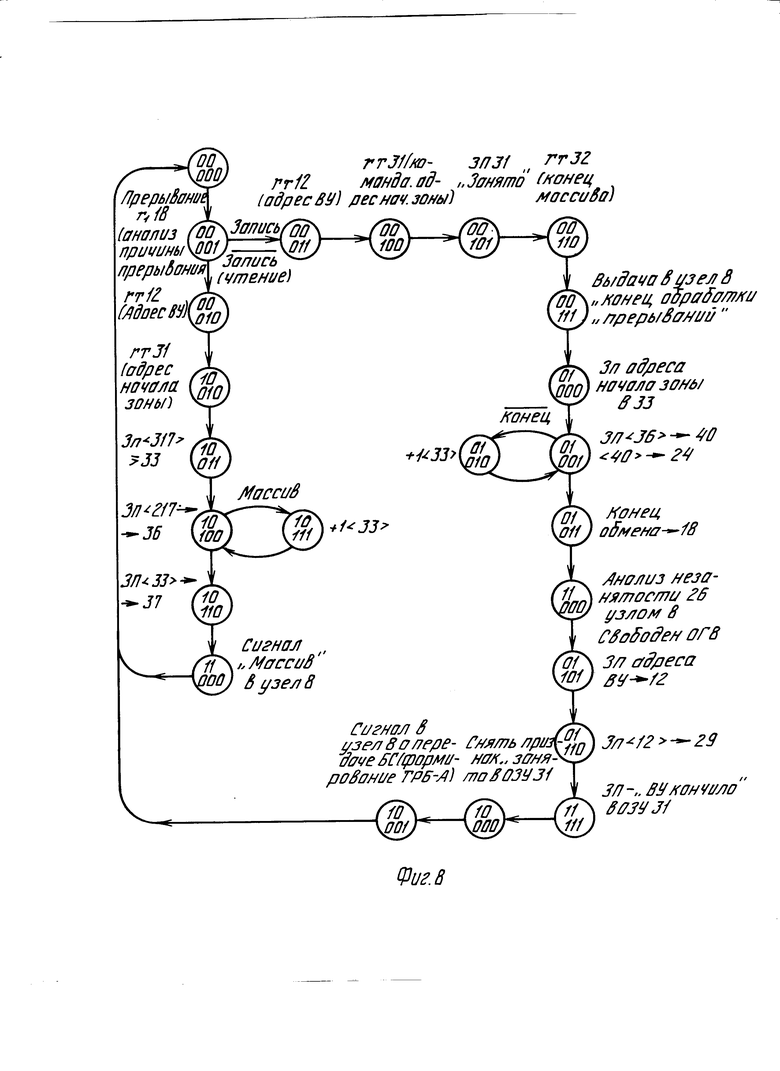

На графах алгоритма (фиг. 6, 7, 8) в кружках изображен адрес ячейки постоянной памяти, в которой хранится микрокоманда, дугами изображены переходы из одного состояния в другое. Названия сигналов над кружками означают, что сигналы формируются в этих состояниях, названия сигналов над дугами означают, что переход из одного состояния (начало дуги) в другое (стрелка дуги) происходит при наличии этого сигнала.

Узел микропрограммного управления работает следующим образом.

В исходном состоянии регистры 43 (48) обнулены и на адресных входах постоянной памяти 42 (47) присутствует нулевой адрес. После сброса сигнала начальной установки по каждому сигналу синхронизации производится анализ сигналов условий, поступающих на входы мультиплексора 41 (46), и переход в очередное состояние. В каждом состоянии узла управления на адресный вход постоянной памяти 42 (47) подключается одна из входных шин узла. Выбор подключаемой шины производится в поле формата микрокоманды. Возможный формат микрокоманды имеет вид АМК - поле адреса следующей микрокоманды, АМХ - поле хода адреса подключаемого входа мультиплексора, УПР - поле выходных сигналов устройства управления.

Если на входной шине присутствует входной сигнал (т.е. логическая "1"), то узел управления переходит в состояние, в младшем разряде которого присутствует единица, если на выбранной шине отсутствует входной сигнал (т.е. присутствует логический "0"), то автомат переходит в состояние, в младшем разряде которого присутствует ноль. Например, пусть поле адресов постоянной памяти (АМК) представляет комбинацию 0011, поле адреса входного мультиплексора (АМХ) - 0101. Если на пятом входе мультиплексора присутствует входной сигнал (т. е. логическая "1"), то переход осуществляется по адресу 00111, если отсутствует - по адресу 00110.

Для формирования выходных сигналов устройства управления используется горизонтальное микропрограммирование, т. е. каждому разряду поля выходных сигналов микрокоманды ставится в соответствие определенный выходной сигнал устройства управления.

Работает адаптер канал-канал следующим образом.

Перед началом работы ЭВМ, подсоединенная к второму блоку связи с каналом (ЭВМ2), производит загрузку исходных данных в узел сравнения адресов и в ОЗУ состояний ВУ. Исходные данные это список адресов ВУ, с которыми может работать канал ввода-вывода ЭВМ, подсоединенной к первому блоку связи с каналом (ЭВМ1), и распределение буферной памяти адаптера канал-канал между разрешенными ВУ. Распределение буферной памяти производится путем загрузки в ОЗУ состояний ВУ адресов начало зон, выделенных для каждого адреса ВУ.

Загрузка списка адресов ВУ производится следующим образом. ЭВМ2 посылает на информационные шины 21 адрес, соответствующий адресу регистра 6 адреса для ЭВМ2, сопровождая его на управляющих шинах 22 сигналом синхронизации СИА.

Узел 18 управления анализирует сигналы на выходе дешифратора 20 адреса и при появлении на управляющих шинах 22 сигнала "Вывод" формирует сигнал записи информации с шин 21 в регистр 6 адреса. На шинах 21 в это время находится адрес ВУ из списка адресов ВУ. Затем ЭВМ2 выставляет на информационные шины 21 адрес ОЗУ адресов, при появлении сигнала СИА на шинах 22 узел 18 управления анализирует этот адрес на выходе дешифратора 20 адреса и при появлении сигнала "Вывод" формирует сигналы записи информации с шин 21 в ячейку ОЗУ адресов, адрес которой соответствует адресу ВУ, записанному в регистре 6 адреса. На информационные шины 21 ЭВМ2 при этом выдает признак соответствия адреса ВУ списку (признак расположен в одном определенном разряде информационных шин, например в нулевом разряде). Таким образом, во все восьмибитные ячейки ОЗУ адресов, адреса которых соответствуют адресам ВУ из списка, в определенный разряд памяти ОЗУ адресов записывается единица. В ячейки, адреса которых не соответствуют адресам ВУ из списка, в этот разряд записывается ноль.

При загрузке распределения буферной памяти между ВУ ЭВМ2 организовывает запись во вторую строку ОЗУ по адресу, соответствующему адресу ВУ, значение адреса начала зоны, выделенной в буферной памяти для данного ВУ.

Алгоритм загрузки исходных данных ЭВМ2 приведен на фиг. 11.

После загрузки исходных данных адаптер канал-канал готов к работе под управлением ЭВМ1 и ЭВМ2.

Канал ЭВМ1, начиная последовательность начальной выборки ВУ, выдает на шины 13 адрес ВУ, сопровождая его сигналами АДР К, ВБР К, РВБ К на шинах 14. Адрес ВУ с выхода узла 3 поступает на первый информационный вход коммутатора 27 адреса узла 7 памяти кодов совпадения адресов. С выхода коммутатора 27 адрес ВУ поступает на адресные входы ОЗУ 28 адресов, под управлением узла 8 производится считывание признака принадлежности адреса ВУ к списку адресов. С информационных выходов ОЗУ 28 адресов значение этого признака поступает в узел 8 управления. Узел управления формирует сигнал записи адреса ВУ с выхода узла 3 в буферный регистр 12. Узел 8 управления формирует сигнал РАБ А по шине 15, который поступает в канал ввода-вывода ЭВМ1. Канал ввода-вывода ЭВМ1 снимает с шин 13 адрес ВУ, а с шины 14 - сигнал АДР К. Содеpжимое буферного регистра 12 (адрес ВУ) через узел 9 согласования выходных сигналов поступает на шину 16, на шине 15 узла 8 управления формирует сигнал АДР А.

Канал ЭВМ1 выдает на шину 13 код операции, сопровождая его на шине 14 сигналом УПР К. Узел 8 управления организует запись кода операции в регистр 4 команд, в нулевую строку ячейки ОЗУ 31, адрес которой соответствует адресу ВУ из буферного регистра 12, - кода операции с выхода узла 3 согласования выходных сигналов. Содержимое регистра 4 команд поступает на вход дешифратора 5 команд. С выхода последнего код типа заданной программой ЭВМ1 операции ввода-вывода ("Запись", "Чтение", "Управление" и т.д.) поступает на вход узла 8 управления. Узел 8 управления снимает с информационных шин 16 адрес ВУ, с шин 15 - сигнал АДР А. Канал ввода-вывода ЭВМ1 снимает сигнал УПР К с шин 14 и код операции с шин 13.

Рассмотрим работу адаптера канал-канал при приеме команды "запись". Узел 8 управления организует считывание из третьей строки ОЗУ состояний ВУ по адресу ВУ признака "занято" (адрес ВУ хранится в буферном регистре 12). Значение этого признака поступает на шестой вход узла 8 управления. Если признак "занято" для данного ВУ отсутствует, то узел управления формирует запись в регистр 10 нулевого байта состояния, который через узел 9 выдается на информационные шины 16, сопровождаемый на шинах 15 сигналом УПР А.

Канал ЭВМ1 подтверждает прием от адаптера канал-канал байта состояния, выдавая на шины 14 сигнал ИНФ К. Узел 8 снимает байт состояния с шин 16 байт состояния, с шин 15 - сигнал УПР А. Канал ЭВМ1 снимает с шин 14 сигнал ИНФ К. Узел 8 управления организует считывание по адресу ВУ из буферного регистра 12 из второй строки ОЗУ 25 состояний ВУ адреса канала зоны, выделенной в буферной памяти 26 для данного ВУ. Этот адрес с выхода ОЗУ 31 записывается в счетчик 32 адреса буферной памяти. Затем узел 8 управления выставляет на шины 15 сигнал запроса на байт информации в ЭВМ1 ИНФ А. Канал ЭВМ1 выдает на шины 13 байт информации, сопровождая его сигналом ИНФ К на шине 14. Узел 8 управления организует запись этого байта с выхода узла 3 согласования входных сигналов в память 36 по адресу начала зоны и снимает сигнал ИНФ А с шин 15. Канал ЭВМ1 снимает с шин 13 байт информации и сигнал ИНФ К с шин 14. Узел 8 управления модифицирует на +1 значение счетчика 32 адреса и выдает на шину 15 сигнал запроса ИНФ А. Канал ЭВМ1 выдает следующий байт информации на шины 13, который записывается в следующую ячейку буферной памяти. Обмен производится до тех пор, пока канал ЭВМ1 в ответ на сигнал запроса ИНФ А не выдаст на шину 14 сигнал УПР К.

Узел 8 управления, получив сигнал окончания УПР К, выдает сигнал окончания обмена в узел 18 управления второго блока связи с каналом и снимает сигнал ИНФ А с шины 15. Узел 18 управления, получив сигнал об окончании обмена, организует выдачу в ЭВМ2 сигнала прерывания по шине 23, на шину 19 выдает информацию о причине прерывания, ЭВМ2 выдает на шину 21 адрес буферного регистра, сопровождая его сигналом СИА на шине 22. Узел 18 управления анализирует выход дешифратора 20 адреса. При приеме на шине 22 сигнала "Ввод" от ЭВМ2 узел 18 управления организует передачу через узел 19 согласования выходных сигналов на шину 24 адреса ВУ из буферного регистра 12, сопровождая его сигналом СИП на шине 23. ЭВМ2 принимает адрес ВУ и снимает сигнал "Ввод" с шин 22. Узел 18 управления снимает сигнал СИП с шин 23 и адрес ВУ с шин 24, ЭВМ2 снимает сигнал СИА. Затем аналогично ЭВМ2 организует считывание из ОЗУ 25 состояний ВУ кода операций выполняемой команды (в одном случае "Запись") адреса начала зоны буфера.

В третью строку ОЗУ состояний ВУ по адресу данного ВУ ЭВМ2 записывает признак "занято". Затем ЭВМ2, обращаясь по адресу счетчика 32 адреса, организует считывание его значения (последний адрес ячейки памяти 36, куда была записана информация от ЭВМ1). Значение счетчика 32 адреса через выходной регистр 40 поступает на четвертый вход узла 19 согласования выходных сигналов, а затем на информационную шину 24 ЭВМ2.

ЭВМ2 после считывания всех необходимых данных, обращаясь по адресу узла 18 управления, сигнализирует об окончании обработки прерывания. Из узла 18 управления сигнал об окончании обработки прерывания поступает на четвертый вход-выход узла 8 управления первого блока связи с каналом.

Узлом 8 управления формируется байт состояния с указателем "Канал кончил", который записывается в регистр 10 байта состояния и через узел 9 согласования выходных сигналов поступает на информационную шину 16, сопровождаемый сигналом УПР А на шине 15. Канал ЭВМ1 пpинимает байт состояния, выдавая при этом на шину 14 сигнал ИНФ К. Узел 8 управления снимает с шин 16 байт состояния, а с шин 15 сигналы УПР А, РАБ А. Канал ЭВМ1 может вводить следующую команду из программы, начиная последовательность начальной выборки для другого адреса ВУ из списка разрешенных.

Если каналом ввода-вывода ЭВМ1 введена команда для того же ВУ, которому была введена, но не закончилась операция "запись", то после приема в последовательности начальной выборки кода команды узел 8 управления, считав из ОЗУ состояний признак "занято", формирует байт состояния с указателем "ВУ занято", команда к исполнению не принята. Если введена команда "запись" для другого ВУ, то выполнение ее происходит так как было рассмотрено выше.

ЭВМ2, получив все исходные данные об объеме переданной информации по команде "запись" (начальный адрес зоны и значение последнего адреса ячейки памяти 36, куда была записана информация, поступившая от ЭВМ1), адрес ВУ, организует считывание из буферной памяти информации, для чего в счетчик 33 адреса буферной памяти ЭВМ2 заносит адрес начала зоны буфера, затем, обращаясь к памяти 36, организует считывание информации из памяти 36, которая через выходной регистр 40 и узел 19 согласования выходных сигналов поступает на шину 24. После каждого обращения к памяти 36 значение счетчика 33 адреса увеличивается на +1. После считывания всего массива информации из буферной памяти в ЭВМ2 операция "запись" завершена. Для сигнализации ЭВМ1 об окончании заданной ранее операции ЭВМ2 выдает по адресу узла 18 управления сигнал об окончании операции, который передается на четвертый вход-выход узла 8 управления первого блока связи с каналом.

Если первый блок связи с каналом не занят выполнением операции ввода-вывода, то сигнал об этом поступает на четвертый вход-выход узла управления второго блока связи с каналом. Через узел 19 он поступает в ЭВМ2. ЭВМ2, обращаясь по адресу буферного регистра 12, записывает адрес ВУ, по которому была завершена операция "запись". Затем под управлением узла 18 адрес ВУ из буферного регистра 12 переписывается в адресный регистр 29 ОЗУ 25 состояний ВУ. Обращаясь по адресу ОЗУ 31, ЭВМ2 записывает в первую строку байт состояния с указателем "ВУ кончило", в третьей строке снимает признак "занято". Затем узел 8 управления выдает на шины 15 сигнал требования на обслуживание ТРБ А. Канал ЭВМ1, получив сигнал ТРБ А, выдает на шины 14 сигнал ВБР К. Узел 8 управления выдает на шину 15 сигнал РАБ А, затем содержимое буферного регистра 12 через узел 9 выдается на шины 16, на шины 15 сопровождается сигналом АДР А. Канал ЭВМ1 подтверждает прием адреса, выставляя сигнал УПР К на шины 14. Узел 8 управления снимает сигнал АДР А с шин 15 и адрес ВУ с шины 16. После снятия каналом ЭВМ1 сигнала УПР К с шин 14 узел 8 управления организует считывание из первой строки ОЗУ состояний ВУ байта состояния с указателем "ВУ кончило".

Узел 9 согласования выходных сигналов выдает байт состояния на шину 16, сопровождая сигналом УПР А на шине 15. Канал ЭВМ1 принимает байт состояния, выдавая на шины 14 сигнал ИНФ К. Узел 8 управления снимает сигналы РАБ А, УПР А с шин 16, байт состояния с шины 16. Канал ЭВМ1 снимает сигнал ИНФ К, выполнение операции "запись" завершено.

Выполнение команды "чтение", заданной программой ЭВМ1, происходит следующим образом аналогично выполнению команды "запись". После приема каналом ЭВМ1 нулевого начального байта состояния узел 8 управления передает на четвертые входы-выходы узла 18 второго блока связи с каналом сигнал о необходимости передачи информации в ЭВМ1. Узел 18 управления формирует на шине 23 сигнал прерывания работы ЭВМ2. Обращаясь по адресу узла 18 управления ЭВМ2 получает на шине 24 информацию о причине прерывания. ЭВМ2, обращаясь по адресу буферного регистра 12, узнает адрес ВУ, которому была задана команда "чтение". Обращаясь к ОЗУ состояний ВУ, ЭВМ2 получает адрес начала зоны буфера, куда необходимо записать информацию. ЭВМ 2 формирует массив информации для передачи в ЭВМ 1. Затем, обращаясь по адресу счетчика 33 адреса буферной памяти, записывает в него адрес начала зоны, обращаясь по адресу памяти 36, записывает массив информации в буферную память. После каждого обращения к памяти 36 значение счетчика 33 адреса модифицируется на +1. После записи последнего байта информации в буферную память узел 18 управления организует запись значения последнего адреса (значение счетчика адреса 33) в регистр 37 длины массива. Затем узел 12 управления выдает на четвертый вход-выход узла 8 сигнал о готовности массива данных. Узел 8 управления считывает из ОЗУ состояний ВУ адрес начальной зоны, записывает его в счетчик 32 адреса буферной памяти, считывает первый байт информации из памяти 36, записывает его в выходной регистр 39, через узел 9 выдает на шины 16, сопровождая сигналом ИНФ А на шинах 15.

Канал ЭВМ1 подтверждает прием этого байта сигналом ИНФ К на шинах 14. Узел 8 управления снимает сигнал ИНФ А и байт информации с шин 16, после снятия сигнала ИНФ К модифицирует значение счетчика 32 адреса, организует считывание из памяти 36 очередного байта информации. Цикл повторяется до тех пор, пока значение счетчика 32 адреса не совпадет со значением регистра 37 длины массива, при этом сигнал с выхода схемы 38 сравнения поступает на седьмой вход узла 8 управления. Последний формирует байт состояния с указателями "Канал кончил", "ВУ кончило", который записывается в регистр 10 байта состояния, затем через узел 9 поступает на шину 16, сопровождаемый сигналом УПР А на шине 15. После приема каналом ЭВМ1 байта состояния узел 8 управления снимает его и сигналы РАБ А, УПР А с шин 15, 16. Выполнение команды "чтение" завершено.

Таким образом, адаптер позволяет производить обмен ЭВМ1 с несколькими ВУ, подключенными к ЭВМ2, кроме того, команды обмена для ВУ с различными адресами могут быть расположены в программе ЭВМ1 последовательно, и переход к выполнению следующей команды ЭВМ1 может осуществляться без ожидания результатов ее завершения ЭВМ2, что повышает производительность многомашинного комплекса, исключая простой ЭВМ1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Устройство для сопряжения двух ЦВМ | 1989 |

|

SU1624468A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Имитатор канала | 1988 |

|

SU1520523A2 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

Изобретение относится к вычислительной технике и может использоваться как системное устройство для связи ЦВМ в многомашинных вычислительных комплексах. Цель изобретения - расширение функциональных возможностей путем обеспечения возможности осуществлять передачу информации по нескольким адресам. Возможна работа ЭВМ 1 с различными ВУ, подсоединенными в ЭВМ 2, и наоборот, возможно включение в программу ЭВМ 1 последовательности операций обмена для различных адресов ВУ и выполнение этой последовательности независимо от ЭВМ 2. 1 з.п. ф-лы, 11 ил.

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-30—Публикация

1991-04-16—Подача