Изобретение относится к электросвязи и может быть использовано в системах передачи данных.

Известно устройство тактовой синхронизации, содержащее на передающей стороне триггер, три элемента И, элемент ИЛИ, передающий парафазный усилитель, формирователь последовательности импульсов, состоящий из двух триггеров и трех элементов И, счетчик тактов и на приемной стороне - приемный парафазный усилитель, два элемента И, счетчик импульсов кодовой последовательности, RS-триггер и блок задержки, а также соответствующие связи всех перечисленных элементов.

Недостатком этого устройства являются ограниченные функциональные возможности, что выражается в невозможности различать окончание блока (массива) слов. Этот недостаток обусловлен отсутствием в составе устройства узлов, обеспечивающих блочную синхронизацию.

Цель изобретения - расширение функциональных возможностей путем обеспечения блочной синхронизации.

Поставленная цель достигается тем, что в устройство тактовой синхронизации, содержащее на передающей стороне последовательно соединенные триггер, первый элемент И, элемент ИЛИ и передающий парафазный усилитель, выход которого соединен с входом канала связи, инверсный выход триггера через второй элемент И соединен с вторым входом элемента ИЛИ, первый и второй выходы формирователя последовательностей импульсов соединены с вторыми входами первого и второго элементов И, третий выход формирователя последовательностей импульсов соединен с вторым входом передающего парафазного усилителя через последовательно соединенные счетчик тактов и третий элемент И, другой вход которого соединен с третьим выходом формирователя последовательностей импульсов, вход которого является тактовым входом устройства, информационным входом которого является вход триггера, а на приемной стороне - последовательно соединенные приемный усилитель, блок задержки и четвертый элемент И, второй вход которого соединен с вторым выходом приемного усилителя, вход которого соединен с выходом канала связи, при этом первый выход приемного усилителя соединен с входом сброса счетчика импульсов кодовой последовательности и RS-триггера, установочный вход которого соединен с выходом четвертого элемента И, второй выход приемного усилителя соединен со счетным входом счетчика импульсов кодовой последовательности и с первым входом пятого элемента И, второй и третий входы которого соединены соответственно с выходом счетчика импульсов кодовой последовательности и с прямым выходом RS-триггера, причем выход блока задержки и выходы четвертого и пятого элементов И являются соответственно тактовым выходом, информационным выходом и выходом импульсов цикловой пословной синхронизации устройства, введен дополнительный элемент И, первый и второй входы которого соединены, соответственно, с первым и вторым входами пятого элемента И, а третий вход дополнительного элемента И и соединен с инверсным выходом RS-триггера, причем выход дополнительного элемента И является выходом импульсов блочной синхронизации устройства.

Введенный на приемной стороне дополнительный элемент И с его связями обеспечивает выделение признака блочной синхронизации, отличающегося от признака пословной синхронизации, что составляет положительный эффект.

Сущность изобретения состоит в разделении на приемной стороне признаков блочной синхронизации и пословной синхронизации по их отличиям, введенным при формировании на передающей стороне двух дополнительных тактов, передаваемых в конце каждого слова, причем в первом дополнительном такте передается полный символ логического "0" (в слове блочной синхронизации) или логической "1" (в остальных словах блока), а во втором дополнительном такте - символ логического "0" (в слове блочной синхронизации) или логической "1" (в остальных словах блока) без отрицательного тактового импульса, в результате чего по приему слова блочной синхронизации формируется на выходе устройства импульс блочной синхронизации, что обеспечивает установление синхронизации каждого передаваемого блока слов.

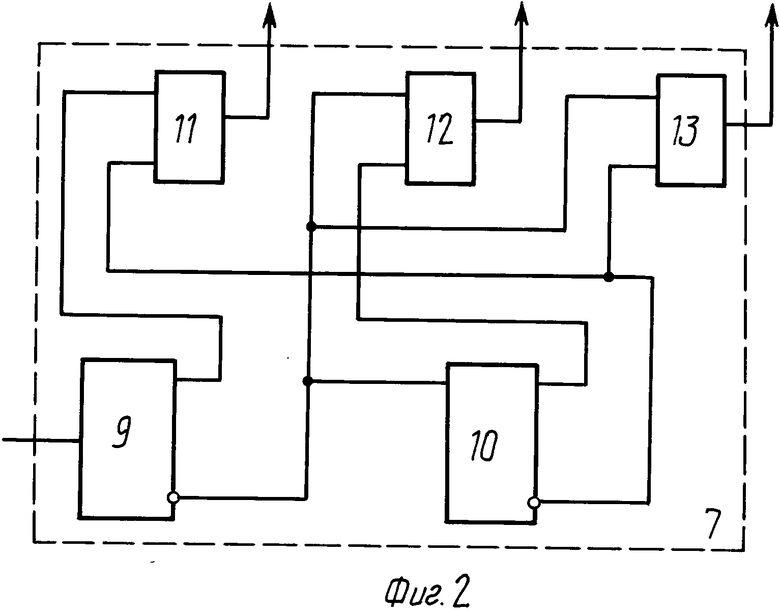

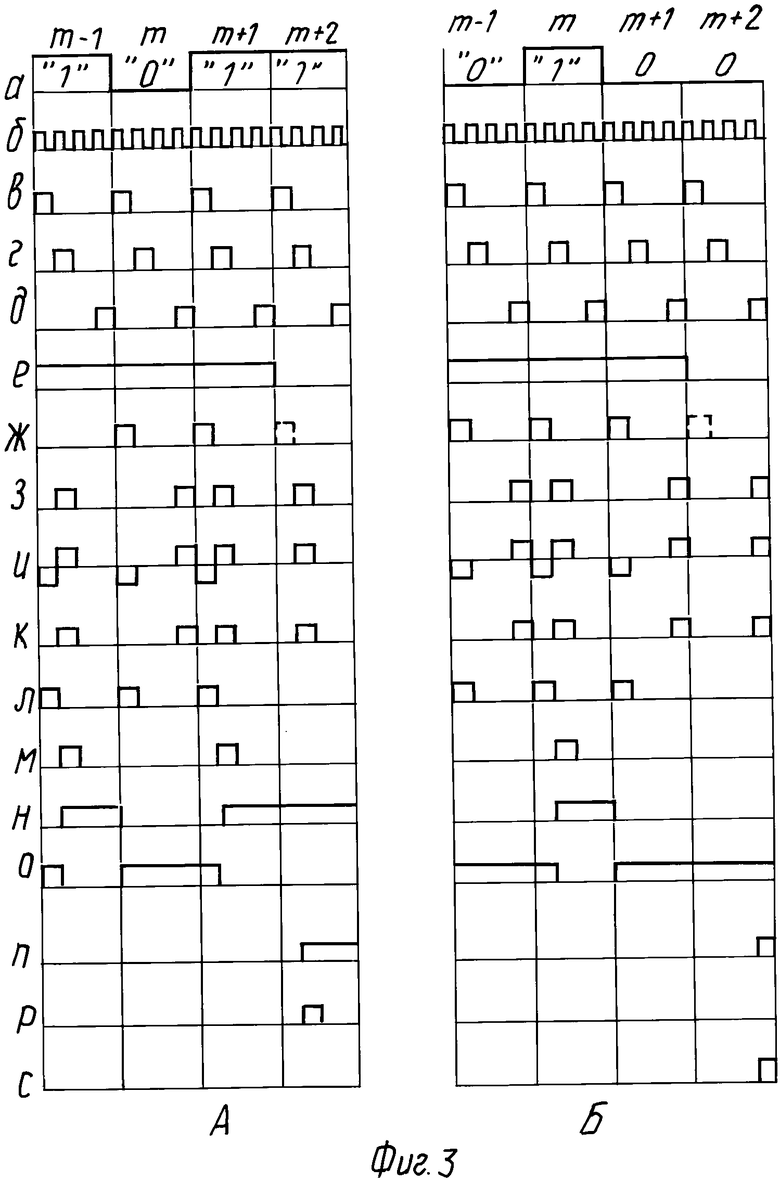

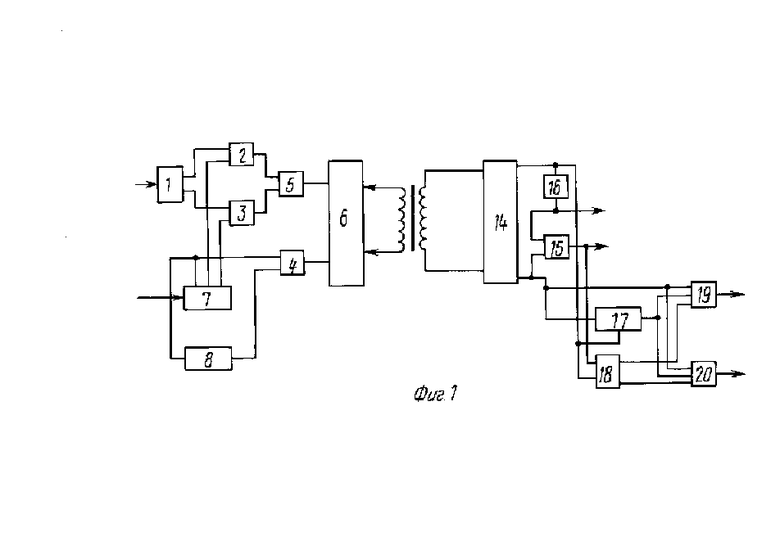

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема формирователя последовательности импульсов; на фиг. 3 - эпюры сигналов в различных точках устройства (фиг. 3Б - при формировании, передаче и приеме слова блочной синхронизации; на фиг. 3А - при формировании, передаче и приеме остальных слов группы).

Устройство тактовой синхронизации содержит на передающей стороне триггер 1, первый 2 и второй 3 и третий 4 элементы И, элемент ИЛИ 5, передающий парафазный усилитель 6, формирователь 7 последовательностей импульсов и счетчик 8 тактов, причем в состав формирователя 7 входят триггеры 9 и 10 и элементы И 11 - 13, а на приемной стороне - приемный парафазный усилитель 14, четвертый элемент И 15, блок 16 задержки, счетчик 17 импульсов кодовой последовательности, RS-триггер 18, пятый элемент И 19 и дополнительный элемент И 20.

На эпюрах - кодовая последовательность импульсов, б - импульсы опорной частоты, в - первая последовательность тактовых импульсов, г - вторая последовательность тактовых импульсов, д - третья последовательность тактовых импульсов, е - потенциал на втором входе элемента И 4, ж - последовательность импульсов на втором входе передающего парафазного усилителя 6, з - последовательность импульсов на первом входе передающего парафазного усилителя 6, и - последовательность двухполярных импульсов в линии, к - последовательность кодовых импульсов на втором выходе приемного парафазного усилителя 14, л - последовательность тактовых импульсов на первом выходе приемного парафазного усилителя 14, м - кодовая последовательность импульсов на выходе устройства, н - потенциал на прямом выходе RS-триггера 18, о - потенциал на инверсном выходе RS-триггера 18, п - потенциал на выходе счетчика 17 импульсов кодовой последовательности, р - импульс пословной синхронизации, с - импульс блочной синхронизации.

Предлагаемое устройство работает следующим образом.

На счетный вход триггера 1 поступает входная кодовая последовательность импульсов (эпюра а), а на вход формирователя 7 последовательностей импульсов поступают импульсы опорной частоты (эпюра б), период следования которых в четыре раза меньше периода выходных тактовых импульсов. При этом на выходах элементов И 11-13 лишь один раз в течение периода следования тактовых импульсов появляется импульсный сигнал, длительность которого равна длительности периода следования импульсов опорной частоты (эпюры в, г, д). При изменении логического состояния входной кодовой последовательности импульсов (эпюра а), например при переходе из "0" в "1", изменяется состояние триггера 1. Пусть, например, на первом входе элемента И 2 появляется "1", тогда элемент И 2 подготовлен для пропуска второй последовательности импульсов (эпюра г), поступающей с первого выхода формирователя 7 на второй вход элемента И 2. При изменении логического состояния входной кодовой последовательности импульсов, например, при переходе от "1" к "0", аналогично описанному работает элемент И 3, второй вход которого соединен с вторым выходом формирователя 7. С выходов элементов И 2 и 3 вторая или третья импульсная последовательности (эпюры г, д), поступает через элемент ИЛИ 5 на первый вход передающего парафазного усилителя 6 (эпюра з).

На счетный вход счетчика 8 тактов поступает первая последовательность импульсов (эпюра в). Выходы всех триггеров счетчика 8 тактов, количество которых (округленное до ближайшего большего целого числа) определяется по формуле k ≥ log2(m+2), где m - количество информационных двоичных разрядов в передаваемом слове, подсоединены к входам входящего в счетчик 8 тактов дешифратора таким образом, что совпадение разрешающих потенциалов на всех входах дешифратора происходит после просчета счетчиков (m+2)-го импульса последовательности (эпюра в), поступающей на его вход. В результате в момент прихода (m+2)-го импульса изменяется полярность на выходе дешифратора. Полученный перепад напряжения через блок сброса, входящий в счетчик 8 тактов, подается на входы сброса всех счетных триггеров счетчика 8 тактов и устанавливает их в исходное состояние. Выход дешифратора является выходом счетчика 8 тактов. В течение тактов с 1-го по (m+1)-й включительно на втором входе элемента И 4 счетчик 8 тактов поддерживает потенциал (эпюра е), разрешающий прохождение через элемент И 4 на второй вход передающего парафазного усилителя 6 первой последовательности импульсов (эпюра в), поступающей на первый вход элемента И 4 с третьего выхода формирователя 7. По приходу (m+2)-го импульса первой последовательности импульсов (эпюра в) потенциал на выходе счетчика 8 тактов изменяется (эпюра е) и запрещает прохождение (m+2)-го импульса первой последовательности импульсов (эпюра в) на второй вход передающего парафазного усилителя 6 (эпюра ж).

В тактах (m+1) и (m+2( на вход триггера 1 всегда подается в слове блочной синхронизации логический "0" (фиг. 3Б-а), а в остальных словах блока - логическая "1" (фиг. 3А-а). В результате, при передаче слова блочной синхронизации на первый вход передающего парафазного усилителя 6 (эпюра з) в тактах (m+1) и (m+2) поступают импульсы третьей последовательности (эпюра д), а при передаче остальных слов блока - импульсы второй последовательности (эпюра г). С выхода передающего парафазного усилителя 6 в линию передаются в такте (m+1) двухполярный импульс (эпюра и), являющийся символом логической "1" или логического "0", а в такте (m+2) только положительный импульс, представляющий часть символа логической "1" или логического "0" без отрицательного тактового импульса.

На приемной стороне принятая последовательность (эпюра и) двухполярных импульсов разделяется в приемном парафазном усилителе 14 на последовательность тактовых импульсов (эпюра л) на первом выходе приемного парафазного усилителя 14 и на последовательность кодовых импульсов (эпюра к) на втором выходе приемного парафазного усилителя 14. Импульсы, проходящие на выход элемента И 15 (эпюра м) только при приеме символа логической "1", переводят RS-триггер 18 в единичное состояние, а тактовые импульсы с первого выхода приемного парафазного усилителя 14 возвращают его в нулевое состояние (эпюра н). Счетчик импульсов 17 кодовой последовательности считает все импульсы, поступающие на его вход со второго выхода приемного парафазного усилителя 14 и сбрасывается в исходное состояние тактовыми импульсами с первого выхода приемного парафазного усилителя 14. Таким образом, в течение тактов с 1-го по (m+1) на выходе счетчика 17 поддерживается потенциал (эпюра п), запрещающий прохождение кодовых импульсов (эпюра к) на выходе элемента И 19 и дополнительного элемента И 20.

Поскольку в такте (m+2) тактовый импульс отсутствует, RS-триггер 18 после установки его в единичное состояние в такте (m+1) при прохождении любого слова блока, кроме слова блочной синхронизации, остается в этом же состоянии также и в такте (m+2), а счетчик 17 после просчета одного кодового импульса в такте (m+1) не сбрасывается в исходное состояние в такте (m+2), а считает в этом такте второй кодовый импульс. В результате на выходе счетчика 17 (эпюра п) и на прямом выходе RS-триггера 18 (эпюра н) устанавливаются потенциалы, разрешающие прохождение в такте (m+2) кодового импульса со второго выхода приемного парафазного усилителя 14 на выход элемента И 19 (эпюра р). Следовательно, на выходе элемента И 19 появляется сигнал (эпюра р) только в такте (m+2), если в такте (m+1) передан символ логической "1". Таким образом, выход элемента И 19 является выходом импульсов пословной синхронизации.

После прохождения слова блочной синхронизации RS-триггер 18 не устанавливается в такте (m+1)в единичное состояние, поскольку в этом такте слова передается символ логического "0", а остается в нулевом состоянии после прохождения тактового импульса (эпюра л) в такте (m+1). Счетчик 17 работает при приеме слова блочной синхронизации также, как и при приеме остальных слов блока. В результате на выходе счетчика 17 (эпюра п) и на инверсном выходе Rs-триггера 18 (эпюра о) устанавливаются потенциалы, разрешающие прохождение в такте (m+2) кодового импульса со второго выхода приемного парафазного усилителя 14 на выход дополнительного элемента И 20 *эпюра с). Следовательно, на выходе дополнительного элемента И 20 появляется сигнал (эпюра 3с) только в такте (m+2), если в такте (m+1) передан символ логического "0". Таким образом, выход дополнительного элемента И 20 является выходом импульсов блочной синхронизации.

(56) Авторское свидетельство СССР N 1615894, кл. Н 04 L 7/02, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПЕРИОДНО-МОДУЛИРОВАННОГО ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПАРАЛЛЕЛЬНЫЙ КОД И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2032270C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ФАЗЫ | 1992 |

|

RU2028727C1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| АКТИВНО-ИМПУЛЬСНЫЙ ОПТИКО-ЭЛЕКТРОННЫЙ ПРИБОР ВИЗУАЛИЗАЦИИ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2037837C1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1992 |

|

RU2072554C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| Система передачи цифровой информации | 1990 |

|

SU1786679A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

Использование: в электросвязи в системах передачи информации. Сущность изобретения: устройство тактовой синхронизации содержит на передающей стороне триггер 1, элементы И 2 - 4, элемент ИЛИ 5, передающий парафазный усилитель 6, формирователь 7 последовательностей импульсов и счетчик 8 тактов, причем в состав формирователя 7 входят триггеры 9 и 10 и элементы И 11 - 13, а на приемной стороне - приемный парафазный усилитель 14, элемент И 15, блок 16 задержки, счетчик 17 импульсов кодовой последовательности, RS-триггер 18, элементы И 19 и 20. Цель изобретения - расширение функциональных возможностей путем обеспечения блочной синхронизации. 3 ил.

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержащее на передающей стороне последовательно соединенные триггер, первый элемент И, элемент ИЛИ и передающий парафазный усилитель, выход которого соединен с входом канала связи, инверсный выход триггера через второй элемент И соединен с вторым входом элемента ИЛИ, первый и второй выходы формирователя последовательностей импульсов соединены с вторыми входами первого и второго элементов И, третий выход формирователя последовательностей импульсов соединен с вторым входом передающего парафазного усилителя через последовательно соединенные счетчик тактов и третий элемент И, другой вход которого соединен с третьим выходом формирователя последовательностей импульсов, вход которого является тактовым входом устройства, информационным входом которого является вход триггера, а на приемной стороне - последовательно соединенные приемный усилитель, блок задержки и четвертый элемент И, второй вход которого соединен с вторым выходом приемного усилителя, первый вход которого соединен с выходом канала связи, при этом первый выход приемного усилителя соединен с входами сброса счетчика импульсов кодовой последовательности и RS-триггера, установочный вход которого соединен с выходом четвертого элемента И, второй выход приемного усилителя соединен со счетным входом счетчика импульсов кодовой последовательности и с первым входом пятого элемента И, второй и третий входы которого соединены соответственно с выходом счетчика импульсов кодовой последовательности и с прямым выходом RS-триггера, причем выход блока задержки и выходы четвертого и пятого элементов И являются соответственно тактовым выходом, информационным выходом и выходом импульсов цикловой пословной синхронизации устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения блочной синхронизации, в него введен дополнительный элемент И, первый и второй входы которого соединены соответственно с первым и вторым входами пятого элемента И, а третий вход дополнительного элемента И соединен с инверсным выходом RS-триггера, причем выход дополнительного элемента И является выходом импульсов блочной синхронизации устройства.

Авторы

Даты

1994-04-15—Публикация

1990-05-03—Подача