Изобретение относится к устройствам сопряжения вычислительной техники и может быть использовано для связи абонентов магистрали последовательного интерфейса, например Манчестер-2, с цифровыми устройствами через стандартный параллельный интерфейс, например И41.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения режима прямого доступа к оперативной памяти вычислительной системы через стандартный интерфейс, а также анализа адреса абонента магистрали последовательного интерфейса.

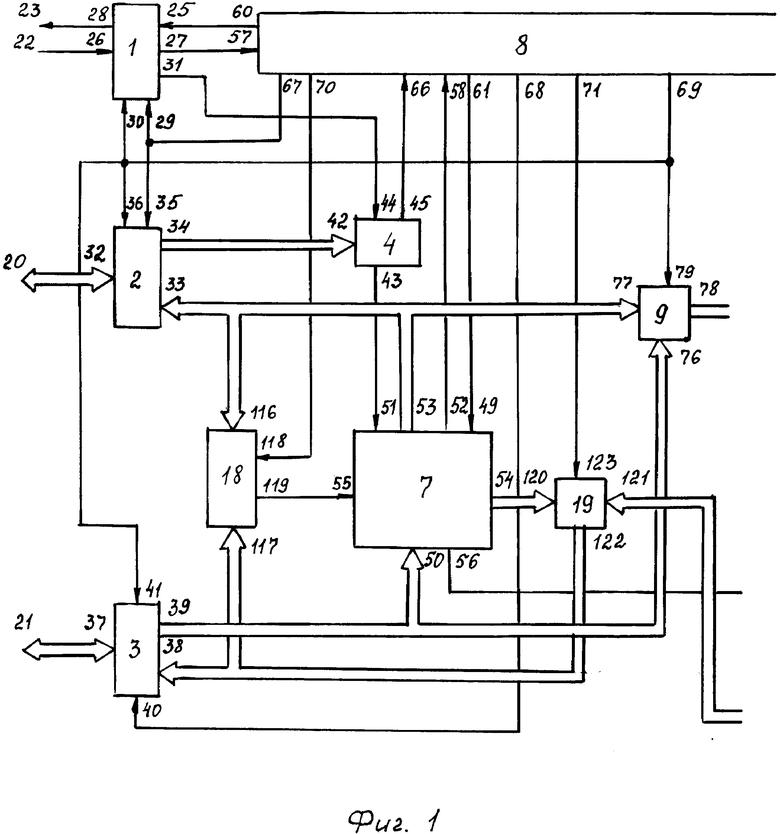

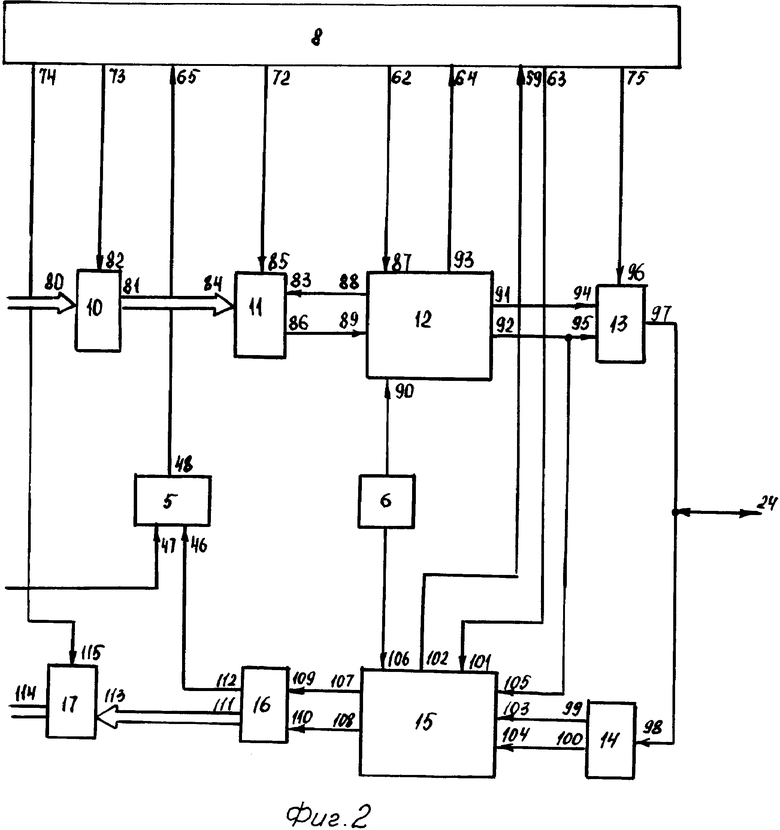

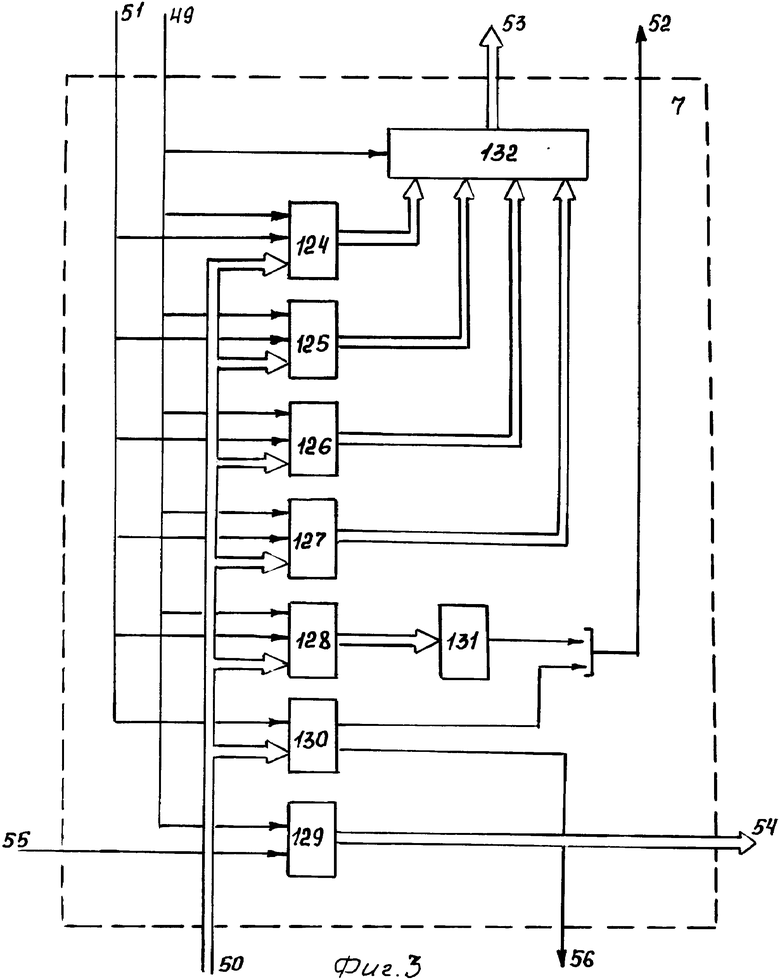

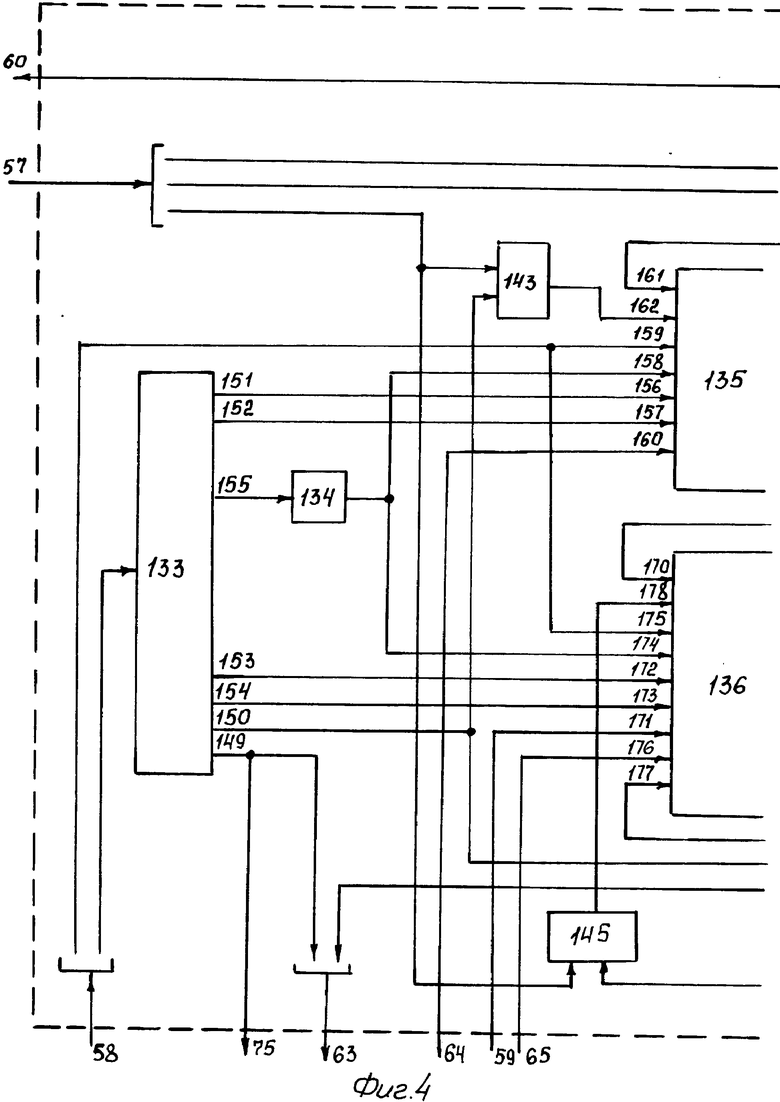

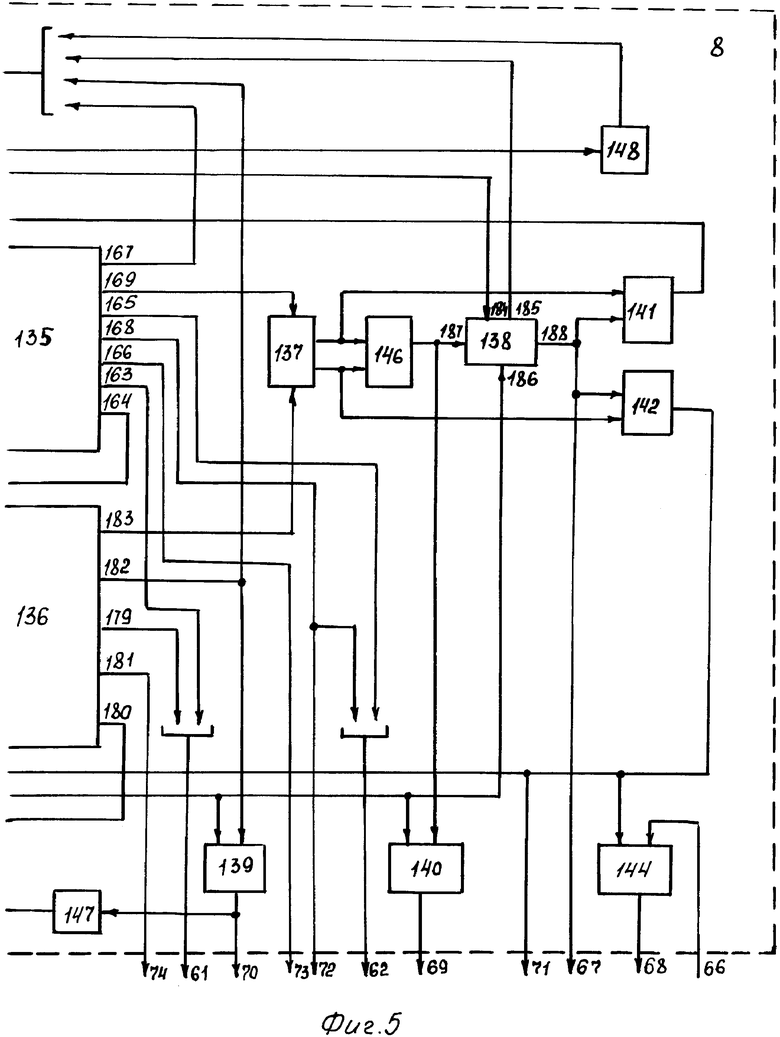

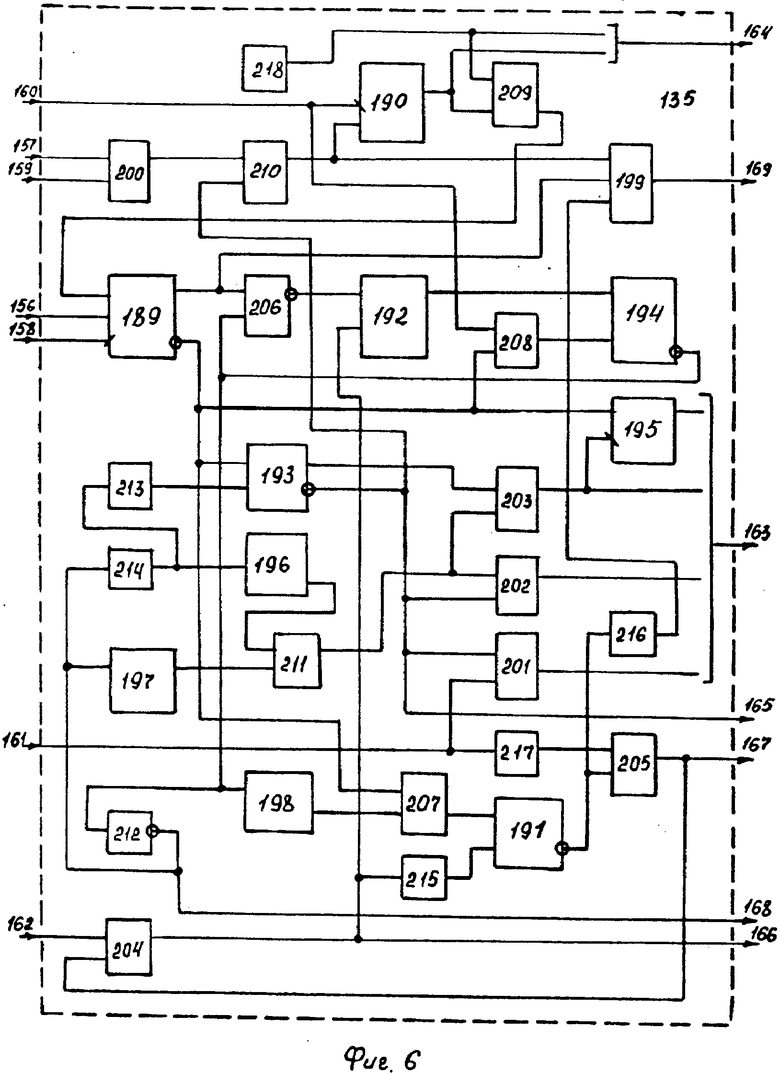

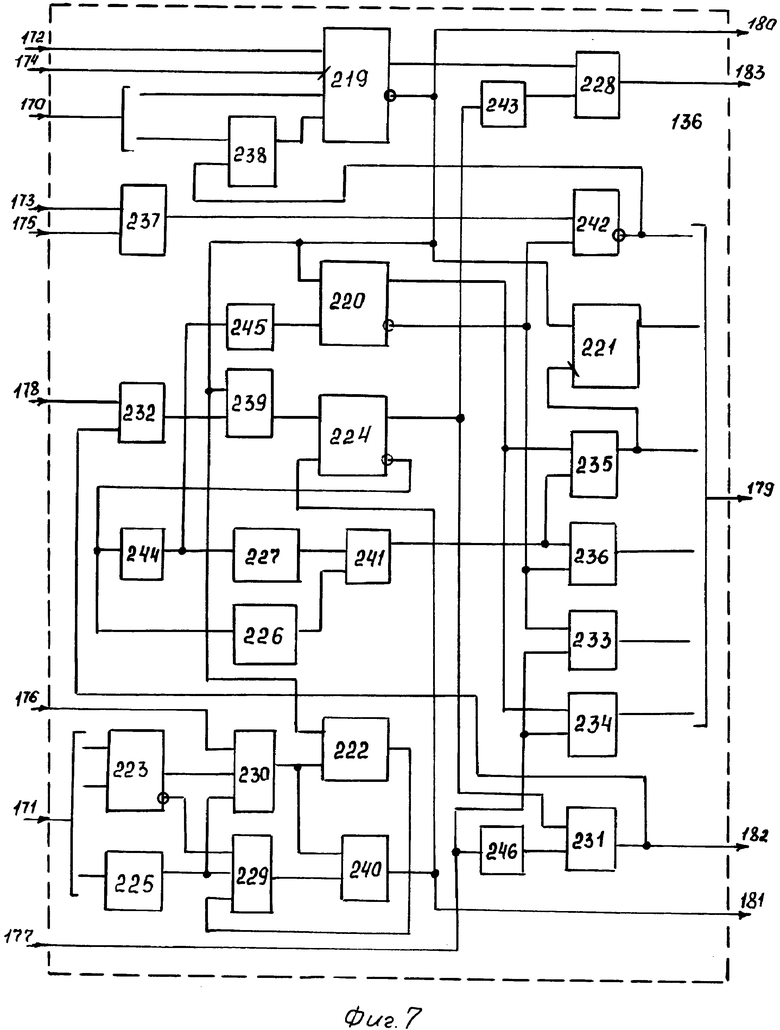

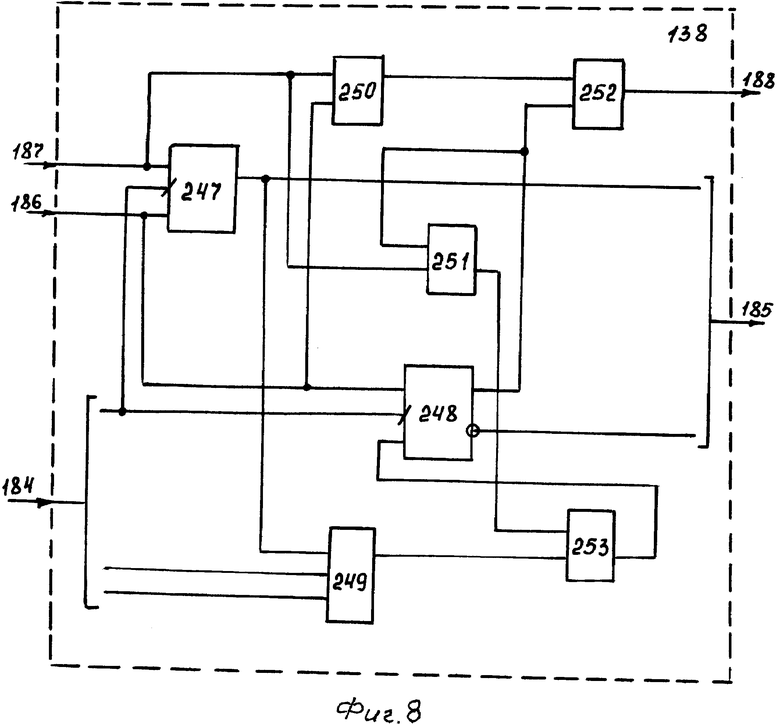

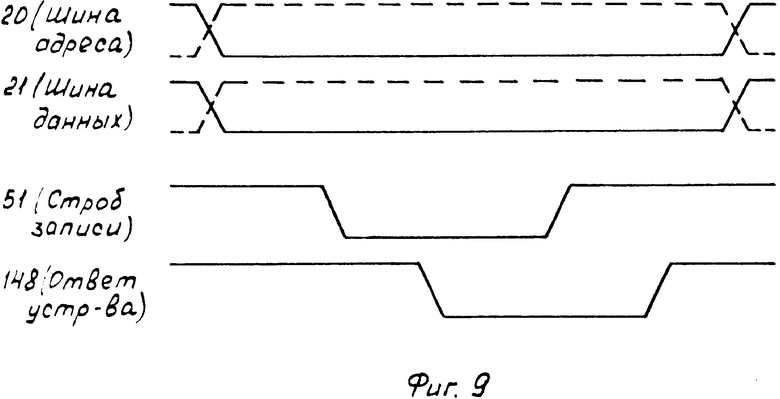

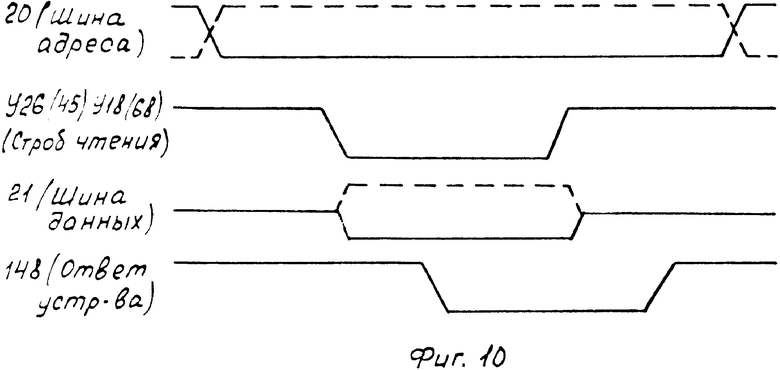

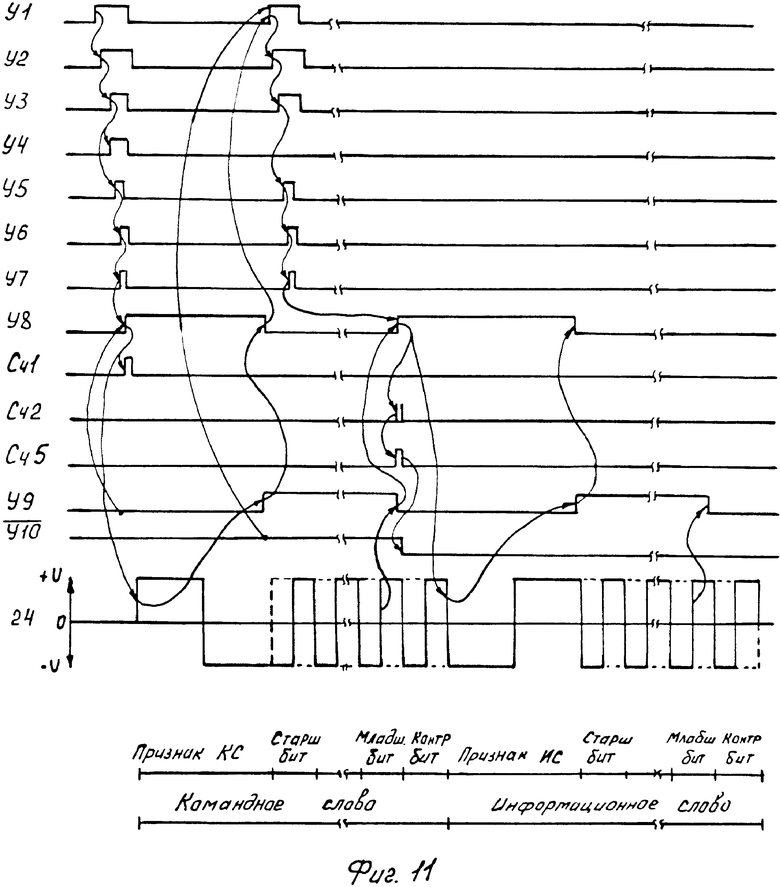

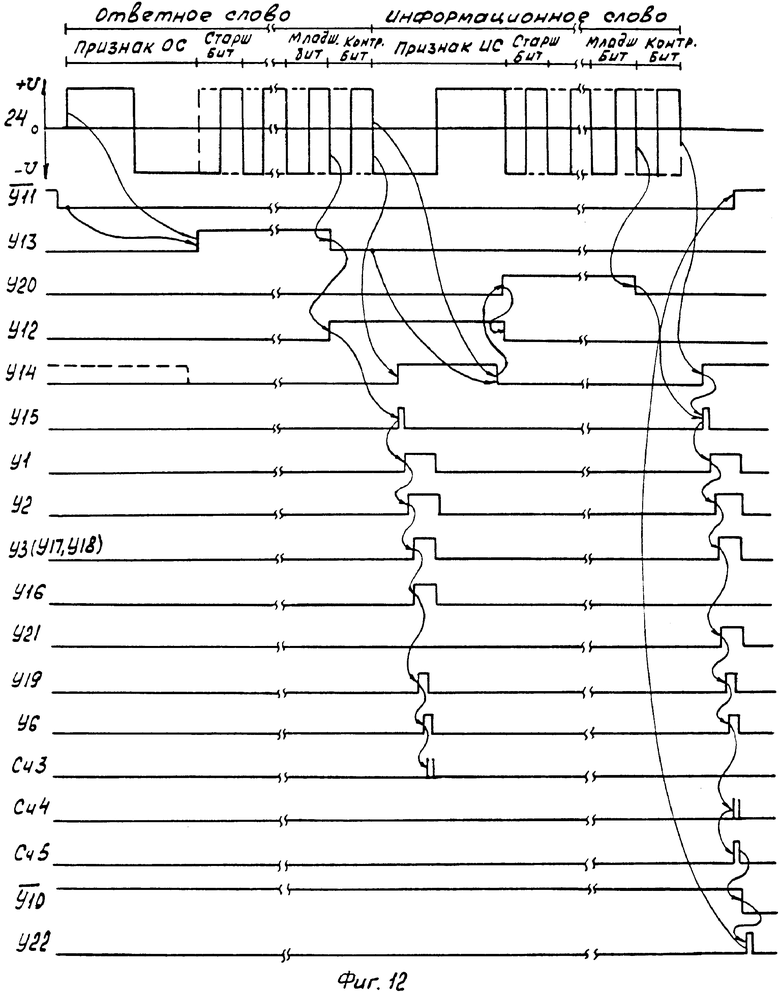

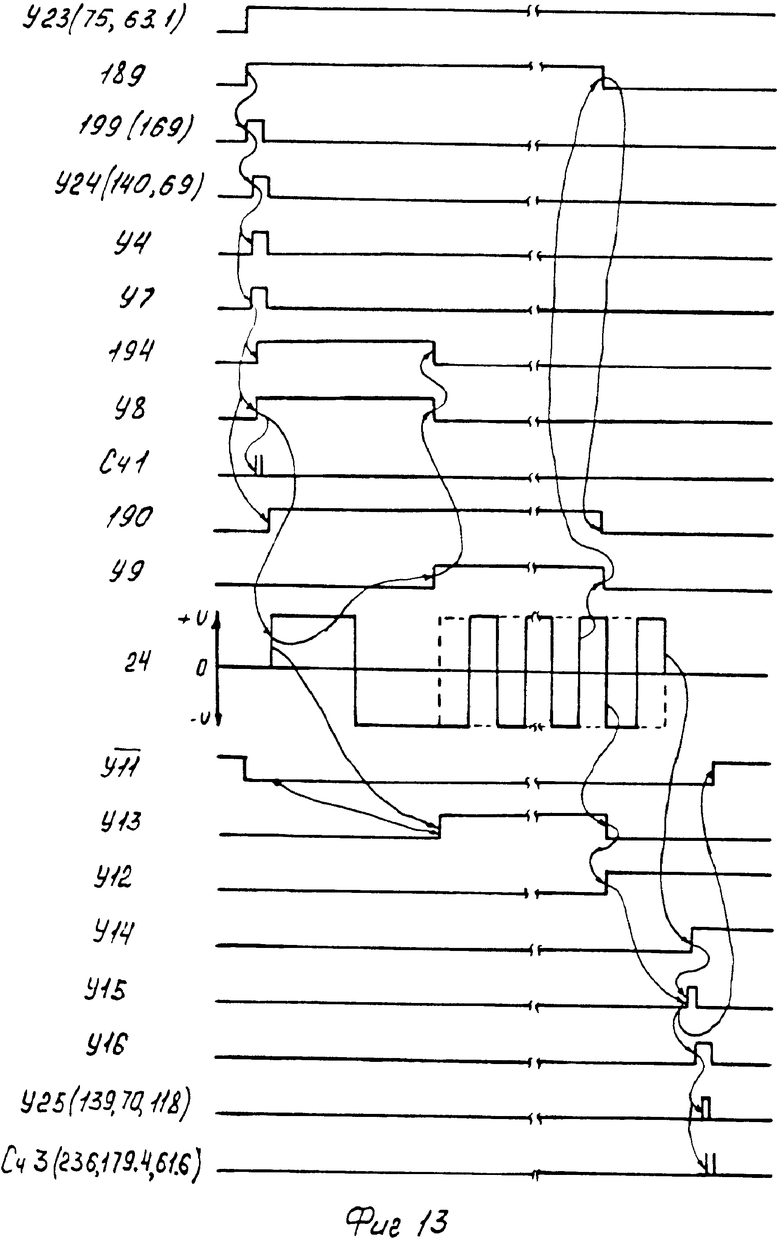

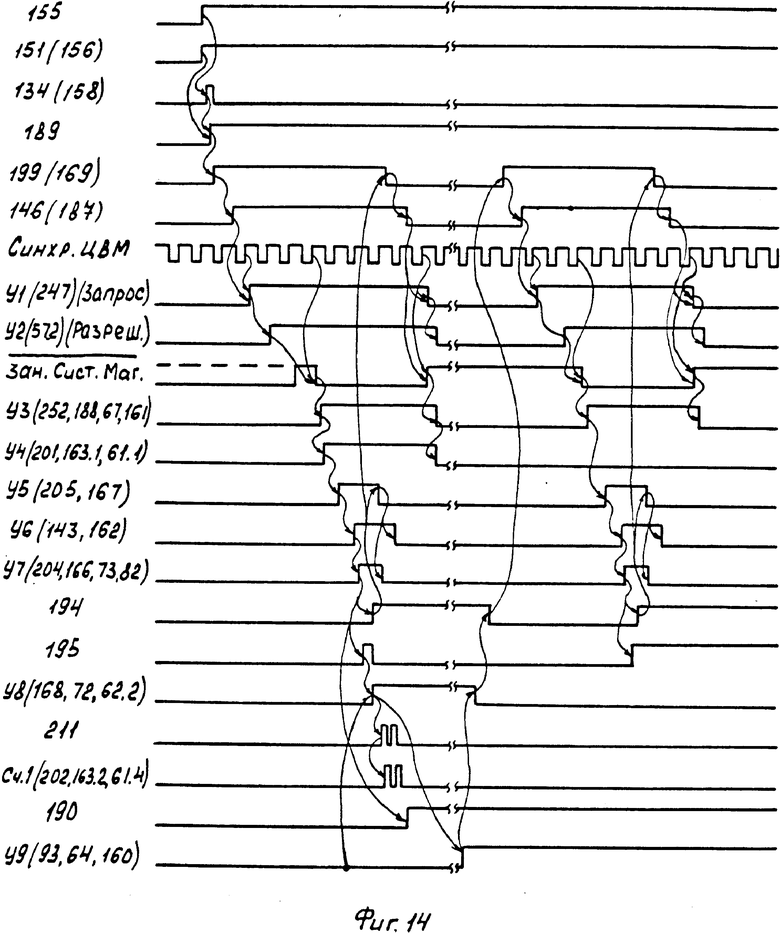

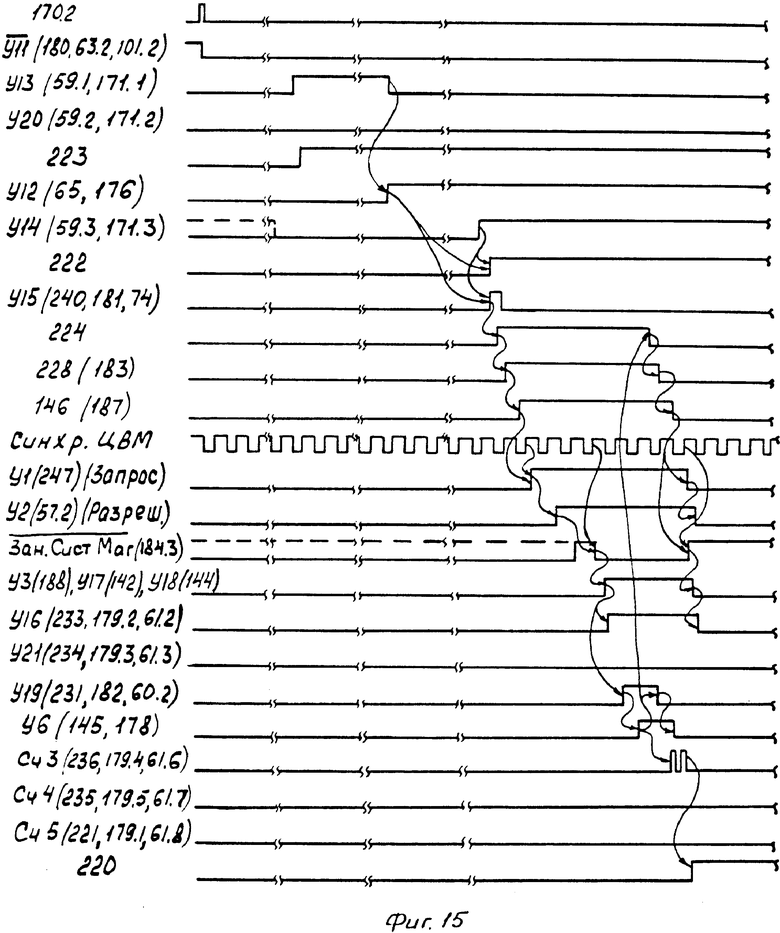

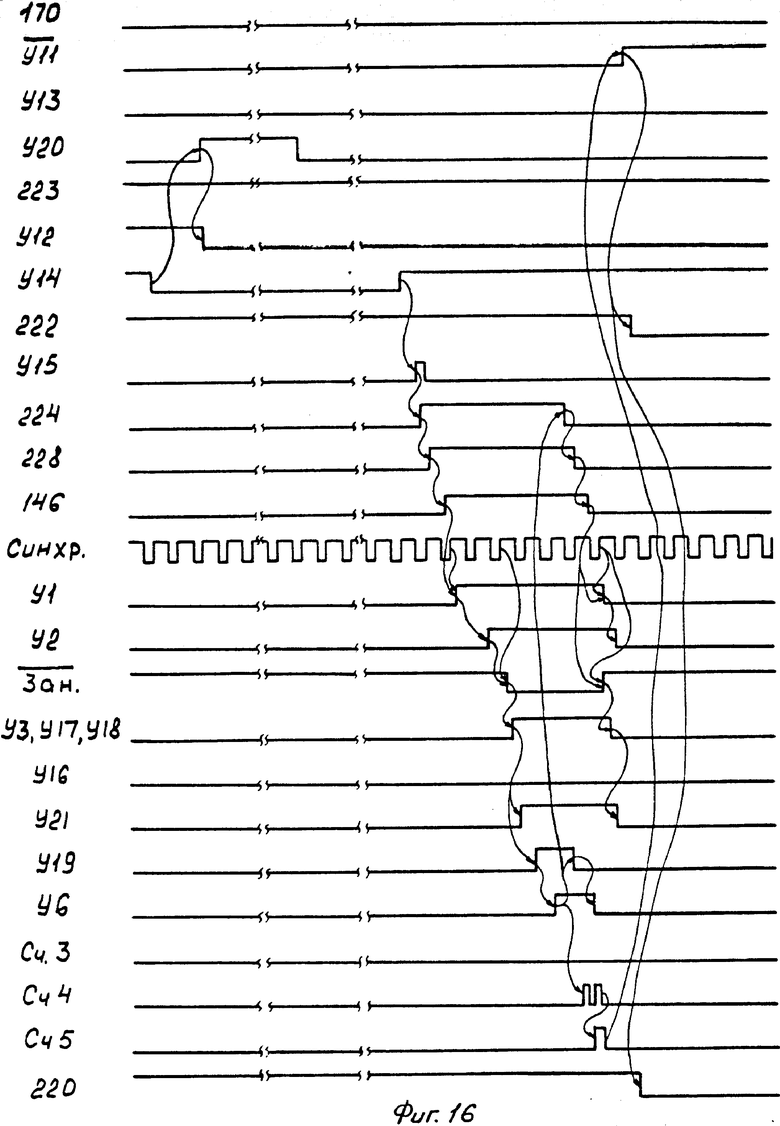

На фиг. 1 и 2 представлена функциональная схема предлагаемого устройства; на фиг.3 - схема блока регистров; на фиг.4 и 5 - схема блока управления; на фиг.6 - схема узла управления передачей; на фиг.7 - схема узла управления приемом; на фиг.8 - схема блока триггеров прямого доступа; на фиг. 9 и 10 представлены временные диаграммы соответственно записи исходных данных и чтения информации о состоянии устройства сопряжения со стороны системной магистрали; на фиг.11 и 12 - диаграммы работы устройства сопряжения в режиме I соответственно при передаче из оперативной памяти в магистраль последовательного интерфейса командного слова с одним информационным словом и при приеме в обратном направлении ответного слова с одним информационным словом; на фиг. 13 - диаграмма работы устройства сопряжения в режиме II ("самопроверка") с одним контрольным словом; на фиг.14 - диаграмма работы узла управления передачей в составе блока управления; на фиг.15 и 16 - диаграмма работы узла управления приемом в составе блока управления.

Устройство сопряжения магистралей (фиг.1 и 2) содержит первый-третий шинные формирователи 1-3, дешифратор 4 адресов, первый элемент 5 сравнения, генератор 6 тактовой частоты, блок 7 регистров, блок 8 управления, первый мультиплексор 9, первый регистр 10, параллельно-последовательный преобразователь 11, шифратор 12 сигналов линии, усилитель-передатчик 13, усилитель-приемник 14, дешифратор 15 сигналов линии, последовательно-параллельный преобразователь 16, второй регистр 17, второй элемент 18 сравнения, второй мультиплексор 19, группу 20 адресных входов-выходов, группу 21 информационных входов-выходов, группу 22 входов управления, группу 23 управляющих выходов, вход-выход 24.

Первый шинный формирователь 1 имеет первую и вторую группы 25 и 26 информационных входов, первую и вторую группы 27 и 28 информационных выходов, вход 29 управления, вход 30 выключения и информационный выход 31. Второй шинный формирователь 2 имеет группу 32 информационных входов-выходов, группу 33 информационных входов, группу 34 информационных выходов, вход 35 управления и вход 36 выключения. Третий шинный формирователь 3 содержит группу 37 информационных входов-выходов, группу 38 информационных входов, группу 39 информационных выходов, вход 40 управления и вход 41 выключения.

Дешифратор 4 адресов имеет группу 42 входов, группу 43 выходов, стробирующий вход 44 и выход 45. Первый элемент 5 сравнения содержит первый, второй входы 46, 47 и выход 48. Блок 7 регистров имеет группу 49 входов управления, группу 52 управляющих выходов, группу 53 адресных выходов, группу 54 информационных выходов, вход 55 и выход 56. Блок 8 управления содержит первую-третью группы 57-59 входов, первую-четвертую группы 60-63 выходов, первый-третий входы 64-66, первый-девятый выходы 67-75. Первый мультиплексор 9 имеет первую и вторую группы 76 и 77 входов, группу 78 и выходов и вход 79 управления. Первый регистр 10 имеет группу 80 входов, группу 81 выходов, вход 82 стробирования. Параллельно-последовательный преобразователь 11 содержит группу 83 входов управления, группу 84 параллельных входов, вход 85 записи и последовательный выход 86. Шифратор 12 сигналов линии содержит группу 87 входов управления, группу 88 управляющих выходов, вход 89 данных, стробирующий вход 90, первый и второй информационные выходы 91 и 92, управляющий выход 93. Усилитель-передатчик 13 имеет первый и второй входы 94 и 95, вход 96 выключения, выход 97. Усилитель-приемник 14 имеет вход 98, первый и второй выходы 99 и 100. Дешифратор 15 сигналов линии содержит группу 101 входов управления, групп 102 управляющих выходов, первый и второй информационные входы 103 и 104, вход 105 контрольных данных, стробирующий вход 106, выход 107 данных, управляющий выход 108. Последовательно-параллельный преобразователь 15 имеет последовательный вход 109, вход 110 управления, группу 111 параллельных выходов и выход 112. Второй регистр 17 имеет группу 113 входов, группу 114 выходов вход 115 стробирования. Второй элемент 18 сравнения содержит первую и вторую группы 116 и 117 входов, стробирующий вход 118 и выход 119. Второй мультиплексор 19 содержит первую и вторую группы 120 и 121 входов, группу 122 выходов и вход 123 управления.

Блок 7 регистров (фиг.3) состоит из первого-пятого счетчиков 124-128, первого и второго регистров 129 и 130, дешифратора 131 нуля и селектора 132.

Блок 8 управления (фиг.4 и 5) содержит дешифратор 133 команд, одновибратор 134, узел 135 управления передачей, узел 136 управления приемом, приоритетный шифратор 137, блок 138 триггеров прямого доступа, первый-четвертый элементы И 139-142, первый-четвертый элементы ИЛИ 143-146, первый и второй элементы 147 и 148 задержки. Дешифратор 133 команд имеет первый-седьмой выходы 149-155. Узел 135 управления передачей содержит первый-седьмой входы 156-162, первую и вторую группы 163 и 164 выходов, первый-пятый выходы 165-169. Узел 136 управления приемом содержит первую и вторую группы 170 и 171 входов, первый-седьмой входы 172-178, группу 179 выходов, первый-четвертый выходы 180-183. Блок 138 триггеров прямого доступа имеет группу 184 входов, группу 185 выходов, первый, второй входы 186, 187 и выход 188.

Узел 135 управления передачей (фиг.6) содержит первый-четвертый D-триггеры 189-192, первый и второй RS-триггеры 193 и 194, счетный триггер 195, первый-третий одновибраторы 196-198, первый-седьмой элементы И 199-205, элемент И-НЕ 206, первый-пятый элементы ИЛИ 207-211, инвертор 212, первый-пятый элементы 213-217 задержки и блок 218 установки.

Узел 136 управления приемом (фиг.7) содержит первый и второй D-триггеры 219 и 220, счетный триггер 221, первый-третий RS-триггеры 222-224, первый-третий одновибраторы 225-227, первый-десятый элементы И 228-237, первый-четвертый элементы ИЛИ 238-241, элемент ИЛИ-НЕ 242, первый-четвертый элементы 243-246 задержки.

Приоритетный шифратор 137 выполнен по авт.св. N 1226460, кл. G 06 F 9/40, 1986.

Блок 138 триггеров прямого доступа (фиг.8) содержит первый и второй D-триггеры 247 и 248, первый-третий элементы И 249-251, первый и второй элементы ИЛИ 252 и 253.

Одновибратор 134 (фиг.4), первый-третий одновибраторы 196-198 (фиг.6), первый-третий одновибраторы 225-227 (фиг.7) выполнены по известной схеме (УДК 621.317.7 : 621.382.049.77 Гутников В.С. Интегральная электроника в измерительных устройствах 2-е изд., Л.: Энергоатомиздат. Ленинградское отделение, 1988, с.159, рис.5.10г).

Блок 218 установки (фиг.6) выполнен также по известной схеме (авт.св. N 1228229, кл. H 03 K 3/64, 1986, фиг.2).

Магистраль последовательного интерфейса стыкуется с устройством сопряжения (фиг.1 и 2) через вход-выход 24, с другой стороны при помощи шинных формирователей 1-3 подстыковывается системная магистраль (СМ) вычислительной системы. Группа 20 адресных входов-выходов устройства соединяется с шиной адреса, группа 21 информационных входов-выходов устройства - с шиной данных. Причем количество линий в каждой из групп равняется числу разрядов в соответствующей шине. Группа 22 входов управления связана с шиной сигналов управления СМ и состоит из пяти входов, соединенных соответственно с линиями сигналов синхронизации СМ, приоритетного разрешения доступа к магистрали, занятости магистрали, подтверждения передачи информации и обращения в порт. Группа 23 управляющих выходов также связана с шиной сигналов управления СМ и состоит из пяти выходов, соединенных соответственно с линиями сигналов чтения памяти, записи в память, запроса управления магистралью подтверждения передачи информации. Все линии СМ являются двунаправленными.

В исходном состоянии в первом шинном формирователе 1 соединены третий-пятый входы первой группы 25 информационных входов соответственно с третьим-пятым выходами второй группы 28 информационных выходов, первый-третий входы второй группы 26 информационных входов - соответственно с первым-третьим выходами первой группы 27 информационных выходов, а пятый вход второй группы 26 информационных входов - с пятым выходом первой группы 27 информационных выходов и информационным выходом 31. Второй и третий шинные формирователи 2 и 3 находятся в состоянии приема сигналов с групп 32, 37 информационных входов-выходов, первый мультиплексор 9 соединяет первую группу 76 входов с группой 78 выходов, шифратор 12 сигналов линии и дешифратор 15 сигналов линии выключены, второй мультиплексор 19 соединяет первую группу 120 входов с группой 122 выходов, управляющие сигналы Y1-У26 во внутренних цепях отсутствуют.

Устройство работает следующим образом.

Предварительно со стороны СМ вводятcя в блок 7 регистров исходные данные, определяющие начальные адреса вывода командных (КС) и информационных (ИС) слов из оперативной памяти (ОП) вычислительной системы, начальные адреса ввода ответных слов (ОС) и ИС в ОП, длину массива ИС, а также управляющую информацию. Для этого на группу 20 адресных входов-выходов устройства и соответственно на группу 32 информационных входов-выходов второго шинного формирователя 2 подается адрес конкретного счетчика или регистра блока 7 регистров, который через группу 34 информационных выходов попадает в дешифратор 4 адресов.

В то же время на группу 21 информационных входов-выходов устройства и группу 37 информационных входов-выходов третьего шинного формирователя 3 подается одно слово исходных данных, которое группой 39 информационных выходов подводится к группе 50 информационных входов блока 7 регистров.

Одновременно через группу 22 входов управления устройства по пятому входу второй группы 26 информационных входов первого шинного формирователя 1 из СМ поступает сигнал записи, который через информационный выход 31 направляется на стробирующий вход 44 дешифратора 4 адресов. Далее в соответствии с имеющимся адресом по одному из выходов группы 43 выходов он направляется через группу 51 стробирюущих входов к конкретному объекту в блоке 7 регистров, когда производится запись слова исходных данных.

Параллельно с этим сигнал записи с пятого выхода первой группы 27 информационных выходов первого шинного формирователя 1 поступает на пятый вход первой группы 57 входов блока 8 управления, который после некоторой паузы, необходимой для запоминания слова исходных данных, отправляет сигнал подтверждения передачи информации по пятому выходу первой группы 60 выходов, пятому входу первой группы 25 информационных входов и пятому выходу второй группы 28 информационных выходов первого шинного формирователя 1 в шину сигналов управления СМ. После этого сигнал записи снимается и освобождаются шины адреса и данных.

Таким образом, вся исходная информация пословно заносится в блок 7 регистров. Последним записывается управляющее слово, так как оно содержит в себе признак запуска устройства. Кроме того, в управляющем слове указываются коды режимов работы, направление передачи массива ИС, адрес абонента магистрали последовательного интерфейса, с которым предстоит обмен. Управляющее слово через первый выход группы 52 управляющих выходов блока 7 регистров направляется в блок 8 управления по первому входу второй группы 58 входов.

Возможны два основных режима работы устройства сопряжения: контроллер магистрали последовательного интерфейса (режим I) и "самопроверка" (режим II).

В режиме I работа устройства осуществляется в два этапа. Первый этап - передача из ОП в магистраль последовательного интерфейса КС и за ним (если задан вывод массива) определенного количества ИС. Второй этап - прием в обратном направлении ОС и за ним (если задан ввод информации) указанного количества ИС.

Первый этап начинается с того, что организуется цикл чтения ОП вычислительной системы по адресу вывода КС. Для этого сигналом Y1 через третий выход первой группы 60 выходов блока 8 управления, третий вход первой группы 25 информационных входов и третий выход второй группы 28 информационных выходов первого шинного формирователя 1 устройство сопряжения запрашивает возможность прямого доступа к ОП через СМ. Разрешение сигналом Y2 поступает из СМ также через первый шинный формирователь 1, с второго выхода первой группы 27 информационных выходов которого сигнал Y2 приходит на второй вход первой группы 57 входов блока 8 управления. После этого сигналом Y3, поступающим с первого выхода 67 блока 8 управления на вход 35 управления второго шинного формирователя 2, последний переводится в состояние передачи сигналов. Этим же сигналом по входу 29 управления в первом шинном формирователе 1 соединяются первый и второй входы первой группы 25 информационных входов соответственно с первым и вторым выходами второй группы 28 информационных выходов, четвертый вход второй группы 26 информационных входов - с четвертым выходом первой группы 27 информационных выходов, кроме того, отключаются пятые входы первой и второй групп 25 и 26 информационных входов соответственно от пятых выходов второй и первой групп 27 и 28 информационных выходов и информационного выхода 31.

По сигналу Y4, проходящему с первого выхода второй группы 61 выходов блока 8 управления на первый вход группы 49 входов управления блока 7 регистров, последний выставляет через группу 53 адресных выходов адрес ячейки ОП, в которой находится требуемое КС. Этот адрес направляется к группе 33 информационных входов второго шинного формирователя 2 и далее через группу 20 адресных входов-выходов устройства в СМ.

Одновременно на первом выходе первой группы 60 выходов блока 8 управления формируется стробирующий сигнал Y5 чтения, который через первый шинный формирователь 1 по первому входу первой группы 25 информационных входов и первому выходу второй группы 28 информационных выходов направляется в СМ.

Расшифровав адрес и получив сигнал Y5, системная ОП устанавливает на шину данных СМ содержимое указанной ячейки (требуемое КС) и формирует ответный сигнал Y6, который через первый шинный формирователь 1 по четвертому входу второй группы 26 информационных входов и четвертому выходу первой группы 27 информационных выходов попадает на четвертый вход первой группы 57 входов блока 8 управления.

Тем временем КС , пройдя через третий шинный формирователь 3, с группы 39 информационных выходов попадает на первую группу 76 входов первого мультиплексора 9 и с его группы 78 выходов подходит к группе 80 входов первого регистра 10. Импульсные сигналом Y7, появляющимся на воде 82 стробирования с седьмого выхода 73 блока 8 управления, КС записывается в указанный регистр и группой 81 выходов устанавливается на группе 84 параллельных входов параллельно-последовательного преобразователя 11. Затем последовательно снимаются сигналы Y5, Y6, Y3, Y4, Y1, Y2. В то же время на шестом выходе 72 и втором выходе третьей группы 62 выходов блока 8 управления появляется сигнал Y8, который направляется к входу 85 записи параллельно-последовательного преобразователя 11, куда переносится КС, и к второму входу группы 87 входов управления шифратора 12 сигналов линии, производя запуск последнего. По сигналу Y8 с некоторой задержкой инициируется сигнал Y9 на управляющем выходе 93 шифратора 12 сигналов линии, по первому входу 64 блока 8 управления сбрасывающий сигнал Y8.

Постоянно получая на стробирующий вход 90 с второго выхода генератора 6 тактовой частоты синхронизирующие импульсы, шифратор 12 сигналов линии через группу 88 управляющих выходов и группу 83 входов управления обеспечивает функционирование параллельно-последовательного преобразователя 11, с последовательного выхода 86 которого по своему входу 89 данных принимает КС, и преобразует его в соответствующую комбинацию двух бифазных сигналов на первом и втором информационных выходах 91 и 92. Усилитель-передатчик 13 преобразует комбинацию указанных униполярных сигналов, попадающих на первый и второй входы 94 и 95, в комбинацию разнополярных импульсов, поступающих с выхода 97 на вход-выход 24 устройства и далее к абоненту магистрали последовательного интерфейса, адрес которого указан в КС.

После появления сигнала Y8 сразу же по четвертому выходу второй группы 61 выходов блока 8 управления и четвертому входу группы 49 входов управления в блок 7 регистров направляются счетные импульсы Сч1 для формирования адреса вывода последующего КС.

Если в исходных данных задана передача массива ИС из ОП, то пропадание сигнала Y8 приводит к тому, что блок 8 управления организует новый цикл чтения ОП вычислительной системы описанным выше образом, но теперь уже по адресу вывода ИС, присутствующему на группе 53 адресных выходов блока 7 регистров (сигнал Y4 не формируется) и так же, как раньше, по сигналу Y7 с седьмого выхода 73 блока 8 управления полученное ИС записывается в первый регистр 10. Однако, если шифратор 12 сигналов линии еще не закончил трансляцию предыдущего слова и удерживает на своем управляющем выходе 93 сигнал Y9, то на шестом выходе 72 и втором выходе третьей группы 62 выходов блока 8 управления не возникает сигнал Y8. Последний появляется тогда, когда предыдущее слово полностью отправлено и снимается сигнал Y9. Параллельно-последовательный преобразователь 11 вновь заполняется словом, предназначенным для передачи, и происходит повторный запуск шифратора 12 сигналов линии.

Очередное появление сигнала Y8 ведет к передаче с пятого и восьмого выходов второй группы 61 выходов блока 8 управления соответственно к пятому и восьмому входам группы 49 входов управления блока 7 регистров счетных импульсов Сч2, формирующих новый адрес вывода следующего ИС, и счетный импульс Сч5, декрементирующий информацию о длине массива. Снятие сигнала Y9 ведет опять к организации цикла чтения ОП по адресу вывода ИС.

Таким образом повторяется работа устройства до тех пор, пока содержимое заданного количества ячеек ОП области вывода ИС не будет передано абоненту магистрали последовательного интерфейса.

Появление нулевой информации о длине массива ведет к образованию сигнала Y10, который с второго выхода группы 52 управляющих выходов блока 7 регистров приходит к второму входу второй группы 58 входов блока 8 управления и предотвращает дальнейшее чтение ОП. Окончание процесса передачи информации происходит после снятия сигнала Y9 с управляющего выхода 93 шифратора 12 сигналов линии, что свидетельствует о завершении трансляции последнего слова.

Если в исходных данных не задана передача массива ИС из ОП, то независимо от установленной длины массива устройство сопряжения ограничивается отправкой одного КС.

Появлением сигнала Y11 от второго выхода четвертой группы 63 выходов блока 8 управления на втором входе группы 101 входов управления дешифратора 15 сигналов линии разрешается работа последнего и тем самым начинается процесс приема информации, которая по входу-выходу 24 устройства и входу 98 попадает в усилитель-приемник 14, преобразующий комбинацию разнополярных импульсов в комбинацию двух бифазных сигналов, поступающих с первого и второго выходов 99 и 100 на первый и второй информационные входы 103 и 104 дешифратора 15 сигналов линии. Постоянно получая на стробирующий вход 106 с первого выхода генератора 6 тактовой частоты синхронизирующие импульсы, дешифратор 15 сигналов линии преобразует комбинацию двух бифазных сигналов в последовательный код, при помощи управляющего выхода 108 и входа 110 управления обеспечивает функционирование последовательно-параллельного преобразователя 16, заполняя его принимаемым словом через последовательный вход 109.

В первую очередь с магистрали последовательного интерфейса приходит ОС. Как только заканчивается формирование ОС в последовательно-параллельном преобразователе 16, на первый вход 46 первого элемента 5 сравнения направляется содержащий в ОС адрес абонента, с которым идет обмен. С другой стороны, на втором входе 47 с выхода 56 блока 7 регистров постоянно присутствует адрес абонента, заданный в исходных данных. При совпадении заданного и полученного адресов абонента с выхода 48 первого элемента 5 сравнения отправляется сигнал Y12 к второму входу 65 блока 8 управления.

Прием ОС сопровождается присутствием сигнала Y13 на первом выходе группы 102 управляющих выходов дешифратора 15 сигналов линии. По окончании приема слова на третьем выходе группы 102 управляющих выходов устанавливается сигнал Y14, который свидетельствует о достоверности принятого слова. Оба эти сигнала воспринимаются соответственно первым и третьим входами третьей группы 59 входов блока 8 управления, в результате чего с его восьмого выхода 74 отправляется импульсный сигнал Y15 к входу 115 стробирования второго регистра 17. Тем самым в последний с группы 111 параллельных выходов последовательно-параллельного преобразователя 16 заносится ответное слово, переданное на группу 113 входов второго регистра 17. Сразу же с его группы 114 выходов ОС направляется к второй группе 121 входов второго мультиплексора 19.

Далее начинается организация цикла записи в ОП вычислительной системы по адресу ввода ОС. Для этого вновь сигналом Y1 запрашивается возможность прямого доступа к ОП и принимается разрешение в виде сигнала Y2. Затем сигналом Y3, появляющимся на первом выходе 67 блока 8 управления, реверсируется второй шинный формирователь 2 и коммутируется часть связей первого шинного формирователя 1 описанным выше образом. По сигналу Y16, приходящему с второго выхода второй группы 61 выходов блока 8 управления на второй вход группы 49 входов управления блока 7 регистров, последний выставляет через свою группу 53 адресных выходов и второй шинный формирователь 2 в СМ адрес ячейки ОП, предназначенной для хранения принятого ОС.

Сигнал Y17 выставляется на пятом выходе 71 блока 8 управления и по входу 123 управления второго мультиплексора 19 переводит его в положение, когда содержимое второго регистра 17 с второй группы 121 входов попадает на группу 122 выходов и далее к группе 38 информационных входов третьего шинного формирователя 3. Кроме того, с второго выхода 68 блока 8 управления направляется сигнал Y18 на вход 40 управления третьего шинного формирователя 3, который также реверсируется в положение передачи сигналов и пропускает ОС со своей группы 38 информационных входов через группу 21 информационных входов-выходов устройства в шину данных СМ.

Вслед за этим на втором выходе первой группы 60 выходов блока 8 управления формируется стробирующий сигнал Y19 записи, который по второму входу первой группы 25 информационных входов и второму входу второй группы 28 информационных выходов первого шинного формирователя 1 направляется в шину сигналов управления СМ.

Расшифровав адрес и получив сигнал Y19, системная ОП принимает ОС с шины данных и выставляет ответный сигнал Y6, который приходит к четвертому входу первой группы 57 входов блока 8 управления. Затем последовательно снимаются сигналы Y19, Y6, Y1 - Y3, Y17, Y18, Y16 и с шестого выхода второй группы 61 выходов на шестой вход группы 49 входов управления блока регистров направляются счетные импульсы. Сч3 для формирования адреса ввода последующего ОС.

Если в исходных данных не предусматривался прием массива ИС в ОП, то происходит снятие сигнала Y11 с второго выхода четвертой группы 63 выходов блока 8 управления. Тем самым запрещается работа дешифратора 15 сигналов линии и на этом работа устройства сопряжения заканчивается.

В противном случае вслед за ОС с магистрали последовательного интерфейса поступают один за другим ИС. Каждое из них также преобразуется в усилителе-приемнике 14, дешифраторе 15 сигналов линии и накапливается в последовательно-параллельном преобразователе 16. Прием ИС сопровождается присутствием сигнала Y20 на втором выходе группы 102 управляющих выходов дешифратора 15 сигналов линии. По окончании приема слова на третьем выходе группы 102 управляющих выходов устанавливается сигнал Y14. Оба эти сигнала воспринимаются вторым и третьим входами третьей группы 59 входов блока 8 управления. В результате этого с его восьмого выхода 74 вновь отправляется импульсный сигнал Y15 к входу 115 стробирования второго регистра 17, в который записывается принятое ИС.

В следующий момент блок 8 управления организует новый цикл записи в ОП, но теперь уже по адресу ввода ИС. Этот цикл записи в ОП от первого отличается тем, что сигнал Y16 не формируется, а с третьего выхода второй группы 61 выходов блока 8 управления на третий вход группы 49 входов управления блока 7 регистров приходит сигнал Y21, вызывающий установку на группе 53 адресных выходов адрес ячейки ОП, предназначенной для хранения принятого ИС.

В завершении цикла с седьмого и восьмого выходов второй группы 61 выходов соответственно на седьмой и восьмой входы группы 49 входов управления блока 7 регистров посылаются счетные импульсы Сч4, формирующие адрес ввода следующего ИС, и счетный импульс Сч5, декрементирующий информацию о длине массива.

ИС принимаются до тех пор, пока не заполнится отведенное для них количество ячеек ОП. Появление нулевой информации о длине массива вызывает образование сигнала Y10, который поступает в блок 8 управления описанным выше образом и приводит к снятию сигнала Y11 с второго выхода четвертой группы 63 выходов, что останавливает дешифратор 15 сигналов линии и завершает работу устройства сопряжения в целом.

Этот факт фиксируется установкой в блоке 7 регистров признака "окончание взаимодействия" посредством импульсного сигнала Y22, который попадает туда через девятый вход группы 49 входов управления с девятого выхода второго группы 61 выходов блока 8 управления.

Следует отметить, что запись ИС во второй регистр 17 возможна только в том случае, если ранее было принято ОС. Такая зависимость предотвращает прием ИС без предшествующего ответного слова, содержащего адрес абонента.

Режим II ("самопроверка") отличается от режима I тем, что устройство сопряжения не осуществляет взаимодействие с магистралями во время работы. Кроме того, процессы передачи и приема слов происходят одновременно.

Для проведения "самопроверки" требуется, чтобы в исходных данных адрес вывода ИС был одинаков с адресом ввода ИС, а адрес вывода КС - с адресом ввода ОС.

В режиме II устанавливается сигнал Y23, который попадает с девятого выхода 75 блока 8 управления на вход 96 выключения усилителя-передатчика 13, блокируя его работу, а также с первого выхода четвертой группы 63 выходов на первый вход группы 101 входов управления дешифратора 15 сигналов линии, выключая первый и второй информационные входы 103 и 104 и включая вход 105 контрольных данных. Таким образом отключается магистраль последовательного интерфейса.

Затем имитируется цикл чтения ОП. В отличие от настоящего цикла не формируются сигналы Y1, Y2, зато появляется на третьем выходе 69 блока 8 управления сигнал Y24, который подходит к входу 79 управления мультиплексора 9 и к входам 30, 36 и 41 выключения первого, второго и третьего шинных формирователей 1-3. Этот сигнал отключает СМ, закрывая шинные формирователи 1-3, и, кроме того, переводит первый мультиплексор 9 на прием по второй группе 77 входов.

Далее по сигналу Y4, описанному выше, блок 7 регистров выставляет адрес вывода КС, который направляется через первый мультиплексор 9 на группу 80 входов первого регистра 10, где он интерпретируется как КС. Сигналы Y5, Y6 здесь не участвуют в работе устройства, а сразу же появляются импульсный сигнал Y7 и затем сигнал Y8, запускающие описанным выше образом тракт передачи, и контрольное КС в виде комбинации униполярных сигналов с второго информационного выхода 92 шифратора 12 сигналов линии попадает на вход 105 контрольных данных дешифратора 15 сигналов линии. Сигнал Y4 снимается после выдачи сигнала Y7.

Поскольку сигнал Y11 в режиме II появляется сразу же после запуска, то контрольное КС проходит через тракт приема описанным образом и фиксируется во втором регистре 17. Здесь следует отметить, что начальный адрес вывода КС при "самопроверке" должен устанавливаться таким образом, чтобы адресная часть контрольного КС совпадала с адресом абонента, заданным в исходных данных.

После приема контрольного КС блок 8 управления имитирует цикл записи в ОП. При этом в отличие от настоящего цикла не инициируются сигналы Y1, Y2, а вновь устанавливается сигнал Y24, который отключает СМ. На второй вход группы 49 входов управления блока 7 регистров поступает сигнал Y16 и на группе 53 адресных выходов появляется адрес ввода ОС, попадающий на первую группу 116 входов второго элемента 18 сравнения. Второй мультиплексор 19, переключившись по сигналу Y17, посылает контрольное КС от группы 114 выходов второго регистра 17 к второй группе 117 входов второго элемента 18 сравнения. Вместо сигнала Y19 формируется импульсный сигнал Y25, который с четвертого выхода 70 блока 8 управления попадает на стробирующий вход 118 второго элемента 18 сравнения. При несовпадении адреса ввода ОС с контрольным КС сигнал Y25 через выход 119 по входу 55 устанавливает в блоке 7 регистров признак "нарушение взаимодействия". Сигнал Y24 снимается после выдачи сигнала Y25.

Таким образом, адрес вывода КС в качестве контрольного слова транслируется по трактам передачи и приема, а затем сравнивается с адресом ввода ОС. Если контрольное слово искажается или не приходит, то сравнение не происходит и результат "самопроверки" отрицательный.

При задании в исходных данных некоторой длины массива вслед за контрольным КС посылаются контрольные ИС, составленные из адресов вывода ИС, формируемых так же, как в режиме I. Контрольные ИС после прогона по трактам передачи и приема сравниваются с адресами ввода ИС. Обнуление информации о длине массива ведет к образованию сигнала Y10, поступающего на второй вход второй группы 58 входов блока 8 управления. Тогда последний прекращает составление контрольных слов и снимает сигнал Y11. В тот же момент с девятого выхода второй группы 61 выходов в блок 7 регистров отправляется импульсный сигнал Y22, который устанавливает признак "окончание взаимодействия". Таким образом режим II обеспечивает проверку работоспособности почти всего оборудования устройства сопряжения без выхода на магистрали и в условиях, максимально схожих с режимом I.

В любом режиме, в любое время, кроме моментов обращения (или имитации обращения) к ОП, со стороны СМ можно прочитать признаки состояния устройства. Для этого на группу 20 адресных входов-выходов устройства подается адрес регистра, содержащего эти признаки. Вслед за этим по пятому входу второй группы 26 информационных входов и информационному выходу 31 первого шинного формирователя 1 поступает сигнал чтения, который направляется на стробирующий вход 44 дешифратора 4 адресов. Далее в соответствии с полученным адресом он в виде сигнала Y26 отправляется с выхода 45 к тертьему входу 66 блока 8 управления. Тут же на втором выходе 68 возникает сигнал Y18, реверсирующий третий шинный формирователь 3 в положение передачи сигналов. Так как второй мультиплексор 19 находится в исходном положении, то информация о состоянии устройства сопряжения с группы 54 информационных выходов блока 7 регистров по первой группе 120 входов второго мультиплексора 19 направляется через группу 122 выходов к группе 38 информационных входов третьего шинного формирователя 3 и далее в шину данных СМ.

Параллельно с этим сигнал чтения подобно сигналу записи с пятого выхода первой группы 27 информационных выходов первого шинного формирователя 1 поступает в блок 8 управления, который после некоторой паузы отправляет сигнал подтверждения передачи информации через пятый выход второй группы 28 информационных выходов первого шинного формирователя 1 в шину сигналов управления СМ. Прочитав признаки состояния устройства сопряжения, См снимает сигнал чтения и освобождает адресную шину. Это приводит к исчезновению сигнала Y18, возвращению третьего шинного формирователя 2 в исходное состояние и освобождению шины данных.

Все шинные формирователи 1-3 (фиг.1) выполняют функции электрического сопряжения линий и усиления сигналов. Второй и третий шинные формирователи 2 и 3 представляют собой наборы приемопередатчиков, имеющих общую схему управления направлением передачи и выключенным состоянием. При наличии лог. "1" на входах 36, 41 выключения группы 34, 39 информационных выходов и группы 32, 37 информационных входов-выходов второго и третьего шинных формирователей 2 и 3 переходят в высокоимпендансное состояние ("выключено"). При наличии лог."0" на входах 36, 41 выключения и входах 35, 40 управления шинные формирователи 2, 3 поразрядно транслируют сигналы от групп 32, 37 информационных входов-выходов соответственно к группам 34, 39 информационных выходов. При наличии лог."0" на входах 36, 41 выключения и лог."1" на входах 35, 40 управления сигналы транслируются от групп 33, 38 информационных входов соответственно к группам 32, 37 информационных входов-выходов. Такое схемное построение шинных формирователей известно (УДК 621.3.049.77.037.372.001.63 (035) Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. Справочник, М.: Радио и связь, 1990, с.57, рис.2.24у).

Блок 7 регистров (фиг.3) работает следующим образом.

В исходном состоянии разряды первого регистра 129 сброшены, а селектор 132 находится во втором положении, т.е. вторая группа информационных входов соединяется с группой информационных выходов.

Во время введения в блок 7 регистров исходных данных информация по группе 50 информационных входов подходит одновременно к группам информационных входов первого-пятого счетчиков 124-128 и второго регистра 130. Затем по одному из шести входов группы 51 стробирующих входов, определенному в соответствии с полученным адресом, поступает сигнал записи на стробирующий вход одного из счетчиков 124у-128 или второго регистра 130 и производит запись информации в выбранный объект.

Первый-четвертый счетчики 124-127 предназначены для хранения адресов ячеек ОП соответственно вывода КС, вывода ИС, ввода ОС и ввода ИС. Пятый счетчик 128 содержит информацию о длине массива ИС, передаваемого или принимаемого устройством сопряжения. Во второй регистр 130 записывается управляющее слово.

Селектор 132 имеет четыре положения, при которых его группа информационных выходов связана с первой, второй, третьей или четвертой группами информационных входов. Сигналы Y4, Y16, Y21 поочередно поступают соответственно по первому-третьему входам группы 49 входов управления блока 7 регистров на первый-третий входы группы входов управления селектора 132, который устанавливается ими соответственно в первое, третье и четвертое положения, и тем самым пропускают на группу 53 адресных выходов блока 7 регистров адреса вывода КС, ввода ОС или ввода ИС с групп информационных выходов соответственно первого, третьего и четвертого счетчиков 124, 126 и 127. Адрес вывода ИС с группы информационных выходов второго счетчика 125 на группу 53 адресных выходов блока 7 регистров пропускается селектором 132 в исходном (втором) положении при отсутствии управляющих сигналов.

Дешифратор 131 нуля анализирует содержимое пятого счетчика 128 и при обнулении последнего вырабатывает сигнал Y10, который направляется к второму выходу группы 52 управляющих выходов блока 7 регистров. К первому выходу группы 52 управляющих выходов поступает основная часть управляющей информации с второго информационного выхода второго регистра 130. К выходу 56 блока 7 регистров с первого информационного выхода второго регистра 130 приходит адрес абонента магистрали последовательного интерфейса, содержащийся в управляющем слове.

В определенные моменты работы устройства сопряжения на четвертом-восьмом входах группы 49 входов управления блока 7 регистров и первых входах соответственно первого-пятого счетчиков 124-128 появляются счетные импульсы Сч1-Сч5 соответственно, которые преобразуют содержимое этих счетчиков. Первый-четвертый счетчики 124-127 функционируют на сложение, а пятый счетчик 128 - на вычитание. Когда работа устройства сопряжения в целом заканчивается, то по девятому входу группы 49 входов управления блока 7 регистров на первый вход первого регистра 129 приходит импульсный сигнал Y22 и устанавливает в одном из разрядов признак "окончание взаимодействия".

В режиме II ("самопроверка") на входе 55 блока 7 регистров может появиться импульсный сигнал Y25, который, попав на второй вход первого регистра 129, устанавливает в последнем признак "нарушение взаимодействия".

Слово состояния устройства сопряжения постоянно присутствует на группе информационных выходов первого регистра 129 и группе 54 информационных выходов блока 7 регистров.

Блок 8 управления (фиг.4 и 5) работает следующим образом. В исходном состоянии сигналы управления отсутствуют. Первой появляется управляющая информация на первом входе второй группы 58 входов, которая воспринимается дешифратором 133 команд.

Признак запуска в виде потенциального сигнала направляется седьмым выходом 155 к одновибратору 134. Отсюда подается импульс запуска на третьи входы 158, 174 и узлов 135, 136 управления передачей и приемом. Одновременно с этим в режиме I с третьего выхода 151 дешифратора 133 команд на первый вход 156 узла 135 управления передачей поступает разрешение. Последний запускается, начиная организацию цикла чтения ОП и выставляя на своем пятом выходе 169 запрос доступа к ОП. Этот сигнал проходит приоритетный шифратор 137, четвертый элемент ИЛИ 146 и активизирует блок 138 триггеров прямого доступа по второму входу 187. С первого выхода группы 185 выходов на третий выход первой группы 60 выходов блока 8 управления отправляется сигнал Y1 запроса СМ.

После того, как через первый вход первой группы 57 входов на первый вход группы 184 входов блока 138 триггеров прямого доступа придет сигнал Y2 разрешения, на выходе 188 выставляется сигнал Y3, который поступает к первому выходу 67 блока 8 управления и вторым входам третьего и четвертого элементов И 141 и 142. Приоритетный шифратор 137 допускает проникновение сигналов Y3 только через третий элемент И 141, направляя его к шестому входу 161 узла 135 управления передачей. Далее упомянутый сигнал инициирует на первом выходе первой группы 163 выходов сигнал Y4, который отправляется на первый выход второй группы 61 выходов блока 8 управления.

После небольшой задержки с третьего выхода 167 узла 135 управления передачей к первому выходу первой группы 60 выходов блока 8 управления уходит стробирующий сигнал Y5 чтения ОП. Здесь происходит ожидание по четвертому входу первой группы 57 входов ответного сигнала Y6, который поступает через первый элемент ИЛИ 143 на седьмой вход 162 узла 135 управления передачей. С второго выхода 166 к седьмому выходу 73 блока 8 управления отправляется импульс Y7.

Затем снимается сигнал Y5, пропадает сигнал Y6, убирается запрос доступа к ОП с пятого выхода 169 и соответственно с второго входа 187 блока 138 триггеров прямого доступа, который тут же блокирует выдачу сигналов Y3, Y1. Вслед за этим исчезают сигналы Y4 и Y2. Таким образом завершается проведение цикла чтения ОП.

Импульс Y7 приводит к появлению сигнала Y8, который поступает на второй выход третьей группы 62 выходов и шестой выход 72 блока 8 управления с четвертого выхода 168 узла 135 управления передачей. Далее с второго выхода первой группы 163 выходов по четвертому выходу второй группы 61 выходов отправляются счетные импульсы Сч1. Затем по первому входу 64 блока 8 управления на пятый вход 160 узла 135 управления передачей поступает сигнал Y9, снимающий сигнал Y8.

Если в управляющем слове задана передача массива ИС из ОП, то на четвертом выходе 152 дешифратора 133 команд и, следовательно, на втором входе 157 узла 135 управления передачей присутствует разрешение дальнейшей работы последнего. Если на его четвертом входе 159 нет сигнала Y10, то пропадание сигнала Y8 приводит к организации нового цикла чтения ОП описанным выше образом с той лишь разницей, что сигнал Y4 не формируется.

Очередное появление сигнала Y8 вызывает возникновение на третьем и четвертом выходах первой группы 163 выходов узла 135 управления передачей и соответственно пятом и восьмом выходах второй группы 61 выходов блока 8 управления счетных импульсов Сч2 и Сч5. Снятие сигнала Y8 ведет опять к организации цикла чтения ОП (без сигнала Y4). Это повторяется до тех пор, пока с второго входа второй группы 58 входов на четвертом входе 159 узла 135 управления передачей не возникнет сигнал Y10, который предотвращает следующий цикл чтения ОП по очередному пропаданию сигнала Y8. Снятие сигнала Y9 при наличии сигнала Y10 влечет за собой создание импульсного сигнала передачи управления на первом выходе второй группы 164 выходов узла 135 управления передачей, который завершает на этом свою работу.

Если в управляющем слове не задана передача массива ИС из ОП, то на четвертом выходе 152 дешифратора 138 команд не появляется сигнал разрешения дальнейшей работы. Следовательно, после самого первого цикла чтения ОП, когда устанавливается, а затем снимается сигнал Y9, независимо от наличия сигнала Y10 происходит прекращение функционирования узла 135 управления передачей с выдачей импульса передачи управления.

Этот импульс по первому входу первой группы 170 входов приводит в действие узел 136 управления приемом, который сразу же вставляет с первого выхода 180 на второй выход четвертой группы 63 выходов блока 8 управления сигнал Y11. После этого ожидается сигнал Y14, который заходит по третьему входу третьей группы 59 входов и принимается узлом 136 управления приемом по третьему входу второй группы 171 входов, что приводит к возникновению на втором выходе 181 и восьмом выходе 74 импульсного сигнала Y15. Одновременно начинается цикл записи в ОП установкой запроса доступа к ОП на четвертом выходе 183. Этот запрос проходит приоритетный шифратор 137, четвертый элемент ИЛИ 146 и активизирует блок 138 триггеров прямого доступа по второму входу 187.

Так же как и раньше уходит сигнал Y1 запроса СМ, приходит сигнал Y2 разрешения, а с выхода 188 выставляется сигнал Y3. Приоритетный шифратор 137 пропускает сигнал Y3 через четвертый элемент И 142, направляя его в виде сигнала Y17 к пятому выходу 71 блока 8 управления и к шестому входу 177 узла 136 управления приемом, а в виде сигнала Y18 - через второй элемент ИЛИ 144 к второму выходу 68 блока 8 управления.

Сигнал Y17 заставляет появиться на втором выходе группы 179 выходов узла 136 управления приемом и втором выходе второй группы 61 выходов блока 8 управления сигналу Y16, а после некоторой задержки на третьем выходе 182 и втором выходе первой группы 60 выходов блока 8 управления возникает стробирующий сигнал Y19 записи в ОП. Ответный сигнал Y6 ожидается по четвертому входу первой группы 57 входов и через третий элемент ИЛИ 145 на седьмом входе 178 узла 136 управления приемом. После его прихода последовательно убираются сигналы Y19, Y6, запрос доступа к ОП сигнал Y1-Y3, Y17, Y18, Y16. Таким образом заканчивается проведение цикла записи в ОП. И сразу же с четвертого выхода группы 179 выходов узла 136 управления приемом к шестому выходу второй группы 61 выходов блока 8 управления отправляются счетные импульсы Сч3.

Если в управляющем слове задан прием массива ИС в ОП, тона шестом выходе 154 дешифратора 133 команд и, следовательно, на втором входе 173 узла 136 управления приемом присутствует разрешение дальнейшей работы последнего. Если на его четвертом входе 175 нет сигнала Y10, то он ожидает появления сигнала Y14 по третьему входу второй группы 171 входов.

Здесь начинается организация нового цикла записи в ОП описанным выше образом, но только сигнал Y16 заменяется сигналом Y21, который отправляется с третьего выхода группы 179 выходов к третьему выходу второй группы 61 выходов. В завершении цикла с пятого и первого выходов группы 179 выходов, а также соответственно с седьмого и восьмого выходов второй группы 61 выходов блока 8 управления отправляются счетные импульсы Сч4, Сч5.

Это повторяется до тех пор, пока к четвертому входу 175 узла 136 управления приемом с второго входа второй группы 58 входов блока 8 управления не придет сигнал Y10, который после очередного цикла записи в ОП блокирует сигнал Y11 на первом выходе 180. В тот же момент с шестого выхода группы 179 выходов узла 136 управления приемом на девятый выход второй группы 61 выходов блока 8 управления поступает импульсный сигнал Y22.

Если в управляющем слове не был задан прием массива ИС в ОП, то на шестом выходе 154 дешифратора 133 команд не присутствует сигнал разрешения дальнейшей работы. Следовательно, сразу же после первого цикла записи в ОП снимается сигнал Y11 и формируется импульс Y22 независимо от наличия сигнала Y10. На этом прекращается функционирование узла 136 управления приемом и устройства сопряжения в целом.

В режиме II работа блока 8 управления несколько отличается от описанной в режиме I. Первым на первом выходе четвертой группы 63 выходов и девятом выходе 75 блока 8 управления с первого выхода 149 дешифратора 133 команд устанавливается сигнал Y23. С второго выхода 150 сигнал СП заходит на первые входы первого элемента ИЛИ 143, первого и второго элементов И 139 и 140, а также по первому входу 186 переключает блок 138 триггеров прямого доступа, который напрямую соединяет второй вход 187 с выходом 188. Кроме того, на третьем и пятом выходах 151 и 153 дешифратора 133 команд и соответственно на первых входах 156, 172 узлов 135 и 136 управления передачей и приемом одновременно присутствуют сигналы разрешения.

Признак запуска при помощи одновибратора 134 по третьим входам 158, 174 одновременно включает в работу узлы 135 и 136 управления передачей и приемом. Узел 136 управления приемом отправляет с первого выхода 180 сигнал Y11 и останавливается в ожидании сигнала Y14. Узел 135 управления передачей своим запросом доступа к ОП по пятому выходу 169 начинает имитацию цикла чтения. Этот сигнал проходит через приоритетный шифратор 137, четвертый элемент ИЛИ 146 и далее пропускается вторым элементом И 140 к третьему выходу 69 блока 8 управления в виде сигнала Y24. С другой стороны, блок 138 триггеров прямого доступа сразу же формирует на своем выходе 188 сигнал Y3, направляющийся к первому выходу 67 блока 8 управления и через третий элемент И 141 к шестому входу 161 узла 135 управления передачей, который отправляет сигнал Y4 к первому выходу второй группы 61 выходов блока 8 управления. После небольшой задержки на третьем выходе 167 узла 135 управления передачей выставляется сигнал Y5, который в режиме II не влияет на работу схемы. Поскольку через первый элемент ИЛИ 143 на седьмом входе 162 постоянно удерживается сигнал СП, то на втором выходе 166 формируется импульс Y7. Затем последовательно снимаются запрос доступа к ОП с пятого выхода 169, сигналы Y24, Y3, Y4.

Через некоторое время на четвертом выходе 168 инициируется сигнал Y8, появление которого сопровождается формированием счетных импульсов Сч1. Возникновение сигнала Y9 на пятом входе 160 при отсутствии сигнала Y10 и наличии на втором входе 157 разрешения дальнейшей работы приводит к имитации нового цикла чтения ОП. Во время второй и последующих имитаций цикла чтения ОП не выставляется сигнал Y4, а после них вместо импульсов Сч1 формируются счетные импульсы Сч2, Сч5.

Каждое последующее (кроме первого) появление сигнала Y8 происходит не сразу после выдачи импульса Y7, а спустя определенное время. В эти паузы (начиная с второй) на третий вход второй группы 171 входов узла 136 управления приемом приходит сигнал Y14 и вызывает имитацию цикла записи в ОП посредством запроса доступа к ОП с четвертого выхода 183. Известным образом создаются сигналы Y24, Y3, Y17, Y18, Y16 и Y19, последний из которых первым элементом И 139 направляется к четвертому выходу 70 блока 8 управления в виде сигнала Y25. После небольшой задержки сигналы снимаются, завершая имитацию цикла записи в ОП. Затем выдаются счетные импульсы Сч3. Возможность последующих имитаций цикла записи в ОП определяется наличием на втором входе 173 узла 136 управления приемом разрешения дальнейшей работы, которая в режиме "самопроверка" устанавливается синхронно на четвертом и шестом выходах 152 и 154 дешифратора 133 команд. Во время второй и последующих имитаций цикла записи в ОП сигнал Y16 заменяется сигналом Y21, а после них вместо импульсов Сч3 формируются счетные импульсы Сч4, Сч5.

Таким образом получается, что в режиме II узел 135 управления передачей и узел 136 управления приемом функционируют поочередно. Такая работа блока 8 управления продолжается до тех пор, пока сигнал Y10 не блокирует имитацию циклов чтения и записи в ОП. В этом случае убирается сигнал Y11, появляется импульс Y22 и на этом все заканчивается.

В любом режиме во время пауз между циклами доступа к системной памяти или после прекращения работы блока 8 управления по пятому входу первой группы 57 входов может прийти сигнал обращения к устройству сопряжения (записи или чтения) со стороны СМ, который через второй элемент 148 задержки отправляется по пятому выходу первой группы 60 выходов в СМ в качестве сигнала подтверждения передачи информации. Одновременно на третьем входе 66 может появиться сигнал Y26, сразу попадающий через второй элемент ИЛИ 144 на второй выход 68 в виде сигнала Y18.

Шифратор 12 сигналов линии (фиг. 1) работает следующим образом. На стробирующий вход 90 постоянно поступают синхроимпульсы. Появление сигнала Y8 на втором входе группы 87 входов управления активизирует шифратор 12 сигналов линии, который в зависимости от наличия или отсутствия сигнала на первом входе группы 87 входов управления отправляет на первый и второй информационные выходы 91 и 92, работающие в паре, признак ИС или КС.

Затем по первому и второму выходам группы 88 управляющих выходов выдаются соответственно сигнал запроса данных и импульсы синхронизации передаваемой информации. Одновременно по входу 89 данных последовательно принимаются биты транслируемого слова, которые уже в бифазном фазоманипулированном коде поступают на первый и второй информационные выходы 91 и 92. На всем протяжении выдачи слова данных на управляющем выходе 93 присутствует сигнал Y9, совпадающий по времени с сигналом запроса данных. Как только будет передан последний бит слова, снимаются все сигналы на выходах шифратора 12 сигналов линии, который ожидает нового появления запускающего сигнала Y8. Такое исполнение шифратора известно под названием кодер мультиплексного канала (УДК 681.3.01(031) Хвощ С.Т. и др. Микропроцессоры и микроЭВМ в системах автоматического управления. Справочник. - Л.: Машиностроение. Ленингр. отделение, 1987, с.236-239).

Дешифратор 15 сигналов линии (фиг.1) работает следующим образом. На стробирующий вход 106 постоянно поступают синхроимпульсы. Появление сигнала Y11 на втором входе группы 101 входов управления разрешает работу дешифратора 15 сигналов линии, который начинает следить за появлением бифазных импульсов фазоманипулированного кода на первом и втором информационных входах 103 и 104, работающих в паре. В первую очередь на этих входах должен появиться признак ОС или ИС, при распознании которого начинается прием и преобразование поступающего слова. При этом по выходу 107 данных выдаются биты информации, а по управляющему выходу 108 - синхроимпульсы и разрешение записи. Процесс приема ОС или ИС сопровождается наличием сигнала Y13 или Y20 соответственно на первом или втором выходе группы 102 управляющих выходов. Прием завершается контролем слова на достоверность. При положительном результате контроля на третий выход группы 102 управляющих выходов выдается сигнал Y14. Далее дешифратор 15 сигналов линии вновь ожидает прихода признака ОС или ИС. Кроме асинхронного приема слов по первому и второму информационным входам 103 и 104 возможен прием синхронизированных слов по входу 105 контрольных данных. Для включения этого режима необходима подача сигнала Y23 на первый вход группы 101 входов управления. Такое исполнение дешифратора известно под названием декодер мультиплексного канала (Микросхема 588ВГЗ. Техническое описание дРЗ.482.033-08 ТО).

Узел 1355 управления передачей (фиг.6) работает следующим образом. В исходном состоянии все внешние сигналы отсутствуют, все триггеры 189-195 сброшены. Работа начинается с подачи на первый вход 156 узла 135 управления передачей и информационный вход первого D-триггера 189 сигнала разрешения запуска, а на третий вход 158 и вход синхронизации первого D-триггера 189 - импульса запуска. Первый D-триггер 189 взводится, снимая обнуление своим инверсным выходом с входом сброса первого RS-триггера 193, счетного триггера 195, третьего D-триггера 191 через первый элемент ИЛИ 207 и второго RS-триггера 194 через второй элемент ИЛИ 208, а своим прямым выходом с входа сброса четвертого D-триггера 192 через элемент И-НЕ 206. На входах первого элемента И 199 собираются три лог."1": на первом входе с прямого выхода первого D-триггера 189, на втором с инверсного выхода первого RS-триггера 193 через четвертый элемент ИЛИ 210 и на третьем с инверсного выхода третьего D-триггера 191 через четвертый элемент 216 задержки. В результате с выхода первого элемента И 199 на пятый выход 169 узла 135 управления передачей выставляется сигнал запроса доступа к ОП для чтения КС.

Ответный сигнал Y3 проникает через шестой вход 161 к второму входу третьего элемента И 201, на первом входе которого присутствует лог."1" с инверсного выхода первого RS-триггера 193. С выхода третьего элемента И 201 по первому выходу первой группы 163 выходов узла 135 управления передачей отправляется сигнал Y4, управляющий селектором 132 (фиг.2).

Чуть позже, пройдя пятый элемент 217 задержки, сигнал Y3 попадает на второй вход седьмого элемента И 205, на первом входе которого удерживаетcя лог. "1" c инверcного выхода третьего D-триггера 191. С выхода cедьмого элемента И 205 по третьему выходу 167 узла 135 управления передачей отправляется сигнал Y5, стробирующий обмен по СМ.

Ответный сигнал Y6 от системной ОП через седьмой вход 162 приходит к первому входу шестого элемента И 204, второй вход которого проверяет наличие сигнала Y5. Лог."1" с выхода шестого элемента И 204 в виде сигнала Y7 направляется к второму выходу 166 узла 135 управления передачей, а также своим появлением взводит по входу синхронизации четвертый D-триггер 192, который своим прямым выходом взводит по входу взведения второй RS-триггер 194.

Лог."0", возникший на инверсном выходе второго RS-триггера 194, попадает на второй вход элемента И-НЕ 206, с выхода которого на вход сброса четвертого D-триггера 192 приходит лог. "1", и он вновь сбрасывается. Кроме того, лог."0" направляется к инверсному 212, на выходе которого появляется сигнал Y8, поступающий на четвертый вход 168 узла 135 управления передачей. Третий одновибратор 198 не реагирует на появление лог."0" на своем входе. Сигнал Y8 запускает второй одновибратор 197, который направляет через пятый элемент ИЛИ 211 на второй вход четвертого элемента И 202 первый счетный импульс Сч1. Этот импульс проходит на второй выход первой группы 163 выходов, так как на первом входе четвертого элемента И 202 удерживается лог."1" с инверсного выхода первого RS-триггера 193.

Выдержав необходимое время, второй элемент 214 задержки пропускает сигнал Y8 для запуска первого одновибратора 196, который направляет второй счетный импульс Сч1 через пятый элемент ИЛИ 211, четвертый элемент И 202 на второй выход первой группы 163 выходов. Эта линия соединена со счетным входом первого счетчика 124 (фиг.2), содержимое которого дважды инкрементируется под воздействием счетных импульсов Сч1.

Как только эти импульсы отправлены, сигналом Y8 через первый элемент 213 задержки по входу взведения взводится первый RS-триггер 193, производя следующие изменения: запрещается в дальнейшем открытие третьего и четвертого элементов И 201-202, на втором входе четвертого элемента ИЛИ 210 появляется лог. "0" и устанавливается лог."1" на первом входе пятого элемента И 203, а через первый выход 165 узла 135 управления передачей производится переключение шифратора 12 сигналов линии (фиг.1) на выдачу в дальнейшем ИС. Если на втором входе 157 узла 135 управления передачей отсутствует разрешение дальнейшей работы или на четвертом входе 159 присутствует инверсный сигнал Y10, то с выхода второго элемента И 200 на первом входе четвертого элемента ИЛИ 210 присутствует лог."0". В этом случае четвертый элемент ИЛИ 210 снимет лог."1" с второго входа первого элемента И 199, блокируя последний, а второй D-триггер 190 освобождается от обнуляющего сигнала по своему входу сброса. Если на втором входе 157 присутствует разрешение дальнейшей работы, а на четвертом входе 159 инверсный сигнал Y10 еще не появился, то четвертый элемент ИЛИ 210 по-прежнему удерживает лог."1" на своем выходе.

После необходимой паузы третий элемент 215 задержки пропускает сигнал Y7 на вход синхронизации третьего D-триггера 191, который взводится и своим инверсным выходом снимает лог."1" с первого входа седьмого элемента И 205. Тем самым убираются сигналы Y5, Y6, Y7. Чуть позже через четвертый элемент 216 задержки снимается лог."1" с третьего входа первого элемента И 199 и прекращается выдача с его выхода сигнала запроса доступа к ОП, что приводит к снятию Y3.

В какой-то момент времени на пятом входе 160 узла 135 управления передачей появится сигнал Y9. На второй D-триггер 190 он влияния не оказывает. Однако, пройдя через второй элемент ИЛИ 208, сигнал Y9 попадает на вход сброса второго RS-триггера 194 и сбрасывает его. Тем самым на инверсном выходе последнего восстанавливается лог."1", снимается через элемент И-НЕ 206 обнуление с входа сброса четвертого D-триггера 192, пропадает сигнал Y8 с выхода инвертора 212, с четвертого выхода 168 узла 135 управления передачей и с некоторой задержкой с входа взведения первого RS-триггера 193. Замена лог. "0" на лог. "1" на входе третьего одновибратора 198 запускает его, возникнувший импульс через первый элемент ИЛИ 207 направляется к входу сброса третьего D-триггера 191 и последний обнуляется. Тем самым вновь устанавливается лог. "1" на первом входе седьмого элемента И 205 и третьем входе первого элемента И 199.

В том случае, если на выходах второго элемента И 200 и четвертого элемента ИЛИ 210 удерживается лог."1" описанным выше способом, то с выхода первого элемента И 199 и пятого выхода 169 узла 135 управления передачей вновь отправляется сигнал запроса доступа к ОП для чтения ИС. Вновь поступает ответный сигнал Y3 через шестой вход 161. Однако сигнал Y4 не формируется, так как первый RS-триггер 193 взведен и третий элемент И 201 закрыт. Только сигнал Y5 отправляется описанным образом. Также появляются сигналы Y6, Y7, взводится четвертый D-триггер 192, подавая лог."1" на вход взведения второго RS-триггера 194. Однако на его инверсном выходе сохраняетcя лог."1", так как на входе сброса продолжает присутствовать сигнал Y9.

После паузы через третий элемент 215 задержки сигналом Y7 взводится третий D-триггер 191, который описанным выше образом снимает сигналы Y5-Y7 и прекращает цикл доступа к системной ОП.

Пропадание сигнала Y9 не оказывает воздействия на второй D-триггер 190, так как на его входе сброса присутствует лог."1". Снятие обнуляющего сигнала Y9 с входа сброса второго RS-триггера 194 ведет к взведению последнего и появлению сигнала Y8.

Сигнал Y8 известным образом вызывает срабатывание первого и второго одновибраторов 196 и 197. Два счетных импульса Сч2 и выхода пятого элемента ИЛИ 211 попадают на третий выход первой группы 163 выходов через пятый элемент И 203, так как на первом входе последнего присутствует лог."1" с прямого выхода первого RS-триггера 193. Кроме того, импульсы Сч2 попадают на тактовый вход счетного триггера 195. Первый импульс Сч2 взводит, а второй сбрасывает счетный триггер 195, на прямом выходе которого и четвертом выходе первой группы 163 выходов образуется одиночный импульсный сигнал Сч5. Третий выход первой группы 163 выходов узла 135 управления передачей соединен со счетным входом второго счетчика 125 (фиг.2), содержимое которого дважды инкрементируется под воздействием счетных импульсов Сч2. Четвертый выход первой группы 163 выходов соединен со счетным входом пятого счетчика 128, содержимое которого декрементируется под воздействием импульса Сч5.

Повторное появление сигнала Y9 и снятие сигнала Y8 приводит к повторному сбросу третьего D-триггера 191 и созданию условий для следующего обращения к ОП. Здесь снова проверяется наличие лог."1" на выходе четвертого элемента ИЛИ 210, и затем работа схемы проверяется по варианту чтения ИС.

В том случае, если после очередного импульса Сч5 с выхода дешифратора 131 нуля (фиг.2) через четвертый вход 159 узла 135 управления передачей на второй вход второго элемента И 200 поступает инверсный сигнал Y10, то на первом входе и соответственно на выходе четвертого элемента ИЛИ 210 перестает удерживаться лог."1". Тем самым запрещается открывание первого элемента И 199, т.е. организация очередного запроса СМ для чтения ИС из ОП, а также снимается обнуление второго D-третьего 190. Происходят появление сигнала Y9, снятие сигнала Y8 и сброс третьего D-триггера 191. На этом циклическая работа схемы обрывается.

Происходит ожидание снятия сигнала Y9, на который реагирует четвертый D-триггер 192. На его прямом выходе появляется сигнал передачи управления, который через второй выход второй группы 164 выходов запускает в работу узел 136 управления приемом. Этот же сигнал через третий элемент ИЛИ 209 по входу сброса обнуляет первый D-триггер 189, который своим инверсным выходом обнуляет первый RS-триггер 193, а тот, в свою очередь, своим инверсным выходом через четвертый элемент ИЛИ 210 сбрасывает второй D-триггер 190. Таким образом, сигнал передачи управления имеет импульсный характер, длительность которого обуславливается временем срабатывания первого и второго D-триггеров 189 и 190, первого RS-триггера 193, третьего и четвертого элементов ИЛИ 209 и 210. Теперь узел 135 управления передачей находится в исходном состоянии и ожидает нового импульса запуска.

Если изначально не задан сигнал разрешения дальнейшей работы на втором входе 157, то после первого обращения к ОП и чтения КС в тот момент, когда взведется первый RS-триггер 193, четвертый элемент ИЛИ 210 снимает на своем выходе лог. "1" и создает условия для окончания работы узла 135 управления передачей. Как только снимется сигнал Y9, возникает импульсный сигнал передачи управления и описанным выше образом схема возвращается в исходное состояние.

Блок 218 установки предназначен для формирования кратковременного сигнала обнуления сразу после включения питания устройства сопряжения с целью установки его в исходное состояние.

Изменение режима работы устройства не отражаетcя на функционировании узлов 135 и 136 управления передачей и приемом.

Узел 136 управления приемом (фиг.7) работает следующим образом. В исходном состоянии все внешние сигналы отсутствуют, все триггеры 219-224 сброшены. В режиме I по второму входу первой группы 170 входов на вход взведения первого D-триггера 219 приходит импульс передачи управления. В режиме II на первом входе 172 и информационном входе первого D-триггера 219 устанавливается разрешение, а по третьему входу 174 на вход синхронизации этого триггера подается импульс запуска. В том и в другом случае указанный триггер взводится и своим инверсным выходом отправляет инверсный сигнал Y11 на первый выход 180 узла 136 управления приемом. Вместе с тем снимается обнуление с входов сброса второго D-триггера 220, счетного триггера 221, первого RS-триггера 222 и третьего RS-триггера 224 через второй элемент ИЛИ 239. Одновременно на первом входе первого элемента И 228 устанавливается лог."1" с прямого выхода первого D-триггера 219.

Присутствие сигнала Y13 на первом входе второй группы 171 входов узла 136 управления приемом и на входе взведения второго RS-триггера 223 свидетельствует о приеме ОС с магистрали последовательного интерфейса. Прямой выход второго RS-триггера 223 устанавливается в единичное состояние, подготавливая по второму входу открывание третьего элемента И 230, а инверсный выход - в нулевое состояние, блокируя по третьему входу второй элемент И 229.

Снятие сигнала Y13 указывает на окончание приема ОС. Если при этом произошло распознание адреса абонента магистрали последовательного интерфейса, то на пятый вход 176 и первый вход третьего элемента И 230 поступает сигнал Y12. Вслед за этим на третьем входе второй группы 171 входов и на входе первого одновибратора 225 появляется сигнал Y14. В результате на третий вход третьего элемента И 230 поступает с выхода первого одновибратора 225 одиночный импульс, который взводит первый RS-триггер по входу взведения и через третий элемент ИЛИ 240 в виде сигнала Y15 направляется к второму выходу 181 узла 136 управления приемом.

Этот же импульс Y15 по входу взведения взводит третий RS-триггер 224. Последний своим прямым выходом через первый элемент 243 задержки по второму входу открывает первый элемент И 228 и тем самым выставляет на четвертом выходе 183 узла 136 управления приемом запрос доступ к ОП для записи ОС.

Ответный сигнал Y17 проникает через шестой вход 177 к первому входу шестого элемента И 233, на втором входе которого присутствует лог."1" с инверсного выхода второго D-триггера 220. С выхода шестого элемента И 233 по второму выходу группы 179 выходов узла 136 управления приемом отправляется сигнал Y16, устанавливающий селектор 132 (фиг.2) в третье положение.

Чуть позже, пройдя четвертый элемент 246 задержки, сигнал Y17 попадает на второй вход четвертого элемента И 231, на первом входе которого удерживается лог."1" с прямого выхода третьего RS-триггера 224. С выхода четвертого элемента И 231 по третьему выходу 182 отправляется сигнал Y19, стробирующий запись в ОП.

Ответный сигнал Y6 от системной ОП через седьмой вход 178 приходит к первому входу пятого элемента И 232, второй вход которого проверяет наличие сигнала Y19. С выхода пятого элемента И 232 через второй элемент ИЛИ 239 подается обнуление на вход сброса третьего RS-триггера 224 и он сбрасывается, снимая сигнал Y19 с третьего выхода 182 и через некоторое время сигнал запроса доступа к ОП с четвертого выхода 183. Тут же пропадает сигнал Y17, снимая сигнал Y16.

Появление лог. "1" на инверсном выходе третьего RS-триггера 224 запускает второй одновибратор 226, с выхода которого первый счетный импульс Сч3 через четвертый элемент ИЛИ 241 проходит по второму входу сквозь девятый элемент И 236 на четвертый выход группы 179 выходов, так как на первом входе девятого элемента И 236 удерживается лог."1" с инверсного выхода второго D-триггера 220. Выдержав необходимое время, второй элемент 244 задержки запускает третий одновибратор 227, направляющий второй счетный импульс Сч3 через четвертый элемент ИЛИ 241, девятый элемент И 236 на четвертый выход группы 179 выходов, который соединен со счетным входом третьего счетчика 126 (фиг.2). Содержимое последнего дважды инкрементируется под воздействием счетных импульсов Сч3.

Как только эти импульсы отправлены, через третий элемент 245 задержки по входу взведения взводится второй D-триггер 220, производят следующие изменения: запрещается в дальнейшем открывание шестого и девятого элементов И 233 и 236, на первом входе элемента ИЛИ-НЕ 242 появляется лог."0" и устанавливается лог."1" на втором входе седьмого и первом входе восьмого элементов И 234 и 235.

Если на втором входе 173 узла 136 управления приемом отсутствует разрешение дальнейшей работы или на четвертом входе 175 присутствует инверсный сигнал Y10, то с выхода десятого элемента И 237 на втором входе элемента ИЛИ-НЕ 242 присутствует лог."0". В этом случае на выходе последнего и на шестом выходе группы 179 выходов образуется сигнал Y22, который попадает на первый вход первого регистра 129 (фиг. 2), устанавливая в нем признак "окончание взаимодействия". Этим же сигналом Y22 через первый элемент ИЛИ 238 обнуляется по входу сброса первый D-триггер 219, который прекращает функционирование узла 136 управления приемом, сбрасывая инверсный сигнал Y11, запрещая выдачу запроса доступа к ОП с четвертого выхода 183 и подавая обнуление на входы сброса второго D-триггера 220, счетного триггера 221, первого и третьего RS-триггеров 222 и 224.

Если на втором входе 173 присутствует разрешение дальнейшей работы, а на четвертом входе 175 инверсный сигнал Y10 еще не появился, то элемент ИЛИ-НЕ 242 и после взведения второго D-триггера 220 удерживает на своем выходе лог."0".

Присутствие сигнала Y20 на втором входе второй группы 171 входов узла 136 управления приемом и на входе сброса второго RS-триггера 223 свидетельствует о приеме ИС с магистрали последовательного интерфейса. Прямой выход второго RS-триггера 223 устанавливается в нулевое состояние, блокируя третий элемент И 230, а инверсный выход - в единичное состояние, подготавливая по третьему входу открывание второго элемента И 229.

Снятие сигнала Y20 указывает на окончание приема ИС. Поскольку ему предшествовало ОС с опознанным адресом абонента, первый RS-триггер 222 взведен и своим прямым выходом удерживает лог."1" на первом входе второго элемента И 229. Таким образом исключается прием ИС от других абонентов магистрали последовательного интерфейса, чьи адреса не совпадают с заданным в устройстве сопряжения.

Прием ИС заканчивается появлением сигнала Y14 на третьем входе второй группы 171 входов. Первый одновибратор 225 вырабатывает импульсный сигнал, направляя его по второму входу через второй элемент И 229 и третий элемент ИЛИ 240 в виде сигнала Y15 к второму выходу 181 и входу взведения третьего RS-триггера 224, который взводится. В результате этого известным способом отправляется запрос доступа к ОП для записи ИС и поступает сигнал Y17, который по первому входу проходит через седьмой элемент И 234, так как на его втором входе удерживается лог."1" с прямого выхода взведенного второго D-триггера 220. Таким образом, вместо сигнала Y16 с выхода седьмого элемента И 234 по третьему выходу группы 179 выходов узла 136 управления приемом отправляется сигнал Y21, устанавливающий селектор 132 (фиг.2) в четвертое положение.

Описанным выше образом образуются сигналы Y19, Y6 и сбрасывается третий RS-триггер 224, снимая сигнал Y9 и запрос доступа к ОП. Известным порядком запускаются второй и третий одновибраторы 226 и 227, формирующие два счетных импульса Сч4. С выхода четвертого элемента ИЛИ 241 по второму входу через восьмой элемент И 235 эти импульсы направляются на пятый выход группы 179 выходов, который соединен со счетным входом четвертого счетчика 127 (фиг. 2). Содержимое последнего дважды инкрементируется под воздействием счетных импульсов Сч4. Кроме того, эти импульсы по тактовому входу взводят, а затем сбрасывают счетный триггер 121, на прямом выходе которого и первом выходе группы 179 выходов узла 136 управления приемом формируется одиночный импульсный сигнал Сч5. Первый выход группы 179 выходов соединен со счетным входом пятого счетчика 128 (фиг.2), содержимое которого декрементируется.

Если импульсный сигнал Сч5 не вызывает появление инверсного сигнала Y10 на четвертом входе 175 узла 136 управления приемом, то десятый элемент И 237 удерживает лог. "1" на втором входе элемента ИЛИ-НЕ 242, предотвращая сброс первого D-триггера 219. В этом случае вновь происходит ожидание сигнала Y14, по которому снова организуется доступ к системной ОП для записи ИС.

В тот момент, когда очередной импульс Сч5 приводит к обнулению пятого счетчика 128 (фиг.2), а дешифратор 131 нуля формирует инверсный сигнал Y10, который попадает на второй вход десятого элемента И 237, последний снимает лог. "1" с второго входа элемента ИЛИ-НЕ 242. Поскольку на его первом входе уже присутствует лог."0" с инверсного выхода второго D-триггера 220, на выходе элемента ИЛИ-НЕ 242 и на шестом выходе группы 179 выходов появляется сигнал Y22. Этот сигнал обнуляет по входу сброса первый D-триггер 219. Последний своим прямым выходом блокирует первый элемент И 228 и инверсным выходом снимает инверсный сигнал Y11, запрещая тем самым работу тракта приема устройства сопряжения. Кроме того, подается обнуление на вход сброса второго D-триггера 220, счетного триггера 221, первого и второго RS-триггеров 222 и 224. Сбросившись, второй D-триггер 220 устанавливает лог."1" на первом входе элемента ИЛИ-НЕ 242 и тем самым с выхода последнего снимает сигнал Y22, длительность которого определяется временем срабатывания первого и второго D-триггеров 219 и 220, первого элемента ИЛИ 238 и элемента ИЛИ-НЕ 242.

Таким образом, схема узла 136 управления приемом снова находится в исходном положении. С целью установки его в исходное положение сразу после включения питания по первому входу первой группы 170 входов через первый элемент ИЛИ 238 к входу сброса первого D-триггера 219 подается кратковременный сигнал обнуления.

Блок 138 триггеров прямого доступа (фиг.8) работает следующим образом. В исходном состоянии первый и второй D-триггеры 247 и 248 сброшены, по первому входу группы 184 входов на входы синхронизации первого и второго D-триггеров 247 и 248 из линии синхронизации СМ постоянно поступает тактовая частота СМ. На третьем входе группы 184 входов и соответственно на третьем входе первого элемента И 249 возможно присутствие инверсного сигнала занятости СМ. На остальных входах и выходах блока 138 триггеров прямого доступа сигналы отсутствуют.

Если устройству сопряжения задан режим I, то на первом входе 186 нет сигнала СП и с входов сброса первого и второго D-триггеров 247 и 248 снято обнуление, а лог."0" на первом входе второго элемента И 250 блокирует его.

Как только по второму входу 187 на информационный вход первого D-триггера 247 приходит сигнал запроса доступа к ОП, а на его вход синхронизации попадает передний фронт импульса тактовой частоты, первый D-триггер 247 взводится. На его прямом выходе формируется сигнал Y1, который устанавливает лог."1" на первом входе первого элемента И 249 и по первому выходу группы 185 выходов блока 138 триггеров прямого доступа отправляется в качестве сигнала запроса в СМ. Далее в качестве сигнала приоритетного разрешения доступа по второму входу группы 184 входов на второй вход первого элемента И 249 принимается сигнал Y2.

В случае отсутствия инверсного сигнала занятости на третьем входе группы 184 входов лог."1" с выхода первого элемента И 249 через второй элемент ИЛИ 253 попадает на информационный вход второго D-триггера 248. По переднему фронту импульса тактовой частоты этот триггер взводится и с его прямого выхода через первый элемент ИЛИ 252 на вход 188 блока 138 триггеров прямого доступа отправляется управляющий сигнал Y3. Одновременно появляется лог."1" на втором входе третьего элемента И 251, на первом входе которого присутствует сигнал запроса доступа к ОП. В результате третий элемент И 251 устанавливает и удеpживает лог."1" на первом входе второго элемента ИЛИ 253 и, следовательно, на информационном входе второго D-триггера 248. Это необходимо для удержания указанного триггера во взведенном состоянии, так как тот же второй D-триггер 248 своим инверсным выходом по второму выходу группы 185 выходов отправляет в СМ инверсный сигнал занятости, который оттуда попадает обратно в блок 138 триггеров прямого доступа и по третьему входу блокирует первый элемент И 249. Такое состояние схемы удерживается до тех пор, пока присутствует сигнал запроса доступа к ОП на втором входе 187. Как только он будет снят, сразу появляется лог."0" на информационном входе первого D-триггера 247, а также по первому входу через третий элемент И 251, по первому входу через второй элемент ИЛИ 253 лог."0" попадает на информационный вход второго D-триггера 248. После этого появление переднего фронта первого же импульса тактовой частоты на входах синхронизации обоих D-триггеров 247, 248 ведет к их сбросу и соответственно снятию сигналов Y1-Y3 и инверсного сигнала занятости. Таким образом, блок 138 триггеров прямого доступа возвращается в исходное состояние.

Если устройству сопряжения задан режим II, то на первом входе 186 блока 138 триггеров прямого доступа постоянно присутствует сигнал СП, который не позволяет взводиться первому и второму D-триггерам 247 и 248. Следовательно, не подаются сигналы Y1 и занятости в СМ.

Кроме того, сигнал СП по первому входу разблокирует второй элемент И 250. Теперь, как только на втором входе 187 появляется сигнал запроса доступа к ОП, он сразу же проходит по второму входу через второй элемент И 250, по первому входу через первый элемент ИЛИ 252 и в виде сигнала Y3 оказывается на выходе 188 блока 138 триггеров прямого доступа. Пропадание запроса доступа к ОП тем же путем снимает сигнал Y3.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для управления обменом данными | 1989 |

|

SU1795466A1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КОДОВ С САМОКОНТРОЛЕМ | 1989 |

|

RU2007863C1 |

| Устройство для сопряжения абонентов с ЦВМ | 1990 |

|

SU1755289A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

Изобретение относится к вычислительной технике и позволяет повысить эффективность связи абонентов магистрали последовательного интерфейса с цифровой вычислительной машиной через стандартный параллельный интерфейс путем использования режима прямого доступа к оперативной памяти (ОП) и анализа адреса абонента. Устройство содержит три шинных формирователя, дешифратор адресов, генератор тактовой частоты, блок управления, два мультиплексора, второй элемент сравнения. Передаваемая информация в параллельном виде считывается из ОП в первый регистр, через параллельно-последовательный преобразователь поступает в шифратор сигналов линии и усилителем-передатчиком отправляется абоненту. Ответ принимается усилителем-приемником и дешифратором сигналов линии, откуда через последовательно-параллельный преобразователь попадает во второй регистр и записывается в ОП при условии распознания адреса абонента первым элементом сравнения. Управляющая информация содержится в блоке регистров. 5 з.п.ф-лы, 16 ил.

(11) 2017211

0715

(13) C1

(51)5 G 06 F 13 /00

(21) 4882511/24

(22) 23.08.90

(72) Копылов В.И.

(71) Институт ядерных исследований РАН

(73) Институт ядерных исследований РАН

(54) (57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛАМИ СВЯЗИ