Изобретение относится к технике цифровых контрольно-диагностических систем и может быть использовано при восстановлении числовой периодической последовательности ступенчатым процессом.

Известен преобразователь код-напряжение, содержащий n-разрядные сумматор и регистр, n логических элементов ИЛИ, источник образцового напряжения, коммутатор и фильтр НЧ.

В известном преобразователе выходной уровень получается путем фильтрации среднего значения импульсной последовательности с длительностью импульсовτо с выхода коммутатора. При этом значение среднего пропорционально управляющему коду. Удовлетворительные фильтрующие свойства возможны при достаточно большой постоянной времени фильтра НЧ, что обусловливает значительное увеличение времени установления сигнала. Это обстоятельство не позволяет использовать такой преобразователь при реализации многоуровневого сигнала.

Цель изобретения - повышение быстродействия преобразователя при синтезе периодического многоуровневого ступенчатого сигнала.

Для достижения поставленной цели в преобразователь, содержащий n-разрядлный комбинационный сумматор, первыми n входами подключенный к выходам n элементов ИЛИ, входом переноса - к первым входам n элементов ИЛИ и первому входу преобразователя, n выходами - к вторым входам сумматора через регистр, а выходом переноса через регистр - к входу управления коммутатором, тактируемый вход регистра является вторым входом преобразователя, источник образцового напряжения соединен с выходом преобразователя через последовательно соединенные коммутатор и фильтр НЧ, введены n-разрядный счетчик, дешифратор и n-разрядный блок памяти, выходами подключенный к соответствующим вторым входам n логических элементов ИЛИ, адресными входами - к выходам счетчика, вход которого является третьим входом преобразователя, и к входам дешифратора, M входов дешифратора являются входами управления фильтра НЧ, содержащего резистор, M конденсаторов, вторыми выводами подключенных к общей шине, M ключей подзаряда и M выходных ключей, вторыми выводами подключенных к выходу преобразователя, а первыми - к соответствующим первым выводам конденсаторов и вторым выводам ключей подзаряда, первые входы которых связаны с входом фильтра через резистор, цепь управления K-го ключа подзаряда подключена к управляющему входу K+1 выходного ключа и к K-ому выходу дешифратора, а цепь управления первого ключа подзаряда подключена к входу управления M-го выходного ключа и первому входу управления фильтра.

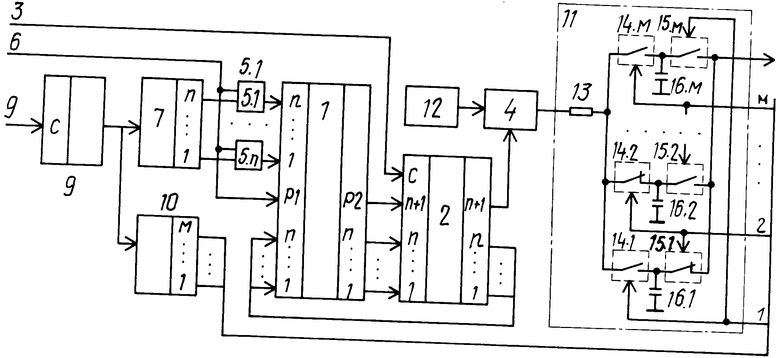

На чертеже показана структурная схема преобразователя код-напряжение.

Преобразователь содержит n-разрядный комбинационный сумматор 1, n+1-разрядный регистр 2, входами подключенный к n выходам суммы S1 сумматора 1 и выходы переноса SP сумматора 1. Тактовым входом регистр 2 подключен к входу 3 преобразователя, n выходами к соответствующим n входам сумматора 1, а n+1 выходом - к входу управления ключом 4. Сумматор 1 другими n входами подключен к выходам n логических элементов ИЛИ 5. Первые входы этих элементов связаны с входом переноса сумматора и входом 6 преобразователя, а вторыми входами к соответствующим n входам блока 7 данных. Адресные входы блока 7 подключены к m выходам счетчика 8, вход которого является входом 9 преобразователя, и к m входам дешифратора 10. M= 2m выходов дешифратора 10 являются цепями управления фильтра 11 НЧ. Входом фильтр 11 подключен к источнику 12 образцового напряжения через ключ 4.

Фильтр 11 содержит резистор 13, одним выводом подключенный к входу фильтра, а другим к входу M ключей 14 заряда.

Вторыми выводами ключа 14 подключены к первым выводам M выходных ключей 15 и к соответствующим конденсаторам 16, свободным выводам подключенным к общему проводу. Вторые выводы ключей 15 соединены с выходом фильтра. Вход управления K-го ключа 14 K подключен к входу управления K-1 ключа 15 K-1 и K-ому выходу дешифратора 10.

Преобразователь работает следующим образом.

С каждым импульсом с периодом τ1 на входе 9 счетчик 8 последовательно изменяет свое состояние.

В результате на выходах блока 7 памяти устанавливаются численные значения a7ЭIIN на выходах блока 7 памяти, где IIN= { 0,1. . . , N-1} , N= 2n. Одновременно на выходах дешифратора 10 формируется единичный позиционный код длиною M, который управляет зарядом через ключ 14 K, где K= 1. . . M соответствующего конденсатора 16 K и выводом потенциала на выход преобразователя с конденсатора 16 K - 1 через ключ 15 K-1.

В зависимости от состояния a 6 входа преобразователя 6 на входы сумматора 1 передается значение a5= a7 при a6= 0, либо N+1+a6 при a6= 1.

В первом случае по каждому i-му импульсу, поступающему по входу 3 с периодом τo состояния 52 регистра 2 по первым n выходам изменяется согласно рекурентного сравнения

S2(i)= S2(i-1)+a5+a6 (mod N),

S2(0)IIN= { 0,1, . . . , N-1} , N= 2nIIN.

(1)

При этом состояние разряда n+1 регистра 2 от состояния P2 переполнения сумматора 1. P2= 1 справедливо для тех значений i, для которых выполняется неравенство

a5+a6+S2(i-1) ≥N. (2)

За N импульсов на входе 3 состояние регистра 2 переходит в исходное

S2(0)+N ˙a5= S2(0) (mod N) (3) что соответствует одному полному циклу, есть a5 и N взаимнопростые числа. В противном случае длина цикла уменьшается в N/нод (a5, N).

Согласно (3) с учетом (1) можно утверждать, что за N импульсов условие (2) выполняется a5 раз. Таким образом, если образцовое напряжение с выхода блока 12 равно Eo, среднее значение равно

Ecp= Eo·

В случае, если a6= 1, то a5= N - 1 и вход переноса сумматора 1 находится в единичном состоянии. Следовательно, неравенство (2) выполняется независимо от S2(i). В этом случае

Ecp= Eo·  = Eo

= Eo

Импульсный характер сигнала управления на входе коммутатора 4 требует фильтрацию постоянной составляющей на его выходе, которая реализуется RC-цепями, состоящими из резистора 13 и одного из конденсаторов 16. (Согласно фиг. 1 на заряд включен конденсатор 16. 2, а на выход преобразователя - 16.1). Выбор постоянной времени фильтра определяется длительностью цикла T= Nτo. Синхронное взаимодействие кодов с блока 7 памяти и конденсаторов 16 фильтра 11 НЧ обеспечивает перед подключением одного из конденсаторов 16 на выход преобразователя подзарядку до величины Eср за время τ1 с периодом M τ1.

Условно работу преобразователя можно разбить на два этапа.

Первый - предварительный этап. По значениям, хранящимся в блоке 7 памяти, устанавливаются заданные уровни на конденсаторах 16.

Второй - рабочий этап. Происходит циклический подзаряд конденсаторов 16 перед подключением их на выход преобразователя с шагом M τ1, который должен быть кратен или существенно больше τ1>>Nτo.

Таким образом, при использовании предлагаемого технического решения по сравнению с прототипом достигается повышение быстродействия при формировании последовательности многоуровневых напряжений за счет предварительного формирования линейки рабочих напряжений с последующим селективным подключением их к выходу преобразователя с помощью управляющих ключей. (56) Авторское свидетельство СССР N 1206957, кл. H 03 M 1/66, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Преобразователь код-частота | 1984 |

|

SU1233285A1 |

| Генератор псевдослучайных узкополосных сигналов | 1980 |

|

SU940157A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Сейсмостанция | 1987 |

|

SU1430924A1 |

| ЭЛЕКТРОННЫЙ РЕНТГЕНОВСКИЙ СПЕКТРОМЕТРИЧЕСКИЙ КАНАЛ | 1999 |

|

RU2157553C1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094815C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| УСТРОЙСТВО КРИПТОГРАФИЧЕСКОЙ ЗАЩИТЫ ИНФОРМАЦИИ | 2011 |

|

RU2475838C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Изобретение может быть использовано в контрольно-диагностических системах при восстановлении числовой периодической последовательности ступенчатым процессом. Цель изобретения - повышение быстродействия преобразователя при синтезе многоуровневого ступенчатого сигнала. Преобразователь код-напряжение содержит n-разрядный комбинационный сумматор 1, n + 1-разрядный регистр 2, вход 3 преобразователя, ключ 4, элемент ИЛИ 5, вход 6 преобразователя, блок 7 данных, счетчик 8, вход 9 преобразователя, дешифратор 10, фильтр 11 нижних частот, источник 12 образцового напряжения. Фильтр 11 выполнен из резистора 13, ключей 14 заряда, выходных ключей 15 и конденсаторов 16. 1 з. п. ф-лы, 1 ил.

Авторы

Даты

1994-05-15—Публикация

1991-04-25—Подача