(54) ПРЕОБРАЗОЙАТЕЛЬ даОИЧНОГО КОДА

В двоично-ДЕСЯтиадмй

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU847318A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

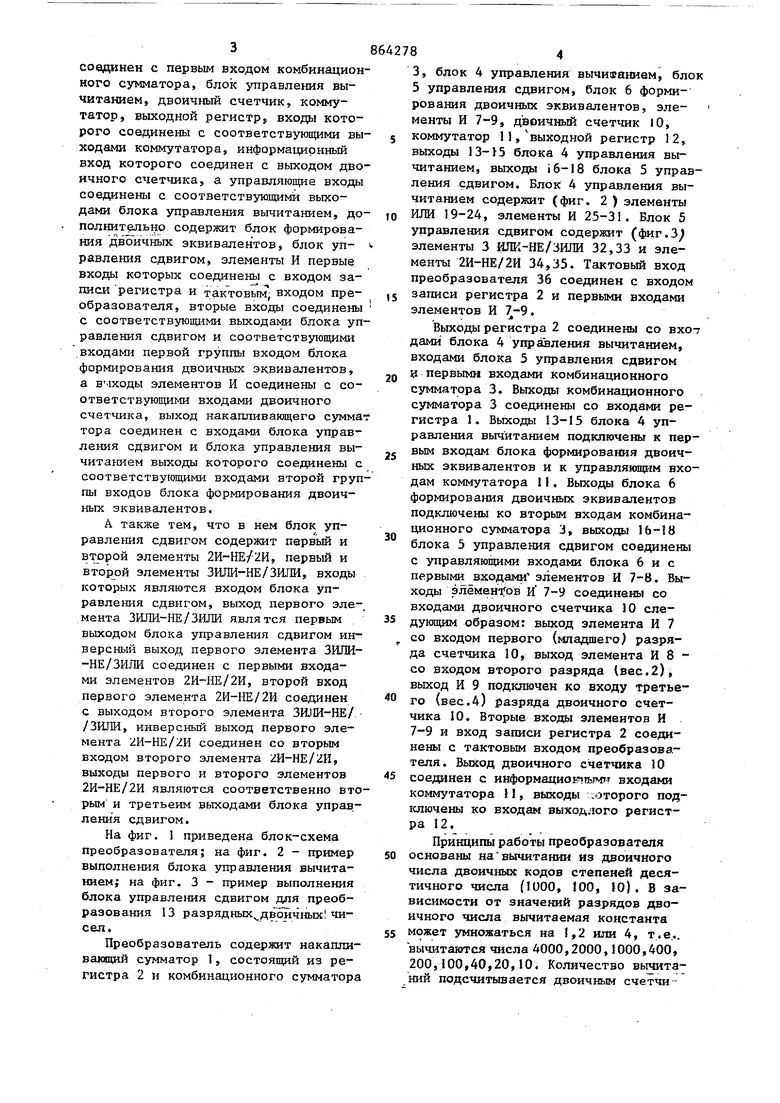

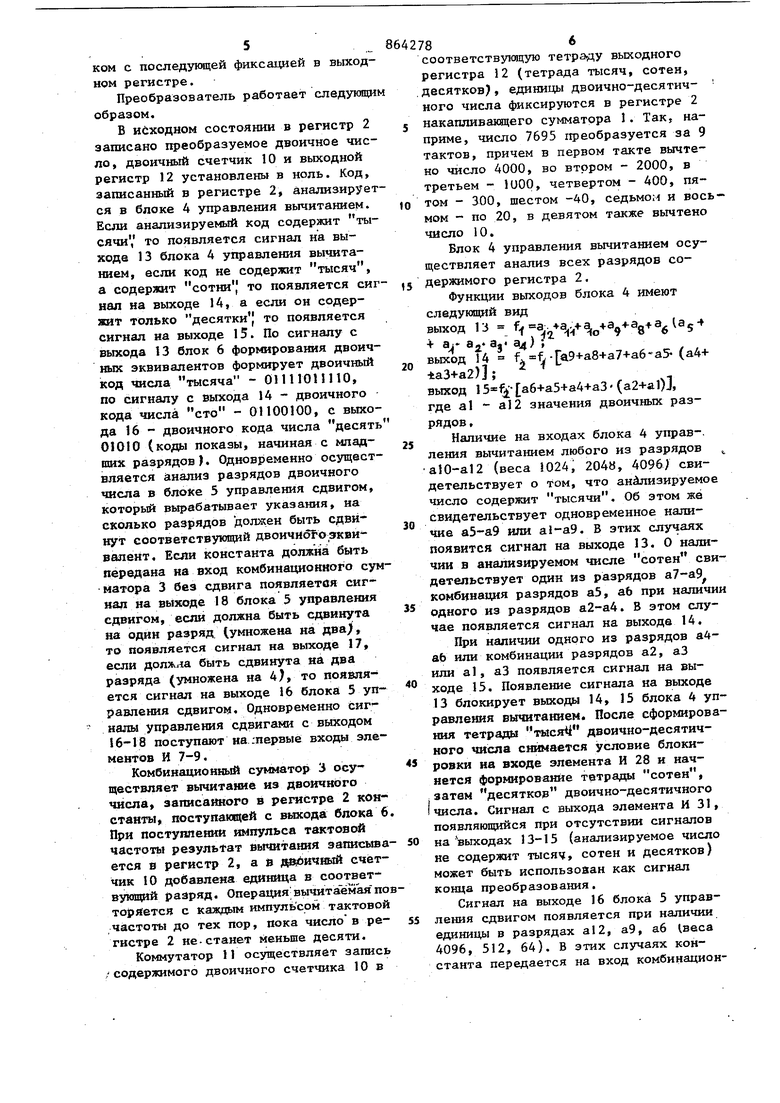

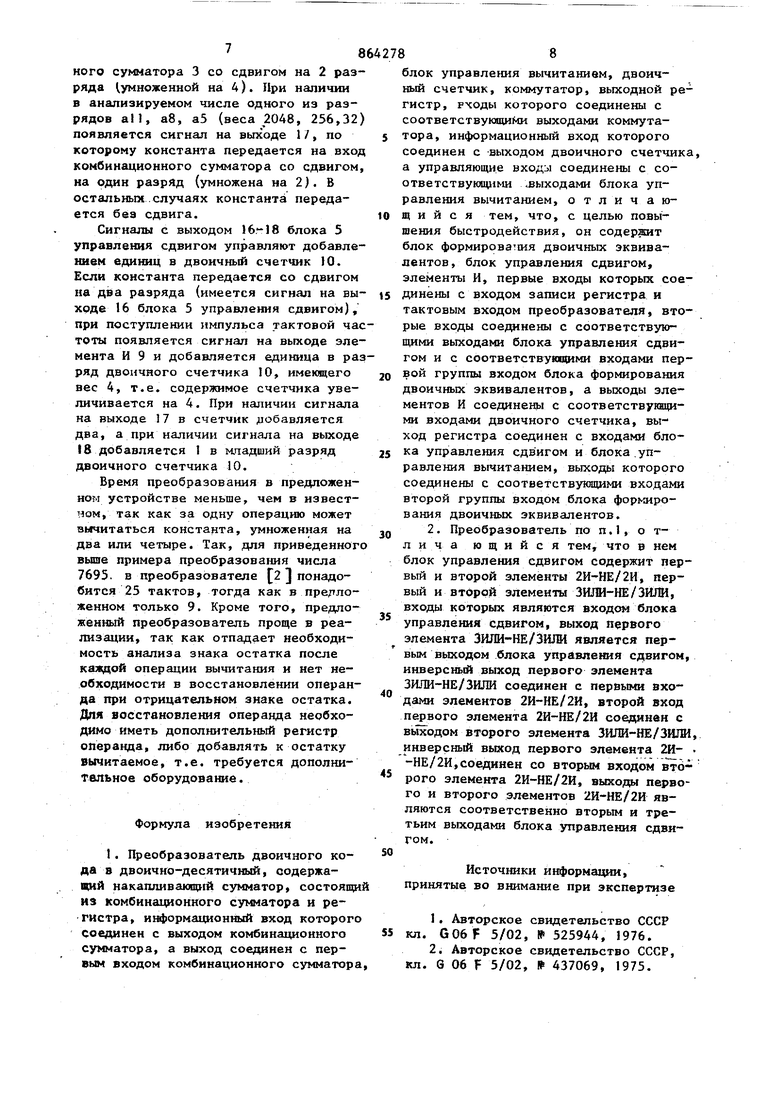

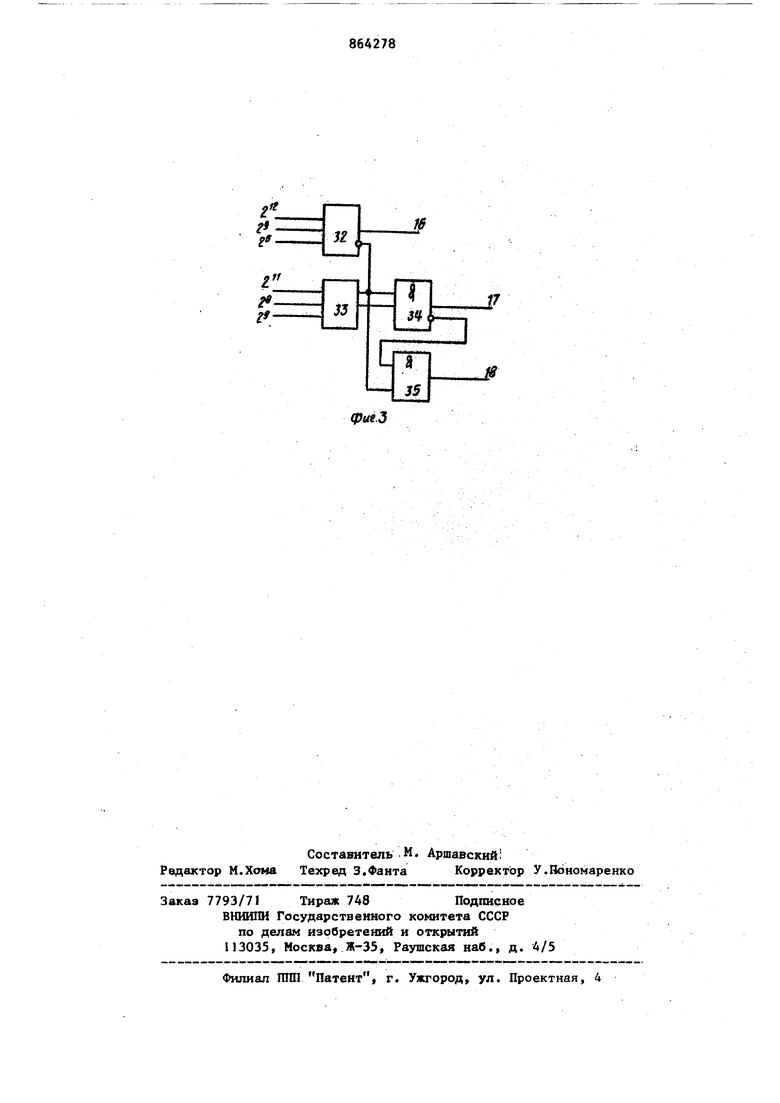

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей. Известен преобразователь двоичкого кода в двоично-десятичный, содержащий счетчик, дешифратор и распределитель ) Недостаток этого преобразователя состоит в низком быстродействии, свя занным с последовательной обработкой разрядов довичного кода. Наиболее близким к предлагаемому является преобразователь двоичного кода в |двоичньШ. код; в двоично-деся тичный, содержаш 1й накапливашцнй сумматор, состоящий из комбинационного сумматора и регистра, информационный вход которого соединен с выходом комбинационного сумматора, а выход соединен с первым входом комби национного сумматора, блок управлени выздтанием, двоичный счетчик, коммутатор, выходной регистр, входы которого соединены с соответствуящини выходами коммутатора, информационный вход которого соединен с выходом двоичного счетчика, а управлйтцие входы соединены с соответствующими выходами блока управления вычитанием 1едостаток этого преобразователя так же состоит в низком быстродействии, так как в нем осуществляется последовательное вычита1д1е из исходного двоичного числа степеней десятичного числа, представленных двоичным кодом. Целью изобретения является повышение быстродействия.. Эта цель достигается тем, что преобразователь двоичного кода в деся тичкый, содержаний накапливакяций сумматор , состоящий из комбинационного сумматора и регистра, информационный вход которого соединен с выходом комбинационного сумматора, а выход соединен с первым входом комбинацион ного сумматора, блок управления вычитанием, двоичный счетчик, коммутатор, выходной регистр, входы которого соединены с соответствунлцими вы ходами коммутатора, информационный вход которого соединен с выходом дво ичного счетчика, а управляющие входы соединены с соответствующими выходами блока управления вычитанием, до полнительно содержит блок формирования двойчных эквивалентов, блок управнения сдвигом, элементы И первые входы которых соединены с входом записи регистра и тактовым; входом преобразователя, вторые входы соединены с соответствующими выходами блока уп равления сдвигом и соответствуюищми входами первой группы входом блока формирования двоичньк эквивалентов, а в-1ходы элементов И соединены с соответствующими входами двоичного счетчика, выход накапливающего сумма тора соединен с входами блока управления сдвигом и блока управления вычитанием выходы которого соединены с соответствующими входами второй груп пы входов блока формирования двоичhuix эквивалентов. А также тем, что в нем блок управления сдвигом содержит первый и второй элементы 2И-НЕ/2И, первый и второй элементы ЗйЛИ-НЕ/ЗИЛИ, входы которых являются входом блока управления сдвигом, выход первого элемента ЗИЛИ-НЕ/ЗИЛИ являтся первым выходом блока управления сдвигом инверсный выход первого элемента ЗИЛИ-НЕ/ЗИЛИ соединен с первыми входами элементов 2И-НЕ/2И, второй нкод первого элемента 2И-11Е/2И соединен с выходом второго элемента ЗИЛИ-НЕ/ /ЗИЛИ, инверсный выход первого элемента 2И-НЕ/2И соединен со вторым входом второго элемента /И НЕ/2И, выходы первого и второго элементов 2И-НЕ/2И являются соответственно вто рым и третьеим выходами блока управления сдвигом. На фиг. 1 приведена блок-схема преобразователя; на фиг. 2 - пример выполнения блока управления вычитанием; на фиг. 3 - пример выполнения блока управления сдвигом для преобразования 13 разрядных двоичных чисел. Преобразователь содержит накапливающий сумматор 1, состоящий из регистра 2 и комбинационного сумматора 3, блок 4 управления вычитанием, блок 5 управления сдвигом, блок 6 формирования двоичных эквивалентов, элементы И 7-9, двоичный счетчик Ю, коммутатор П,выходной регистр 12, выходы 13-У5 блока 4 управления вычитанием, выходы 16-18 блока 5 управления сдвигом. Блок 4 управления вычитанием содержит (фиг. 2 ) элементы ИЛИ 19-24, элементы И 25-31. Блок 5 управления сдвигом содержит (фиг.З элементы 3 ШЖ-НЕ/ЗИЛИ 32,33 и элементы 2И-НЕ/2И 34,35. Тактовый вход преобразователя 36 соединен с входом записи регистра 2 и первыми входами элементов И 7-9. Выходы регистра 2 соединены со вхо-7 дами блока 4 управления вычитанием, входами блока 5 управления сдвигом у первымн входами комбинационного сумматора 3. Выходы комбинационного сумматора 3 соединены со входами регистра 1. Выходы 13-15 блока 4 управления вычитанием подключены к первым входам блока формирования двоичных эквивалентов и к управляющим входам коммутатора 1I. Выходы блока 6 формирования двоичных эквивалентов подключены ко вторым входам комбинационного сумматора 3, выходы 16-18 блока 3 управления сдвигом соединены с управляющими входами блока 6 и с первыми входамиэлементов И 7-8. Выходы элементов и 7-9 соединены со входами двоичного счетчика 10 следующим образом: выход элемента И 7 со входом первого (младшего) разряда счетчика 10, выход элемента И В со входом второго разряда 1вес.2), выход И 9 подключен ко входу третьего (вес.4) разряда двоичного счетчика 10. Вторые входы элементов И 7-9 и вход записи регистра 2 соединены с тактовым входом преобразователя. Выход двоичного счетчика 10 соединен с информациоттьтмг входами коммутатора 11, выходы которого под1слючены ко входам выходлого регистра 12. Принципы работы преобразователя основаны навычитании из двоичного числа двоичных кодов степеней десятичного числа (1000, 100, 10). В зависимости от значений разрядов двоичного числа вычитаемая константа может умножаться на 1,2 шш 4, т.е... вычитаются числа 4000,2000,1000,400, 200,100,40,20,10. Количество вычитаний подсчитьюается двоичным счетчи ком с последукидей фиксацией в выход ном регистре. Преобразователь работает следующ образом. В исходном состоянии в регистр 2 записано преобразуемое двоичное чис ло, двоичный счетчик 10 и выкодной регистр 12 установлены в ноль. Код, записанный в регистре 2, анализируе ся в блоке 4 управления вычитанием. Если анализируемый код содержит ты сячи, то появляется сигнал на выхода 13 блока 4 управления вычитанием, если код не содержит тысяч, а содержит сотни , то появляется си нал на выходе 14, а если он содержит только десятки то появляется сигнал на выходе 15. По сигналу с выхода 13 блок 6 формирования двоичных эквивалентов формирует двоичный код числа тысяча - 01111011110, по сигналу с выхода 14 - двоичного кода числа сто - 01100100, с выхода 16 - двоичного кода числа десять 01010 (коды показы, начиная с младших разрядов ). Одновременно осуществляется анализ разрядов двоичного числа в блоке 5 управления сдвигом, который вырабатывает указания, на сколько разрядов должен быть сдвинут соответствующий двоичнб о эквивалент. Если константа должна быть передана на вход комбинационного сум матора 3 без сдвига появляется сигнал на выходе 18 блока 5 управления сдвигом, если должна быть сдвинута на один разряд (умножена на два), то появляется сигнал на выходе 17, если должна быть сдвинута на два разряда (умножена на 4), то появляется сигнал на выходе 16 блока 5 управления сдвигом. Одновременно сигналы управления сдвигами с выходом 16-18 поступают на ;первыё входы элементов И 7-9. Комбинационш 1й сумматор 3 осуществляет вычитание из двоичного числа, записанного в регистре 2 константы, поступающей с выхода блока 6 При поступлении импульса тактовс частоты результат вычитания эатшсьюа ется в регистр 2, а и дабичный счетчик 10 добавлена единица в соответвующий разряд. Операция вычитаемаяпо торяется с каждым импульсом тактовой частоты до тех Пор, пока числов регистре 2 не.станет меньше десяти. Коммутатор 11 осуществляет запись содержимого двоичного счетчика 10 в 786 соответствукицзпо тетраду выходного регистра 12 (тетрада тысяч, сотен, ,десятков), единицы двоично-десятичиого числа фиксируются в регистре 2 накапливающего сумматора 1. Так, наприме, число 7695 преобразуется за 9 тактов, причем в первом такте вычтено число 4000, во втором - 2000, в третьем - 1UOO, четвертом - 400, пятом - 300, шестом -40, седьмом и восьмом - по 20, в девятом также вычтено число 10. Блок 4 управления вычитанием осуществляет анализ всех разрядов содержимого регистра 2. Функции выходов блока 4 имеют следующий вид выход 13 ,.,-a +a -ag+a U5- а. aj« ад) ; выход 14 fv -|ja9+a8+a7+a6a5 (а4+ -ьаЗ+а2); выход 15 f - a6+a5+a4+a3(a2+al), где al - ai2 значения двоичных разрядов , Наличие на входах блока 4 управ-, ления вычитанием любого из разрядов alO-al2 (веса 1024) 204, 4096) свидетельствует о том, что анализируемое число содержит тысячи. Об этом же свидетельствует одновременное наличие а5-а9 или al-a9. В этих случаях появится сигнал на выходе 13. О наличии в анализируемом числе сотен свидетельствует один из разрядов а7-а9 комбинация разрядов а5, а6 при наличии одного из разрядов а2-а4. В этом случае появляется сигнал на выходе 14. При наличии одного из разрядов а4а6 или комбинации разрядов а2, аЗ или al, аЗ появляется сигнал на выходе 15. Появление сигнала на выходе 13 блокирует выходы 14, 15 блока 4 управления вычитанием. После сформирования тетрады тыся двоично-десятичного числа снимается условие блокировки на входе элемента И 28 и начнется формирование тетрады сотен, затем десяткор двоично-десятичного числа. Сигнал с выхода элемента И 31, появляющийся при отсутствии сигналов на выходах 13-15 (анализируемое число не содержит тысяч, сотен и десятков) ожет быть использован как сигнал конца преобразования. Сигнал на выходе 16 блока 5 управения сдвигом появляется при наличии единицы в разрядах al2, а9, а6 1веса 096, 512, 64). В этих случаях контанта передается на вход комбинационкого сумматора 3 со сдвигом на 2 разряда умноженной на 4). При наличии в анализируемом числе одного из разрядов all, а8, а5 (веса 2048, 256,32 появляется сигнал на выходе 1/, по которому константа передается на вход комбинационного сумматора со сдвигом на один разряд (умножена на 2). В остальных.случаях константа передается без сдвига. Сигналы с выходом 6.-18 блока 5 управления сдвигом управляют добавле нием еди1шц в двоичный счетчик 10. Если константа передается со сдвигом на два разряда (имеется сигнал на вы ходе 16 блока 5 управления сдвигом), при поступлении импульса тактовой ча тоты появляется сигнал на выходе эле мента И 9 и добавляется единица в ра ряд двоичного счетчика 10, имеющего вес 4, т.е. содержимое счетчика увеличивается на 4. При наличии сигнала на выходе 17 в счетчик добавляется два, а при наличии сигнала на выходе 18 добавляется 1 в младший разряд двоичного счетчика 10. Время преобразования в предложенном устройстве меньше, чем в известном, так как за одну операцию может вычитаться константа, умноженная на два или четыре. Так, для приведенног выше примера преобразования числа 7695. в преобразователе f23 понадобится 25 тактов, тогда как в пре;тложениом только 9. Кроме того, предложенный преобразователь проще в реализации, так как отпадает необходимость анализа знака остатка после каяф1ой операции вычитания и нет необходимости в восстановлении операнда при отрицательном знаке остатка. Для восствновления операнда необходимо иметь дополнительный регистр операнда, либо добавлять к остатку вычитаемое, т.е. требуется дополнительное оборудование. Формула изобретения 1. Преобразователь двоичного кода в двоично-десятичный, содержап;ий накапливающий сумматор, состоящи из комбинационного сумматора и регистра, и1«1|Ормационный вход которого соединен с выходом комбинационного сумматора, а выход соединен с первым входом комбинационного сумматор блок управления вычитанием, двоичный счетчик, коммутатор, выходной регистр, рходы которого соединены с соответствующими выходами коммутатора, информационный вход которого соединен с выходом двоичного счетчика, а управляющие входы соединены с соoтвeтcтвyющ ш .выходами блока управления вычитанием, отличаюи и с я тем, что, с целью повышения быстродействия, он содерлшт блок формироватшя двоичньпс эквивалентов, блок управления сдвигом, элементы И, первые входы которых соединены с входом записи регистра и тактовым входом преобразователя, вторые входы соеданены с соответствующими вьпсодами блока управления сдвигом и с соответствующими входами первой группы входом блока формирования двоичных эквивалентов, а выходы элементов И соединень с соответствуннцими входами двоичного счетчика, выход регистра соединен с входами блока управления сдвигом и блока.управления вычитанием, выходы которого соединены с соответствующими входами второй группы входом блока формирования двоичных эквивалентов, 2. Преобразователь по п.1, о тлича ющийся тем, что в нем блок управления сдвигом содержит первый и второй элементы 2И-НЕ/2И, первый и второй элементы ЗИЛИ-НЕ/ЗИЛИ, входы которых являются входом блока управления сдвигом, выход первого элемента ЗИЛИ-НЕ/ЗШШ является первым выходом блока управления сдвигом, инверсный выход первого элемента ЗИЛИ-НЕ/ЗИЛИ соединен с первь1ми ахо дами элементов 2И-НЕ/2И, второй вход первого элемента 2И-НЕ/2И соединен с выходом второго элемента ЗИЛИ-НЕ/ЗШШ, инверсный выход первого элемента 2И- -НЕ/2И,соединен со вторым входом второго элемента 2И-НЕ/2И, выходы первого и второго элементов 2И-НЕ/2И являются соответственно вторым и третьим выходами блока управления сдвигом. Источники информа1щи, принятые во внимание при экспертизе 1.Авторское свидетельство СССР кл. G06F 5/02, № 525944, 1976. 2.Авторское свидетельство СССР, кл. 6 06 F 5/02, 437069, 1975.

Авторы

Даты

1981-09-15—Публикация

1978-10-17—Подача