Изобретение относится к вычислительной технике, в частности к обнаружению и исправлению ошибок при передаче информации по каналам связи или записи/чтения информации на устройствах памяти, например системах магнитной, магнитооптической, оптической памяти.

Известны способы и устройства защиты информации от ошибок (Бэрлекемп Э. Алгебраическая теория кодирования. М. Мир, 1971, Блейхут Р.Э. Теория и практика кодов, контролирующих ошибки. М. Мир, 1986, Кларк Дж. и Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. М. Радио и связь, 1987, Питерсон У. и Уэлдон Э. Коды, исправляющие ошибки. М. Мир, 1976, Габидулин Э. М. и Афанасьев В. Б. Кодирование в радиоэлектронике. М. Радио и связь, 1986.).

Наибольшее распространение получили коды Рида-Соломона, так как для них разработаны эффективные алгебраические методы декодирования и иттерационные алгоритмы Бэрлелемпа-Месси.

Для повышения эффективности кодов применяют каскадные (двойные) коды Рида-Соломона. При использовании каскадных кодов применяют в основном двойные коды внутренний и внешний. При этом последовательность символов перемежается (операция интерливинга), разбивается на блоки, которые кодируются внутренним кодом, блоки также могут перемежаться. После перемежения производится дополнительное кодирование внешним кодом. Следовательно, каскадный код можно рассматривать как матрицу символов, в которой кодирование внутренним кодом производится по столбцам, а внешним кодом по строкам и наоборот. Для внешнего кода символы принадлежат к различным кодовым словам по отношению к внутреннему коду.

При декодировании производят обратное деперемежение, если оно необходимо. При этом, например, внешний код (или внутренний) обнаруживает и исправляет t ошибок, а в случае невозможности декодирования помечает все кодовое слово флагом стирания (предположительной ошибки).

Внутренний (внешний) код производит декодирование кодовых слов с учетом флагов стирания, что значительно повышает эффективность кода. Например, применяется внешний код Рида-Соломона (105, 100) над полем Галуа GF(265), позволяющий обнаружить и исправить до двух ошибок. Тогда внутренний код (55,50) может обнаружить и исправить до двух ошибок или пять стираний.

Известны устройства для декодирования кодов Рида-Соломона (Ко С.С. and Tjhung T.T. Simple programmable processor for decoding Reed-Solomon codes in compact disc devices at high speed. INТ. J. Еlectronics, 1989, vol. 67, no. 16p. 15-25; европейский патент N 0061345, 1981, европейский патент N 0136587, 1983).

К недостаткам этих устройств относится невозможность применения их для исправления стираний и реализация алгоритма, требующая большого количества ПЗУ, так как применяются табличные методы вычислений с использованием логарифмов и антилогарифмов.

Известны другие устройства декодирования кодов Рида-Соломона (Муттер В. М. и др. Микропроцессорные кодеры и декодеры. М. Радио и связь, 1991, с. 65-75.

К недостаткам данных устройств относятся большие аппаратурные затраты на реализацию, а также невозможность предсказания результата до окончания попытки исправления последнего символа кодового слова.

Известно устройство быстрого декодирования кодов Рида-Соломона (Arvind М. Patel "On-the-fly decoder for multiple byte errors", IВM Journal of Research and Development, vol. 3, по.3, 1986). Предложенный алгоритм реализует быструю процедуру исправления с попыткой предсказать отказ от декодирования. Однако он не реализует процедуру исправления стираний и использует процедуру Ченя, следовательно, отказ от декодирования подтверждается только после проверки на возможность исправления последнего символа кодового слова.

Наиболее близким к предлагаемому является устройство (европейский патент N 0096109, кл. G 06 F 11/10, 1982).

Устройство содержит буфер данных, вычислитель полинома локаторов ошибок, вычислитель синдромов, буферный региcтр cиндромов (регистровый файл), определитель локаторов ошибок, блок вычисления значения ошибок.

Существенным недостатком данного технического устройства является невозможность исправления стираний, большие аппаратные затраты на реализацию предлагаемого в нем алгоритма.

Цель изобретения расширение области применения устройства и повышение его быстродействия при декодировании кодов Рида-Cоломона с учетом стираний.

Поставленная цель достигается тем, что в известное устройство, содержащее буферный регистр данных (БР), вычислитель синдромов (ВС), блок управления и синхронизации (БУ), первый счетчик символов кодового слова (1СБ), причем связи выполнены так, что первая группа информационных входов БР является первой группой информационных входов устройства и соединена с группой информационных входов ВС, первая группа управляющих входов блока управления является первой группой управляющих входов устройства, введены счетчик флагов стирания (СФС), генератор локаторов (ГЛ), схема управления записью номеров стертых символов и их локаторов (СЭНЛ), дешифратор количества флагов (ДКФ), регистровый файл номеров стертых символов (РФН), регистровый файл локаторов стертых символов (РФЛ), первый и второй блоки принятия решений (1БПР, 2БПР), блок стираний (БС), блок обнаружения и определения количества ошибок (БОО), регистр количества стертых символов (РСС), первый, второй и третий коммутаторы данных (1МХ, 2МХ, 3МХ), блок регистрации ошибок кодового слова (БРО), вычитающий счетчик количества исправленных (скорректированных) символов (СИС), дешифратор (ДШ), второй счетчик символов кодового олова (2CБ), регистровый файл номеров символов (РФКС), подлежащих коррекции, регистровый файл значений ошибок (РФЗО), блок управления коррекцией (БУК), буфер значения ошибки (БЗО), n-разрядный сумматор по модулю m (СМ), схема И, причем информационный вход счетчика флагов стирания является информационным входом флагов стираний устройства, вторая управляющая группа блока управления и синхронизации является второй управляющей группой режима работы устройства, первая группа управляющих выходов блока управления и синхронизации соединена с управляющими входами вычислителя синдромов, первого счетчика символов кодового cлова, генератора локаторов, первыми группами управляющих входов счетчика флагов стирания, схемы управления записью номеров стертых символов и их локаторов соответственно, вторая группа управляющих выходов блока управления и синхронизации соединена с первыми группами управляющих входов первого и второго блоков принятия решений, регистра количества стертых символов, блока обнаружения и определения количества ошибок, блока регистрации ошибок кодового cлова, блока управления коррекцией, счетчика количества исправленных символов, группами управляющих входов второго счетчика символов кодового cлова, регистрового файла номеров символов кодового cлова, регистрового файла значений ошибки и блока стирания соответственно, информационная группа выходов вычислителя синдромов соединена с первой информационной группой первого блока принятия решений, информационная группа выходов которого соединена с первой информационной группой входов блока стирания, информационной группой блока обнаружения и определения количества ошибок и второй группой управляющих входов блока регистрации ошибок кодового cлова соответственно, группа управляющих выходов первого блока принятия решений соединена с вторыми группами управляющих входов блока обнаружения и определения количества ошибок, второго блока принятия решений, третья управляющая группа входов блока управления и синхронизации соединена с первой группой управляющих выходов дешифратора количества флагов, второй группой управляющих входов первого блока принятия решений, первой информационной группой второго блока принятия решений и информационной группой входов регистра количества стертых символов, информационная группа выходов которого соединена с первой группой входов первого коммутатора данных, группа выходов которого соединена с группой входов загрузки счетчика количества исправленных символов, выходы которого соединены с входами дешифратора, выходы которого соединены с третьей группой управляющих входов блока регистрации ошибок кодового cлова, выход которого является выходом флага ошибки декодирования устройства, выходы счетчика флагов стирания соединены с входами дешифратора количества флагов и второй группой управляющих входов схемы управления записью номеров стертых символов и их локаторов, управляющая группа выходов которого соединена с управляющими входами регистрового файла номеров стертых символов и регистрового файла локаторов стертых символов соответственно, вторая группа управляющих выходов дешифратора количества флагов соединена с второй группой управляющих входов счетчика флагов стирания, информационная группа выходов первого счетчика символов кодового слова соединена с группами информационных входов регистрового файла номеров стертых символов, генератора локаторов, схемы управления записью номеров стертых символов и их локаторов и блока управления и синхронизации соответственно, информационная группа выходов генератора локаторов соединена с информационной группой входов регистрового файла локаторов стертых символов, группа информационных выходов которого соединена с второй группой информационных входов блока стирания, информационная группа выходов которого соединена с первой группой входов третьего коммутатора данных, группа выходов которого соединена с группой информационных входов регистрового файла значений ошибок, группа информационных выходов которого соединена с группой информационных входов буфера значений ошибки, группа управляющих входов которого соединена с первой группой управляющих выходов блока управления коррекцией, второй управляющий выход которого соединен с вторым управляющим входом счетчика количества исправленных символов и с первой группой входов элемента И, вторая группа входов которого соединена с группой информационных выходов буфера значений ошибки, группа выходов элемента И соединена с первой группой m-разрядного сумматора по модулю q, вторая группа входов которого соединена с группой информационных выходов буферного регистра, а группа выходов сумматора является группой информационных выходов устройства, информационная группа выходов регистрового файла номеров стертых символов соединена с первой группой входов второго коммутатора данных, группа выходов которого соединена с группой информационных входов регистрового файла номеров символов, подлежащих коррекции, группа информационных выходов которого соединена с первой группой информационных входов блока управления коррекцией, вторая группа информационных входов которого соединена с группой информационных выходов второго счетчика символов кодового cлова, первая группа управляющих выходов второго блока принятия решений соединена с группами управляющих входов первого, второго и третьего коммутаторов данных соответственно, вторая группа управляющих выходов второго блока принятия решений соединена с четвертой группой управляющих входов блока регистрации ошибок кодового олова и второй группой входов первого коммутатора данных, первая группа информационных выходов блока обнаружения и определения количества ошибок соединена с второй группой входов третьего коммутатора данных, вторая группа информационных выходов блока обнаружения и определения количества ошибок соединена с второй группой входов второго коммутатора данных, выход флага ошибки блока обнаружения и определения количества ошибок соединен с третьим управляющим входом второго блока принятия решений.

В зависимости от задания режима работы устройство производит или декодирование внешнего кода с исправлением ошибок, а при отказе от декодирования помечает все кодовое слово флагом стирания, или декодирование внутреннего кода с учетом флагов стирания. При декодировании с учетом флагов стирания устройство вначале определяет стратегию декодирования. Если количество стираний удовлетворяет условию t+1<=N(Fст)<=2t+1 для кодов, например, с количеством проверочных символов, равном 5, то разрешается работа блока стирания. Параллельно блок обнаружения и определения количества ошибок пытается провести декодирование самостоятельно. При успешном завершении блок обнаружения и определения количества ошибок игнорирует сообщения блока стирания, в противном случае информация блока стирания используется блоком коррекции для исправления стираний.

Существенным отличием предлагаемого устройства от прототипа и других аналогичных устройств является параллельное и независимое функционирование двух алгоритмов: стирания и обнаружения ошибок, что значительно повышает быстродействие устройства и расширяет его функциональное применение. Первый и второй блоки принятия решений принимают решения: отказ от использования алгоритма стираний, если t+1>N(Fст)>2t+1 и запуск только алгоритма обнаружения; принятие решений при выполнении условий t+1<=N(Fст)<=2t+1: используется информация блока обнаружения, если он определил, что количество ошибок не более двух и в противном случае используется информация блока стирания.

Блок коррекции использует полученную информацию для исправления ошибочных символов.

Блок принятия решений (1БПР), анализируя значения синдрома и информацию о количестве стираний, может предсказать реальную ситуацию: попытку декодирования и полный отказ от декодирования.

Введение счетчика количества ошибок в данном случае позволяет дополнительно контролировать работу устройства, так как количество подлежащих исправлению символов известно после работы соответствующих оригинальных алгоритмов блока стирания и блока обнаружения и определения количества ошибок.

Известных технических решений, позволяющих реализовать параллельный алгоритм исправления стираний и ошибок с предсказанием результата, не обнаружено.

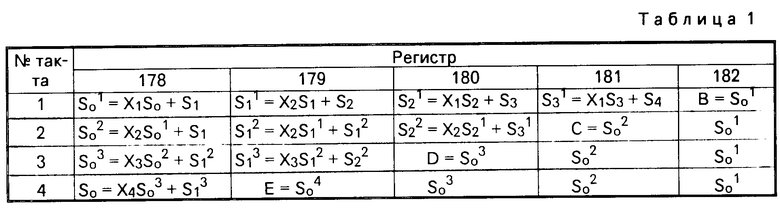

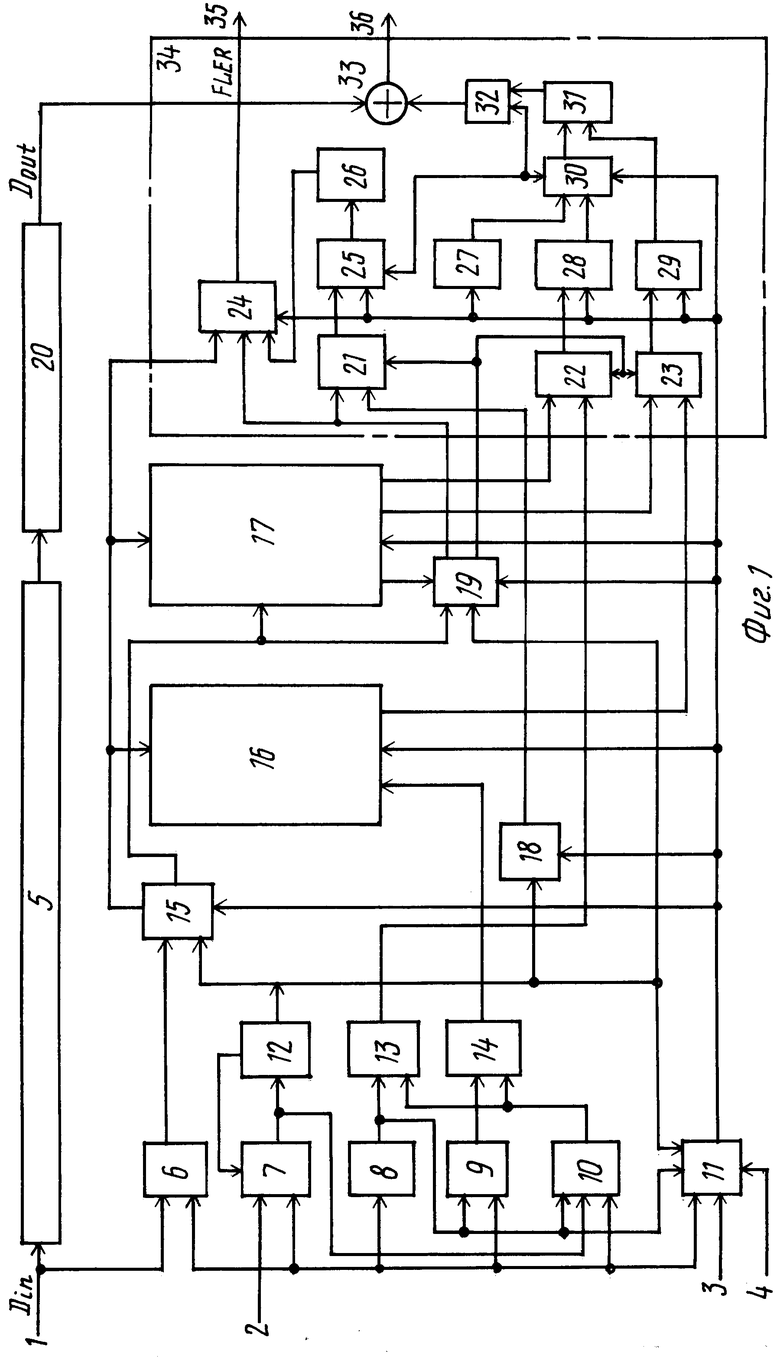

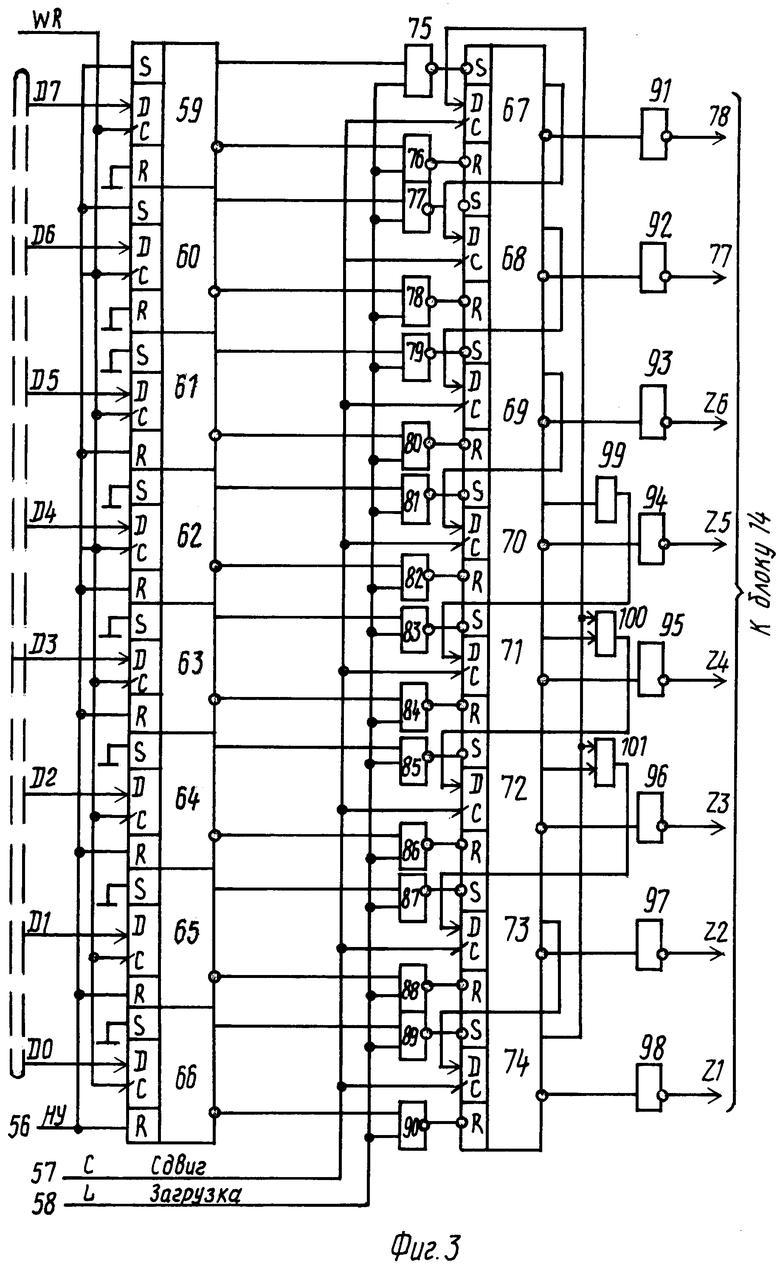

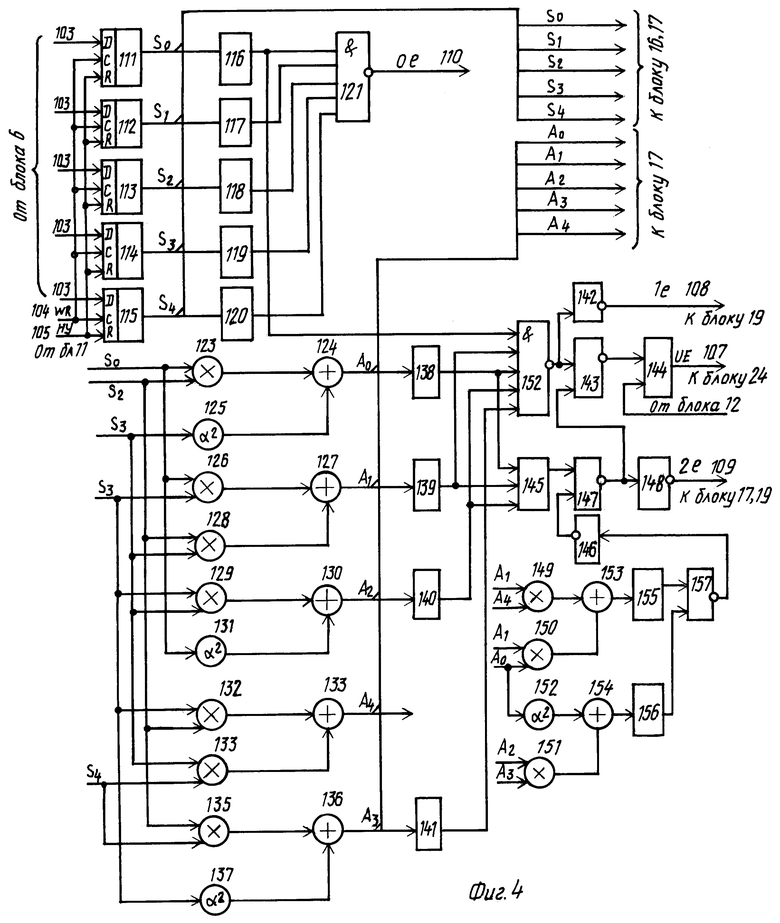

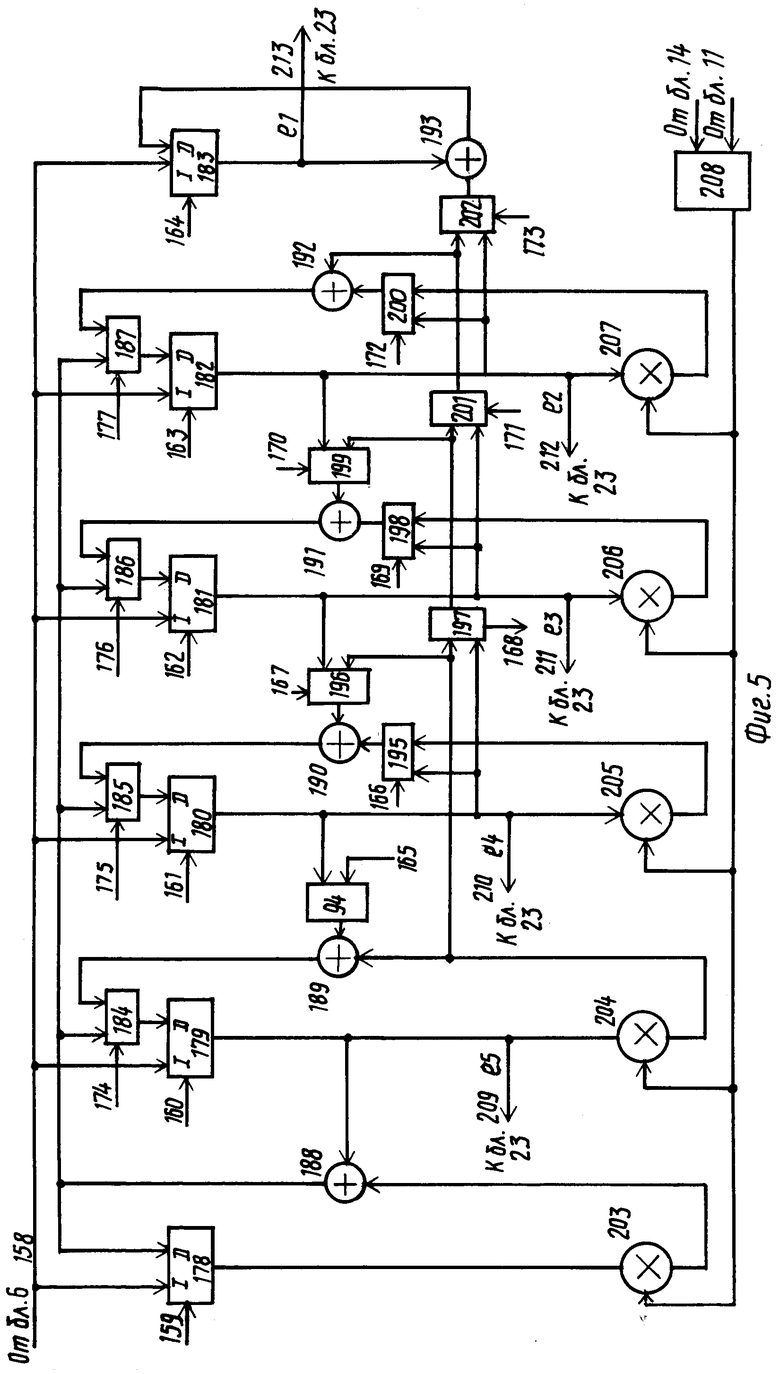

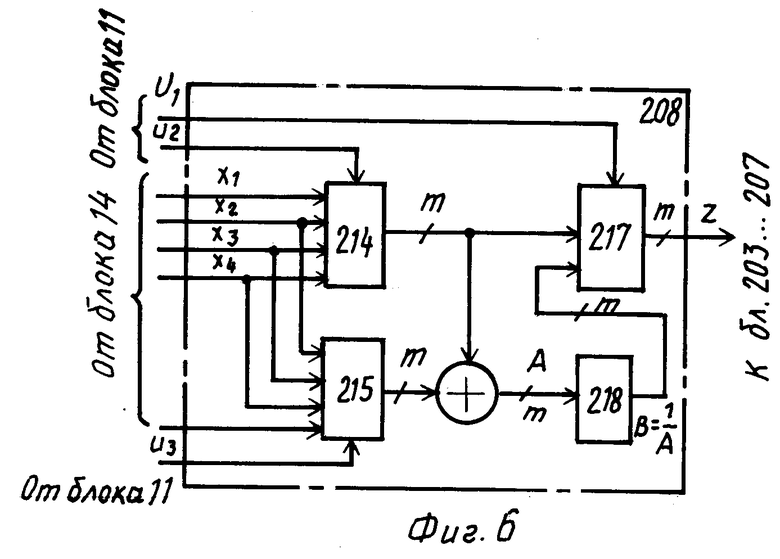

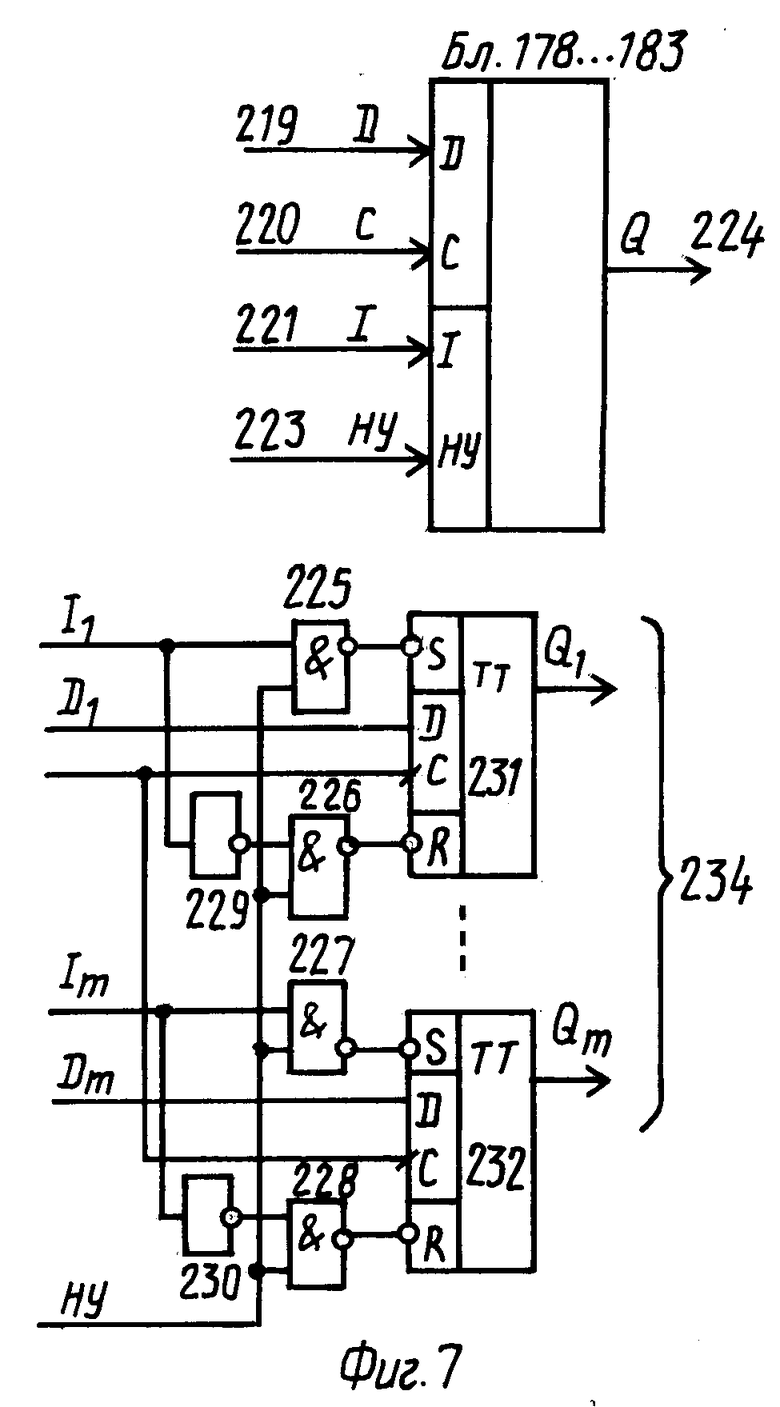

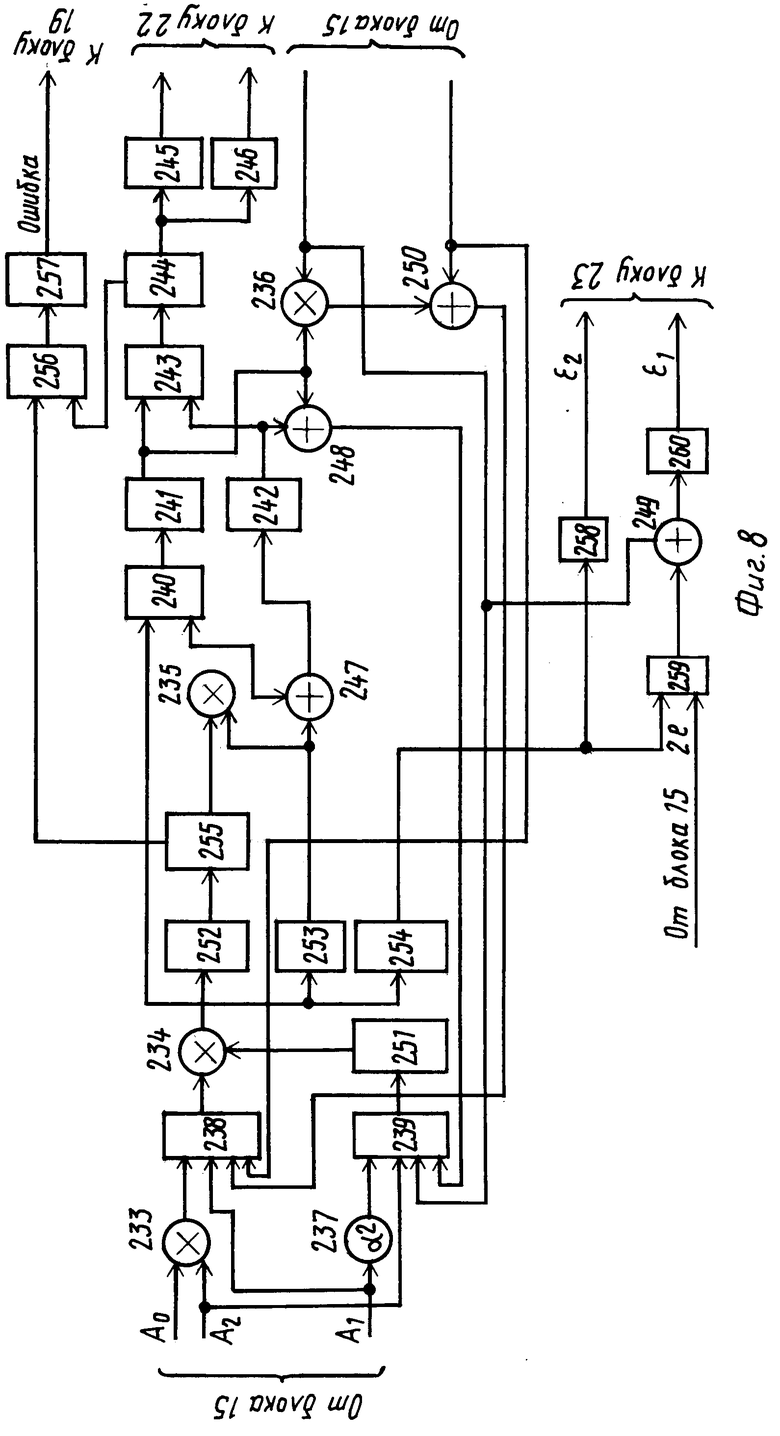

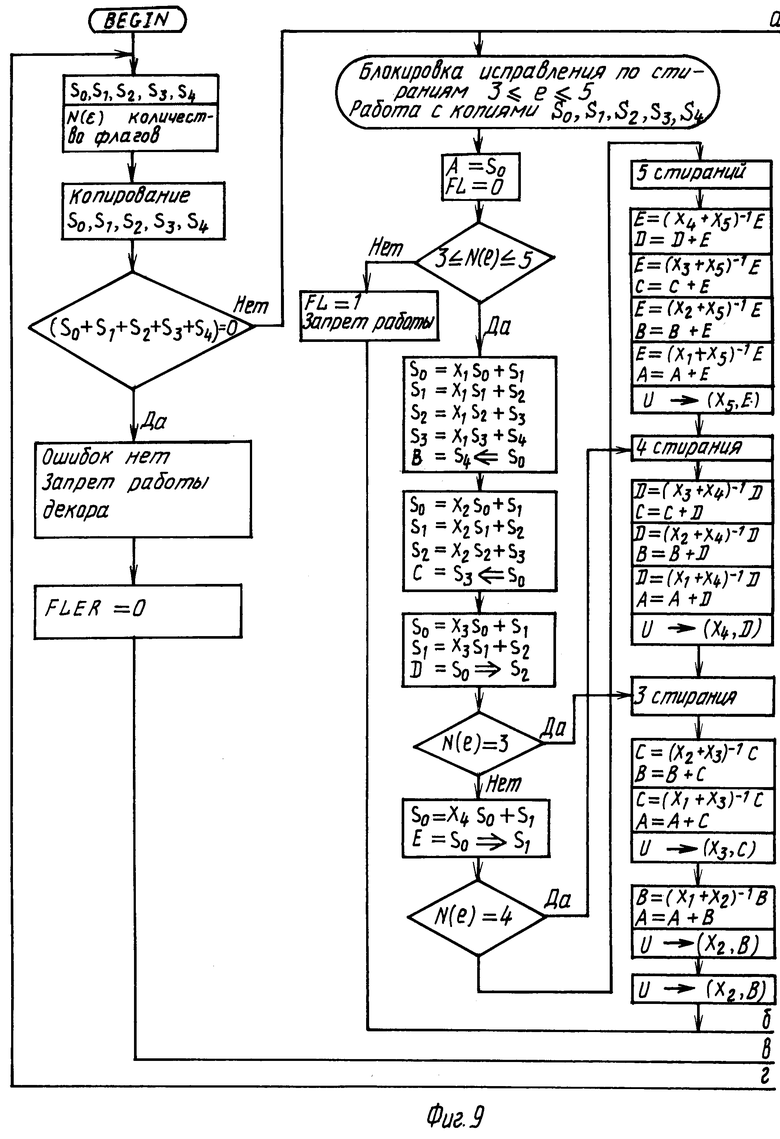

На фиг.1 дана структурная схема устройства; на фиг.2 вариант выполнения вычислителя синдромов; на фиг.3 вариант выполнения генератора синдромов; на фиг. 4 структурная схема варианта выполнения первого блока принятия решений; на фиг. 5 блок стираний; на фиг.6 и 7 вариант выполнения блока стирания; на фиг. 8 структурная схема блока обнаружения и определения количества ошибок; на фиг. 9 и 10 алгоритм функционирования устройства для режима исправления ошибок и стираний (при работе в режиме обнаружения и исправления ошибок и установок флагов стирания работа блока стирания исключается из алгоритма).

Используются следующие обозначения: Din входные символы кодового олова (вектора), подлежащие декодированию, Dout выходные данные БР, подлежащие выдаче и/или исправлению из декодера; FL флаги стираний; Еi- значение i-ой ошибки, Ni значение номера символа, соответствующее i-ой ошибке, Хi значение локатора для стертого Ni символа.

Предлагаемое устройство (фиг.1) состоит из буферных регистров 5 и 20 данных (БР). Условное разбиение БР, выполненного как, например, последовательный сдвиговый регистр с разрядностью n-бит, сделано из расчета, что длина регистра 5 определяется количеством символов кодового cлова, а длина регистра 20 задержкой декодирования. Устройство также содержит блок ВС 6, СФС 7, 1СБ 8, ГЛ 9, СЗНЛ 10, блок 11 управления и синхронизации, ДКФ 12, РФН 13, РФЛ 14, 1БПР 15, БС 16, БОО 17, РСС 18, 2БПР 19, коммутаторы: 1МХ 21, 2МХ 22, 3МХ 23, БРО 24, СИС 25, ДЩ 26, 2СБ 27, регистровый файл номеров символов, подлежащих коррекции (РФКС) 28, РФЗО 29, БУК 30, БЗО 31, элемент И 32, n-разрядный сумматор по модулю m (СМ) 33.

На фиг. 1 также показаны группа 1 информационных входов устройства Din, вход 2 флагов стирания, первая управляющая группа 3 входов устройства, вторая управляющая группа 4 задания режимов работы устройства, блок 34 коррекции (входящие в него блоки), выход 35 флага ошибки декодирования устройства, информационная группа 36 выходов устройства, Dout выходные символы БР.

Вычислитель синдромов (ВС) содержит (фиг.2) СМ 39-43, регистры 44-48, блоки умножения: на элемент поля α1 49, на элемент α2 50, на элемент α3 51, на элемент α4 52. На фиг.2 также показаны входная шина 38 символов Din, выходы 53 значений синдромов Si.

Генератор локаторов (фиг.3) содержит регистры "Защелки" 59-66 на триггерах с установкой и сбросом, сдвиговые регистры 67-74 c обратными связями, элементы И-НЕ 75-90, выходные инверторы-умощнители 91-98, сумматоры по модулю 2 99-101. На фиг. 3 также показаны: 56 начальная установка регистра "защелки", 57 управление сдвигом регистров 67-74, 58 загрузка начального значения регистра. Группа выходов Z8-Z1 образуют группу выходов текущего значения локатора. Группа входов 55 (D7-D0) может быть использована для загрузки начального значения локатора.

Первый блок принятия решения (1БПР) содержит (фиг.4) первый 111, второй 112, третий 113, четвертый 114, пятый 115 регистры хранения значений синдромов Si, первый 116, второй 117, третий 118, четвертый 119, пятый 120, шестой 138, седьмой 139, восьмой 140, девятый 141, десятый 155, одиннадцатый 156 m-входовые элементы ИЛИ-НЕ, первый 121, второй 122, третий 147, четвертый 157, пятый 143 элементы И-НЕ, двенадцатый элемент ИЛИ-НЕ 145, первый 123, второй 126, третий 128, четвертый 129, пятый 132, шестой 134, седьмой 135, восьмой 149, девятый 150, десятый 151 умножители (УМ) в поле Галуа GF(qm), первый 124, второй 127, третий 130, четвертый 133, пятый 136, шестой 153, седьмой 154 m-разрядные сумматоры по модулю q (СМ), первый 142, второй 148, третий 146, элементы НЕ, элемент И 144, первый 125, второй 131, третий 137, четвертый 152 блоки возведения в квадрат элементов поля Галуа.

Связи выполнены так, что группа информационных входов всех регистров является группой информационных входов блока, группа управляющих входов всех регистров является группой управляющих входов блока, информационные группы выходов первого, второго, третьего, четвертого, пятого регистров соединены с группами входов первого, второго, третьего, четвертого, пятого элементов ИЛИ-НЕ соответственно и совместно с группами выходов первого, второго, третьего, четвертого, пятого сумматоров являются группой информационных выходов блока, группы выходов первого, второго, третьего, пятого сумматоров дополнительно соединены с группами входов шестого, седьмого, восьмого, девятого элементов ИЛИ-НЕ соответственно, выход первого элемента ИЛИ-НЕ соединен с первыми входами первого и второго элементов И-НЕ соответственно, выходы второго, третьего, четвертого, пятого элементов ИЛИ-НЕ соединены с вторым, третьим, четвертым, пятым входами первого элемента И-НЕ, выход которого является выходом НЕТ ОШИБОК в группе управляющих выходов блока, выход шестого элемента ИЛИ-НЕ соединен с вторым и первым входами второго элемента И-НЕ и двенадцатого элемента ИЛИ-НЕ соответственно, выход седьмого элемента ИЛИ-НЕ соединен с третьим и вторыми входами второго элемента И-НЕ и двенадцатого элемента ИЛИ-НЕ cоответственно, выход восьмого элемента ИЛИ-НЕ cоединен с четвертым и третьим входами второго элемента И-НЕ и двенадцатого элемента ИЛИ-НЕ соответственно, выход девятого элемента ИЛИ-НЕ cоединен с пятым входом второго элемента И-НЕ, выход которого соединен с входом первого элемента НЕ и первым входом пятого элемента ИЛИ-НЕ соответственно, выход последнего соединен с первым входом элемента И, второй вход которого является вторым управляющим входом блока, выход двенадцатого элемента ИЛИ-НЕ cоединен с первым входом третьего элемента И-НЕ, выход которого соединен с входом второго элемента НЕ и вторым входом пятого элемента ИЛИ-НЕ, группа информационных выходов первого регистра дополнительно соединена с первыми группами входов первого и второго умножителей и группой входов второго блока возвещения в квадрат, группа выходов которого соединена с второй группой входов третьего сумматора, группа информационных выходов второго регистра дополнительно соединена с первыми группами входов третьего, четвертого и шестого умножителей, группа информационных выходов третьего регистра дополнительно соединена с вторыми группами входов первого, третьего, пятого и седьмого умножителей, группа информационных выходов четвертого регистра дополнительно соединена с вторыми группами входов второго, четвертого умножителей, первой группой входов пятого умножителя и группой входов третьего блока возведения в квадрат соответственно, группа информационных выходов пятого регистра дополнительно соединена с второй группой шестого умножителя, и первой группой входов седьмого умножителя соответственно, группа выходов первого умножителя соединена с первой группой входов первого сумматора, вторая группа которого соединена с группой выходов первого блока возведения в квадрат, группа выходов второго умножителя соединена с первой группой входов второго сумматора, вторая группа входов которого соединена с группой выходов третьего умножителя, группа выходов четвертого умножителя соединена с первой группой третьего сумматора, группа выходов пятого умножителя соединена с первой группой входов четвертого сумматора, вторая группа входов которого соединена с группой выходов шестого умножителя, группа выходов седьмого умножителя соединена с первой группой входов пятого сумматора, вторая группа выходов которого соединена с группой входов третьего блока возведения в квадрат, группа выходов первого сумматора дополнительно соединена с первой группой входов девятого умножителя и группой входов четвертого блока возведения в квадрат, группа выходов которого соединена с первой группой входов седьмого сумматора, группа выходов которого соединена с группами входов одиннадцатого элемента ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ, группа выходов второго сумматора соединена с вторыми группами входов восьмого и девятого умножителей, группа выходов последнего соединена с первой группой входов шестого сумматора, группа выходов которого соединена с группой входов десятого элемента ИЛИ-НЕ, выход которого соединен с вторым входом четвертого элемента НЕ, группа выходов третьего сумматора дополнительно соединена с первой группой входов десятого умножителя, группа выходов которого соединена с второй группой входов седьмого сумматора, группа выходов четвертого сумматора дополнительно соединена с второй группой входов десятого умножителя, группа выходов пятого сумматора дополнительно соединена с первой группой входов восьмого умножителя, группа выходов которого соединена с второй группой входов шестого сумматора, выход первого элемента НЕ, выход второго элемента НЕ и выход элемента И являются выходами ОДНА ОШИБКА, ДВЕ ОШИБКИ и НЕИСПРАВИМАЯ ОШИБКА cоответствен-но в группе управляющих выходов блока.

На фиг.4 также показаны: 103 группа информационных входов значения синдромов Si, 104 управление записью в регистр синдромов, 105 начальная установка регистра синдромов, 110 выход ое НЕТ ОШИБКИ, 108 выход 1е ОДНА ОШИБКА, 107 выход признака UЕ НЕИСПРАВИМАЯ ОШИБКА, 109 выход 2е ДВЕ ОШИБКИ.

Блок стираний (фиг.5) содержит первый 178, второй 179, третий 180, четвертый 181, пятый 182, шестой 183 регистры соответственно, первый 184, второй 185, третий 186, четвертый 187 коммутаторы данных, пятый 196, шестой 199, седьмой 195, восьмой 198, девятый 200, десятый 197, одиннадцатый 201, двенадцатый 202 коммутаторы данных, первый 188, второй 189, третий 190, четвертый 191, пятый 192, шестой 193 сумматоры (СМ) по модулю q, первый 203, второй 204, третий 205, четвертый 206, пятый 207 умножители (УМ), блок 208 операций с локаторами, элемент И 194.

Связи блока выполнены так, что первые группы информационных входов первого, второго, третьего, четвертого, пятого и шестого регистров соединены между собой и являются первой группой информационных входов блока стирания, группа информационных входов блока операций с локаторами является второй информационной группой входов блока, группа управляющих входов регистров, коммутаторов данных и первый вход элемента И являются первой группой управляющих входов блока, группа управляющих входов блока операций с локаторами является второй группой управляющих входов блока, группа выходов блока операций с локаторами соединена с первыми группами входов умножителей, группа выходов первого умножителя соединена с первой группой входов первого сумматора, группа выходов которого соединена с второй группой информационных входов первого регистра и первыми группами входов первого, второго, третьего и четвертого коммутаторов данных соответственно, группы выходов первого, второго, третьего и четвертого коммутаторов данных соединены с вторыми группами входов второго, третьего, четвертого, пятого регистров соответственно, группа выходов первого регистра соединена с второй группой входов первого умножителя, группа выходов второго регистра соединена с вторыми группами входов второго сумматора и умножителя соответственно, первыми группами входов пятого и десятого коммутаторов данных соответственно, группа выходов второго умножителя соединена с первой группой входов второго сумматора, группа выходов которого соединена с второй группой входов первого коммутатора данных, группа выходов третьего регистра соединена с второй группой входов третьего умножителя, вторыми группами входов седьмого и десятого коммутаторов данных, группой информационных входов элемента И соответственно, группа выходов элемента И соединена с второй группой входов второго сумматора, группа выходов третьего умножителя соединена с первой группой входов седьмого коммутатора данных, группа выходов которого соединена с первой группой входов третьего сумматора, группа выходов которого соединена с второй группой входов второго коммутатора данных, группа выходов пятого коммутатора данных соединена с второй группой входов третьего сумматора, группа выходов четвертого регистра соединена с вторыми группами входов пятого, восьмого, одиннадцатого коммутаторов данных и четвертого умножителя соответственно, группа выходов которого соединена с первой группой входов восьмого коммутатора данных, группа выходов которого соединена с первой группой входов четвертого сумматора, группа выходов которого cоединена c второй группой входов третьего коммутатора данных, группа выходов десятого коммутатора данных соединена с первыми группами входов одиннадцатого и шестого коммутатора данных, группа выходов которого соединена с второй группой входов шестого коммутатора данных, группа выходов пятого регистра данных соединена с вторыми группами входов шестого, девятого, двенадцатого коммутаторов данных и пятого умножителя соответственно, группа выходов которого соединена с первой группой входов девятого коммутатора данных, группа выходов которого соединена с первой группой входов пятого сумматора, группа выходов которого соединена с второй группой входов четвертого коммутатора данных, группа выходов одиннадцатого коммутатора данных соединена с первой и второй группой входов двенадцатого коммутатора данных и пятого сумматора соответственно, группа выходов шестого регистра соединена с первой группой входов шестого сумматора, группа выходов которого соединена с второй группой информационных входов шестого регистра, группа выходов двенадцатого коммутатора данных соединена с второй группой входов шестого сумматора, группа выходов с второго по шестой регистров является группой информационных выходов блока.

На фиг.5 также изображены 158 первая группа информационных входов блока; 159-164 шины управления регистрами, 174-177, 166-173 шины управления коммутаторов, которые образуют первую группу управляющих входов блока совместно с управляющим входом 165 элемента И 144, 209-213 выходы значений ошибок е5, е4, е3, е2, е1 информационная группа выходов блока, U вторая группа управляющих входов блока, Х вторая группа информационных входов блока.

Блок 208 операций с локаторами (БС) содержит (фиг.6) первый 214 и второй 215 коммутаторы данных с памятью, сумматор (СМ) 216, третий коммутатор 217 данных, определитель 218 обратного элемента (003) поля GF (qm). На фиг.6 также показаны: Х1-Х5 группа информационных входов блока, U1, U2, U3 группа управляющих входов блока; Z группа информационных выходов блока 208.

Связи выполнены так, что группа информационных входов первого и второго коммутаторов данных является группой информационных входов блока, группы управляющих входов первого, второго коммутатора данных и управляющий вход третьего коммутатора данных являются группой управляющих входов блока, группа выходов первого коммутатора данных соединена с первыми группами входов третьего коммутатора данных и сумматоров соответственно, группа выходов второго коммутатора данных соединена с второй группой входов сумматора, группа выходов которого соединена с группой входов определителя обратного элемента, группа выходов которого соединена с второй группой входов третьего коммутатора, группа выходов которого является группой выходов блока.

Регистры 178-183 (фиг.5) содержат (фиг.7), m D-триггеров 231 и 232, 2m элементов И-НЕ 225-228, элементы НЕ 229 и 230.

На фиг. 7 также показаны 224 группа информационных выходов Qiрегистра, 221 первая группа информационных входов I1-Im, 219 вторая группа информационных входов Do-Dm, 220 вход тактирования С записи по входам Di, 223 вход НУ записи (установки) по входам Ii.

Блок обнаружения и определения количества ошибок (БОО) [фиг.8] содержит первый 233, второй 234, третий 235 и четвертый 236 умножители (УМ), первый 247, второй 248, третий 249 и четвертый 250 сумматоры (СМ), блок 237 возведения в квадрат элементов поля Галуа, первый 238, второй 239, третий 240 и четвертый 243 коммутаторы данных, ООЭ 251, первый 252, второй 253, третий 254, четвертый 241, пятый 242, шестой 245, седьмой 246, восьмой 258 и девятый 260 регистры, блок 255 решения квадратного уравнения, элемент ИЛИ 256, триггер ошибки 257, блок 244 определения номера символа по локатору элемент И 259.

Связи между элементами блоками выполнены так, что первая группа входов первого умножителя соединена с первой группой входов второго коммутатора данных, первая группа входов первого коммутатора данных соединена с группой входов блока возведения в квадрат, первая группа входов четвертого сумматора соединена с первой группой входов четвертого умножителя и второй группой входов второго коммутатора данных, первая группа входов третьего сумматора соединена с второй группой входов первого коммутатора данных и вместе с второй группой входов первого умножителя является группой информационных входов блока, группа выходов первого умножителя соединена с третьей группой входов первого коммутатора данных, группа выходов которого соединена с первой группой входов второго умножителя, группа выходов блока возведения в квадрат соединена с третьей группой входов второго коммутатора данных, группа выходов которого соединена с группой входов блока определения обратного элемента, группа выходов которого соединена с второй группой входов второго умножителя, группа выходов которого соединена с первой группой входов первого сумматора и третьего умножителя, группа выходов которого соединена с первой группой входов третьего коммутатора данных и второй группой входов первого сумматора, группа выходов которого соединена с группами информационных входов пятого регистра, группа выходов которого соединена с первыми группами входов четвертого коммутатора данных и второго сумматора, группа выходов которого соединена с четвертой группой входов второго коммутатора данных, группа выходов второго умножителя соединена с второй группой входов третьего коммутатора данных и группами информационных входов первого, второго и третьего регистров соответственно, группа выходов третьего регистра соединена с группой информационных входов восьмого регистра и первой группой входов элемента И, группа выходов которого соединена с второй группой входов четвертого сумматора, группа выходов которого соединена с группой информационных входов девятого регистра, группа выходов восьмого и девятого регистров являются первой группой информационных выходов блока, группа выходов четвертого умножителя соединена с второй группой входов третьего сумматора, группа выходов которого соединена с четвертой группой входов первого коммутатора данных, группа выходов первого регистра соединена с группой входов блока решения квадратного уравнения, группа выходов которого соединена с второй группой входов третьего умножителя, а выход ошибки соединен с первым входом элемента ИЛИ, выход которого соединен с информационным входом триггера ошибки, выход которого является выходом флага ошибки блока, группа выходов третье- го коммутатора данных соединена с второй группой входов третьего коммутатора данных, группа выходов которого соединена с группой информационных входов четвертого регистра, группа выходов которого соединена с вторыми группами входов четвертого умножителя, второго сумматора и четвертого коммутатора данных, группа выходов которого соединена с группой входов блока определения номера символа по локатору, выход признака ошибки которого соединен с вторым входом элемента ИЛИ, группа информационных выходов блока определения номера символа по локатору соединена с группами информационных входов шестого и седьмого регистров соответственно, группы выходов которых являются второй группой информационных выходов блока, группа управляющих входов всех коммутаторов данных, всех регистров и триггера ошибки являются первой группой управляющих входов блока, вторая группа входов элемента И является вторым управляющим входом блока.

На фиг.8 также обозначены: А0, А1, А2, S0, S1 группа информационных входов блока, 2е второй управляющий вход блока, ОШ выход флага ошибки блока; Е1 и Е2 первая группа информационных выходов блока; N1 и N2 вторая группа информационных выходов блока.

При реализации устройства могут быть применены микросхемы серий 133, 155, 531, 555, 589, 565. Наиболее эффективно выполнение устройства в интегральном исполнении.

Устройства работает следующим образом.

Рассмотрим реализацию устройства для каскадного кода Рида-Соломона (105, 100) и (55,50) в поле Галуа GF (256).

Применяется код с кодовым расстоянием d= 6=2t+e+1, где t количество ошибок; е количество стираний. Код (105,100) обнаруживает ошибки, исправляет и/или устанавливает флаги стираний. Код (55, 50) обнаруживает и исправляет до двух ошибок или пять стираний. Введение пятого проверочного символа позволяет увеличить обнаруживающую способность кодов с минимальной избыточностью.

Поле Галуа GF(256) задается примитивным элементом а 0000 0010 с порождающим полиномом g(x) Х8 + X4 + Х2 + 1. Кодирование систематическим кодом обоих кодов производится, например, полиномом

G(x) (x + 1)(x + a)(х + a2)(x + a3) (x + a4), с помощью которого вычисляются пять проверочных символов, расположенных после информационных символов, содержащих 100 или 50 байт.

При декодировании ВС вычисляет синдромы S0, S1, S2, S3, S4 по схеме Горнера. При отсутствии ошибок S0 S1 S2 S3S4 0.

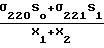

Алгоритм обнаружения и исправления ошибок

Для одной и двух ошибок справедливы уравнения (далее σ [см.фиг.9] обозначена как h): Одна ошибка

S1 + h ˙ S1 0

S2 + h ˙ S1 0 (1)

S3 + h ˙ S2 0

S4 + h ˙ S3 0 Две ошибки

S2 + h1 ˙ S1 + h2 ˙ S0 0

S3 + h1 ˙ S2 + h2 ˙ S1 0 (2)

S4 + h1 ˙ S3 + h2 ˙ S2 0 Условием наличия одной ошибки будут следующие уравнения

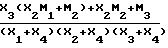

h S1/S0 S2/S1 S3/S2 S4/S3. (3) Введем обозначения:

A0 S1 ˙ S3 + S2 ˙ S2

A1 S0 ˙ S3 + S1 ˙ S2

A2 S0 ˙ S2 + S1 ˙ S1 (4)

A3 S2 ˙ S4 + S3 ˙ S3

A4 S1 ˙ S4 + S2 ˙ S3

Тогда условие одной ошибки (3) можно записать в следующем виде

А0 A1 A2 A3 0 и SO ≠ 0 (5)

Значение ошибки и ее положение определяются как e1 S0 и x1 S1/SO, где x1 локатор ошибки.

Условия для двух ошибок представим в виде

Не все А0, А1, А2 0

A3 ≠ 0

А2 ˙ A4 + A1 ˙ A0 0 (6)

A0 ˙ A0 + A2 ˙ A3 0

Тогда значения локаторов удовлетворяют уравнению

A2 ˙ Z ˙ Z + A1 ˙ Z + A0 0 (7) или

Z*Z + Z + h 0, (8) где h A0 ˙ A2/A1 ˙ A1 и

x1 K ˙ Z,

x2 x1 + K, (9) где K A1/A2 [все операции в поле Галуа GF(256)]

Решение уравнения (8) можно провести используя аффинный оператор. Тогда условием существования решения будет неравенство 0 6-ой компоненты σ h в векторном представлении: Hh7, h6, h5, h4, h3, h2, h1, h0} т.е. h5 0.

Решение уравнения (8) будет иметь вид

z1 h0 + h2 + h4

z2 h0 + h3 + h4 + h6

z3 h0 + h2 + h4

z4 h0 + h7 (10)

z5 h1 + h2 + h3 + h4 + h6

z6 h0 + h1 + h2 + h4 + h7

z7 h0 + h1 + h2 + h4

z0 0 или 1, т.е. свободная переменная. Все операции "+" сложение по модулю 2. Тогда Zz7, z6, z5, z4, z3, z2, z1} один из корней уравнения (8), второй корень Z2 Z+1.

Первый блок принятия решения вычисляет истинность условий (5) и (6) для прогнозирования возможного количества ошибок.

Если определено, что из условий (5) и (6) количество ошибок больше двух, то 1БПР 15(фиг.1 и 4) формирует признак неисправимой ошибки для Б00 17 и при выполнении условия, что количество флагов стирания больше 3, но не более 5, разрешает работу БС, а блок 34 коррекции использует результаты БС.

Для случая двух ошибок Б00 17 вычисляет значения локаторов х1 и х2и значения ошибок е1 и е2:

x1 A1˙ Z/A2

x2 X1 + A1/A2

e2 (x1 ˙ S0 + S1)/(x1 + x2) (11)

е1 e2 + S0

Значения локаторов х1 и х2 проверяются на вхождение в множествоa} допустимых значений. Для кода (55, 50) множествоa} будет определено какa54, a53, а, 1} Следовательно, локатор а54 соответствует 0-му байту, а i 54-му байту 55-байтового кодового cлова. Блок 244 (фиг.8) производит преобразование значений локаторов х в номер байта с одновременным определением вхождения вa}

Умножители (УМ) устройства реализуют операцию умножения в поле Галуа по следующим формулам:

Q A ˙ B

q7 a7& (b6 + b5 + b4 + b0) + a6& (b7 + b6 + + b5 + b1) + a5 (b7 + b6 + b2) + a4 (b7 + b3) + + a3 b4) + a2 b5 + a1 b6 + a0 b7

q6 a7 (b5 + b4 + b3) + a6 (b6 + b5 + b4 + + b0) + a5 (b7 + b6 + b5 + b1) + a4 (b7 + b6 + +b2) + a3 (b7 + b3) + a2 b5 + a1& b6 + + a0 b7

q5 a7 (b2 + b4 + b3) + a6 (b5 + b4 + + b3) + a5 (b6 + b5 + b4 + b0) + a4& (b7 + b6 + +b5 + a1) + a3 (b7 + b2 + b6) + a2 (b7 + b3) + +a1 b4 + a0

b5

q4 a7 (b7 + b3 + b2 + b1) + a6 (b4 + b3 + + b2) + a5 (b5 + b4 + b3) + a4

(b6 + b5 + b4 + + a0) + a3 (b7 + b6 + b5 + b1) + а2 (b7 + b6 + + b2) + a1 (b7 + b3) + a0 b4

q3 a7 (b5 + b4 + b2 + b1) + a6 (b5 + b3 + + b2 + b6) + a5 (b7 + b6 + b4 + b3) + a4 (b7 + +b5 + a4) + a3 (b6 + b5 + b0) + a2 (b7 + b6 + +b1) + a1 (b7 + b2) + a0 b3

q2 a7 (b6 + b5 + b3 + b1) + a6&(b7 + b6 + + b4 + b2) + a5& (b7 + b5 + b3) + a4 (b6 + a4) + + a3 (b7 + b5) + a2 (b6 + b0) + a1&(b7 + b1) + + a0&b2 q1 a7 (b7 + b6 + b2) + a6 (b7 + b3) + + a5 b4 + a4 b5+ a3 b6 + a2 b7 + a1 b0 + + a0 b1

q0 a7 (b7 + b6 + b5 + b1) + a6( b7 + b6 + + b2) + a5 (b7 + b3) + a4 b4 + a3 b5 + + a2 b6 + a1 b7 + a0 b0, (12) где "+" операция суммирования по модулю 2,

"&" операция И (логического умножения).

Реализация УМ требует 64 элемента И-НЕ и 73 элемента сумматоров по модулю 2.

Блоки умножения на константы в вычислителе синдромов на а, а2, а3, а4 реализуют логические функции: умножение на а B Z ˙ а

b7 z7

b6 z5

b5 z4

b4 z7 + z3

b3 z7 + z2 (13)

b2 z7 + z1

b1 z0

b0 z7 умножение на а2 B Z ˙ a2

b7 z5

b6 z4

b5 z7 + z3

b4 z7 + z6 + z2

b3 z7 + z6 + z1 (14)

b2 z6 + z0

b1 z7

b0 z6 умножение на а3 B Z ˙ a3

b7 z4

b6 z7 + z3

b5 z7 + z6 + z2

b4 z7 + z6 + z5 + z1

b3 z6 + z5 + z0 (15)

b2 z7 + z5

b1 z6

b0 z5 умножение на а4 B Z ˙ a4

b7 z7 + z3

b6 z7 + z6 + z2

b5 z7 + z6 + z5 + z1

b4 z6 + z5 + z4 +z0

b3 z7 + z5 + z4 (16)

b2 z6 + z4

b1 z5

b0 z4

Блоки возведения в квадрат, применяемые в БС и Б00, реализуют следующую логическую функцию:

B A ˙ A

b7 a6

b6 a6 + a5 + a3

b5 a5

b4 a7 + a5 + a4 + a2

b3 a6 + a4 (17)

b2 a6 + a5 + a4 + a1

b1 a7

b0 a7 + a6 + a4 + a0

Вычисление обратного мультипликативного элемента СМ 216 и ООЭ 251 БС и Б00 реализовано как перекодировщик 8 ->> 8 для 255 наборов 8-разрядных данных. Реализация ООЭ требует в этом случае 303 элемента И (И-НЕ) и 494 элемента ИЛИ. Возможна реализация ООЭ на ПЗУ 256 х 8 бит.

Алгоритм исправления стираний

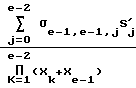

В общем виде исправление стираний заключается в решении уравнений

Sj=  Yi·Xi, j= 0, d-2, (18) где d минимальное кодовое расстояние; е число стираний; Хi локаторы стираний, относительно неизвестных Yi, представляющих собой истинные значения стертых символов. Локаторы стираний аналогичны локаторам ошибок, но указывают на положение флагов стираний.

Yi·Xi, j= 0, d-2, (18) где d минимальное кодовое расстояние; е число стираний; Хi локаторы стираний, относительно неизвестных Yi, представляющих собой истинные значения стертых символов. Локаторы стираний аналогичны локаторам ошибок, но указывают на положение флагов стираний.

Поскольку Хi известные коэффициенты, система (18) является системой d-1 линейных уравнений с е неизвестными. Определить неизвестные можно из первых е уравнений системы (должно выполняться условие e < d-1). Прямой путь стандартное решение системы путем обращения матриц. Однако он требует большого количества вычислений. Объем вычислений сокращается, если использовать алгоритм Форни. Можно еще более существенно сократить количество операций, если вычисление значений Yiдля разных i производить последовательно и при вычислении последующих значений использовать результаты предыдущих вычислений. Например, для случая исправления двух стираний справедливы формулы(11) с той лишь разницей, что в них фигурируют значения и локаторы стираний, а не ошибок. Y1 вычисляется на основании вычисленного значения Y2.

Далее этот метод распространяют на исправление до пяти стираний, получают соответствующие формулы. Вначале находят в удобной форме выражение для произвольного Yi.

Многочлен локаторов стираний определяют следующим образом

σe(Z) (Z+Xk)=

(Z+Xk)= σejZj, (19) где σej элементарные симметрические функции от локаторов стираний.

σejZj, (19) где σej элементарные симметрические функции от локаторов стираний.

Вводят многочлен

σei(Z)  (Z+Xк). (20)

(Z+Xк). (20)

Очевидно, что если σeij=[σei (Z)]j коэффициент при j-ой степени в многочлене σei (Z), то σeijZj=

σeijZj=  (Xk+Z). (21)

(Xk+Z). (21)

При этом

Yi=  . (22)

. (22)

Действительно, Sj=

Sj= X

X Y

Y X

X Yk

Yk (Xk+Xj)

(Xk+Xj)

В последней сумме индекс k пробегает все значения от 1 до n, а индекс j все значения, кроме j=i. Следовательно, все слагаемые, кроме одного, равны нулю, поскольку содержат хотя бы одну скобку (Хk + Хj), для которой k j. Единственное отличное от нуля слагаемое имеется при k i. Поэтому справедливо Yk

Yk (Xk+Xj)= Yi

(Xk+Xj)= Yi (Xk+Xj), откуда вычисляют формулу (22), по которой можно было бы найти все Yi, однако в соответствии с вышесказанным поступают следующим образом. Сначала находят Yе по формуле

(Xk+Xj), откуда вычисляют формулу (22), по которой можно было бы найти все Yi, однако в соответствии с вышесказанным поступают следующим образом. Сначала находят Yе по формуле

Ye=  . (23)

. (23)

Затем добавляют величину YeХеj, j0,е-1 к первым е-1 уравнениям системы (19). При этом из системы исключается переменная Yе. Следовательно, теперь можно решать систему из е-1 уравнений с е-1 неизвестными, но с другими значениями синдромов.

Sj' Sj + YeXej, j 0,1,е-2. (24) Для этой системы в качестве Ye выступают величины Ye-1. Следовательно,

Ye-1 . (25)

. (25)

Затем снова модифицируют синдромы

Sj'' Sj' + Ye-1Xе-1j, j 0,1,е-3, находят Ye-2 и т.д. до Y1.

Исправление одного стирания (е=1).

Очевидно, Y1= S0. (26)

Исправление двух стираний (е=2).

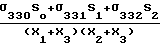

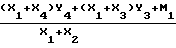

Из (23) получают

Y2 (σ220So+σ221 S1)/(X1 + X2), причем σ22 (Z) Z + X1 откуда σ220 Х1, σ221=1. Следовательно,

Y2 (SoX1 + S1)/(Х1 + Х2).

Обозначают М1 X1So + S1, (27) при этом окончательно получат

Y2=  (28)

(28)

Y1 Y2 + So

Исправление трех стираний (е=3).

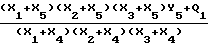

Аналогично получают

Y3=  , где σ330=X1X2,σ331=X1+X2,σ332 1. После преобразований и введения новых переменных

, где σ330=X1X2,σ331=X1+X2,σ332 1. После преобразований и введения новых переменных

М2 Х1S1 + S2,

Р1 Х2М1 + M2, (29) окончательно получают

Y3=  . (30) Модифицируют синдромы

. (30) Модифицируют синдромы

S0' S0 + Y3; S1' S1 + Y3X3 и получают

Y2=

, (30)

, (30)

Y1 Y3 + Y2 + So. (32)

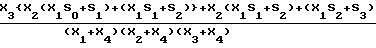

Исправление четырех стираний (е=4).

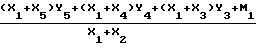

Y4=

, (33) где М3 Х1S2 + S3;

, (33) где М3 Х1S2 + S3;

Р2 Х2М2 + M3;

Q1 Х3P1 + P2. (34) Аналогично находим Y3, Y2, Y1.

Y3=  ,

,

Y2=  ,

,

Y1 Y4 + Y3 + Y2 + S0. (35)

Исправление пяти стираний (е 5).

После преобразования в числителе Y5 получают выражение

Х4{ X3X2(X1So+ S1) + (X2 + X3)(X1S1 + S2) + + (X1S2 + S3)} + X3{X2(X1S1 + S2) + (X1S2 + S3)} + + X2(X1S2 + S3) + (X1S3 + S4).

Вводят переменные

М4 X1S3 + S4,

Р3 X2M3 + M4,

Q2 X3P2 + P3,

R1 X4Q1 + Q2. С учетом этого получают

Y5=  ,

,

Y4=  , (37)

, (37)

Y3=  ,

,

Y2=  ,

,

Y1 Y5 + Y4 + Y3 + Y2 + So.

Таким образом, в выражениях для последующих Yi имеется много составляющих, входящих как компоненты в выражения для предыдущих значений. Это резко сокращает общее количество операций. Так, например, в процессе вычисления величины R1 определяются также Q1,P1,M1. С учетом требования обеспечения общности между ветвями алгоритма, на фиг.9 и 10 приведена блок-схема алгоритма исправления до пяти стираний. При этом использована несколько другая форма записи выражений: переменные А,В,С,D,Е, соответствуют величинам So,M1, P1,Q1,R1.

Алгоритм работы устройства (см. фиг. 1, 9 и 10).

Первый символ каждого блока помечен соответствующим маркером, который по первой управляющей группе 3 входов устройства поступает в блок 11, по которому осуществляется его привязка к кодовому слову.

Вторая управляющая группа 4 задает режим работы:

1) обнаружение и исправление до двух ошибок,

2) исправление ошибок и стираний. Так как алгоритм обнаружения и исправления ошибок выполняется параллельно алгоритму исправления стираний, отдельно его не рассматривают.

Синхронизацию последовательности выполнения операций обеспечивает блок 11. Вначале каждого кодового cлова все блоки устройства, исключая блок 34 коррекции, устанавливаются в исходное состояние. Блок 34 фиксирует в РФКС 28 и РФЗО 29 номера символов, подлежащих коррекции, и соответствующие значения ошибок, СИС 25 устанавливается в соответствии с информацией от БС 16, Б00 17, 1БПР 15, 2БПР 19, РСС 18, РФН 13 и РФЛ 14 после задержки, вызванного декодированием, кодового cлова.

Если принято решение, что коррекция невозможна, на выходе БРО 24 (выходе 35 устройства) устанавливается признак FLER неисправимой ошибки, запрещается работа БС, Б00 и блока 34 коррекции.

По первой информационной группе 1 входов устройства поступают символы кодового олова, которые запоминаются в буфферных регистрах 5 и 20, причем длина регистра 5 равна длине кодового cлова, а регистра 20 определяется задержкой декодирования.

ГЛ 9 устанавливает начальное значение локатора, например, для кода (55, 50), равного а54.

ВС 6 параллельно с заполнением буфера (его сдвигом) вычисляет компоненты синдрома S0, S1, S2, S3, S4.

СБ 8 производит подсчет символов, его текущее значение равно номеру символа кодового cлова. Текущее значение ГЛ соответствует текущему значению локатора. СФС 7 использует информацию о наличии флага стирания по входу 2 устройства, производит подсчет и разрешает работу СЗНЛ 10, которая управляет записью в РФН 13 и РФЛ 14. СФС 7 обеспечивает подсчет флагов до 6, после чего ДКФ 12 запрещает его работу.

После поступления последнего символа кодового cлова вычисленные значения синдромов записываются в регистры 111-115 1БПР 15 (см.фиг.4). Копия значений Ni (номера cтертых символов) переписывается в выходные регистры "защелки" РФН 13, а значение регистрового файла обнуляется. Значения локаторов Хi РФЛ 14 переписываются в блок 208 операций с локаторами БС 16 (см.фиг.5 и 6), а состояние РФЛ 14 становится нулевым.

Значения количества стертых символов N(e) записывается в РСС 18, блок 11, значение флага неисправимой ошибки для условия 5 < N(е) < 2 используется при дальнейшей работе 1БПР и 2БПР и поступает на один из входов БРО 24.

Для условия 5 < N(е) < 2 работа БС запрещается 1БПР 15. Последний определяет стратегию декодирования кодового cлова:

определяет отсутствие ошибок выход ое 110;

формирует признак одной ошибки 1е на выходе 108;

формирует признак неисправимой ошибки на выходе 107, при этом запрещается работа БС, Б00 и блока 34 коррекции, а на выходе 35 устройства устанавливается признак ошибки декодирования.

Если 1БПР 15 (фиг.4) определил, что количество ошибок не более двух, то разрешается работа Б00 17; если 2 < N(е) < 6, то и БС 16. 1БПР 15 вычиcляет также необходимые значения для работы БС и Б00 по формулам (4).

Значения компонент синдромов записываются в регистры 178-183 БС для выполнения итерационной процедуры. На работу 1БПР требуется 1-2 такта работы.

Блок стираний работает следующим образом.

Вначале работы блока (см.фиг.5) в регистры 178-183 загружаются значения компонент синдромов из 1БПР 15. В регистры 178 и 183 значения S0, в регистры 179-182 S1, S2, S3, S4 соответственно.

В последующем БС осуществляет итерационный алгоритм вычисления в соответствии с фиг.8. Блок 208 операций с локаторами формирует на выходах Z (cм. фиг.6) следующие значения: Хi, i 1,4 или i/(Хi + Хj), где i 1,4; j 5,2.

В результате итерационной процедуры значения регистров принимают следующие значения (см.табл.1). Значение регистра 183 не меняется и равно S0. Верхние индексы соответствуют номеру такта.

Если количество флагов стирания меньше пяти, то не выполняется четвертый такт, если меньше четырех, то не выполняются четвертый и третий такты.

Следовательно, максимальное количество тактов для модификации синдромов равно четырем. Описанные ниже блоки для пятого и четвертого стираний выполняются при выполнении условий, что количество флагов равно 5 или 4 соответственно.

Пять стираний (см.табл.2). Регистр 178 в дальнейших вычислениях не участвует.

Четыре стирания (см.табл.3). Регистр 179 не изменяет своего состояния.

Три стирания (см.табл.4). Регистры 178-180 не изменяют своего состояния.

Всего требуется 4 + 4 + 3 + 3 14 тактов работы.

В регистрах 179-183 хранятся значения Е,D,C,B,A, соответствующие значения 5-ой, 4-ой, 3-ей, 2-ой, 1-ой ошибок.

Необходимые управляющие сигналы для указанной процедуры формирует блок 11. Запись и формирование информации обеспечивается соответствующим управлением коммутаторов данных 174-177, 195-202 и элемента И 194.

Блок обнаружения и определения количества ошибок работает следующим образом.

На фиг.7 не показаны управляющие воды коммутаторов данных и регистров.

Две ошибки.

Для этого случая на входе 2е элемента И 259 имеется высокий уровень сигнала. Управление работой блока производит блок 11. Вычисление занимают шесть тактов работы.

Первый такт. В регистр 252 записывается значение σ  что достигается соответствующим управлением выходов первого 238 и второго 239 коммутаторов данных. На выходе УМ 233 находится значение А0А2, которое через третью группу входов первого коммутатора 238 данных поступает на первую группу входов второго УМ 234, на вторую группу входов которого поступает значение 1/А12 с выходов блока ООЭ 251, на вход которого поступает значение с выходов блока 237 возведения в квадрат через третью группу входов второго коммутатора 239 данных и группу его выходов.

что достигается соответствующим управлением выходов первого 238 и второго 239 коммутаторов данных. На выходе УМ 233 находится значение А0А2, которое через третью группу входов первого коммутатора 238 данных поступает на первую группу входов второго УМ 234, на вторую группу входов которого поступает значение 1/А12 с выходов блока ООЭ 251, на вход которого поступает значение с выходов блока 237 возведения в квадрат через третью группу входов второго коммутатора 239 данных и группу его выходов.

Значения величин, которые устанавливаются на входах первого 238 и второго 239 коммутаторов, даны в табл.5.

Второй такт. Вычисление и запись во второй регистр 253 значения А1/A2.

Третий такт. Блок решения квадратного уравнения определяет один из корней уравнения Z2 + Z +  0 и при отсутствии корней формирует признак ошибки, который через первый вход элемента ИЛИ 256 поступает на вход триггера ошибки 257 и устанавливает его выход в состояние "1" ошибка.

0 и при отсутствии корней формирует признак ошибки, который через первый вход элемента ИЛИ 256 поступает на вход триггера ошибки 257 и устанавливает его выход в состояние "1" ошибка.

Четвертый такт. Вычисленные значения Х1 Z ˙ K Z ˙ A1/A2 и X2 X1 + K с выходов УМ 235 и СМ 247 поступают: первый через коммутатор 240 данных на регистр 241, второй на регистр 242 соответственно. Регистры 242 и 241 сохраняют значение Х1 и Х2 до конца работы блока.

Пятый такт. Значения локаторов из регистров 241 и 242 через коммутатор 243 данных поступают поочередно на вход блока 244 определения номера символов по локатору, с выходов которого номера символов записываются в регистры 245 и 246. Если Х1 или Х2 X a} множество допустимых локаторов, то на выходе признака ошибки устанавливается значение высокого уровня, которое через второй вход элемента ИЛИ 256 устанавливает триггер ошибки 257. Параллельно на выходах УМ 236 формируется значение Х1So, а на выходах СМ 250 значение B Х1So + S1, которое поступает на четвертую группу входов коммутатора 238. На четвертую группу входов коммутатора 239 поступает значение (Х1 + Х2) с выходов СМ 248. В регистре 254 фиксируется значение B (Х1So + S1)/(Х1+Х2).

a} множество допустимых локаторов, то на выходе признака ошибки устанавливается значение высокого уровня, которое через второй вход элемента ИЛИ 256 устанавливает триггер ошибки 257. Параллельно на выходах УМ 236 формируется значение Х1So, а на выходах СМ 250 значение B Х1So + S1, которое поступает на четвертую группу входов коммутатора 238. На четвертую группу входов коммутатора 239 поступает значение (Х1 + Х2) с выходов СМ 248. В регистре 254 фиксируется значение B (Х1So + S1)/(Х1+Х2).

Шестой такт. Номера ошибочных символов записываются в регистры 245 и 246. Значение регистра 254 используется для вычисления ошибок Е1 и Е2. Значение Е2B/(Х1 + Х2) (Х1So + S1)/(Х1 + Х2), содержащееся в регистре 254, переписывается в регистр 258 значения ошибки и поступает на входы элемента И 259, на второй группе входов которого установлено значение высокого уровня от 1БПР 15.

На выходе СМ 249 формируется значение Е1 Е2 + S0, которое записывается в регистр 260.

Первая ошибка. Сигнал 2е "0" на входе элемента И 259. Вычисления занимают три такта.

Первый такт. Активными будут значения на вторых группах входов коммутаторов 238, 239 S1 и S2 соответственно. На выходе УМ 234 сформировано значение Х1 S1/S0, которое через коммутатор 240 записывается в регистр 241. В регистре 260 фиксируется значение ошибки Е1 S0.

Второй такт. Значение локатора Х1 через коммутатор 243 поступает на входы блока 244 определения номера символа по локатору и с его выходов значение номера записывается в регистр 245. Если Х1a} то выход признака ошибки блока 244 через вход элемента ИЛИ 256 устанавливает триггер ошибки 257.

Следовательно, максимальное значение тактов работы Б00 равно 6.

После выполнения операций блоками БС и БОО 2БПР 19 принимается решение о дальнейшей стратегии декодирования:

если БОО определил возможность самостоятельной коррекции ошибок, блок коррекции использует его информацию о количестве, номерах ошибочных символов и значениях ошибок;

если БОО определил, что количество ошибок больше двух и, если 2<N(t) < 6, тогда используется информация БС;

если 5 < N(е) < 2 и БОО определили наличие более двух ошибок, то запрещается работа блока 34 коррекции для данного кодового cлова и на выходе 35 устанавливается флаг ошибки декодирования. 2БПР требует для своей работы один такт.

При разрешении работы блока 34 коррекции в РФКС 28 и РФЗО 29 через 2МХ 22 и ЗМХ 23 загружаются соответствующие значения номеров ошибочных символов и значения ошибок. СИС 25 загружается количеством ошибок и предназначен для контроля работы устройства. 2СБ 27 ведет подсчет количества символов кодового cлова, поступающих с выхода регистра 20 на вторую группу входов СМ 33. Текущее значение 2СБ 27 равно номеру текущего символа.

БУК 30 определяет совпадение текущего номера Ni символов с номером символа, записанного в РФКС 28, при этом соответствующее значение ошибки Еi через буфер БЗО 31 и элемент И 32 поступает на первую группу входов СМ 33, так как вторая управляющая группа выходов БУК разрешает передачу Еi на группу входов СМ 33 и разрешает счет СИС 25.

Если по окончании коррекции кодового cлова значение СИС 25 не нулевое, то это тpактуется как неисправность аппаратуры при декодировании (сбой) и на выходе 35 устройства устанавливается флаг ошибки декодирования.

В процессе декодирования и коррекции происходит вычисление компонент синдрома следующего кодового cлова, номеров стертых символов и их локаторов.

При поступлении первого символа нового кодового cлова алгоритм повторяется. Декодированная информация поступает с группы выходов СМ 33 на группу информационных выходов 36 устройства.

Временные параметры декодирования составляют:

задержка 1БПР 1 такт;

задержка БС 14 тактов;

задержка БОО 2-6 тактов;

Следовательно, при декодировании без исправления стираний задержка составляет от 3 до 8 тактов, что значительно лучше, чем у известных устройств.

При декодировании с учетом стираний задержка составляет 15 тактов, так как алгоритм выполняется параллельно.

Применение данного устройства позволит увеличивает быстродействие декодирования, особенно при использовании каскадных Рида-Соломона.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ЛОКАТОРОВ ПОЛЯ ГАЛУА GF(Q*99M) | 1993 |

|

RU2103817C1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для декодирования кода Рида-Соломона /15,12/ | 1985 |

|

SU1290540A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для декодирования кода Рида-Соломона | 1985 |

|

SU1332539A1 |

Устройство содержит буферный регистр данных, вычислитель синдромов, блок управления и синхронизации, первый и второй счетчики символов кодового слова, счетчик флагов стирания, генератор локаторов, схему управления записью номеров стертых символов и их локаторов, дешифратор количества флагов, регистровый файл номеров стертых символов, первый и второй блоки принятия решений, блок стираний, блок обнаружения и определения количества ошибок, регистр количества стертых символов, первый, второй и третий коммутаторы данных, счетчик количества исправленных символов, дешифратор, регистровый файл значений ошибок, блок управления коррекцией, буфер значения ошибки, m-разрядный сумматор по модулю q, элемент И. Параллельное выполнение двух алгоритмов: исправления и исправления с учетом стертых символов - увеличивает быстродействие устройства и реализует два режима работы устройства. Введение блоков принятия решений позволяет гибко менять стратегию декодирования и прогнозировать ситуацию отказа от декодирования. Введение счетчика исправленных ошибок позволяет наряду с прогнозированием количества ошибок проводить контроль работы устройства в процессе декодирования. 4 з.п. ф-лы, 10 ил., 5 табл.

| Шарнирное устройство для сцепки буксира-толкача с толкающей баржой или другим судном | 1952 |

|

SU96109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-05-27—Публикация

1993-03-03—Подача