Изобретение относится к электросвязи и может использоваться при передаче дискретной информации по волоконно-оптическим линиям связи.

Цель изобретения - снижение избыточности линейного кодирования.

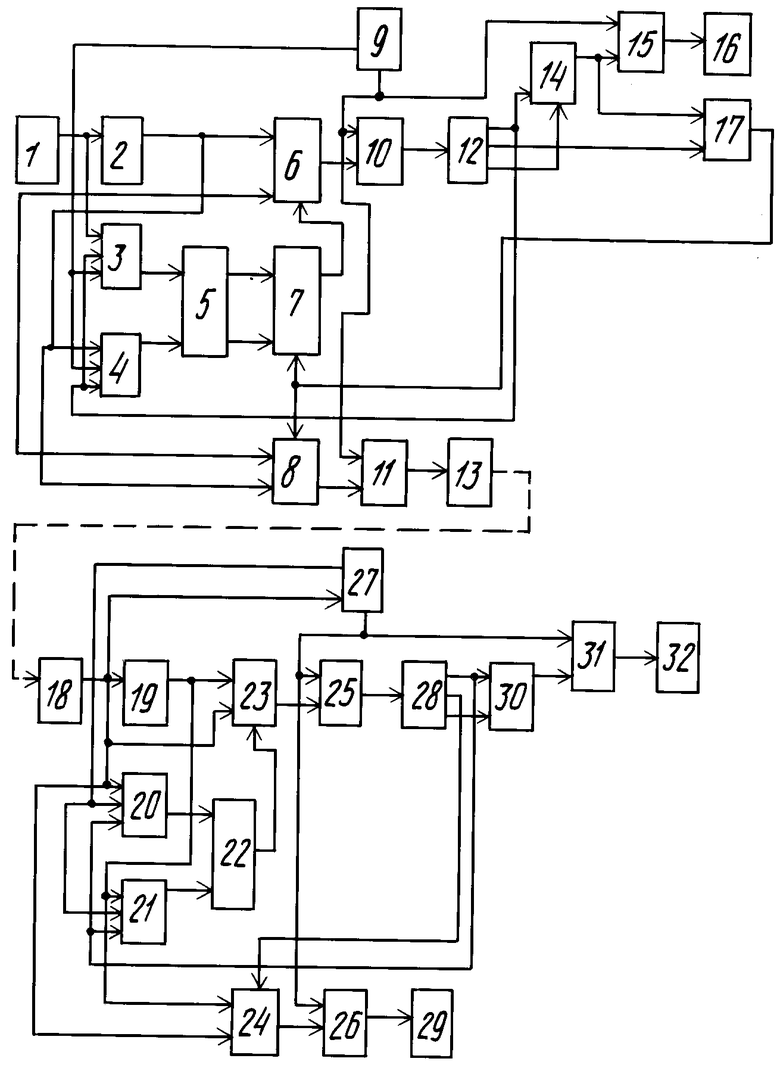

На чертеже представлена структурная электрическая схема устройства передачи и приема дискретных сообщений.

Устройство передачи, передачи и приема дискретных сообщений содержит на передающей стороне источник 1 цифрового сигнала, информационный инвертор 2, первый элемент 3И 3, второй элемент 3И 4, триггер знака 5, информационный мультиплексор 6, знаковый мультиплексор 7, канальный мультиплексор 8, генератор 9 синхроимпульсов, реверсивный счетчик 10, D-триггер 11, дешифратор 12, согласующий блок 13, RS-триггер 14, первый элемент 2И 15, блок 16 выделения синхросигнала, второй элемент 2И 17, а на приемной стороне - согласующий блок 18, информационный инвертор 19, первый элемент 3И 20, второй элемент 3И 21, триггер знака 22, информационный мультиплексор 23, канальный мультиплексор 24, реверсивный счетчик 25, D-триггер 26, дешифратор 27, блок 28 выделения цифрового сигнала, блок 29 синхронизации, RS-триггер 30, элемент 2И 31, блок выделения синхросигнала 32. Устройство работает следующим образом.

Источник цифрового сигнала 1 по переднему фронту тактовой частоты, которая поступает с элемента 2И 15 на вход блока 16 выделения синхросигнала, выдает новый бит информации, если до того момента текущая цифровая сумма была равна нулю, то в течение предыдущего полутакта предыдущий бит через элементы 3И устанавливает триггер знака 5 в такое состояние, чтобы предыдущий бит на входе управления реверсом был единичным после прохождения информационного мультиплексора. Таким образом на выходе реверсивного счетчика 10 в младшем разряде появится единица после переднего фронта тактовой частоты. Если в предыдущем такте на выходе источника цифрового сигнала была единица, то триггер знака 5 на прямом выходе также будет иметь 1, что приводит к передаче на вход управления реверсом реверсивного счетчика 10 неинвертированной информации с выхода источника цифровой информации 1. Теперь при появлении на выходе источника цифровой информации 1 единиц они будут суммироваться к содержимому реверсивного счетчика, а нули будут вычитаться.

В канал через канальный мультиплексор 18 передается неинвертированная информация с выхода источника цифрового сигнала 1. Если прошли две "1" подряд, на втором выходе дешифратора 12 появится "1", которая переключит знаковый мультиплексор 7 и тот в свою очередь переключит информационный мультиплексор 6 на инверсный канал, т. е. если появится единица, то на реверсивном входе счетчика 10 будет ноль и он вычтет единицу из текущей суммы, а если появится ноль, то на реверсивном входе будет единица и счетчик просуммирует единицу к текущей сумме. В это же время канальный мультиплексор также переключается на инверсный канал. Если прошла комбинация "110", то на третьем выходе дешифратора 12 появится "1", которая "перебросит" прямой выход RS-триггера 14 в "0" и запретит прохождение тактовой частоты на вход потребителя синхросигнала источника 17. Так как последним информационным битом на выходе источника цифрового сигнала 1 был "0", то он так и останется на следующие три такта, потому что тактовая частота к нему поступать не будет. За три последующих такта на выходе реверсивного счетчика 10 появится "00" и следовательно на первом выходе дешифратора появится "1", которая установит RS-триггер 14 в единичное состояние и разрешит выдачу тактовой частоты источнику.

Работа приемной части устройства аналогична работе передающей частоты. При нулевой текущей сумме реверсивного счетчика 25 знаковый триггер 2 изменяет свое состояние так, чтобы управляемый им информационный мультиплексор 23 подключал к входу управления реверсивного счетчика 25 тот канал на выходе которого содержится единица. Если текущая сумма равна 2, с второго выхода дешифратора 28 осуществляется управление подключением входа канального мультиплексора 24 к инверсному каналу. Если текущая сумма равна 3, то активный третий выход дешифратора 28 переводит прямой выход RS-триггера 30 в ноль и запрещает выдачу тактовой частоты блока выделения синхросигнала 32 до тех пор, пока текущая цифровая сумма не станет равной нулю.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2014736C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ, ПРИЕМА И ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2115240C1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА СООБЩЕНИЙ С ИСПОЛЬЗУЕМЫМ В ЛИНИИ СВЯЗИ КОДОМ NB(N+1)B | 1991 |

|

RU2012141C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОДВИГАТЕЛЕМ-МАХОВИКОМ | 1980 |

|

SU1840113A1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для управления многоканальным электроприводом тренажера | 1984 |

|

SU1180846A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Цифровой измеритель ускорения вала | 1985 |

|

SU1272254A1 |

Использование: в электросвязи при передачи дискретной информации по волоконно-оптическим линиям связи. Сущность изобретения: устройство содержит на передающей стороне источник 1 цифрового сигнала, информационный инвертор 2, первый, второй элементы 3И, 3, 4, триггер знака 5, информационный мультиплексор 6, знаковый мультиплексор 7, канальный мультиплексор 8, генератор 9 синхроимпульсов, реверсивный счетчик 10, D-триггер 11, дешифратор 12, согласующий блок 13, RS-триггер 14, первый, второй элементы 2И 15, 17, блок 16 выделения синхросигнала, а на приемной стороне согласующий блок 18, информационный инвертор 19, первый, второй элементы 3И 20, 21, триггер знака 22, информационный мультиплексор 23, канальный мультиплексор 24, реверсивный счетчик 23, D-триггер 26, дешифратор 27, блок 28 выделения цифрового сигнала, блок 29 синхронизации, RS-триггер 30, элемент 2И 31, блок выделения синхросигнала 32. 1 ил.

УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ, содержащее на передающей стороне источник цифрового сигнала, согласующий блок, а на приемной стороне - согласующий блок, блок выделения цифрового сигнала и блок выделения синхросигнала, отличающееся тем, что, с целью снижения избыточности линейного кодирования, на передающей стороне введены блок выделения синхросигнала, генератор синхроимпульсов, реверсивный счетчик, дешифратор, информационный мультиплексор, информационный инвертор, знаковый мультиплексор, триггер знака, первый и второй элементы 3И, канальный мультиплексор, D-триггер, RS-триггер, первый и второй элементы 2И, причем выход источника цифрового сигнала соединен с первыми входами информационного и канального мультиплексоров, входом первого элемента 3И и входом информационного инвертора, выход которого соединен с вторыми входами информационного и канального мультиплексоров и первым входом второго элемента 3И, выход информационного мультиплексора соединен с входом управления реверсивного счетчика, счетный вход которого соединен с прямым выходом генератора синхросигнала, первым входом первого элемента 2И и синхровходом D-триггера, выход реверсивного счетчика соединен с входом дешифратора, первый выход которого соединен с вторыми входами первого и второго элементов 3И, и входом установки единицы RS-триггера, второй выход дешифратора соединен с первым входом второго элемента 2И, выход которого соединен с управляющими входами знакового и канального мультиплексоров, третий выход дешифратора соединен с входом установки нуля RS-триггера, выход которого соединен с вторыми входами первого и второго элементов 2И, выход первого элемента 2И соединен с входом блока выделения синхросигнала, выход канального мультиплексора соединен с D-выходом D-триггера, выход которого соединен с входом первого согласующего блока, инверсный выход генератора синхроимпульсов соединен с третьими входами первого и второго элементов 3И, выход первого элемента 3И соединен с входом установки единицы триггера знака, а выход второго элемента 3И соединен с входом установки нуля триггера знака, прямой и инверсный выходы которого соединены с первым и вторым входами знакового мультиплексора, выход которого соединен с управляющим входом информационного мультиплексора, а на приемной стороне дополнительно введены блок синхронизации, реверсивный счетчик, дешифратор, информационный мультиплексор, информационный инвертор, триггер знака, первый и второй элементы 3И, канальный мультиплексор, D-триггер, RS-триггер, элемент 2И, причем выход второго согласующего блока соединен с первыми входами информационного и канального мультиплексоров, входом информационного инвертора, первым входом первого элемента 3И, входом блока синхронизации, выход информационного инвертора соединен с вторыми входами информационного и канального мультиплексоров и с первым входом второго элемента 3И, выход информационного мультиплексора соединен с входом управления реверсивного счетчика, счетный вход которого соединен с прямым выходом блока синхронизации, первым входом элемента 2И и синхровходом D-триггера, выход реверсивного счетчика соединен с входом дешифратора, первый выход которого соединен с вторыми входами первого и второго элементов 3И, и входом установки единицы RS-триггера, второй выход дешифратора соединен с управляющим входом канального мультиплексора, третий выход дешифратора соединен с входом установки нуля RS-триггера, выход которого соединен с вторым входом элемента 2И, выход которого соединен с входом блока выделения синхросигнала, выход канального мультиплексора соединен с D-входом D-триггера, выход которого соединен с входом блока выделения цифрового сигнала, инверсный выход блока синхронизации соединен с третьими входами первого и второго элементов 3И, выход первого элемента 3И соединен с входом установки единицы триггера знака, а выход второго элемента 3И соединен с входом установки нуля триггера знака, прямой выход которого соединен с управляющим входом информационного мультиплексора.

Авторы

Даты

1994-05-30—Публикация

1991-02-13—Подача