Изобретение относится к вычислительной технике и может быть использовано по прямому назначению для измерения, регистрации и анализа текущих значений физических величин вещественной, энергетической и информационной групп, а также для анализа формы физических процессов.

Известны многоканальные системы для регистрации физических величин [1] содержащие усилители, аналого-цифровые преобразователи, блоки памяти, коммутатор каналов, блок управления и регистратор.

Принцип действия известных систем заключается в адаптивной или неадаптивной дискретизации исследуемых процессов, выборке дискретных значений сигналов, преобразовании их в цифровой код и запоминании кодов в блоках памяти для восстановления впоследствии формы исследуемых сигналов или обработки полученных данных.

Известным многоканальным системам присущи недостаточная точность и ограниченные функциональные возможности, поскольку в них не предусмотрено использование структурно-алгоритмических методов коррекции погрешностей, а сам процесс ограничивается регистрацией формы выходных сигналов датчика. Кроме того, известные системы предназначены для исследований физических величин только одной группы, например, энергетической.

Известна многоканальная система для регистрации физических величин [2] В известной системе имеется возможность оперативно устанавливать заданные частоты дискретизации на заданных участках периода регистрации. Это позволяет значительно сократить объем запоминающих блоков при регистрации переходных процессов и импульсов сложной формы. Помимо этого имеется возможность воспроизводить последовательно ряд полных периодов регистрации с заданной частотой дискретизации в каждом периоде регистрации. Это позволяет, например, автоматически изменять программу испытаний различных источников аналоговых сигналов в заданном частотном диапазоне. Однако известной многоканальной системе присущи ограниченные функциональные возможности и недостаточная точность регистрации.

Известная многоканальная система не обеспечивает измерение и регистрацию дискретных величин. Наличие информационной избыточности не используется для повышения точности измерений и регистрации. Не реализованы какие-либо методы коррекции погрешностей измерительных каналов, отсутствует диагностика работоспособности основных функциональных блоков системы. Отмеченные недостатки ограничивают широкое использование известной системы для регистрации физических величин и процессов.

Целью изобретения является повышение точности за счет введения структурной и информационной избыточности и использования тестовых методов коррекции погрешностей, а также расширение области применения системы в части измерения и регистрации аналоговых и дискретных величин, использования режима автономного управления и накопления данных и т.д.

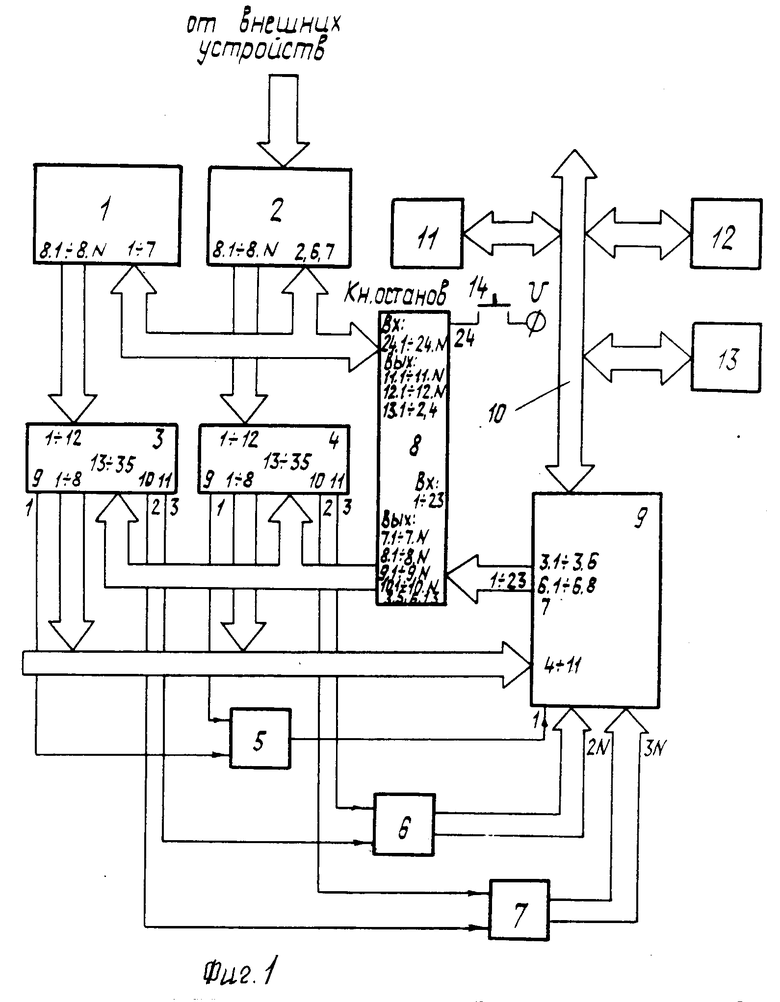

На фиг.1 приведена структурная схема многоканальной системы для регистрации физических величин; на фиг.2 структурная схема аналоговых каналов измерения; на фиг.3 структурная схема дискретных каналов измерения; на фиг.4 структурная схема i-го блока оперативной памяти (БОП); на фиг.5 структурная схема блока автономного управления; на фиг.6 структурная схема пульта управления, входящего в состав блока автономного управления; на фиг.7 структурная схема одного из буферных запоминающих устройств, входящих в состав блока автономного управления; на фиг.8 структурная схема интерфейса; на фиг.9 эпюры напряжений, характеризующие работу системы во времени; на фиг.10 и 11 структурная схема алгоритма работы системы; на фиг.12 эпюры напряжений, характеризующие процесс регистрации сигналов.

На фиг.1 приняты следующие обозначения: 1 аналоговые каналы измерения, 2 дискретные каналы измерения, 3 и 4 блоки оперативной памяти первой и второй групп, 5 элемент "ИЛИ", 6 и 7 первая и вторая группы элементов "НЕ", 8 блок автономного управления, 9 интерфейс, 10 общая шина, 11 накопитель на магнитной ленте, 12 вычислительный блок (ЭВМ), 13 процессор, 14 кнопка останова.

На фиг.2 приняты следующие обозначения: 15 источник опорного напряжения, 16 элемент "2И-ИЛИ-НЕ", 17 элемент "НЕ", 18 счетчик импульсов, 19 элемент "ИЛИ-НЕ", 20 одновибратор, 21 блок световой индикации, 22 коммутатор аналоговых сигналов, 23 формирователь; 24 аналого-цифровой преобразователь, 25.1-25.m m датчиков, 26.1-26.m m сумматоров, 27 первое аналоговое запоминающее устройство, 28.1-28. m m четных аналоговых запоминающих устройств, 29.1-29.m m нечетных аналоговых запоминающих устройств.

На фиг.3 приняты следующие обозначения: 30 коммутатор цифровых сигналов, 31.1-31. Rs Rs счетчиков импульсов, 32 (Rs+1)-й счетчик импульсов, 33 Rs+2 счетчик импульсов, 34 элемент "ИЛИ", 35.1-35.Rp Rp регистров, 36 (Rp+1)-й регистр, 37.1-37. Rs первые Rsформирователей, 38.1-38.Rp вторые Rp формирователей, 39 (Kf+1)-й (где Rf Rs + Rp) формирователь, 40.1-40.Rk Rk компараторов, 41 одновибратор.

На фиг.4 приняты следующие обозначения: 42 дешифратор, 43,44,45 первый, второй и третий счетчики импульсов, 46 и 47 первый и второй элементы "2И-ИЛИ-НЕ", 48,49 и 50 первый, второй и третий элементы "И-НЕ", 51 и 52 первый и второй элементы "ИЛИ-НЕ", 53 и 54 первый и второй одновибраторы, 55,56,57,58,59,60,61 и 62 первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы "И", 63,64,65 и 66 первый, второй, третий и четвертый элементы "НЕ", 67 и 68 первый и второй триггеры, 69-75 семь элементов "3И-ИЛИ-НЕ", 76-99 двадцать четыре блока памяти, 100 и 101 первый и второй четырехразрядные шинные формирователи.

На фиг.5 приняты следующие обозначения: 102 кварцованный генератор, 103 счетчик импульсов, 104 элемент "3И-ИЛИ-НЕ", 105 элемент "И", 106 и 107 первый и второй элементы "ИЛИ", 108 блок элементов "2И-ИЛИ", 109 управляемый делитель частоты, 110, 111, 112, 113, 114 и 115 первый, второй, третий, четвертый, пятый и шестой регистры, 116 и 117 первый и второй дешифраторы, 118 триггер, 119.1-119.N N нечетных буферных запоминающих устройств, 120.1-120.N N четных буферных запоминающих устройств, 121 (2N+1)-е буферное запоминающее устройство, 122.1-122. N N основных реверсных счетчиков, импульсов, 123.1-123. N N дополнительных реверсивных счетчиков импульсов, 124 (N+1)-й дополнительный реверсивный счетчик импульсов, 125.1-125.N первые N элементов "И-НЕ", 126.1-126. N вторые N элементов "И-НЕ", 127 формирователь импульсов сброса, 128 пульт управления.

На фиг. 6 приняты следующие обозначения: 129 136, 137, 138, 139-142, 142-145, 146, 147, 148, 149 и 150 первая-восьмая, девятая, десятая, одиннадцатая-четырнадцатая, четырнадцатая-семнадцатая, восемьнадцатая, девятнадцатая, двадцатая, двадцать первая и двадцать вторая кнопки, 151 158, 159, 160, 161 164, 164 167, 168, 169, 170, 171, 172 первый-восьмой, девятый, десятый, одиннадцатый-четырнадцатый, четырнадцатый-семнадцатый, восемнадцатый, девятнадцатый, двадцатый, двадцать первый, двадцать второй и двадцать третий формирователи импульсов, 173 счетчик импульсов, 174, 175, 176 и 177 первый, второй, третий и четвертый триггеры, 178 элемент "ИЛИ", 179 регистр, 180 дешифратор, 181 блок световой индикации.

На фиг.7 приняты следующие обозначения: 182 элемент "ИЛИ", 183 и 184 первый и второй одновибраторы, 185 элемент "И-НЕ", 187 счетчик импульсов, 188 блок памяти.

На фиг. 8 обозначено: 189 приемо-передатчики, 190 и 191 первый и второй дешифраторы, 192 регистр вывода данных, 193 регистр команд, 194 регистр ввода, 195 регистр состояний, 196 передатчик, 197 приемник.

При этом выводы 8.1-8.N аналоговых и дискретных каналов 1 и 2 измерения соединены с информационными входами 1-12 блоков 3 и 4 оперативной памяти соответственно.

Управляющие входы (входы 1-6 и выход 7) каналов 2 и 3, подключены к входам/выходам (к выходам 11.1-11. N, 12.1-12.N, 13,1,2,4 и входам 24.1-24.N соответственно) блока 8 автономного управления системой. Выводы кнопки 14 "останов. " подключены к источнику постоянного напряжения "U" и управляющему входу 24 блока 8 автономного управления. Выходы блока 8 автономного управления (выходы 7.1-7.N, 8.1-8.N, 9.1-9.N, 10.1-10.N, 3,5,6 и 13) соединены с объединенными управляющими входами (35,13-19,20-24,32,28,27,34 и 25 соответственно) соответствующих блоков 3 и 4 оперативной памяти обеих групп. Информационные входы дискретных каналов 2 измерения являются входами системы. Одноименные информационные выходы 1-8 блоков 3 и 4 оперативной памяти обеих групп объединены между собой и подключены к информационным входам (входам 4-11) интерфейса 9. Выходы (1-23) интерфейса 9 соединены с информационными входами (одноименными входами 1-23) блока 8 автономного управления. Первые управляющие выходы (выходы 9) блоков 3 и 4 оперативной памяти обеих групп соединены с входами элемента "ИЛИ" 5. Выход элемента "ИЛИ" 5 подключен к первому управляющему входу интерфейса 9. Вторые и третьи управляющие выходы (выходы 10 и 11) блоков 3 и 4 оперативной памяти обеих групп соединены с входами соответствующих элементов "НЕ" 6 и 7 соответственно первой и второй групп. Выходы элементов "НЕ 6 и 7 подключены соответственно, ко вторым (2N) и третьим (3N) управляющим входам интерфейса 9.

Входы/выходы интерфейса 9 соединены с входами/выходами ЭВМ 12, процессора 13 и накопителя 11 на магнитной ленте через общую шину 10.

В каждом из N аналоговых каналов 1 измерения системы к источнику опорного сигнала 15 подключены первые входы m сумматоров 26.1.26.m. Вторые входы сумматоров 26.1.26.m соединены с сигнальными (первыми входами аналоговых запоминающих устройств 28.1.28.m и подключены к выходам датчиков 25.1.25.m соответственно. Выходы m сумматоров 26.1. 26. m соединены с сигнальными (первыми) входами нечетных аналоговых запоминающих устройств 29.1-29.m. Сигнальный (первый) вход первого аналогового запоминающего устройства 27 подключен к источнику опорного сигнала 15.

Выходы аналоговых запоминающих устройств 27-29.m соединены со входами коммутатора 22 аналоговых сигналов, управляющие входы которого подключены к выходам счетчика импульсов 18. Выход старшего разряда счетчика импульсов 18 дополнительно соединен с первым входом элемента "2И-ИЛИ-НЕ" 16 и через одновибратор 20 с первым входом элемента "ИЛИ-НЕ" 19. Выход элемента "ИЛИ-НЕ" 19 подключен к входу установки нуля счетчика импульсов 18.

Второй вход элемента "ИЛИ-НЕ" 19, второй, третий и четвертый входы элемента "2И-ИЛИ-НЕ" 16 и вход элемента "НЕ" 17 являются соответственно вторым, третьим, четвертым, пятым и шестым управляющим входами аналоговых и дискретных каналов 1 и 2 измерения.

Выход элемента "2И-ИЛИ-НЕ" 16 подключен к объединенным (вторым) синхронизирующим входам аналоговых запоминающих устройств 27.29.m.

В каждом из дискретных каналов 2 системы входы коммутатора 30 цифровых сигналов подключены, соответственно, к выходам Rp регистров 35.1-35.Rp, (Rp+1)-го регистра 36, Rs счетчиков импульсов 31.1-31.Rs и паре выходов (Rs+1)-го счетчика импульсов 32. Управляющие входы коммутатора 30 цифровых сигналов соединены с одноименными входами элемента "ИЛИ" 34 и подключены к выходам (Rs+2)-го счетчика импульсов 33. Счетный вход счетчика импульсов 33 соединен через (Rs+1)-й формирователь 39 с шестым управляющим входом дискретного канала. Счетные входы (Rs+1)-х счетчиков импульсов 31.1.31.Rs соединены с выходами соответствующих Rs формирователей 37.1.37.Rs. Выходы Rp формирователей 38.1. 38.Rp подключены соответственно к управляющим входам Rp регистров 35.1. 35. Rp. Входы (Rp+1)-го регистра 36 соединены с выходами Rkкомпараторов 40.1.40.Rk. Входы установки нулей Rs-го и (Rp+2)-го счетчика импульсов 31.1. 31. Rs и 33 объединены между собой и подключены к второму управляющему входу дискретного канала. Первый, третий, четвертый и пятый управляющие входы дискретного канала свободны. Выходы коммутатора 30 цифровых сигналов и одновибратора 31 являются информационными выходами дискретного канала, входы которого соединены с входами Rk компараторов 40.1-40. Rk, Rf формирователей 37.-37.Rs, 38.1-38.Rp и с входами регистров 35.1-35. Rp.

В блоках 3 и 4 оперативной памяти первые и третьи входы элементов "3И-ИЛИ-НЕ" 69.75 подключены соответственно к одноименным первой и второй семерке выходов разрядов параллельного кода первого счетчика импульсов 43. Вторые входы элементов "3И-ИЛИ-НЕ" 69.75 объединены между собой, с первым входом первого элемента "ИЛИ-НЕ" 51 и подключены к двадцать девятому входу блока оперативной памяти. Четвертые входы элементов "3И-ИЛИ-НЕ" 69.75 объединены между собой и подключены к тридцатому входу блока оперативной памяти. Пятые входы элементов "3И-ИЛИ-НЕ" 69.75 объединены между собой и подключены к выходу второго одновибратора 54. Шестые входы каждого элемента "3И-ИЛИ-НЕ" 69. 75 соединены с соответствующими, начиная с младшего разряда, выходами второго счетчика импульсов 44. Выходы элементов "3И-ИЛИ-НЕ" 69.75 подключены к объединенным между собой одноименным адресным входам блоков памяти 76.99.

Три группы входов "Д1" блоков памяти 76.99 соединены соответственно с входами, например, 1.12, 13.19, 20.24-го блока оперативной памяти (БОП). Входы "CAS" 1.8, 9.16 и 17.24-го блоков памяти 76.99 объединены между собой, соединены с первыми входами четвертого, пятого и шестого элементов "И" 58,59,60 и подключены к выходам первого, второго и третьего элементов "И" 55,56,57 соответственно. Входы "RAS" всех блоков памяти 76.99 объединены и соединены с выходом первого элемента "ИЛИ-НЕ" 51. Входы "WE" каждой восьмерки блоков памяти 76.99 (76.83, 84.91, 92.99) объединены между собой и подключены соответственно к выходам четвертого, пятого и шестого элементов "И" 58,59 и 60. Вторые входы четвертого, пятого и шестого элементов "И" 58,59 и 60 объединены между собой, соединены с четвертым входом элемента "2И-ИЛИ-НЕ" 47 и подключены к выходу третьего элемента "И-НЕ" 50. Одноименные входы 1.8-го, 9.16-го и 17.24-го блоков памяти 76.83, 84.91 и 91.99 объединены между собой и соединены (по четыре) с входами первого и второго четырехразрядных шинных формирователей 108 и 109. Управляющие входы "УВ" шинных формирователей 100 и 101 соединены между собой и подключены к клемме питания "U".

Синхронизирующие входы "ВК" шинных формирователей 100 и 101 соединены с входами четвертого элемента "НЕ" 66, со счетным входом третьего счетчика 45 импульсов и подключены к выходу первого элемента "И-НЕ" 48. Выходы 1.4 и 5.8 первого и второго шинных формирователей 100 и 101 соединены с выходами 1.4, 5.8 БОП. Девятый выход БОП подключен к выходу четвертого элемента "НЕ" 66. Двадцать пятый вход БОП соединен с входом второго элемента "НЕ" 64 и с входами установки нуля первого счетчика 43 импульсов. Двадцать шестой вход соединен с третьим входом первого элемента "2И-ИЛИ-НЕ" 46. Двадцать седьмой вход через первый одновибратор 53 подключен к первому входу второго элемента "И-НЕ" 49. Двадцать восьмой вход соединен с входом второго одновибратора 54 и через третий элемент "НЕ" 65 со счетным входом второго счетчика импульсов 44. Тридцать первый вход БОП подключен к второму входу первого элемента "ИЛИ-НЕ" 51. Тридцать второй и тридцать четвертый входы БОП соединены соответственно с входами установки единицы первого и второго триггеров 67 и 68. Тридцать третий и тридцать пятый входы подключены соответственно к первым входам седьмого и восьмого элементов "И" 61 и 62. Выход восьмого элемента "И" 62 соединен с вторым входом третьего элемента "И-НЕ" 50. Второй вход восьмого элемента "И" 62 соединен с десятым выходом БОП, с вторым входом восьмого элемента "И-НЕ" 49, с первым входом третьего элемента "И-НЕ" 50 и подключен к прямому выходу второго триггера 68. Вход установки нуля второго триггера 68 подключен к выходу второго элемента "ИЛИ-НЕ" 52, чей первый вход соединен с выходом второго элемента "НЕ" 64. Второй вход второго элемента "ИЛИ-НЕ" 52 соединен с первым и вторым входами первого элемента "2И-ИЛИ-НЕ" 46 и подключен к старшему разряду первого счетчика 43 импульсов. Инверсный выход второго триггера 68 соединен с третьим входом седьмого элемента "И" 61. Выход седьмого элемента "И" 61 подключен к третьему входу второго элемента "2И-ИЛИ-НЕ" 47 и второму входу первого элемента "И-НЕ" 48. Второй вход седьмого элемента "И" 61 соединен с одиннадцатым выходом БОП, с первым входом первого элемента "И-НЕ" 48 и подключен к прямому выходу первого триггера 67. Инверсный выход триггера 67 соединен с третьим входом восьмого элемента "И" 62. Вход установки нуля первого триггера 67 подключен к выходу первого элемента "2И-ИЛИ-НЕ" 46, четвертый вход которого соединен через первый элемент "НЕ" 63 со счетным входом первого счетчика 43 импульсов и подключен к выходу элемента "2И-ИЛИ-НЕ" 47. Первый и второй входы элемента "2И-ИЛИ-НЕ" 47 соединены с входом установки нуля третьего счетчика 45 импульсов и подключен к четвертому выходу дешифратора 42. Входы дешифратора 42 соединены с выходами третьего счетчика 45 импульсов. Первый, второй и третий выходы дешифратора 42 подключены к вторым входам первого, второго и третьего элементов "И" 55,56, и 57 соответственно. Первые входы элементов "И" 55,56 и 57 объединены между собой и подключены к входу второго элемента "И-НЕ" 49.

В блоке 8 автономного управления входы установки нуля 2N+1 буферных запоминающих устройств 119.1.121 объединены, соединены с входами установки нуля счетчика 103 импульсов, с входами установки нулей основных и дополнительных реверсивных счетчиков 122.1.124 импульсов, с первым дополнительным выходом блока 8 автономного управления и подключены к инверсному выходу формирователя 127 импульсов сброса, подключенного своим входом к клемме питания "U". Управляющие входы буферных запоминающих устройств 119.1.121 соединены с соответствующими выходами первого дешифратора 116. Одноименные информационные входы буферных запоминающих устройств 119.1.121 объединены и подключены к соответствующим выходам блока элементов "И-ИЛИ" 108. Входы пересчета адреса каждой i-й пары первых 2N буферных запоминающих устройств 119.1.120.N объединены между собой и подключены к выходу переполнения "P"_ и к входу перезаписи i-го дополнительного счетчика 123.J импульсов, за исключением (N+1)-го дополнительного счетчика 124 импульсов. Выходы нечетных и четных буферных запоминающих устройств 119.1.121 соединены с одноименными информационными входами соответственно основных и дополнительных реверсивных счетчиков 122.1.124 импульсов. Счетные входы реверсивных счетчиков 122.1.102.N импульсов объединены между собой и подключены к выходу управляемого делителя частоты 109. Выход каждого i-го основного реверсивного счетчика 122.J (где i 1,2,3,N) импульсов соединен со счетным входом соответствующего N-го дополнительного реверсивного счетчика 123.J (где i 1,2,3,N) импульсов. Выход N-го дополнительного реверсивного счетчика 123.N импульсов подключен к счетному входу (N+1)-го дополнительного счетчика 124 импульсов. Вход перезаписи кода (N+1)-го дополнительного счетчика импульсов 124 соединен с входом пересчета адреса (2N+1)-го буферного запоминающего устройства 121 и подключен к третьему выходу пульта управления 128. Выход переполнения "P"_ (N-1)-го дополнительного реверсивного счетчика импульсов 124 соединен с пятым входом элемента "3И-ИЛИ-НЕ" 104. Выход переполнения "P"_ каждого i-го основного реверсивного счетчика 122.J импульсов соединен со входом переустановки (перезаписи) кода этого же счетчика импульсов и со вторым входом i-го (125.J, где i 1,2, N) и первых N элементов "И-НЕ" 125.1.125.N. Выход параллельного кода каждого i-го (i ≠ N + 1) дополнительного реверсивного счетчика 123.J импульсов вместе с выходами параллельного кода (N+1)-го дополнительного реверсивного счетчика 124 импульсов составляют N информационных выходов блока автономного управления 8. Первые N управляющих выходов блока автономного управления 8 соединены с выходами первых N элементов "И-НЕ" 125.1.125.N. Первые входы элементов "И-НЕ" 125.1.125.N подключены к соответствующим управляющим входам 24.1.24.N блока автономного управления 8. Третьи входы соединены с выходами разрядов четвертого регистра 113. Четвертые входы первых N элементов "И-НЕ" 125.1.125.N объединены между собой, соединены с шестым выходом блока 8 автономного управления и подключены к восьмому выходу второго дешифратора 117. Первый, второй, третий, четвертый и седьмой выходы второго дешифратора 117 соединены соответственно с первым, вторым, третьим, четвертым и пятым синхронизирующими выходами блока 8 автономного управления. Первые и вторые N управляющих выходов 10.1.10.N блока 8 автономного управления соединены соответственно с выходами первых и вторых N элементов "И-НЕ" 126.1.126.N. Первые входы вторых N элементов "И-НЕ" 126.1-126.N подключены к одноименным выходам разрядов пятого регистра 114. Третьи входы элементов "И-НЕ" 126.1. 126. N объединены и через первый вход элемента "ИЛИ" 107 соединены с шестым выходом пульта управления 128. Третьим 2N управляющих (парафазных) выходов 11.1.11.N и 12.1.12.N блока 8 автономного управления подключены к соответствующим парафазным выходам шестого регистра 115. Одноименные информационные входы шести регистров 110, 111, 112, 113, 114 и 115 объединены между собой и соединены с соответствующими выходами блока элементов "И-ИЛИ" 108.

Управляющие входы каждого из шести регистров 110.115 через элементы "И-ИЛИ" блока элементов "И-ИЛИ" 108 соединены с соответствующими выходами дешифратора 180 пульта управления 128.

Выходы первого и второго регистров 110 и 111 соединены с установочными входами управляемого делителя частоты 109, счетный вход которого подключен к выходу кварцованного генератора 102, с которым соединен и счетный вход счетчика импульсов 103. Своими выходами счетчик импульсов 103 подключен к входам второго дешифратора 117.

Вход установки нуля управляемого делителя 109 частоты соединен с первым входом пульта управления 128 и подключен к выходу триггера 118. Вход установки единицы триггера 118 соединен с первым выходом пульта управления 128. Вход установки нуля триггера 118 соединен с вторым входом элемента "И" 105 и подключен к выходу элемента "3И-ИЛИ-НЕ" 104, первый и второй входы которого соединены с прямым выходом формирователя 127 импульсов сброса. Третий и четвертый входы элемента "3И-ИЛИ-НE" 104 подключен к выходу первого элемента "ИЛИ" 106. Шестой вход элемента "3И-ИЛИ-НЕ" 104 соединен с вторым выходом пульта управления 128. Четвертый и пятый выходы пульта управления 128 соединены соответственно с первым и вторым управляющими входами блока элементов "И-ИЛИ" 108. Дополнительный выход блока элементов "И-ИЛИ" 108 подключен к первому входу первого элемента "ИЛИ" 106. Второй вход первого элемента "ИЛИ" 106 соединен с дополнительным входом 24 блока 8 автономного управления. Входная шина 1.21, 22, 23 блока 8 автономного управления подключена к первым входам элементов "ИЛИ" блока 108 элементов "И-ИЛИ" и ко вторым входам пульта 128 управления и второго элемента "ИЛИ" 107. Вторые входы блока 108 элементов "И-ИЛИ" соединены с выходной шиной пульта управления 128. При этом выход элемента "И" 105 является дополнительным выходом "Уст.0" блока 8 автономного управления.

В пульте 128 управления входы двадцати двух кнопок 129.150 объединены между собой и подключены к клемме питания. Выходы кнопок 129.150 соединены с входами формирователей 151.172 соответственно. Выходы первых восьми формирователей 151.158 импульсов подключены к первому-восьмому разрядным входам регистра 179.

Управляющий вход регистра 179 соединен с двадцать шестым входом блока 181 световой индикации и подключен к выходу девятого формирователя 159 импульсов. Первый-восьмой выходы регистра 179 соединены с одноименными выходами пульта 128 управления.

Девятый-четырнадцатый входы блока 181 световой индикации подключены к одноименным выходам 9.14 пульта 128 управления, представляющими собой шину адреса, и соединены соответственно с первым-шестым выходами дешифратора 180. Входы дешифратора 180 через счетчик 173 импульсов подключены к выходам десятого формирователя 160 импульсов.

Пятнадцатый-двадцатый входы блока 181 световой индикации соединены с одноименными выходами 15.20 пульта 128 управления, составляющими совместно с его двадцать первым выходом шину управления, и подключены соответственно к выходам одиннадцатого-шестнадцатого формирователей 161-164 импульсов. Двадцать первый вход блока 181 световой индикации соединен с одноименным выходом пульта 128 управления и подключен к прямому выходу первого триггера 174. Счетный вход первого триггера 174 соединен с выходом семнадцатого формирователя 167 импульсов.

Двадцать второй вход блока 181 световой индикации соединен с выходом восемнадцатого формирователя 168 импульсов и подключен к первому дополнительному выходу пульта 128 управления. Второй дополнительный выход пульта 128 управления соединен с двадцать третьим входом блока 181 световой индикации и подключен к прямому выходу второго триггера 175. Счетный вход триггера 175 соединен с выходом девятнадцатого формирователя 169 импульсов.

Третий дополнительный выход пульта управления соединен с двадцать четвертым входом блока 181 световой индикации и подключен к прямому выходу третьего триггера 176. Счетный вход триггера 176 соединен с выходом двадцатого формирователя 170 импульсов.

Четвертый дополнительный выход пульта 128 управления соединен с двадцать пятым входом блока 181 световой индикации и подключен к прямому выходу четвертого триггера 177. Вход установки единицы триггера 177 соединен с выходом двадцать первого формирователя 171. Вход установки нуля триггера 177 подключен к выходу элемента "ИЛИ" 178, первый вход которого соединен с выходом двадцать второго формирователя 172 импульсов. Инверсный выход четвертого триггера 177 соединен с пятым дополнительным выходом пульта 128 управления.

Шестой дополнительный выход пульта 128 управления подключен к входу четырнадцатого формирователя 164 импульсов. Двадцать седьмой вход блока 181 световой индикации является первым входом пульта 128 управления, второй вход которого подключен к второму входу элемента "ИЛИ" 178.

В буферном запоминающем устройстве 119-121 выходы первого и второго одновибраторов 183 и 184 подключены к входам управления V "чтение" и W "запись" блока 188 памяти, выходы которого являются выходами буферного запоминающего устройства.

Вход первого одновибратора 183 соединен с вторым входом элемента "ИЛИ" 182 и является управляющим входом "чтение" буферного запоминающего устройства. Третий вход элемента "ИЛИ" 182 соединен с первым входом элемента "И" 186 и является управляющим входом "запись" буферного запоминающего устройства. Адресные входы блока 188 памяти соединены с выходами счетчика 187 импульсов.

Вход установки нуля счетчика 187 импульсов является входом установки нуля буферного запоминающего устройства. Счетный вход счетчика 187 импульсов подключен к выходу элемента "И-НЕ" 185. Первый вход элемента "И-НЕ" 185 соединен с вторым входом элемента "И" 186 и является первым управляющим входом буферного запоминающего устройства. Второй вход элемента "И-НЕ" 185 подключен к выходу элемента "ИЛИ" 182. Третий вход элемента "И-НЕ" 185 является вторым управляющим входом буферного запоминающего устройства, который совместно с управляющими входами "чтение", "запись" и шиной данных блока 188 памяти составляет шину управления и данных буферного запоминающего устройства.

В интерфейсе 9 к общей шине подключены и входы первого дешифратора 190 и приемо-передатчики 189, с которыми соединены входы и выходы регистров 192 и 194 вывода и ввода данных с предвключенными соответственно передатчиками 196 и приемниками 197, входы регистра 193 команд с вторым дешифратором 191 и выходы регистра 195 состояний. Первый, второй, третий и четвертый выводы первого дешифратора 190 соединены с адресными входами регистра 192 вывода данных, регистра команд 193, регистра ввода 194 и регистра 195 состояния соответственно.

Выходы передатчика 196 данных регистра 192 вывода и выходы второго дешифратора 191 подключены к выходной шине интерфейса 9. Входная шина интерфейса 9 соединена с входами приемника 197 регистра 194 ввода и входами регистра 195 состояния. Выходы данных регистра 192 вывода используются в качестве шины данных блока 8 автономного управления и подключены через передатчики 196 к первым восьми выходам 1.8 интерфейса 9. Следующие шесть выходов (9.14) интерфейса 9 соединены с шестью выходами (1.6) второго дешифратора 191 и используются в качестве шины адреса регистров 110.115 блока 8 автономного управления. Остальные семь выходов 7.13 второго дешифратора 191 и выход 22 строб-импульса регистра 192 вывода данных подключены к последним восьми выходам 14.22 интерфейса 9, используются в качестве шины управления блока 8 автономного управления. Причем выход 22 интерфейса 9 соединен с выходом регистра 192 через один из передатчиков 196.

Первый вход интерфейса 9 через один из приемников соединен с входом строб-импульса регистра 194 ввода. Второй и третий входы интерфейса 9 соединены соответственно с первым и вторым входами регистра 195 состояния и используются по прямому назначению, как и остальные входы регистра ввода 194, соединенные с входами 4.11 интерфейса 9 через приемник 197.

Работа системы поясняется эпюрами напряжений, приведенными на фиг.12, и заключается в следующем.

Как уже отмечалось, заявляемая система содержит в своем составе аналоговые каналы измерения физических величин вещественной и энергетической групп (например, объема вещества, расхода, вязкости, концентрации, диэлектрической проницаемости, потребляемой мощности объекта, тока, напряжения, энергии излучения и т.д.), а также дискретные каналы, представляющие собой каналы передачи информации о физических величинах информационной группы (амплитудно-частотного спектра, корреляционной функции, суммы или разности сигналов, интегрального значения сигнала и т.д.). В последнем случае к дискретным каналам подключаются выходы цифровых анализаторов спектра, коррелометров, интеграторов и другие приборы информационной группы. При необходимости дискретные каналы могут быть использованы для подключения образцовых средств измерений (с цифровым выходом).

Каждый канал системы позволяет подключать от одного до m датчиков (фиг. 2), от одного до Rp цифровых приборов, от одного до Rk аналоговых приборов и до Rs+1 преобразователей или приборов с частотным выходом (фиг.3).

Предположим, что датчики 25.1-25.m физических величин аналоговых каналов 1 подключены к исследуемому объекту, а выходы дополнительных приборов, используемых при изучении объекта, подключены к соответствующим входам дискретных каналов 2.

Система обеспечивает два режима работы: автономный режим (АР) регистрации физических процессов и величин и режим автоматического управления (АУ) процессами регистрации и измерения.

В режиме автономного (ручного) управления вместо ЭВМ 12 может быть подключен накопитель 11 на магнитной ленте, например, типа ЕС.004.09, или любой другой кассетный магнитофон, сопрягаемый с общей шиной 10.

В режиме автономного управления система работает следующим образом.

После включения напряжения питания на клемме "U" блока 8 автономного управления (БАУ) появится напряжение, которое запускает формирователь 127 импульсов сброса. Выходной импульс с инверсного выхода формирователя 127 поступает на входы установки нуля счетчиков импульсов 187 буферных запоминающих устройств (БЗУ) 119.1.119.N, 120.1.120.N, 121, реверсивных счетчиков импульсов (РСИ) 122.1.122.N, 123.1.123.N и 124, а также на вход установки нуля счетчика импульсов 103 блока 8 автономного управления.

Одновременно импульс сброса с инверсного выхода формирователя 127 поступает на первый вход элемента "И" 105. Импульс сброса с выхода элемента "И" 105 через тринадцатый выход блока 8 автономного управления поступает на вторые входы аналоговых и дискретных каналов 1 и 2 (фиг.2,3) и на двадцать пятые входы блоков 3 и 4 оперативной памяти (фиг.4), устанавливая их счетчики и триггеры в исходное нулевое состояние.

В тот же момент времени после включения питания с прямого выхода формирователя 127 импульс сброса через элемент "3И-ИЛИ-НЕ" 104 поступает на второй вход элемента "И" 105 и на вход установки нуля триггера 118. Последний обеспечивает управление работой делителя частоты 109. При поступлении управляющего импульса на вход установки нуля триггера 118 управляемый делитель частоты обнуляется. На его выходе тактовые импульсы будут отсутствовать. При подаче импульса на вход установки единицы триггера 118 формируется сигнал, разрешающий работу управляемого делителя частоты 109.

Необходимо отметить, что установка в единицу триггера 118 осуществляется с пульта управления 128. При нажатии кнопки "Пуск" 146 на выходе формирователя 168 появится импульс, который поступает через первый выход пульта управления 128 на вход установки единицы триггера 118. С помощью пульта управления 128 в нуль триггер 118 не устанавливается. Но, нажатием кнопки 147 "ЦД" [циклический (конечный во времени) или длительный (практически бесконечный) режим работы системы] на выходе формирователя 169 появляется импульс, поступающий на счетный вход второго триггера 175, устанавливая его в состояние нуля или единицы. Выходной сигнал триггера 175 поступает через второй выход пульта управления 128 на шестой вход элемента "3И-ИЛИ-НЕ" 104, тем самым разрешая или запрещая прохождение импульса с выхода "P"_ реверсивного счетчика импульсов 124 через элемент "3И-ИЛИ-НЕ" 104 на вход установки нуля триггера 118.

После установки в нуль управляемого делителя частоты 109 сигнал на его выходе будет отсутствовать.

Отсутствие выходного сигнала на выходе управляемого делителя частоты (УДЧ) 109 приведет к отсутствию процесса дискретизации выходных сигналов датчиков 25.1.25.m.

После включения питания системы начинает работать кварцованный генератор 102 блока 8 автономного управления (фиг.5), генерируя импульсы с частотой f01 1 мГц.

Счетчик 103 с коэффициентом пересчета, равным десяти, сразу же после сброса его в нуль производит пересчет выходных импульсов генератора 102. С помощью дешифратора 117, подключенного к выходам счетчика 103, осуществляется дешифрация состояний последнего и формирование импульсов синхронизации. Последние осуществляют синхронизацию работы аналоговых запоминающих устройств (АЗУ) 27, 28.1.28.m, 29.1.29.m и аналого-цифровых преобразователей 24 аналоговых каналов 1; регенерацию блоков памяти (БП) 76.99, синхронизацию процесса записи информации в блоке 3 и 4 оперативной памяти системы и окончание процесса измерения (записи информации в БОП).

После установки функциональных блоков системы в исходное состояние оператор нажимает кнопку 149 выбора режима "РУ/АУ" (ручное или автоматическое управление) пульта управления 128 (фиг.6). Сформированный с помощью блока 171 сигнал переводит триггер 177 в состояние "1" и "0" на его прямом и инверсном выходах, а, следовательно, и на четвертом и пятом выходах пульта управления 128 (фиг.5). Эти сигналы поступают на входы "И" блока элементов "И-ИЛИ" 108. Сигнал логического нуля с пятого пульта управления 128 запрещает прохождение сигналов на выход блока элементов "И-ИЛИ" 108 с входом 1-21 блока 8 автономного управления (или с первых входов блокa 108). Сигнал логической единицы с четвертого выхода пульта управления 128 разрешает прохождение на выходы блока элементов "И-ИЛИ" 108 только сигналов с выходов 1-21 пульта управления 128. Необходимо отметить, что любая команда, поданная с помощью кнопок 129-150 пульта управления 128, отображается с помощью блок 181 световой индикации.

После установки режима ручного управления (РУ) путем многократного (до 6 раз) нажатия кнопки 138 установки адреса регистров ("АР") (фиг.6) счетчик импульсов 173 переводится в состояние, при котором блок 181 световой индикации указывает, например, адрес первого регистра 110 ("РЧ1"). С помощью кнопок 129-136 набирается 8-й разрядный код младших разрядов управляемого делителя частоты 109 (фиг.5), который вначале заносится в регистр 179 пульта управления 128. Контроль за состоянием разрядов регистра 179 осуществляется с помощью блока 181 световой индикации. Нажатием кнопки 137 ввод данных ("ВД") осуществляется перезапись данных в регистр 110 из регистра 179. Последующее однократное нажатие кнопки 138 "АР" обеспечивает появление сигнала на втором выходе дешифратора 180 адреса, разрешающем запись данных во второй регистр 111 блока 8 автономного управления. С помощью кнопок 129-136 нбирается 8-и разрядный код старших разрядов управляемого делителя частоты 109. Нажатием кнопки 137 "ВД" осуществляется ввод данных регистра 179 в регистр 111.

Таким образом осуществляется установки 16-ти разрядного значения коэффициента пересчета управляемого делителя частоты 109. Разрешение на пересчет импульсов с помощью УДЧ 109 выдается после записи данных в остальные четыре регистра 112, 113, 114, 115 блока 8 автономного управления (фиг.5) путем нажатия кнопки 146 "Пуск". В результате выходной сигнал формирователя 168, подключенного к кнопке 146, выдает сигнал логического нуля. Последний через первый выход пульта управления 128 поступит на вход установки единицы триггера 118 блока 8 автономного управления. Этот сигнал переведет триггер 118 в единицу и тем самым разрешит прохождение счетных импульсов с выхода генератора 102 через управляемый делитель частоты 109. печивает появление сигнала на втором выходе дешифратора 180 адреса, разрешающем запись данных во второй регистр 111 блока 8 автономного управления. С помощью кнопок 129-136 нaбирается 8-и разрядный код старших разрядов управляемого делителя частоты 109. Нажатием кнопки 137 "ВД" осуществляется ввод данных регистра 179 в регистр 111. Таким образом осуществляется установка 16-ти разрядного значения коэффициента пересчета управляемого делителя частоты 109. Разрешение на пересчет импульсов с помощью УДЧ 109 выдается после записи данных в остальные четыре регистра 112, 113, 114, 115 блока 8 автономного управления (фиг.5) путем нажатия кнопки 146 "Пуск". В результате выходной сигнал формирователя 168, подключенного к кнопке 146, выдает сигнал логического нуля. Последний через первый выход пульта управления 128 поступит на вход установки единицы триггера 118 блока 8 автономного управления. Этот сигнал переведет триггер 118 в единицу и тем самым разрешит прохождение счетных импульсов с выхода генератора 102 через управляемый делитель частоты 109.

Затем оператор устанавливает заданные значения частот дискретизации или съема информации по каждому из каналов. Частота дискретизации выбирается в соответствии с условиями эксперимента и частотным диапазоном исследуемых физических процессов. Необходимо отметить, что на информационных выходах каждого из каналов данные появляются с частотой следования f02 100 кГц, равной частоте синхронизации. Чтобы исключить информационную избыточность и переполнение емкости памяти БОП системы, заранее определяется, сколько значений амплитуд выборок и по каким каналам следует записать в БОП. Причем для регистрации переходных процессов необходимо большее число данных, чем при регистрации установившихся процессов в исследуемом объекте.

Для обеспечения хода эксперимента с разными частотами дискретизации и съема информации в блок 8 автономного управления введено 2N + 1 БЗУ 119.1-119. N, 120.1-120. N, 121, в которые заносятся данные о значении частот fgi дискретизации, о числе Nbi выборок с заданной частотой и о количество циклов Nц с заданной программой исследований (т.е. с заданными fgi и Nbi). Выбор того или иного БЗУ осуществляется указанным выше способом путем записи в регистр 112 адреса БЗУ. С помощью первого дешифратора 116 входной код дешифрируется и в соответствующее БЗУ заносятся данные о ходе эксперимента. Причем в первые N БЗУ 119.1-119.N заносятся значения частот дискретизции по каждому каналу, во вторые N БЗУ 120.1-120.N вводятся данные о числе выборок или снимаемых данных по тому же каналу, а в БЗУ 121 заносятся данные о количестве циклов регистрации или измерения по заданной программе. Следует отметить, что емкость каждого БЗУ выбрана равной 128 бит. Т.е. в память БЗУ может быть записано по шестнадцать 8-и разрядных данных о значениях частот, числе выборок и количестве циклов. Практически в память первых N БЗУ записываются 8-и разрядные коды данных, а во вторые БЗУ 7-и разрядные коды данных, поскольку используются соответственно 8-и разрядные основные и 7-и разрядные (за исключением 5-и разрядного реверсивного счетчика 124) дополнительные реверсивные счетчики импульсов 122.1.122.N и 123.1.123.N, подключенные своими входами предустановки к выходам соответствующих БЗУ (фиг.5).

Действительно, для статистической обработки данных о характере случайных процессов достаточно иметь 128 значений выборок и 32 цикла (серии) однотипных экспериментов. Хотя значения частот f02 и fgi может варьироваться в весьма широких пределах от 2 до 216 для f02 и от 21 до 28 для fgi.

После записи данных во все БЗУ нажимают кнопку 146 "Пуск". В результате с выхода УДЧ 109 на вычитающие входы основных РСИ начнут поступать импульсы с частотой следования f02 f01/KУДЧ, где КУДЧ 21.216.

На выходах "P"_ переполнения РСИ автоматически формируется периодическая последовательность импульсов с частотами fgi foi/Kgi,где Kgi установленные значения коэффициентов пересчета РСИ.

Сигнал переполнения с выхода "P"_ основных РСИ 122.1.122.N поступает на вход перезаписи кода предустановки РСИ. В дополнительных N РСИ 123.1.123.N сигнал переполнения с выхода "P"_ подается на входы пересчета кода адреса блока памяти 188 БЗУ.

Сигнал переполнения с выхода "P"_ N + 1-го дополнительного реверсивного счетчика импульсов 124 поступает на пятый вход элемента "3И-ИЛИ-НЕ" 104. При наличии разрешающего сигнала на шестом входе элемента "3И-ИЛИ-НЕ" 104 триггер 118 переводится в состояние нуля на его прямом выходе. Состояние триггера 118 индицируется с помощью блока световой индикации 181.

Разрешающий сигнал формируется, как уже отмечалось, путем нажатия кнопки 147 "ЦД" и установки триггера 175 в требуемое состояние. Причем циклический режим соответствует установки триггера 175 в состояние единицы на его выходе. Окончание процесса измерения во втором режиме определяется решением оператора или моментом времени поступлением команды с объекта об окончании эксперимента, например, путем включения кнопки 14 "Останов.".

Наличие разрешающего сигнала на выходе триггера 175, а, следовательно, и на втором выходе пульта управления 128 обеспечивает прохождение сигнала переполнения с выхода "P"_ РСИ 124 на вход установки в нуль триггера 118. В результате состояние триггера 118 изменится на противоположное, запрещающее работу УДЧ 109. Процесс регистрации и измерений, состоящий из Nц циклов, завершится. Повторение этого процесса осуществляется повторным нажатием кнопки 146 "Пуск".

В течение Nц циклов работы системы выходные данные каналов 1 и 2 с выходов 8.1-8.N поступают на входы 1-12 соответствующих блоков 3 и 4 оперативной памяти (БОП) (фиг.1).

Для записи получаемых данных в БОП с помощью пульта управления 128 выбирается соответствующий регистр 113, в который заносится код адреса требуемого БОП. Выходы регистра 113 соединены с соответствующими третими входами элементов "И-НЕ" 125.1-125.N. В зависимости от состояния разрядов регистра 113 на выходах элементов "И-НЕ" 125.1-125.N появятся сигналы, разрешающие запись данных с выходов каналов в соответствующий БОП. Эти сигналы формируются путем совпадения четырех различных сигналов: сигналов готовности выдачи информации с цифровых выходов каналов (поступают на входы 24.1-24.N блока 8), выходных сигналов основных РСИ блока 8, синхросигнала с восьмого выхода дешифратора 117 и разрешающих сигналов с выходов разрядов регистра 113 блока 8 автономного управления (фиг.5).

Чтение информации из БОП осуществляется по команде, формируемой в блоке 8 автономного управления. Для этого в разряды регистра 114 адреса БОП известным способом заносится сигнал, соответствующий выбранному номеру БОП.

С выходов разрядов регистра 114 сигнал поступает на первые входы вторых N элементов "И" 126.1-126.N, разрешая или запрещая прохождение через них импульсов с выходов второго элемента "ИЛИ" 107 и второго дешифратора 117. На входы элемента "ИЛИ" 107 поступают импульсы с ЭВМ 12 или с пульта управления 128. В последнем случае они формируются с помощью формирователя 164 путем нажатия кнопки 142 "ЧТ" чтение "ОЗУ". Последняя подключена к входу формирователя 164. Как и остальные эта команда также отображается с помощью блока 182 световой индикации пульта управления 128.

Алгоритм ручного управления системой в общем виде может быть представлен в виде структурной схемы, приведенной на фиг.8 и отражающей совокупность и последовательность команд, выполненных оператором вручную.

Рассмотрим подробно работу одного из БОП в режимах записи и чтения информации (данных).

Отличительной особенностью работы БОП является синхронизация его импульсами кварцованного генератора 102, распределенными во времени и в пространстве с помощью счетчика 103 и дешифратора 117 (фиг.5). Для управления работой БОП используются импульсы третьего, седьмого и восьмого выходов дешифратора 117, диаграмма распределения выходных импульсов которого приведена на фиг.9.

В БОП используются блоки памяти 76.99, представляющие собой оперативные динамические запоминающие устройства, выполненные, например, на ИМС К565РУЗ. Код адреса блоков памяти 76.99 формируется с помощью четырнадцатиразрядного счетчика 43 импульсов.

Потактная (по семь разрядов в одном такте) передача кодов адреса на одноименные входы блоков памяти 76.99 осуществляется через элементы "3И-ИЛИ-НЕ" 69.75 и сопровождается синхроимпульсами, поступающими на вторые и четвертые входы элементов "3И-ИЛИ-НЕ" 69.75. В качестве импульсов синхронизации используются сигналы с седьмого и восьмого выходов дешифратора 117. Эти сигналы поступают соответственно через пятый и шестой выходы блока автономного управления, двадцать девятый и тридцатый входы БОП, на первый вход элемента "ИЛИ-НЕ" 51 и на вторые и четвертые входы семи элементов "3И-ИЛИ-НЕ" 69.75. Первые входы каждого из семи элементов "3И-ИЛИ-НЕ" 69.75 подключены к соответствующим первым семи выходам разрядов счетчика 43 адреса блоков памяти 76. 99. Третьи входы каждого из семи элементов "3И-ИЛИ-НЕ" 69.75 соединены соответственно с вторыми семью выходами счетчика 43 кода адреса блоков памяти 76.99. Кроме того, на шестые входы семи элементов "3И-ИЛИ-НЕ" 69.75 подается код адреса строки блоков памяти 76.99 с разрядов второго (семиразрядного) счетчика 44 импульсов.

На пятые (объединенные между собой) входы элементов "3И-ИЛИ-НЕ" 69.75 с третьего выхода дешифратора 117 через третий выход блока 8 автономного управления, двадцать восьмой вход БОП и второй одновибратор 54 поступают импульсы с частотой fp 100 кГц, задающие время цикла регенерации. Формируемые с помощью элементов "3И-ИЛИ-НЕ" 69.75 семизарядные сигналы кода адреса строки поступают на объединенные между собой одноименные входы адреса блоков памяти 76.99. По второму такту заносится код адреса столбца с тех же выходов элементов "3И-ИЛИ-НЕ" 69.75. Для полной регенерации хранимой в БОП информации необходимо 128 циклов (обращения по всем 128 адресам строк блоков памяти 76.99). При выбранной частоте регенерации fp 100 кГц полное время регенерации блоков памяти 76.99 составит tp 27/fp 27˙1˙10-6 27˙10-3 с.

В режиме записи информации в блоки памяти 76.99 данные поступают в виде 24-х разрядных слоев на 1-24 входы БОП. Первые 12 разрядов этого слова составляют данные с выходов аналого-цифрового преобразователя 24 аналоговых каналов 1 или с выходов коммутатора 30 цифровых сигналов дискретных каналов 2. Эти данные поступают с 8.1-8.N выходов каналов на 1-12 входы БОП. Вторые 12 разрядов составляют: 7 разрядов число выборок при заданной частоте дискретизации, 5 разрядов число соответствующих циклов. Для каждого i-го БОП эти разряды слова формируются в блоке 12 автономного управления и являются выходами дополнительных i-х реверсивных счетчиков импульсов 123.J и N + 1-го реверсивного счетчика импульсов 124, подключенными через 8.J и 9.J выходы блока 8 к 13-19 и 20-24 входам БОП соответственно (см. фиг.4).

Входы 1.24 блока оперативной памяти соединены с входами "Д1" блоков памяти 76.99 соответственно.

Выбор любой из 16384 ячеек блоков памяти 76.99 обеспечивается 14-и разрядным адресным кодом, поступающим в два такта, в сопровождении стробирующих сигналов на входы  и

и  (

( вход выбора адреса строки,

вход выбора адреса строки,  вход выбора адреса столбца).

вход выбора адреса столбца).

На входы  блоков памяти 76.99 поступает сигнал с выхода элемента "ИЛИ-НЕ" 51, первый и второй входы которого через двадцать девятый и тридцать первый входы БОП, пятый и шестой выходы блока 8 автономного управления соединены с седьмым и третьим выходом дешифратора 117 (фиг.5).

блоков памяти 76.99 поступает сигнал с выхода элемента "ИЛИ-НЕ" 51, первый и второй входы которого через двадцать девятый и тридцать первый входы БОП, пятый и шестой выходы блока 8 автономного управления соединены с седьмым и третьим выходом дешифратора 117 (фиг.5).

На каждые восемь входов  блоков памяти 76.99 поступают в режиме записи сигналы выбора адреса столбца с выходов элементов "И" 58, 59 и 60. Вторые входы элементов "И" 58, 59 и 60 объединены и подключены соответственно к выходу элемента "И-НЕ" 50. Последний обеспечивает разрешение управления режимом записи данных в блоке памяти 76.99 по сигналам с выходов второго триггера 68 и пятого элемента "И" 62. Выходы блоков 68 и 62 соединены соответственно с первым и вторым входами элемента "И" 50 (фиг.4). Необходимо отметить, что режим записи информации в блоки памяти 76.99 (фиг.4) устанавливается путем подачи логического нуля на вход установки единицы триггера 68 и перевода последнего в единицу на его прямом выходе. При этом сигналом логического нуля с инверсного выхода триггера 68, поступающего на третий вход элемента "И" 61, запрещается выполнение операции считывания данных с БОП. Это позволяет исключить одновременное выполнение операции "запись" и "чтение" информации в БОП.

блоков памяти 76.99 поступают в режиме записи сигналы выбора адреса столбца с выходов элементов "И" 58, 59 и 60. Вторые входы элементов "И" 58, 59 и 60 объединены и подключены соответственно к выходу элемента "И-НЕ" 50. Последний обеспечивает разрешение управления режимом записи данных в блоке памяти 76.99 по сигналам с выходов второго триггера 68 и пятого элемента "И" 62. Выходы блоков 68 и 62 соединены соответственно с первым и вторым входами элемента "И" 50 (фиг.4). Необходимо отметить, что режим записи информации в блоки памяти 76.99 (фиг.4) устанавливается путем подачи логического нуля на вход установки единицы триггера 68 и перевода последнего в единицу на его прямом выходе. При этом сигналом логического нуля с инверсного выхода триггера 68, поступающего на третий вход элемента "И" 61, запрещается выполнение операции считывания данных с БОП. Это позволяет исключить одновременное выполнение операции "запись" и "чтение" информации в БОП.

Управление записью информации в блоки памяти 76.99 производится сигналами выбора адресов строк, запись/считывание и адресов столбцов, поступающих соответственно на входы  ,

,  и

и  указанных блоков памяти с выходов элементов "ИЛИ-НЕ" 51, "И" 58, 59, 60 и элементов "И" 55, 56 и 57 соответственно (фиг.4).

указанных блоков памяти с выходов элементов "ИЛИ-НЕ" 51, "И" 58, 59, 60 и элементов "И" 55, 56 и 57 соответственно (фиг.4).

В режиме считывания в состояние логической единицы переводится триггер 67. В результате запрещается выполнение операции записи данных в БОП. Это достигается подачей сигнала логического нуля с инверсного выхода триггера 67 и третий вход элемента "И" 62.

Сигналы выбора адреса строк блоков памяти 76.83, 84.91, 92.99 поступают на входы  этих блоков с выходов элементов "И-НЕ" 55, 56 и 57.

этих блоков с выходов элементов "И-НЕ" 55, 56 и 57.

При этом с выходов элементов "3И-ИЛИ-НЕ" 69.75 на адресные входы блоков памяти 69.75 подается код адреса строки. Код адреса столбца заносится в блок памяти 69.75 по второму из двух тактов.

Процесс считывания 24-х разрядного слова происходит побайтно.

Из общих четырех тактов три используется для считывания 24-х разрядного слова и один (четвертый) такт для пересчета адреса блоков памяти 69.75.

Указанные такты формируются путем подачи сигнала с шестого выхода блока 8 автономного управления через тридцать третий вход БОП и элементы "И" 61 и "И-НЕ" 48 на счетный вход счетчика импульсов 45, входы выбора кристалла "ВК" шинных формирователей 100 и 101 и вход элемента "НЕ" 66.

С помощью счетчика импульсов 45 и дешифратора 42 осуществляется формирование тактовых импульсов. С первых трех выходов дешифратора 42 тактовые импульсы поступают на вторые входы элементов "И" 55, 56 и 57 соответственно. На первые входы элементов "И" 55, 56 и 57 поступает выходной сигнал элемента "И-НЕ" 49. Необходимо отметить, что элементы "И" 55, 56 и 57 выполняют функцию "ИЛИ" при поступлении на их входы логических нулей.

Сигналом с четвертого выхода дешифратора 42 осуществляется установка счетчика импульсов 45 в нуль и пересчет, в режиме считывания, адреса блоков памяти 76. 99 путем подачи импульса через первый и второй входы элемента "2И-ИЛИ-НЕ" 47 на счетный вход счетчика импульсов 43.

На выходах элементов "И" 55, 56 и 57 формируются сигналы записи информации в блок памяти 76.83, 84.91 и 92.99 соответственно, которые поступают на входы  последних (фиг.4).

последних (фиг.4).

Управление тремя тактами передачи информации производится сигналами выбора адресов строк, адресов столбцов и сигнала запись-считывания, поступаемых на входы  ,

,  и

и  блоков памяти 76.83, 84.91, 92.99 с выходов элементов "ИЛИ-НЕ" 51, "И" 55, 56 и 57 и элементов "И" 58, 59 и 60 соответственно (фиг. 4). По первому такту на входы

блоков памяти 76.83, 84.91, 92.99 с выходов элементов "ИЛИ-НЕ" 51, "И" 55, 56 и 57 и элементов "И" 58, 59 и 60 соответственно (фиг. 4). По первому такту на входы  ,

,  и

и  блоков памяти 76.83 поступают в той же последовательности сигналы логического нуля. Наличие сигналов, соответствующих логической единицы на входах

блоков памяти 76.83 поступают в той же последовательности сигналы логического нуля. Наличие сигналов, соответствующих логической единицы на входах  блоков памяти 84.91 и 92. 99, обеспечивает установку их в третье состояние, соответствующее отключение выходных этих блоков памяти от выходной шины.

блоков памяти 84.91 и 92. 99, обеспечивает установку их в третье состояние, соответствующее отключение выходных этих блоков памяти от выходной шины.

По второму и третьему тактам считывание информации с выходов соответственно блоков памяти 84.91, 92.99 осуществляется аналогичным образом. При этом установленный в счетчике 43 импульсов код адреса блоков памяти 76.99 не пересчитывается. Пересчет кода адреса осуществляется сигналом с четвертого выхода дешифратора 42 (задатчика тактов чтения). Побайтная выдача информации с выходов шинных формирователей 100 и 101 осуществляется путем подачи на их входы "ВК" выходного сигнала элемента "И-НЕ" 48 и сопровождается стоб-импульсом с выхода элемента "НЕ" 66. Эта информация через выходы 1-8 шинных формирователей 100 и 101 поступает на входы 4-11 интерфейса 9.

С выходов интерфейса 9 информация поступает на накопитель 11 на магнитой ленте, подключенной вместо ЭВМ 12 в режиме автономного (ручного) управления системой.

Сигналы данных с 1-8 выходов блоков 3 и 4 оперативной памяти поступают на 4-11 входы интерфейса 9. На его первый вход поступает строб-импульс с выхода первого элемента "ИЛИ" 5 (фиг.1). Входы этого элемента подключены к девятым выходам всех БОП, сигналы которых объединяются по "ИЛИ" и обеспечивают синхронизацию ввода информации через приемники 197, регистр 194, приемо-передатчики 189 и общую шину 10 в накопитель 11 на магнитной ленте, в случае работы системы без ЭВМ 12, т.е. в автономном режиме регистрации данных.

Рассмотрим режим автоматического управления (АУ) процессами регистрации и измерения с использованием ЭВМ 12.

Режим "АУ" устанавливается вручную путем нажатия кнопки 159 на пульте управления 128 или соответствующей кнопки на пульте управления ЭВМ 12. В последнем случае управляющий сигнал через общую шину 10, приемо-передатчики 189 интерфейса 9, через один из разрядов регистра 192 и передатчик 196 (фиг. 8) поступает на двадцать второй выход интерфейса 9, а следовательно, и на второй вход пульта управления 128, подключенного к второму входу элемента "ИЛИ" 178. Указанный сигнал переводит триггер 177 в состояние логического нуля на его прямом выходе. На первый вход элементов "И" блока элементов "И-ИЛИ" 108 поступит запрещающий сигнал, а на второй вход элементов "И" разрешающий сигнал соответственно с четвертого и пятого выходов пульта управления 128. В результате управление системой будет производиться только по команде с ЭВМ 12 в заданной последовательности.

Как видно из фиг. 8, на первые входы элементов "ИЛИ" блока элементов "И-ИЛИ" 108 поступают данные с 1-8 выходов интерфейса 9, адреса регистров 110. 115 с 9-14 выходов интерфейса 9 и команды "чтение БЗУ", "запись БЗУ", "чтение ОЗУ", "запись ОЗУ", "СТОП", "чтение однократ/многократ." и строб-импульс сопровождения данных с 15-22 выходов интерфейса 9 соответственно.

В режиме автоматического управления процессами регистрации работа системы осуществляется по тому же алгоритму, что и при ручном управлении (фиг. 10, 11). Однако измерение и обработка данных в режиме автоматического управления существенно отличаются от автономного режима.

Основной особенностью автоматического режима является возможность статистической обработки результатов исследований и выбора по ним оптимальных режимов измерения и регистрации физических процессов и величин. Это позволяет эффективно использовать аппаратно-программные средства системы и повысить информативность, достоверность и надежность результатов исследований.

Для этого проводится регистрация переходного процесса U(t) (фиг.12), измерение и обработка, по меньшей мере, трех его параметров: а) скорости протекания исследуемого процесса

v

du(t)/dt в заданных интервалах времени Δ ti Ti, где i 0,1,2,N; б) частоты fог основной гармоники или спектрального состава сигнала U(t); в) времени затухания Тз переходных процессов; г) характеристических моментов времени to, t1, t2, ti.

du(t)/dt в заданных интервалах времени Δ ti Ti, где i 0,1,2,N; б) частоты fог основной гармоники или спектрального состава сигнала U(t); в) времени затухания Тз переходных процессов; г) характеристических моментов времени to, t1, t2, ti.

Затем, в зависимости от частоты основной гармоники, устанавливается средняя частота дискретизации исследуемого процесса, требуемое число выборок и количество циклов измерений.

Частота дискретизации уточняется в зависимости от скорости протекания исследуемых процессов. Число выборок устанавливается с учетом объема памяти БОП. Время проведения эксперимента определяется как величина

Тэ KTц, где Тц время одного цикла, составляющее 3-10 интервалов времени между характеристиками момента времени, К число циклов, при которых амплитуда процесса уменьшается до наперед заданной величины Аm.min.

После уточнения значений частоты дискретизации, числа выборок и количества циклов измерений вновь регистрируют переходной процесс и обрабатывают его параметры. Такая итерационная процедура повторяется несколько раз до получения однотипных результатов обработки, а следовательно, и номинальных значений частот дискретизации, числа выборок и числа циклов, необходимых для достоверного изучения объекта исследования. Необходимо отметить, что в аналоговые каналы измерения физических величин введена структурная избыточность и новые связи между функциональными блоками, обеспечивающие: коррекцию аддитивной и мультипликативной составляющих погрешности измерения каждого из упомянутых каналов и их тестирование. Кроме того, обеспечена реализация двух режимов дискретизации и измерения амплитуд выборок из выходных сигналов датчиков 25.1.25.m: а) одновременная (с частотой f03 f02/m) запись мгновенных значений амплитуд выборок из выходных сигналов датчиков в АЗУ 28.1.28.m, с последующим поочередным считыванием и преобразованием в код записанной информации и б) разновременная (с частотой f02 100 кГц) запись в АЗУ мгновенных значений амплитуд выборок из выходных сигналов датчиков и синхронное преобразование их в код с помощью АЦП 24.

Тестирование аналоговых каналов осуществляется следующим образом. При положении коммутатора 22 аналоговых сигналов, соответствующем поступлению первого (после сброса в нуль) импульса на счетный вход счетчика 18, осуществляется запись в БОП выходного кода Nxo АЦП 24 каждого из аналоговых каналов. Этот код пропорционален амплитуде выборки из выходного сигнала источника 15 опорного напряжения.

Значение No напряжения Vo источника 15 известно априори с высокой точностью. Само напряжение Vo выбирается весьма малым по значению, т.е. Vo ΔV. Результат измерения Nxo этого напряжения записывается в память ЭВМ 12 как величина Nxo KoiSVo, где Koi коэффициент передачи i-го канала, S крутизна преобразования АЦП. Значения Nxo и No сравнивают между собой. По результату сравнения вносят существующие поправки в результаты измерений.

Для исключения систематической погрешности канала обработка значений амплитуд выборок осуществляется с помощью второго процессора 13 по алгоритму

Nxi= No , (1) где N1i, N2i и N3i результаты преобразования в код амплитуд выборок, записанных в АЗУ, из выходных сигналов источников 25 опорного напряжения, датчика 25.J и сумматора 26.J (где 1 ≅ J ≅ m) соответственно.

, (1) где N1i, N2i и N3i результаты преобразования в код амплитуд выборок, записанных в АЗУ, из выходных сигналов источников 25 опорного напряжения, датчика 25.J и сумматора 26.J (где 1 ≅ J ≅ m) соответственно.

Обработка данных по алгоритму (1) осуществляется следующим образом. Задним фронтом импульса, поступающего с выхода четырнадцатого разряда счетчика 43 адреса памяти в режиме чтения (т.е. при перезаписи информации с выходов блоков 3 и 4 оперативной памяти (фиг.4) в оперативное запоминающее устройство ЭВМ 12 или накопитель 13 на магнитной ленте) через первый элемент "2И-ИЛИ-НЕ" 46 триггер 67 чтения, устанавливается в нуль.

С прямого выхода триггера 67 сигнал поступает через 11 выход блоков 3 и 4 оперативной памяти и элементы 6 (фиг.1) на входы 2N интерфейса 9 (или на входы 1N регистра 195 состояния), фиг.8. Регистр 195 формирует код, характеризующий окончание работы соответствующего канала. После появления этого кода осуществляется обработка данных выбранного канала с помощью ЭВМ 12 по алгоритму, структурная схема которого приведена на фиг.10, 11.

Покажем, что алгоритм (1) обеспечивает исключение аддитивной и мультипликативной составляющих погрешности при линейной характеристике преобразования каналов, т.е.

Ni Ki Si Vi (1 + γi + Δ Ni), (2) где Δ Ni приведенная к выходу i-го канала аддитивная составляющая погрешности преобразования;

KiSiUi γi приведенная к выходу мультипликативная составляющая погрешности;

Ki коэффициент передачи i-го канала от датчика к АЦП;

Si крутизна преобразования i-го АЦП;

Vxi выходной сигнал i-го датчика (амплитуда i-й выборки).

При характеристике преобразования (2) мы получим

N1i Ki Si Voi (1 + γi + Δ Ni), (3)

N2i Ki Si V1i (1 + γi + Δ Ni), (4)

N3i Ki Si V2i (1 + γi + Δ Ni), (5) где Voi амплитуда выборки из выходного напряжения источника 15;

V1i Vxi амплитуда i-й выборки,

V2i Vxi + Voi амплитуда выборки из выходного сигнала i-го сумматора.

Подставим результаты измерений (3)-(5) амплитуд выборок в выражение (1). Тогда  (6)

(6)

Из выражения (6) видно, что реализация алгоритма (1) обработки данных обеспечивает исключение систематической погрешности каждого i-го канала. Основные требования по стабильности и точности предъявляются к идентичности характеристик АЗУ 27-29.m. Неидентичность характеристик АЗУ приведет к неравенству их коэффициентов передачи и возникновению небольшой систематической погрешности, зависящей от степени идентичности характеристик. Эффект в этом случае достигается только за счет исключения погрешностей АЦП 34.

Особенностью работы дискретных каналов (фиг.3) является, как уже отмечалось выше, возможность ввода измерительной информации от внешних дополнительных стандартных и нестандартных цифровых измерительных приборов путем подключения их выходов к входным регистрам 35.1-35.Rp.

Путем подключения образцовых измерительных приборов к входам дискретных каналов обеспечивается возможность использования их для коррекции коэффициента передачи аналоговых измерительных каналов. С помощью счетчиков 31.1-1.Rs и многоразрядного счетчика 32 возможен подсчет различного числа неоднородных событий, имевших место в исследуемом объекте, а также преобразовании последовательности этих событий в параллельный код. Дискретные каналы выполняют также с помощью компараторов 40.1-40.Rk, операции сравнения уравнений выходных сигналов датчиков, преобразователей, источников тока или напряжения, расположенных на исследуемом объекте и несущих информацию о состоянии отдельных элементов или узлов объекта в реальном масштабе времени.

Наличие в системе ЭВМ 12 и интерфейсов 9 позволяет дополнительно решать задачи усреднения и сглаживания результатов исследований, цифровой фильтрации зарегистрированных сигналов по известным алгоритмам обработки данных.

В отличие от прототипа многоканальная система для регистрации физических величин отличается широкими функциональными возможностями и повышенной точностью измерений и регистрации.

Расширение функциональных возможностей достигается за счет введения в систему дискретных каналов. В результате стало возможным дополнительное включение внешних стандартных или нестандартных цифровых измерительных приборов, в том числе и образцовых. Введение дискретных каналов обеспечивает также подсчет различного числа неоднородных событий, имеющих место в исследуемом объекте, преобразование последовательности событий в параллельный код, а также выполнение операций сравнения уровней выходных сигналов датчиков, преобразователей, источников тока или напряжения, расположенных на исследуемом объекте.

Введение в систему блоков оперативной памяти, соединенных определенным образом с дискретными и аналоговыми каналами, с интерфейсом и блоком автономного управления системой, обеспечивает расширение функциональных возможностей за счет быстродействующего запоминания заданных массивов выборок выходных сигналов датчиков, характеризующих физические процессы в изучаемом объекте, с учетом различной скорости протекания исследуемых процессов, а также за счет разделения во времени процессов съема и обработки значений амплитуд выборок, программируемого распределения всего объема информации, поступающей в блоки оперативной памяти и в ЭВМ.

Введение второго процессора 13 обеспечивает разделение функций управления работой функциональных блоков системы и обработки полученной информации. Введение группы элементов "НЕ" и их связей с интерфейсом и с блоками оперативной памяти обеспечивает синхронизацию процесса передачи информации в ЭВМ. Это повышает достоверность получаемой информации и готовность ЭВМ к ее восприятию и обработке.

Введение блока автономного управления расширяет функциональные возможности системы в части реализации автономного режима работы без ЭВМ, но с накопителем на магнитной ленте, и режим с автоматическим управлением ходом эксперимента. Введение блока автономного управления позволяет осуществлять отработку программы оптимального управления процессом дискретизации, в частности выбирать частоту дискретизации, задавать необходимый объем выборок, формировать интервалы времени между выборками по циклам и по каналам; контролировать команды, поданные с пульта управления; выполнять операцию останова системы по команде с объекта, с пульта управления или от ЭВМ.

Введение существенных отличительных признаков в измерительные каналы обеспечивает реализацию тестового алгоритма коррекции погрешностей каналов, т. е. обеспечивает повышение точности регистрации и измерения физических процессов и величин. Кроме того, обеспечивают регистрацию быстропротекающих с различной скоростью процессов и введение поправки в результат измерений в случае отклонения коэффициентов передачи каналов от заданных номинальных значений.

Отличительные признаки, введенные в каждое буферное запоминающее устройство, позволяют осуществлять ручное и автоматическое управление режимами чтения, записи и пересчета адреса. Отличительные признаки, введенные в интерфейс, обеспечивают сопряжение через общую шину, блоков оперативной памяти и блока автономного управления с ЭВМ, а также режим автоматического управления системой с помощью ЭВМ.

Таким образом, предложенная совокупность функциональных блоков и их связей обеспечивает расширение функциональных возможностей и повышение точности регистрации и измерения физических процессов и величин с помощью предложенной многоканальной системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛОЖЕНИЕМ ОБЪЕКТА | 1991 |

|

RU2042169C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2022364C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| СПОСОБ ЦИФРОВОГО ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2025044C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

Изобретение относится к вычислительной технике, его использование для измерения, регистрации и анализа текущих значений физических величин и формы физических процессов позволяет повысить точность за счет введения структурной и информационной избыточности и тестовых методов коррекции погрешностей, а также расширить функциональные возможности системы. Система содержит аналоговые каналы 1 измерения, группу 3 блоков оперативной памяти, элемент ИЛИ 5, блок 8 автономного управления и интерфейс 9. Благодаря введению цифровых каналов 2 измерения, группы 4 блоков оперативной памяти, групп 6, 7 элементов НЕ, накопителя 11 на магнитной ленте, вычислительного блока 12 и кнопки 14 останова в системе достигается вышеуказанный технический результат. 7 з. п. ф-лы, 12 ил.

1 8, 9 16 и 17 24 блоков памяти объединены между собой, соединены с первыми входами четвертого, пятого и шестого элементов И и подключены к выходам первого, второго и третьего элементов И соответственно, входы

1 8, 9 16 и 17 24 блоков памяти объединены между собой, соединены с первыми входами четвертого, пятого и шестого элементов И и подключены к выходам первого, второго и третьего элементов И соответственно, входы  всех блоков памяти объединены и соединены с выходом первого элемента ИЛИ НЕ, входы

всех блоков памяти объединены и соединены с выходом первого элемента ИЛИ НЕ, входы  каждой восьмерки блоков памяти объединены между собой и подключены соответственно к выходам четвертого, пятого и шестого элементов И, вторые входы которых объединены между собой, соединены с четвертым входом второго элемента 2И ИЛИ НЕ и подключены к выходу третьего элемента И НЕ, одноименные выходы 1 8, 9 16 и 17 24 блоков памяти объединены между собой и соединены по четыре с входами первого и второго шинных формирователей, управляющие входы УВ которых соединены между собой и подключены к клемме питания, синхронизирующие входы ВК соединены с входами четвертого элемента НЕ, со счетным входом третьего счетчика импульсов и подключены к выходу первого элемента И НЕ, выходы первого и второго шинных формирователей соединены с выходами 1 4, 5 8 блоков оперативной памяти, девятый выход которого подключен к выходу четвертого элемента НЕ, двадцать пятый вход блока оперативной памяти соединен с входом второго элемента НЕ и с входом установки нуля первого счетчика импульсов, двадцать шестой вход соединен с третьим входом первого элемента 2И ИЛИ НЕ, двадцать седьмой вход через первый одновибратор подключен к первому выходу второго элемента И

каждой восьмерки блоков памяти объединены между собой и подключены соответственно к выходам четвертого, пятого и шестого элементов И, вторые входы которых объединены между собой, соединены с четвертым входом второго элемента 2И ИЛИ НЕ и подключены к выходу третьего элемента И НЕ, одноименные выходы 1 8, 9 16 и 17 24 блоков памяти объединены между собой и соединены по четыре с входами первого и второго шинных формирователей, управляющие входы УВ которых соединены между собой и подключены к клемме питания, синхронизирующие входы ВК соединены с входами четвертого элемента НЕ, со счетным входом третьего счетчика импульсов и подключены к выходу первого элемента И НЕ, выходы первого и второго шинных формирователей соединены с выходами 1 4, 5 8 блоков оперативной памяти, девятый выход которого подключен к выходу четвертого элемента НЕ, двадцать пятый вход блока оперативной памяти соединен с входом второго элемента НЕ и с входом установки нуля первого счетчика импульсов, двадцать шестой вход соединен с третьим входом первого элемента 2И ИЛИ НЕ, двадцать седьмой вход через первый одновибратор подключен к первому выходу второго элемента И

НЕ, двадцать восьмой вход соединен с входом второго одновибратора и через третий элемент НЕ со счетным входом второго счетчика импульсов, тридцать первый вход блока оперативной памяти подключен к второму входу первого элемента ИЛИ НЕ, тридцать второй и тридцать четвертый входы блока оперативной памяти соединены соответственно с входами установки единицы первого и второго триггеров, тридцать третий и тридцать пятый входы подключены соответственно к первым входам седьмого и восьмого элементов И, выход восьмого элемента И соединен с вторым входом третьего элемента И НЕ, второй вход восьмого элемента И соединен с десятым выходом блока оперативной памяти, с вторым входом второго элемента И НЕ, с первым входом третьего элемента И - НЕ и подключен к прямому выходу второго триггера, вход установки нуля которого подключен к выходу второго элемента ИЛИ НЕ, чей первый вход соединен с выходом второго элемента НЕ, второй вход второго элемента ИЛИ НЕ соединен с первым и вторым входами первого элемента 2И ИЛИ НЕ и подключен к старшему разряду первого счетчика импульсов, инверсный выход второго триггера соединен с третьим входом седьмого элемента И, выход которого подключен к третьему входу второго элемента 2И ИЛИ НЕ и второму входу первого элемента И НЕ, второй вход седьмого элемента И соединен с одиннадцатым выходом блока оперативной памяти, с первым входом второго элемента И НЕ и подключен к прямому выходу первого триггера, инверсный выход которого соединен с третьим входом восьмого элемента И, вход установки нуля первого триггера подключен к выходу первого элемента 2И ИЛИ НЕ, четвертый вход которого соединен через первый элемент НЕ со счетным входом первого счетчика импульсов и подключен к выходу второго элемента 2И ИЛИ НЕ, первый и второй входы которого соединены с входом установки нуля третьего счетчика импульсов и подключены к четвертому выходу дешифратора, входы которого соединены с выходами третьего счетчика импульсов, первый, второй и третий выходы дешифратора подключены к вторым входам первого, второго и третьего элементов И соответственно, первые входы которых объединены между собой и подключены к выходу второго элемента И НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-06-09—Публикация

1991-04-03—Подача