1

Изобретение относится к ке и вычислительной технике.и может быть использовано в измерительных системах, измерительно-вычислительных комплексах и системах контроля и управления повьшенной надежности.

Цель изобретения - повышение надежности и помехоустойчивости и обеспечение самоконтроля.

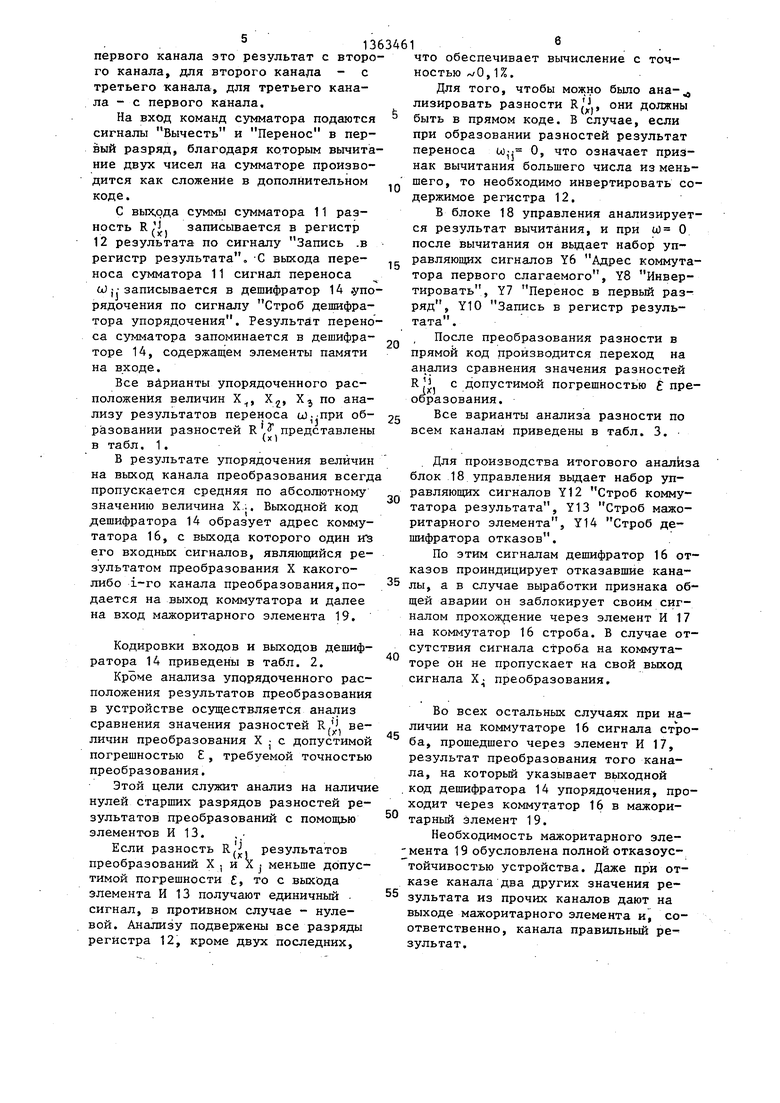

На фиг. 1 приведена функциональная схема вероятностного преобразователя, аналог - код; на фиг, 2 - функциональная схема блока управления.

1363461 - 2 автомати- ратора отказов Y15 - тановка ГПСЧ.

Ш

15

Устройство работает разом.

По сигналу Пуск из равления вьщается сигна установки Y15. Начальн ГПСЧ для каждого канала ния в целях повътенкя п вости и достоверности р производится посредство личных ненулевых кодов, 101010, 111000, 010101 венно для первого, втор го каналов преобразован му значению сигнала Y2 татора младших разрядо 18, нулевому значению с рес коммутатора старших признак второго цикла Признак первого цикла блоком 18 в первом цикл вания, коммутатор 2 пер ды старших разрядов ЦАП выхода генератора 1 псе чисел, второй коммутато ет на входы младших раз логические нули, а выхо ра 5 через элемент И 6 к входу счетчика 8. При очередного сигнала Y1 из блока 18 на вход ген его выходах формируется дослучайное число, кото зуется в случайное напр ходе ЦАП 4.

Вероятностный преобразователь аналог - код (фиг. 1) содержит три идентичных канала преобразования, каждый из которых выполнен на генераторе 1 псевдослучайных чисел (ГПСЧ) первом 2 и втором 3 коммутаторах,циф- роаналоговом преобразователе (ЦАП) 4, компараторе 5, первом 6 и втором 7 элементах И, первом 8 и втором 9 счетчиках, третьем коммутаторе 10, сумматоре 11, регистре 12, третьем элементе И 13, первом 14 и втором 15 дешифраторах, четвертом коммутаторе 16, четвертом элементе И 17, блоке 18 управления, мажоритарном элементе 19 и трех элементах 20 индикации отказов каналов преобразования.

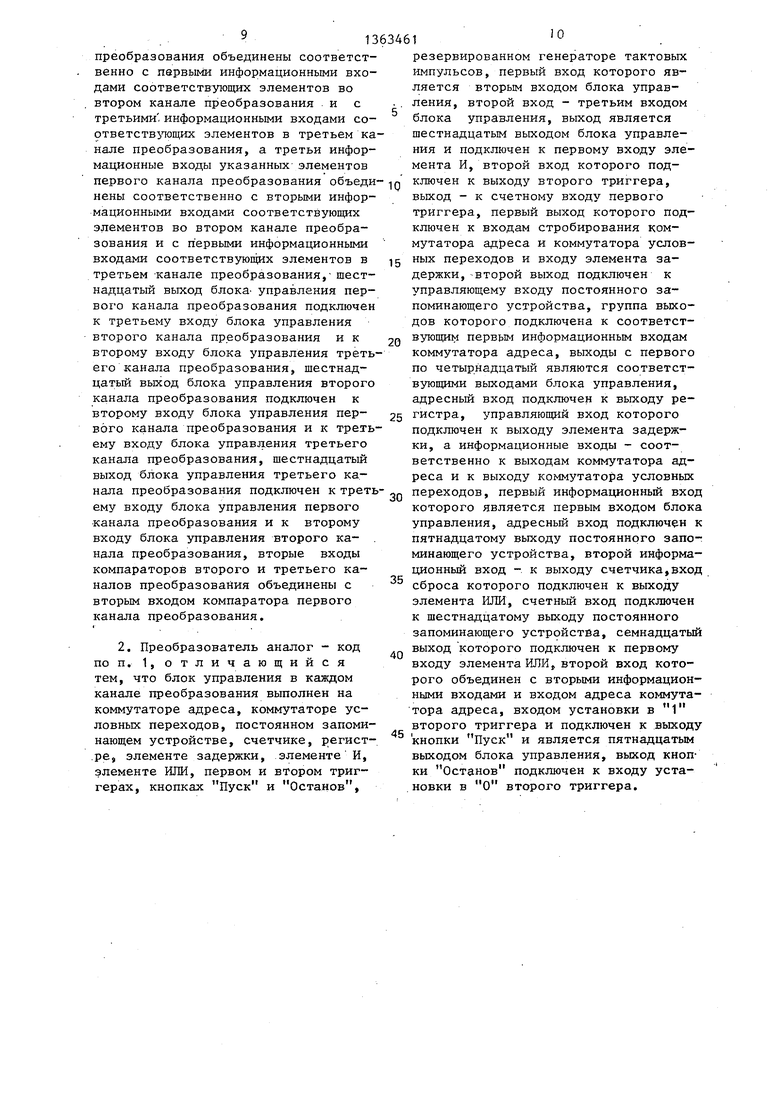

Блок 18 управления (фиг. 2) выполнен на коммутаторе 21 условных переходов, постоянном запоминающем устройстве (ПЗУ) 22, счетчике 23, регистре 24, элементе 25 задержки,элементе ИЛИ 26, резервированном гене- раторе 27 тактовых импульсов, элементе И 28, первом 29 и втором 30 триггерах, коммутаторе 31 адреса, кнопке 32 Пуск и кнопке 33 Останов.

Функциональное назначение сигналов управления на соответствующих выходах блока 18 управления: Yt - сдвиг ГПСЧ; Y2 - адрес коммутатора младших разрядовi Y3 - адрес коммутатора старших разрядов и признак второго циклаj Y4 - признак первого цикла Y5,- сброс счетчиков; Y6 - адрес коммутатора первого слагаемого; Y7 - +1Р -; Y8 - инвертировать; Y9 - вычесть; Y10 - запись в регистр результата; Y11 - строб дешифратора упорядочения; Y,12 - строб коммутатора результата; Y13 - строб мажоритарного элемента; Y14 - строб дешифначальная ус

5

5

0

5

Устройство работает следующим образом.

По сигналу Пуск из блока 18 управления вьщается сигнал начальной установки Y15. Начальная установка ГПСЧ для каждого канала преобразования в целях повътенкя помехоустойчивости и достоверности результатов производится посредством записи различных ненулевых кодов, например, 101010, 111000, 010101 - соответственно для первого, второго и третьего каналов преобразования. По нулевому значению сигнала Y2 Адрес коммутатора младших разрядов из блока 18, нулевому значению сигнала Y3 Адрес коммутатора старших разрядов и признак второго цикла и сигналу Y4 Признак первого цикла, выдаваемым блоком 18 в первом цикле преобразования, коммутатор 2 передает на входы старших разрядов ЦАП 4 коды с выхода генератора 1 псевдослучайных чисел, второй коммутатор 3 передает на входы младших разрядов ЦАП 4 логические нули, а выход компаратора 5 через элемент И 6 подключается к входу счетчика 8. При поступлении очередного сигнала Y1 Сдвиг ГПСЧ из блока 18 на вход генератора 1 на его выходах формируется новое псевдослучайное число, которое преобразуется в случайное напряжение на выходе ЦАП 4.

Блок 18 управления, который формирует последовательности управляю- щих сигналов, представляет собой

микропрограммное устройство управления с микрокомандами, зашитыми в

ПЗУ 22, Сигнал начального пуска выдается с вькода кнопки 32, и по нему

устанавливается в единичное состояние, триггер 30, который позволяет пропустить синхроимпульсы с генератора 27 через элемент И 28. Частота синхроимпульсов делится на триггере

выходов обеспечивается чтение ПЗУ 22 и запись адреса следующей микрокоманды из формата микрокоманды через коммутатор.31 в регистр 24 адреса. Условные переходы

от сигнала переноса сумматора 11 и от выхода счетчика 23 формируют младий разряд адреса через коммутатор 21 ри записи в регистр 24. Сброс счетика 23 после его отработки и при

начальной установке производится через элемент ИЛИ 26. Элемент 25 задержки обеспечивает задержку записи в регистр 24 на время прохождения кода через коммутаторы 31 и 21.

При сравнении напряжения на выходе 1Щ1 4 с напряжением входного сигнала на компараторе 5 на его выходе формируется единичный сигнал, если напряжение с ЦАП меньше, чем напряжение на входе канала. Единичный сигнал при своем появлении прибавляется к содержимому счетчика 8. Генератор 1 псевдослучайных чисел формирует последовательность псевдослучайных чисел периода N 2-1, в которо отсутствует единственное число-нуль Поэтому по истечении первого цикла преобразования из N тактов в счетчике 8 образуется 1-разрядный код, определяющий старшие К/2 разрядов выходного напряжения ().

Во втором цикле преобразования, переход к которому осуществляется по появлении сигнала переноса на счетчике 23, который обеспечивает запись единицы в младший разряд адреса через коммутатор 21 в регистр 24, формируется с выхода ПЗУ 22 блока 18 набор управляющих сигналов Y3 Адрес коммутатора старших разрядов и признак второго цикла, Y2 Адрес коммутатора младших разрядов, Y1 Сдвиг ГПСЧ.

В этом цикле сформированный в счетчике 8 код через коммутатор 2 поступает на входы старших разрядов ЦАП 4, на его младшие разряды через коммутатор 3 поступают коды с выходов генератора 1 псевдослучайных чисел, а выход компаратора 5 через элемент И 7 подключается к входу счетчика 9. На выходе ЦАП формируется случайное напряжение, представляющее сумму постоянного напряжения,пропорционального коду в счетчике 8, и случайного напряжения на выходе генератора 1 псевдослучайных чисел. Эт напряжение сравнивается с входным напряжением, и результат сравнения (единица, если напряжение на выходе ЦАП меньше входного напряжения, и нуль в противном случае) заносится в счетчик 9, По окончании второго цикла преобразования из N тактов в счетчике 9 образуется 1-разрядный код, соответствующий младшим К/2 разрядам входного напряжения (X(t)).

0

5

0

5

0

5

0

5

0

5

Аналогично работают второй и третий каналы преобразования, Отличием в их работе является то, что во втором и третьем каналах используются генераторы псевдослучайных чисел, формирующие сдвинутые по фазе последовательности псевдослучайных чисел, что достигается установкой различных начальных состояний ГПСЧ, в результате чего ни одно из псевдослучайных чисел X j ,i 1,2,3, получаемых на выходах этих генераторов в некотором такте К, не совпадает. Этим обеспечивается неидентичность последовательностей бинарных символов, поступающих на входы счетчиков 8 и 9 в каждом из параллельных каналов преобразования, и следовательно, малая вероятность одинакового искажения результата преобразования в результате добавления к преобразуемому напряжению импульса помехи.

После окончания второго цикла преобразования и сброса счетчика 23 Д (подготовка к преобразованиям последующих чисел) организуется сравнение результатов преобразований, находящихся в счетчиках 8 и 9 каждого канала преобразования.

Сравнение величин X,, Х,, Х результатов преобразования производится попарным вычитанием содержимых счетчиков 8 и 9 смежных каналов. В результате образзтотся разности величин КЦ X ;-Х., (i,j е 1,,2,3). Итогом анализа разностей R 3 является упорядочение взаиморасположения величин X;. Оно производится на основе классификации набора сигналов переноса сумматоров uj, при производстве попарных вычитаний величин X ,-Xj, X/j-X, Xj-X.

Для этого блоком 18 управления после завершения второго цикла преобразования вырабатывается набор управляющих сигналов Y6 Адрес коммутатора первого слагаемого (в инверсном коде), Y9 Вычесть, Y10 Запись в регистр результата, Y7 Перенос в :первый разряд (+Р;), Y11 Строб дешифратора упорядочения. , По этим сигналам на вход первого слагаемого сумматора 11 подается результат преобразования своего канала с выхода счетчиков 8 и 9 через первый вход коммутатора 10, на вход второго слагаемого подается результат преобразования смежного канала. Для

136

первого канала это результат с второго канала, для второго канала - с третьего канала, для третьего канала - с первого канала.

На вход команд сумматора подаются сигналы Вычесть и Перенос в первый разряд, благодаря которым вычитание двух чисел на сумматоре производится как сложение в дополнительном коде.

С вых,ода суммы сумматора 11 разность R , J записывается в регистр 12 результата по сигналу Запись .в регистр результата, -С выхода переноса сумматора 11 сигнал переноса со с записывается в дешифратор 1А .упорядочения по сигналу Строб дешифратора упорядочения. Результат переноса сумматора запоминается в дешифраторе 14, содержащем элементы памяти на входе.

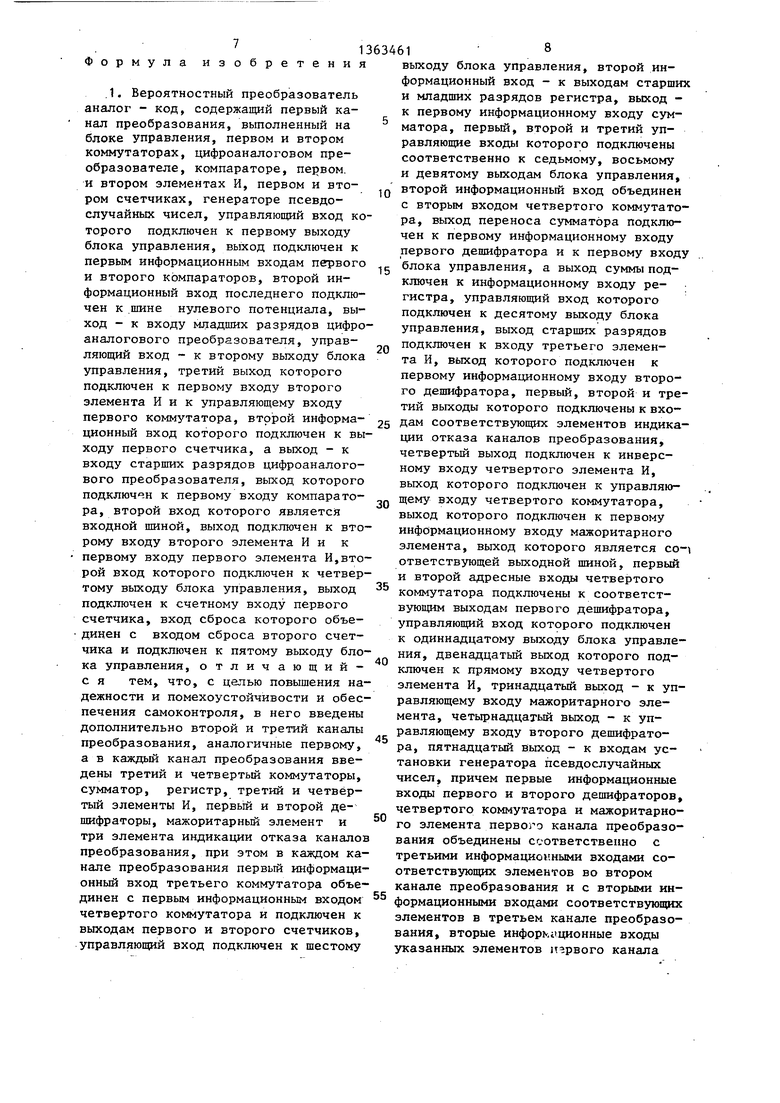

Все варианты упорядоченного расположения величин Х, Х, Xj по анализу результатов переноса о)-при об- разовании разностей R , представлены в табл. 1.

В результате упорядочения величин на выход канала преобразования всегд пропускается средняя по абсолютному значению величина X... Выходной код дешифратора 14 образует адрес коммутатора 16, с выхода которого один из его входных сигналов, являющийся результатом преобразования X какого- либо i-ro канала преобразования,подается на выход коммутатора и далее на вход мажоритарного элемента 19.

Кодировки входов и выходов дешифратора 1А приведены в табл. 2.

Кроме анализа упорядоченного расположения результатов преобразования в устройстве осуществляется анализ сравнения значения разностей Pv. величин преобразования X j с допустимой погрешностью , требуемой точностью преобразования.

Этой цели служит анализ на наличи нулей старших разрядов разностей результатов преобразований с помощью элементов И 13.

Если разность R, - . результатов преобразований X . и X j меньше допустимой погрешности , то с выхйда элемента И 13 получают единичный . сигнал, в противном случае - нулевой. Анализу подвержены все разряды регистра 12, кроме двух последних.

1

6

ЧТО обеспечивает вычисление с точностью 0,1%.

Для того, чтобы можно было ана-,

лизировать разности R/A они должны быть в прямом коде. В случае, если при образовании разностей результат переноса to,-; О, что означает признак вычитания большего числа из меньшего, то необходимо инвертировать содержимое регистра 12.

В блоке 18 управления анализируется результат вычитания, и при а) О после вычитания он вьщает набор управляющих сигналов Y6 Адрес коммутатора первого слагаемого, Y8 Инвертировать, Y7 Перенос в первый раз- Y10 Запись в регистр резульряд, тата

После преобразования разности в прямой код производится переход на сравнения значения разностей R 1 с допустимой погрешностью t преобразования.

Все варианты анализа разности по всем каналам приведены в табл. 3.

Для производства итогового анализа блок 18 управления вьщает набор управляющих сигналов Y12 Строб коммутатора результата, Y13 Строб мажоритарного элемента, Y14 Строб дешифратора отказов.

По этим сигналам дешифратор 16 отказов проиндицирует отказавшие кана- лы, а в случае выработки признака общей аварии он заблокирует своим сигналом прохождение через элемент И 17 на коммутатор 16 строба. В случае отсутствия сигнала строба на коммутаторе он не пропускает на свой выход сигнала Х преобразования.

Во всех остальных случаях при наличии на коммутаторе 16 сигнала строба, прошедшего через элемент И 17, результат преобразования того канала, на который указывает выходной

код дешифратора 14 упорядочения, проходит через коммутатор 16 в мажоритарный элемент 19.

Необходимость мажоритарного элемента 19 обусловлена полной отказоустойчивостью устройства. Даже при отказе канала два других значения результата из прочих каналов дают на выходе мажоритарного элемента и, соответственно, канала правильный результат.

Формула изобретения

.1, Вероятностный преобразователь аналог - код, содержащий первый канал преобразования, выполненный на блоке управления, первом и втором коммутаторах, цифроаналоговом преобразователе, компараторе, первом. и втором элементах И, первом и втором счетчиках, генераторе псевдослучайных чисел, управляющий вход которого подключен к первому выходу блока управления, выход подключен к первым информационным входам первого и второго компараторов, второй информационный вход последнего подключен к щине нулевого потенциала, выход - к входу младших разрядов цифро- аналогового преобразователя, управляющий вход - к второму выходу блока управления, третий выход которого подключен к первому входу второго элемента И и к управляющему входу первого коммутатора, второй информа- ционный вход которого подключен к выходу первого счетчика, а выход - к входу старших разрядов цифроаналого- вого преобразователя, выход которого подключ н к первому входу компаратора, второй вход которого является входной шиной, выход подключен к второму входу второго элемента И и к первому входу первого элемента И,второй вход которого подключен к четвертому выходу блока управления, выход подключен к счетному входу первого счетчика, вход сброса которого объединен с входом сброса второго счетчика и подключен к пятому выходу блока управления, отличающий- с я тем, что, с целью повышения надежности и помехоустойчивости и обеспечения самоконтроля, в него введены дополнительно второй и третий каналы преобразования, аналогичные первому, а в каждый канал преобразования введены третий и четвертый коммутаторы, сумматор, регистр, третий и четвёртый элементы И, первый и второй дешифраторы, мажоритарный элемент и три элемента индикации отказа каналов преобразования, при этом в каждом канале преобразования первый информационный вход третьего коммутатора объединен с первым информационным входом четвертого коммутатора и подключен к выходам первого и второго счетчиков, управляющий вход подключен к шестому

0

5

0

5 5

0

0

5

0

выходу блока управления, второй информационный вход - к выходам старших и младших разрядов регистра, выход - к первому информационному входу сумматора, первый, второй и третий управляющие входы которого подключены соответственно к седьмому, восьмому и девятому выходам блока управления, второй информационный вход объединен с вторым входом четвертого коммутатора, выход переноса сумматора подключен к первому информационному входу первого дешифратора и к первому входу блока управления, а выход суммы подключен к информационному входу регистра, управляющий вход которого подключен к десятому выходу блока управления, выход старших разрядов подключен к входу третьего элемента И, выход которого подключен к первому информационному входу второ- го дешифратора, первый, второй и третий выходы которого подключены к входам соответствующих элементов индикации отказа каналов преобразования, четвертый выход подключен к инверсному входу четвертого элемента И, выход которого подключен к управляющему входу четвертого коммутатора, выход которого подключен к первому информационному входу мажоритарного элемента, выход которого является со- ответствующей выходной шиной, первый и второй адресные входы четвертого коммутатора подключены к соответствующим выходам первого дешифратора, управляющий вход которого подключен к одиннадцатому выходу блока управления, двенадцатый выход которого подключен к прямому входу четвертого элемента И, тринадцатый выход - к управляющему входу мажоритарного элемента, четырнадцатый выход - к управляющему входу второго дешифратора, пятнадцатый выход - к входам установки генератора псевдослучайных чисел, причем первые информационные входы первого и второго дешифраторов, четвертого коммутатора и мажоритарного элемента первого канала преобразования объединены соответственно с третьими информационными входами соответствующих элементов во втором канале преобразования и с вторыми информационными входами соответствующих элементов в третьем канале преобразования, вторые информационные входы указанных элементов 1тэрвого канала

13

преобразования объединены соответственно с первыми информационными входами соответствующих элементов во втором канале преобразования и с третьими информационными входами со- ответств тощих элементов в третьем канале преобразования, а третьи информационные входы указанных- элементов первого канала преобразования объеди нены соответственно с вторыми информационными входами соответствующих элементов во втором канале преобразования и с первыми информационными входами соответствующих элементов в третьем канале преобразования,- шестнадцатый выход блока- управления первого канала преобразования подключен к третьему входу блока управления второго канала преобразования и к второму входу блока управления третьего канала преобразования, шестнадцатый выход блока управления второго канала преобразования подключен к второму входу блока управления пер- вого канала преобразования и к третьему входу блока управления третьего канала преобразования, шестнадцатый выход блока управления третьего канала преобразования подключен к третьему входу блока управления первого канала преобразования и к второму входу блока управления второго ка- . нала преобразования, вторые входы компараторов второго и третьего каналов преобразования объединены с вторым входом компаратора первого канала преобразования.

2. Преобразователь аналог - код по п. 1, отличающийся тем, что блок управления в каждом канале преобразования выполнен на коммутаторе адреса, коммутаторе условных переходов, постоянном запоминающем устройстве, счетчике, регнст- .ре, элементе задержки, элементе И, элементе ИЛИ, первом и втором триггерах, кнопках Пуск и Останов,

10

5

0

5

0

5

резервированном генераторе тактовых импульсов, первый вход которого является вторым входом блока управления, второй вход - третьим входом блока управления, выход является шестнадцатым выходом блока управления и подключен к первому входу элемента И, второй вход которого подключен к выходу второго триггера, выход - к счетному входу первого триггера, первый выход которого подключен к входам стробирования коммутатора адреса и коммутатора условных переходов и входу элемента задержки, -второй выход подключен к управляющему входу постоянного запоминающего устройства, группа выходов которого подключена к соответст- первьм информационным входам коммутатора адреса, выходы с первого по четырнадцатый являются соответствующими выходами блока управления, адресный вход подключен к выходу регистра, управляюш 1й вход которого подключен к выходу элемента задержки, а информационные входы - соответственно к выходам коммутатора адреса и к выходу коммутато за условных переходов, первый информационный вход которого является первым входом блока управления, адресный вход подключен к пятнадцатому выходу постоянного запоминающего устройства, второй информационный вход - к выходу счетчика,вход сброса которого подключен к выходу элемента ИЛИ, счетный вход подключен к шестнадцатому выходу постоянного запоминающего устройства, семнадцатый выход которого подключен к первому входу элемента ИЛИ, второй вход которого объединен с вторыми информационными входами и входом адреса коммутатора адреса, входом установки в 1 второго триггера и подключен к выходу кнопки Пуск и является пятнадцатым выходом блока управления, выход кнопки Останов подключен к входу установки в О второго триггера.

Примечание. Сочетание 8 допускает подключение любого канала

преобразования на выход.

Таблица2

1 О

О

результат преобразования второго

результат преобразования первого

результат преобразования третьего

Таблица 3

2S

2if

S 23

№

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Вероятностный преобразователь аналог-код | 1984 |

|

SU1236608A1 |

| Устройство для взаимного установления подлинности абонентов | 1986 |

|

SU1442993A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Мажоритарное устройство обработки аналоговой информации | 1988 |

|

SU1737775A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в измерительных системах, измерительно-вычислительных комплексах и системах контроля и управления повьппенной надежности. Цельповьппение надежности и помехоустойчивости и обеспечение самоконтроля.Вероятностный преобразователь аналог - код содержит три идентичных взаимосвязанных канала преобразования, каждый из которых выполнен на генераторе 1 псевдослучайных чисел, первом и втором коммутаторах 2, 3, цифроанало- говом преобразователе 4, компараторе 5, первом и втором элементах И 6, 7 первом и втором.счетчиках 8,9,третьем коммутаторе 10, сумматоре 11, регистре 12, третьем элементе И 13, первом и втором дешифраторах 14, 15, четвертом коммутаторе 16, четвертом элементе И 17, блоке 18 управления, мажоритарном элементе 19, трех элементах 20 индикации отказов каналов преобразования. Предложенное устройство позволяет повыс ить надежность и помехоустойчивость за счет различного сдвига фаз сигналов генераторов 1 и мажоритарного режима работы трех каналов преобразования. 1 з.п. ф-лы, 2 ил., 3 табл. ф (/) СО О5 со 4 О5

Составитель В.Першикрв , Редактор А.Огар Техред М.Двдык Корректор О.Кравцова

Заказ 6379/53 Тираж 900Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий .113035, Москва, )К-35, Раушская наб., Д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Гладкий B.C | |||

| Вероятностные вычислительные модели | |||

| М.: Наука, 1973, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Авторское свидетельство СССР № 756626, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-12-30—Публикация

1986-01-06—Подача