11444946

Изобретение относится к измерительной технике и может быть использовано в резервированных информационно-измерительных системах.

Цель изобретения - повьшение точности преобразования.

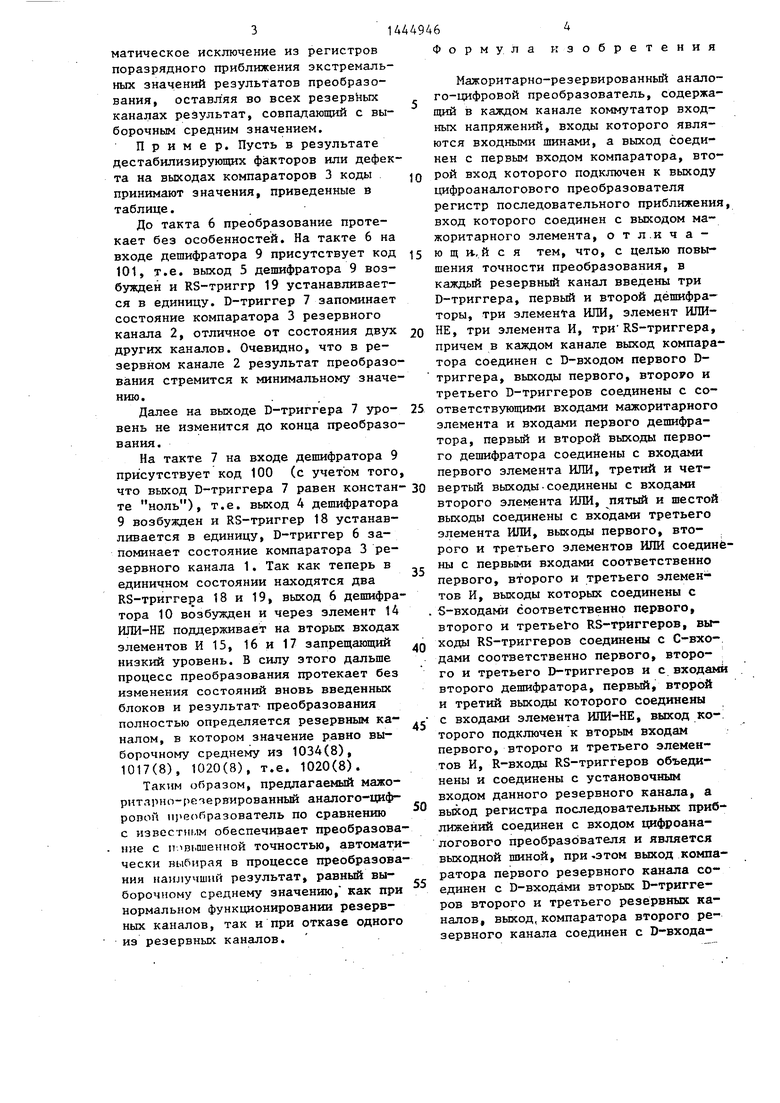

На чертеже представлена структурная схема предлагаемого аналого-цифрового преобразователя.Ю : Мажоритарно-резервированный аналого-цифровой преобразователь в каж- дом резервном канале содержит мажоритарный элемент 1, коммутатор 2 вход- тшх напряжений, компаратор 3, цифро- 15 вом состоянии), на выходе элемента аналоговый преобразователь 4, регистр ИЛИ-НЕ 14 высокий уровень и сигналы

Допустим, что, начиная с некоторо го разряда, состояние выхода компара тора 3 одного из резервных каналов не совпало с состоянием выходов ком параторов 3 двух других резервных каналов. Тогда на одном из шести выходов 1, 2, 3, 4, 5 или 6 дешифратора 9 появится высокий уровень, пройдет через соответствующий элемент ИЛИ 12, 11 или 13 на вход соответствующего элемента И 15, 16 или 17. Та как выходы 3, 5, 6 дешифратора не возбуждены (RS-тригегры 18-20 в нула

вом состоянии), на выходе элемента ИЛИ-НЕ 14 высокий уровень и сигналы

Допустим, что, начиная с некоторого разряда, состояние выхода компаратора 3 одного из резервных каналов не совпало с состоянием выходов ком-, параторов 3 двух других резервных каналов. Тогда на одном из шести выходов 1, 2, 3, 4, 5 или 6 дешифратора 9 появится высокий уровень, пройдет через соответствующий элемент ИЛИ 12, 11 или 13 на вход соответствующего элемента И 15, 16 или 17. Так как выходы 3, 5, 6 дешифратора не возбуждены (RS-тригегры 18-20 в нула

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| ТРЕХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ ГЕНЕРАТОР | 1988 |

|

SU1568771A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ДЛЯ ФОРМИРОВАНИЯ МЕТОК ВРЕМЕНИ | 2008 |

|

RU2379829C1 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| ТРЕХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ ГЕНЕРАТОР | 1991 |

|

RU2037194C1 |

| Счетное резервированное устройство | 1986 |

|

SU1354413A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Мажоритарное устройство обработки аналоговой информации | 1988 |

|

SU1737775A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

Изобретение относится к области измерительной техники и может быть использовано в резервированных информационно-измерительных системах. Для повышения точности преобразования аналого-цифровой преобразователь дополнительно содержит группу D-триг- геров, первый и второй дешифраторы, группу элементов ИЛИ, элемент ИЛИ-НЕ, группу элементов И, группу RS-тригге- ров. Вновь введенные блоки, работая совместно с мажоритарно-резервированным аналого-цифровым преобразователем поразрядного взвешивания, обеспечивают в процессе преобразования - автоматическое исключение из регистров поразрядного приближения экстремальных значений результатов преобразования, оставляя во всех резервных каналах результат, совпадакяций с выборочными средним значением, 1 табл., 1 ил.

5 поразрядного приближения, первый, второй и третий D-триггеры, обозначенные соответственно 6, 7 и 8, пер- вьй дешифратор 9, второй дешифратор 10, первый, второй и третий элементы ИЛИ, обозначенные соответственно 11, 12: и 13, элемент ИЛИ-НЕ 14, первый, второй и третий элементы И 15, 16 и 17 соответственно, первый, второй и третий RS-триггеры 18, 19 и 20.

Мажоритарно-резервированный аналого-цифровой преобразователь работает следующим образом.

Перед началом преобразования из центрального устройства (не показанного на чертеже) на установочные входы аналого-цифрового преобразователя поступает сигнал, устанавливающий RS-триггеры 18-20 в каждом резервном канале в нулевое состояние. Низкие уровни с выходов RS-триггеров 18-20 поступают на С-входы D-тригге- ,ров 6-8 и переводят последние в режим повторителя, т.е. сигналы с выхо-до либо 110, т.е. на дешифраторе 10 появится возбужденный выход , который создаст через элемент 14 ШШ-НЕ на входах элементов И 15, 16, 17 запрещающий низкий уровень, а один из D-триггеров 6, 7 или 8 запомнит состояние выхода компаратора 3 еще одного резервного канала. Далее процесс преобразования не приводит к изменению состояния вновь введенных

дов компараторов 3 каждого резервного канала, поступающие на D-входы, передаются на выходы D-триггеров 6-8 и далее на входы мажоритарного элемента 1 и первого/дешифратора 9. Одно- временно со сбросом RS-триггеров 18- 20 регистр 5 поразрядного приближения начинает процесс преобразования, подавая на вход цифро-аналогового преобразователя 4 весовые коды, начи- - блоков и завершается известным обра- ная со старшего разряда. До тех пор, зом.

пока последовательные коды на выхо- Сущность предлагаемого мажоритар- дах.компараторов 3 всех разрядных каналов совпадают, преобразование протекает по алгоритму поразрядного : г уравновешивания, выходы дешифраторов 9 и 10 не переходят в возбужденные состояния, RS-триггеры 18-20 остаются в исходных нулевых состояниях.

но-резервированного аналого-цифрового преобразователя заключается в том, что вновь введенные блоки, работая совместно мажоритарно-резервированным аналого-цифровым преобразователем поразрядного уровновешивания, обеспечивают в процессе преобразования авто0

5

с выходов элементов ИЛИ 11, 12 или 13 проходят через элементы И 15, 16 или 17 на S-вход соответствующего RS-триггера 18, 19 или 20, устанавливая последний в единичное состояние. Высокий уровень с сработавшего RS-т риггера 18, 19 или 20 защелкнет на соответствующем D- триггере 6, 7 или 8 состояние выхода того компаратора 3 из трех резервных-каналов которое отличается от двух других. После отработки описанного события RS-триггеры 18-20 поддерживают на 0 входах дешифра.тора 10 либо код 001 либо 010, либо 100, т.е. выходы 3, 5, 6 дешифратора 10 по-прежнему не возбуждены.

Следующим шагом в работе аналого- цифрового преобразователя является повторение события на некотором следующем разряде. При повторении события RS-триггеры .18-20 установятся в состояние либо 011, либо 101,

5

Сущность предлагаемого мажоритар-

но-резервированного аналого-цифрового преобразователя заключается в том, что вновь введенные блоки, работая совместно мажоритарно-резервированным аналого-цифровым преобразователем поразрядного уровновешивания, обеспечивают в процессе преобразования авто

3

матическое исключение из регистров поразрядного приближения экстремальных значений результатов преобразования, оставляя во всех резервных каналах результат, совпадающий с выборочным средним значением.

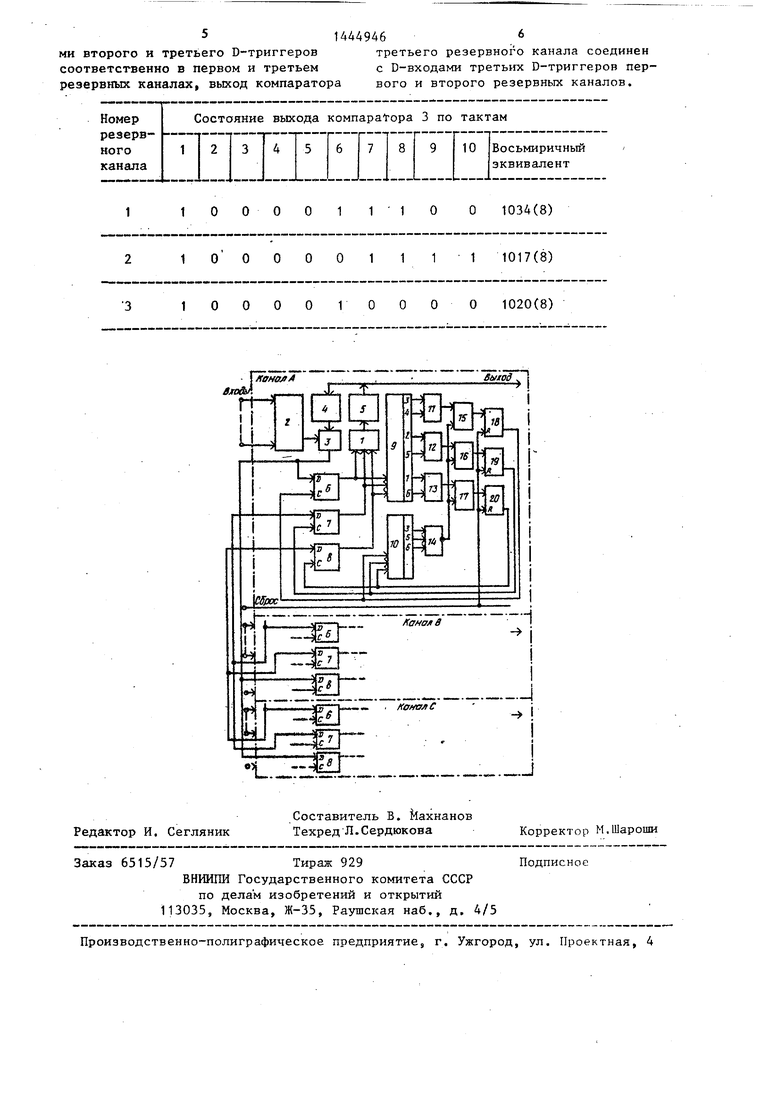

Пример. Пусть в результате дестабилизирующих факторов или дефекта на выходах компараторов 3 коды принимают значения, приведенные в таблице.

До такта 6 преобразование протекает без особенностей. На такте 6 на входе дешифратора 9 присутствует код 101, т.е. выход 5 дешифратора 9 возбужден и RS-триггр 19 устанавливается в единицу. D-триггер 7 запоминает состояние компаратора 3 резервного канала 2, отличное от состояния двух других каналов. Очевидно, что в резервном канале 2 результат преобразования стремится к минимальному значению.

Далее на выходе D-триггера 7 уровень не изменится до конца преобразования.

На такте 7 на входе дешифратора 9 присутствует код 100 (с учетом того что выход D-триггера 7 равен констан те ноль), т.е. выход 4 дешифратора 9 возбужден и RS-триггер 18 устанавливается в единицу, D-триггер 6 запоминает состояние компаратора 3 резервного канала 1. Так как теперь в единичном состоянии находятся два RS-триггера 18 и 19, выход 6 дешифратора 10 возбужден и через элемент 14 ИЛИ-НЕ поддерживает на вторых входах элементов И 15, 16 и 17 запрещакщий низкий уровень. В силу этого дальше процесс преобразования протекает без изменения состояний вновь введенных блоков и результат преобразования полностью определяется резервным каналом, в котором значение равно выборочному среднему из 1034(8), 1017(8), 1020(8), т.е. 1020(8).

Таким образом, предлагаемый мажо- ритярно-речервированный аналого-цифровой преобразователь по сравнению с извсстнмм обеспечивает преобразование с 1т.1пышенной точностью, автоматически выбирая в процессе преобразования наилучший результат, равный выборочному среднему значению, как при нормальном функционировании резервных каналов, так и при отказе одного иэ резервных каналов.

рмула изобретения

10

15

20

25

Ф о

ЗО

35

40

45

50

5

Мажоритарно-резервированный аналого-цифровой преобразователь, содержащий в каждом канале коммутатор входных напряжений, входы которого являются входными шинами, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу цифроанапогового преобразователя регистр последовательного приближения, вход которого соединен с выходом мажоритарного элемента, о т л.и ч а - ю щ и., и с я тем, что, с целью повышения точности преобразования, в каждый резервньй канал введены три D-триггера, первый и второй дешифраторы, три элемента ИЛИ, элемент ИЛИ- НЕ, три элемента И, три RS-триггера, причем в каждом канале выход компаратора соединен с D-входом первого D- триггера, выходы первого, второго и третьего D-триггеров соединены с соответствующими входами мажоритарного элемента и входами первого дешифратора, первый и второй выходы первого дешифратора соединены с входами первого элемента ШШ, третий и четвертый выходы.соединены с входами второго элемента ИЛИ, пятый и шестой выходы соединены с входами третьего элемента ШШ, выходы первого, второго и третьего элементов ИЛИ соединены с первыми входами соответственно первого, второго и третьего элементов И, выходы которых соединены с S-входами соответственно первого, второго и третьего RS-триггеров, выходы RS-триггеров соединены с С-вхо- дами соответственно первого, второго и третьего D-триггеров и с входами второго дешифратора, первый, втррой и третий выходы которого соединены с входами элемента ИЛИ-НЕ, выход ко- торого подключен к вторым входам первого, второго и третьего элементов И, R-входы RS-триггеров объединены и соединены с установочным входом данного резервного канала, а выход регистра последовательных приближений соединен с входом цифроана- логового преобразователя и является выходной шиной, при отом выход компаратора первого резервного канала соединен с D-входами вторых D-триггеров второго и третьего резервных каналов, выход, компаратора второго резервного канала соединен с D-входа5U449466

ми второго и третьего D-триггеровтретьего резервного канала соединен

соответственно в первом и третьемс D-входами третьих D-триггеров перреэервнъгх каналах, выход компаратора вого и второго резервных каналов.

100001 110 О 1034(8)

1 о О О О О 1 1 11 1017(8)

1000010000 1020(8)

VffOHO H

J

| Гитис Э.И | |||

| Преобразователи информации для ЭЦВУ, М.: Наука, 1975, с | |||

| РУЧКА С РЕЗЕРВУАРОМ ДЛЯ ЧЕРНИЛ | 1922 |

|

SU402A1 |

| Мартыненко Я.Д., Смесов А.А., Татаринов К.А., Шмойлов Ю.А | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Электронная техника | |||

| Сер | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-16—Подача