Изобретение относится к автоматике и вычислительной технике, а именно к преобразователям угла поворота вала в код.

Цель изобретения - повышение точности преобразователя угла поворота

вала в код путем снижения погрешности, пропорциональной скорости вращения вала, исключения немонотонности изменения кода угла при равномерном вращении вала, а также повышение точности формирования кода угловой скорости.

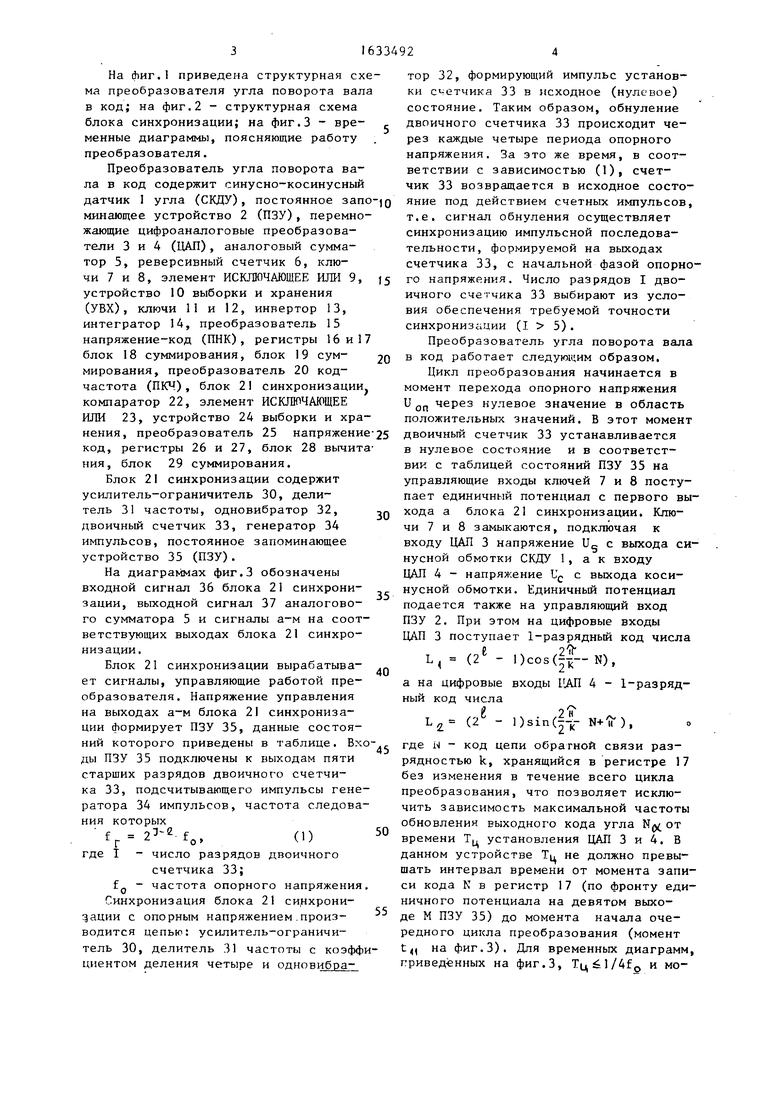

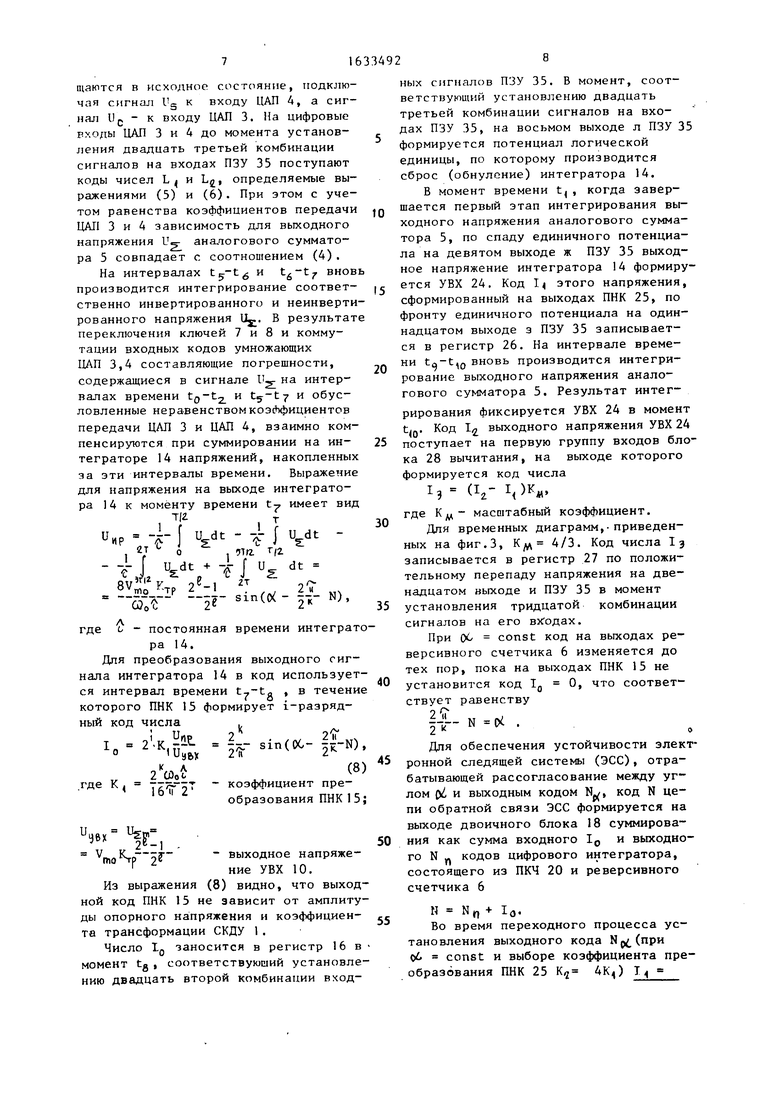

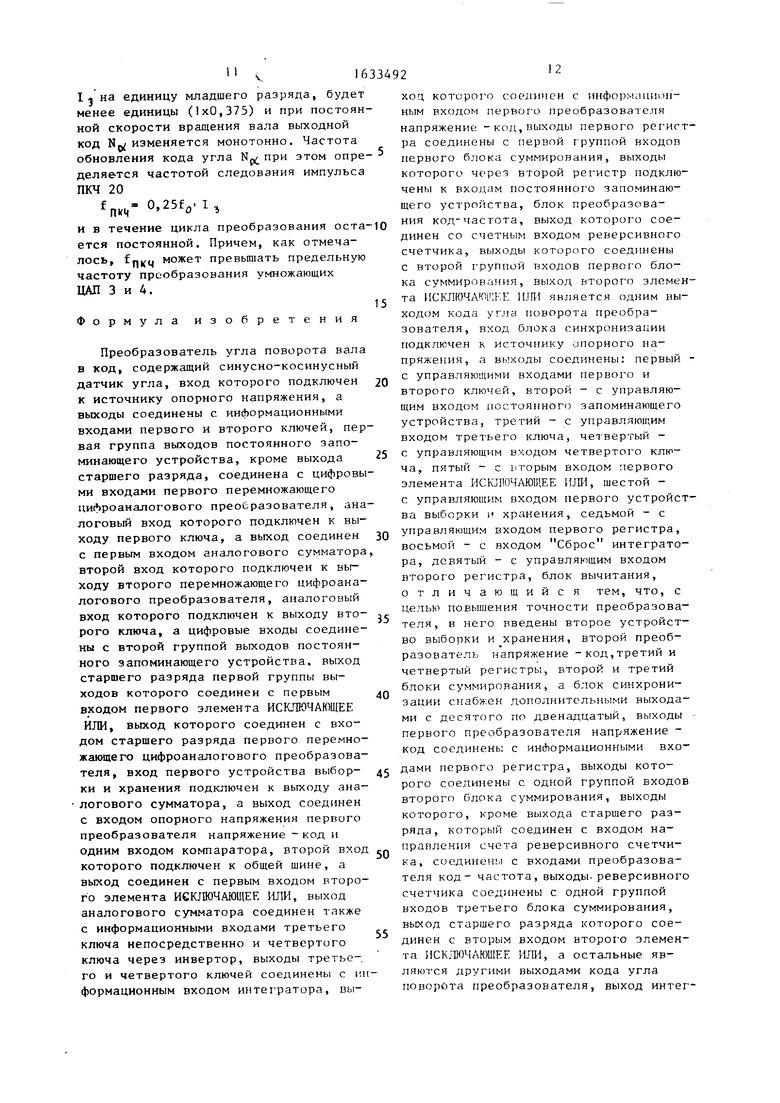

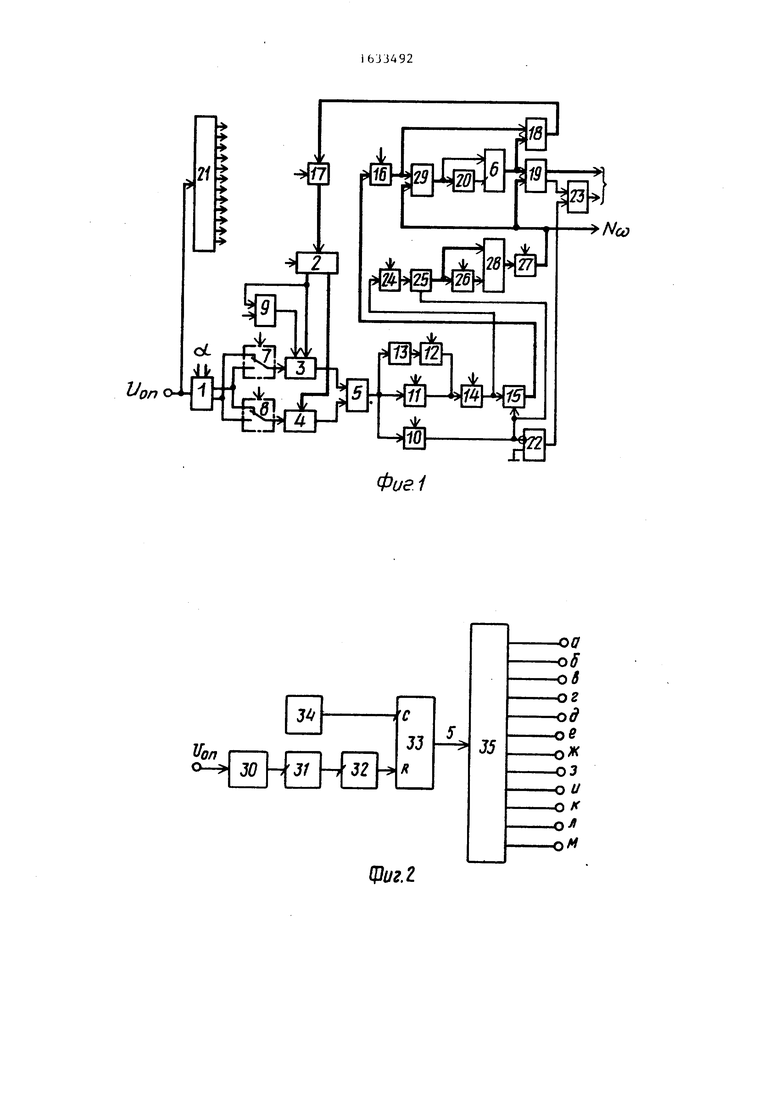

На Лиг. приведена структурная схема преобразователя угла поворота вала в код; на фиг.2 - структурная схема блока синхронизации; на фиг.З - временные диаграммы, поясняющие работу преобразователя.

Преобразователь угла поворота вала в код содержит синусно-косинусный датчик 1 угла (СКДУ), постоянное запоминающее устройство 2 (ПЗУ), перемножающие цифроаналоговые преобразователи 3 и 4 (ЦАП), аналоговый сумматор 5, реверсивный счетчик 6, ключи 7 и 8, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, устройство 10 выборки и хранения (УВХ), ключи Н и 12, инвертор 13, интегратор 14, преобразователь 15 напряжение-код (ПНК), регистры 16 и 17 блок 18 суммирования, блок 19 суммирования, преобразователь 20 код- частота (ПК1), блок 21 синхронизации компаратор 22, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, устройство 24 выборки и хранения, преобраэоватепь 25 напряжение- код, регистры 26 и 27, блок 28 вычитания, блок 29 суммирования.

Блок 21 синхронизации содержит усилитель-ограничитель 30, делитель 31 частоты, одновибратор 32, двоичный счетчик 33, генератор 34 импульсов, постоянное запоминающее устройство 35 (ПЗУ).

На диаграммах фиг.З обозначены входной сигнал 36 блока 21 синхронизации, выходной сигнал 37 аналогового сумматора 5 и сигналы а-м на соответствующих выходах блока 21 синхронизации.

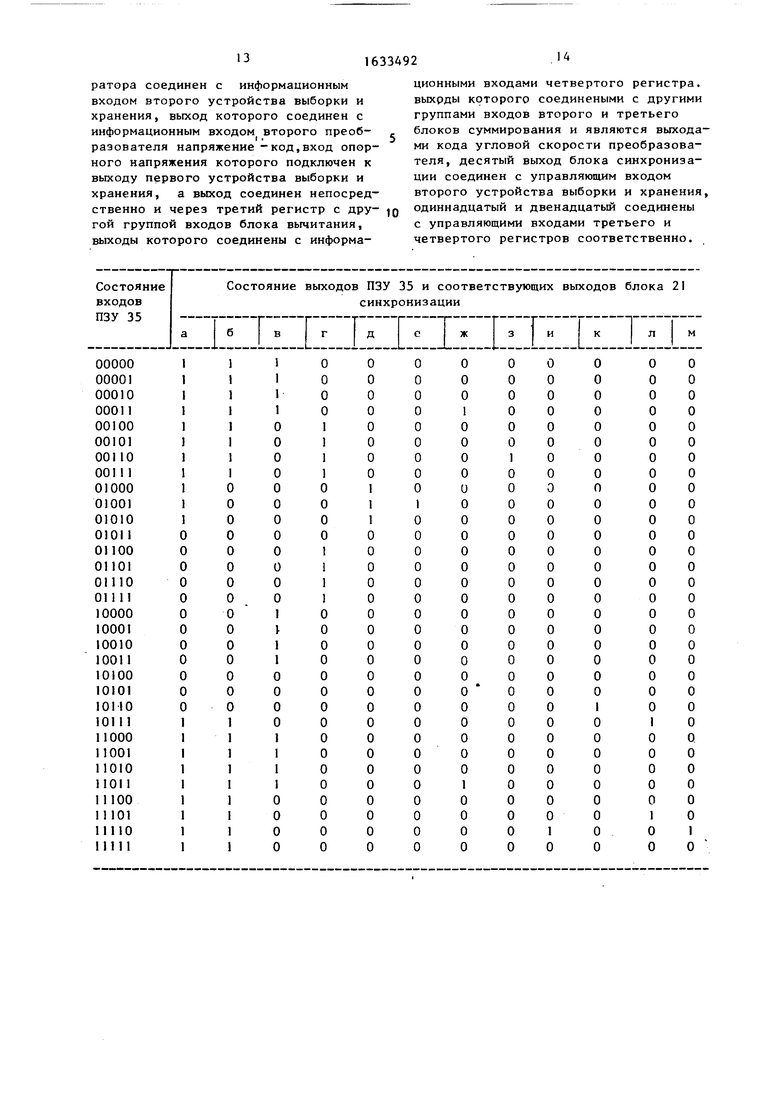

Блок 21 синхронизации вырабатывает сигналы, управляющие работой преобразователя. Напряжение управления на выходах а-м блока 21 синхронизации Нормирует ПЗУ 35, данные состояний которого приведены в таблице. Входы ПЗУ 35 подключены к выходам пяти старших разрядов двоичного счетчика 33, подсчитывающего импульсы генератора 34 импульсов, частота следования которых

f

где

Г

Lo

число разрядов двоичного счетчика 33;

fQ - частота опорного напряжения. Синхронизация блока 21 синхронизации с опорным напряжением производится цепью: усилитель-ограничитель 30, делитель 31 частоты с коэффи циентом деления четыре и одновибра0

5

0

5

0

5

0

5

0

5

тор 32, формирующий импульс установки сметчика 33 в исходное (нулевое) состояние. Таким образом, обнуление двоичного счетчика 33 происходит через каждые четыре периода опорного напряжения. За это же время, в соответствии с зависимостью (1), счетчик 33 возвращается в исходное состояние под действием счетных импульсов, т.е. сигнал обнуления осуществляет синхронизацию импульсной последовательности, формируемой на выходах счетчика 33, с начальной фазой опорного напряжения. Число разрядов I двоичного счетчика 33 выбирают из условия обеспечения требуемой точности синхронизации (I 5).

Преобразователь угла поворота вала в код работает следующим образом.

Цикл преобразования начинается в момент перехода опорного напряжения U оп через нулевое значение в область положительных значений. В этот момент двоичный счетчик 33 устанавливается в нулевое состояние и в соответствии с таблицей состояний ПЗУ 35 на управляющие входы ключей 7 и 8 поступает единичный потенциал с первого выхода а блока 21 синхронизации. Ключи 7 и 8 замыкаются, подключая к входу ЦАП 3 напряжение Ug с выхода синусной обмотки СКДУ 1, а к входу ЦАП 4 - напряжение Uc с выхода косинусной обмотки. Единичный потенциал подается также на управляющий вход ПЗУ 2. При этом на цифровые входы ЦАП 3 поступает 1-разрядный код числа

L, (2е - l)cos(|f--N),

а на цифровые входы 1ГДП 4 - 1-разрядный код числа

L2 (2й - l)sin(- N+tf),

где и - код цепи обратной связи разрядностью k, хранящийся в регистре 17 без изменения в течение всего цикла преобразования, что позволяет исключить зависимость максимальной частоты обновления выходного кода угла N от времени Т ц установления ЦАП 3 и 4. В данном устройстве Тц не должно превышать интервал времени от момента записи кода К в регистр 17 (по фронту единичного потенциала на девятом выходе М ПЗУ 35) до момента начала очередного цикла преобразования (момент t на фиг.З). Для временных диаграмм, приведенных на фиг.З, Тц 1/4Јо и мо51633492

же т превышать минимальный период обновления выходного кода угла М-,.

Напряжения на выходах ЦАП 3 и ЦАП 4 описываются соотношениями

U,

в4

10

С момента времени t (восьмая комбинация входных сигналов ПЗУ 35) ключ 12 размыкается, а на управляющий вход 2 поступает сигнал логического нуля. При этом коды, поступающие на ЦАП 3 и 4, меняются между собой. Е ., . ,2 „./ч(2 -l)sin(|i- N+и );

г fr (2К -l)cos(- N)

(5) (0)

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1424124A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478332A1 |

| Устройство для измерения диаграммы направленности антенны | 1990 |

|

SU1707573A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к преобразователям угла поворота вала в код. Целью изобретения является повышение точности преобразователя угла поворота вала в код за счет снижения скоростной составляющей погрешности. Цель достигается тем, что в преобразователь, содержащий синусно- косинусный датчик угла, постоянное запоминающее устройство (ПЗУ), два перемножающих цифроаналоговых преобразователя ( ЦАШ , аналоговый сумматор, реверсивный счетчик, четыре ключа, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, устройство выборки и хранения, инвертор, интегратор, преобразователь напряжение - код, два регистра, блок вычитания, блок суммирования, преобразователь код-частота, блок синхронизации и компаратор, введены второе устройство выборки и хранения, второй преобразователь напрях;ение-код, третий и четвертый регистры, второй и третий блоки суммирования. Введенные в преобразователь блоки образуют канал измерения угловой скорости, причем в отличие от устройства-прототипа формирование кода скорости осуществляется одновременно с формированием кода угла и при неизменном коде на входах ПЗУ. Это позволяет снизить скоростную составляющую погрешности за счет исключения погрешностей ПЗУ и ЦАП и, кроме того, уменьшить коэффициент коррекции скоростной погрешности первого блока суммирования и, таким образом, исключить возможную немонотонность изменения выходного кода угла при равномерном вращении вала. 3 ил.,. 1 табл. «Л О со со 4Ь 9

Подставив в формулы (2) и (3) выражения для выходных сигналов СКДУ 1

V- vrr)0.KT

sin sinOCL t;

Uc Vmo.KTp- cos -sincj0t:

где

VmoKTp

U

mo

K.

максимальная амплитуда выходных сигналов СКДУ 1;

амплитуда опорного напряжения;

коэффициент трансформации СКДУ Г;

круговая частота опорного напряжения,

после преобразования получаем зависимость для выходного напряжения аналогового сумматора 5

-

Я U.

U,

U4

27

V.

е

2 -1

mo

(4)

x sin( tf - -у N)sin C00 t ,

С целью упрощения полученной зависимости коэффициенты передачи перемножающих 1 АП 3 и 4 в соотношениях (2) и (3) приняты равными.

В начале цикла преобразования, в соответствии с таблицей, ключ 11 замкнут и напряжение U поступает на , вход интегратора 14. В момент времени t (фиг.З), соответствующий установлению четвертой комбинации сигналов на входах ПЗУ 35, ключ 11 размыкается, а ключ 12 замыкается и выходное напряжение аналогового сумматора 5 U- поступает на вход интегратора 14 через инвертор 13. Таким образом осуществляются синхронное двух- полупериодное выпрямление сигнала Ut- и интегрирование выпрямленного сигнала в течение периода питающего напряжения. При этом полностью подавляются квадратурные и четные гармонические составляющие сигнала U. , a остальные высокочастотные составляющие ослабляются.

Одновременно в момент t с пятого выхода g блока 21 синхронизации подается сигнал логической единицы на управляющий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, и значение старшего разряда кода L | инвертируется, т.е. выражение (5) принимает вид

(2 -) sin(-N) (7)

Используя зависимости (6) и (7), получаем следующее выражение для выходного сигнала аналогового сумматора 5:

2«UZO -2tT

cos«tf- f-J-N)x

0

5

0

5

0

x sinC00t

В установившемся состоянии элект„гронной следящей системы (ЭСС) --г.-N

2 к

и амплитуда выходного сигнала аналогового сумматора 5 соответствует максимальной амплитуде выходных сигналов СКДУ 1. В течение действия девятой комбинации сигналов на входах ПЗУ 35 с шестого выхода 1 ПЗУ 35 поступает сигнал логической единицы на управляющий вход УВХ 10 и выходное напряжение УВХ 10 начинает повторять его входной сигнал. Максимальное значение выходного сигнала аналогового сумматора 5 фиксируется на выходе УВХ 10 в момент времени tj, соответствующий установлению десятой комбинации сигналов на входах ПЗУ 35. Сиг-нал на выходе УВХ 10 служит опорным напряжением для ПНК 15 и ПНК 2Ь. Таким образом устраняется влияние на точность преобразования температурной и временной нестабильности амплитуды опорного напряжения трансформации СКДУ 1. г. В момент времени Ц (установление одиннадцатой комбинации сигналов на входах ПЗУ 35) на всех выходах блока 21 синхронизации устанавливается нулевой-потенциал, ключи 7 и 8 возвраl on и коэффициента

щаются в исходное состояние, подключая сигнал Us к входу ЦАП 4, а сигнал DC - к входу ЦАП 3. На цифровые РХОДЫ ЦАП 3 и 4 до момента установ- ления двадцать третьей комбинации сигналов на входах ПЗУ 35 поступают коды чисел L и L2, определяемые выражениями (5) и (6). При этом с учетом равенства коэффициентов передачи ЦАП 3 и 4 зависимость для выходного напряжения аналогового сумматора 5 совпадает с соотношением (4).

На интервалах и внов производится интегрирование соответ- ственно инвертированного и неинвертированного напряжения U.. В результат переключения ключей 7 и 8 и коммутации входных кодов умножающих ЦАП 3,4 составляющие погрешности, содержащиеся в сигнале на интервалах времени tfl-tz и t5-t и обусловленные неравенством коэффициентов передачи ЦАП 3 и ЦАП 4, взаимно компенсируются при суммировании на ин- теграторе 14 напряжений, накопленных за эти интервалы времени. Выражение для напряжения на выходе интегратора 1 4 к моменту времени t-p имеет вид

1Т 1 }

т V т Vb 1 V ° 1 ™

1| 1 е

TJ

Ок , то ;-тр -I . . I. «

оГоГ F 2 N)

ЯП Т|2.

U dt 8V31 К 9е-1

ОУ„,„ Г.-ro - |2 «

где

- постоянная времени интегратора 14.

Для преобразования выходного сигнала интегратора 14 в код используется интервал времени t-,-tg , в течение которого ПНК 15 формирует i-раэряд- ный код числа

2;.К,

zW

k

21Г

-JJJT sin (ОС- ) (8)

где К . коэффициент пре- 1 о и J ,.„,

образования ПНК 15;

U

уех %

выходное напряжение УВХ 10. Из выражения (8) видно, что выходной код ПНК 15 не зависит от амплитуды опорного напряжения и коэффициен- та трансформации СКДУ 1.

Число IQ заносится в регистр 16 в момент tg, соответствующий установлению двадцать второй комбинации вход,. Q

| п 5

35

0

5

0

ных сигналов ПЗУ 35. В момент, соответствующий установлению двадцать третьей комбинации сигналов на входах ПЗУ 35, на восьмом выходе л ПЗУ 35 формируется потенциал логической единицы, по которому производится сброс (обнуление) интегратора 14.

В момент времени t( , когда завершается первый этап интегрирования выходного напряжения аналогового сумматора 5, по спаду единичного потенциала на девятом выходе ж ПЗУ 35 выходное напряжение интегратора 14 формируется УВХ 24. Код l этого напряжения, сформированный на выходах ПНК 25, по фронту единичного потенциала на одиннадцатом выходе з ПЗУ 35 записывается в регистр 26. На интервале времени t(,-t,0 вновь производится интегрирование выходного напряжения аналогового сумматора 5. Результат интегрирования фиксируется УВХ 24 в момент . Код TЈ выходного напряжения УВХ 24 поступает на первую группу входов блока 28 вычитания, на выходе которого формируется код числа

I, (V I)KM,

где Км масштабный коэффициент.

Для временных диаграмм,-приведенных на фиг.З, Кдц 4/3. Код числа Ij записывается в регистр 27 по положительному перепаду напряжения на двенадцатом выходе и ПЗУ 35 в момент установления тридцатой комбинации сигналов на его .

При (X/ const код на выходах реверсивного счетчика 6 изменяется до тех пор, пока на выходах ПНК 15 не установится код 10 0, что соответ ствует равенству

Ј-«.

Для обеспечения устойчивости электронной следящей системы (ЭСС), отрабатывающей рассогласование между углом 0/, и выходным кодом N, код N цепи обратной связи ЭСС формируется на выходе двоичного блока 18 суммирования как сумма входного 10 и выходного N « кодов цифрового интегратора, состоящего из ПКЧ 20 и реверсивного счетчика 6

N

NO+ 10.

Во время переходного процесса установления выходного кода Np(npn 0& const и выборе коэффициента преобразования ПНК 25 К 4К) Т 4

- 12 10 я Г j 0, т.е. выходной код N.-J канала Люрмирования кода скорости, хранящийся в регистре 27, не оказывает влияния на устойчивость ЭСС.

С целью устранения ложного согласования ЭСС (1ф 0), которое,как следует из зависимости (8), возникае при

29 „ Oi + и

(9)

в схему преобразователя введены компаратор 22 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23. В случае выполнения соотношения (9) напряжение на выходе УВХ 10 становится отрицательным, на выходе компаратора 22 устанавливается потенциал логической единицы и элемент ИСКЛЮЧАЮПЕЕ ИЛИ 23 инвертирует значение старшего разряд выгодного кода Nj блока 19 суммирования.

Код Тэ будет нулевым липь при 0( const. Если же угол (у1 изменяется с постоянной скоростью, то код Т j пропорционален скорости изменения с. и используется для компенсации скоростной погрешности преобразователя, а также поступает на выход преобразователя (NGJ 1з)и может использоваться для целей коррекции цифровой системы автоматического регулирования, включающей преобразователь угл; поворота вала в код. Формирование кода Т j производится при неизменном значении кода N на входах ПЗУ 2, т.е. погрешности ПЗУ- 2-4 не оказывают влияния на величину Ij. Таким образом повышается точность формирования кода 1з пропорционального скорости вращения вала СКДУ 1, и, следовательно, повышается точность компенсации скоростной погрешности преоор о- вателя, т.е. повышается точность преобразования угла поворота вала в код.

В установившемся режиме код 10, поступающий на один из входов (на первую группу входов блоьа 29 суммирования) цифрового интегратора, состоящего из ПКЧ 20 и реверсивного счетчика 6, будет нулевым при фиксированном положении вала (ot- const) и при вращении вала с постоянной скоростью. В последнем случае скоростная погрешность, присущая ЭСС с астатиз- мом первого порядка (с одним интегратором в контуре регулирования), компенсируется введением в контур регулирования кода Ij, пропоционального скорости вращения вала. Мгновенное

0

значение кода угла N при этом отсп- ет от текущего угловог о положения вала на время, равное части длительности одного цикла преобразования. В то же время у известного устройства запаздывание выходного кода превышает длительность цикла преобразования. Таким образом, у предлагаемого устройства удается уменьшить значение ко ф- ФИЦИРНТЯ коррекции скоростной погрешности блок, 19 суммирования, вырабатывающего РЫ ОДНОИ код угла

N N и + KVT з

(10)

5

0

5

0

5

0

5

0

5

где Кс - коэффициент коррекции скоростной погрешности, зависящий от задержки выходной информации (кода Т0 ) относительно начала цикла преобразования. Для временных диаграмм, приведенных на Фиг.З, Кс 0,375. При таком значении Кс исключается немонотонность изменения выходного кода N, которая может возникнуть в известном устройстве при равномерном вращении вала СКДУ 1.

Пусть, например, вал ГКДУ I вращается со скоростью, соответствующей промежуточному значст, ю между единицей первого и второго младших разрядов регистра 27. В -чом случае под воздействием помех происходит случайное переключение кода Ij от значения 0...001 к значению 0...010 и обратно в различных циклах преобразования. В известном устройстве, имеющем коэффициент коррекции в выражении (10) К 1,65, такие переключения кода Iз вызывают переключение кода корректирующей добавки IjK соответственно Е единицу (целая часть от 1x1,65) и три единицы (цепая часть от 2x1,65) младшего разряда, т.е. выходной код угла N случайно изменяется, увеличиваясь ипи уменьшаясь на две единицы младшего разряда. Такое переключение выходного кода N при равномерном изменении угла может вызвать сбои в работе цифровой системы автоматического регулирования, включающей преобразователь угла поворота вала в код, и требует специальных мер для обеспечения устойчивости этой системы.

В предлагаемом устройстве указанные выше естественные переключения младшего разряда кода 1 не вызывают переключения выходного кода угла N, так как приращение кода Т, КС , соответствующее приращению кода скорости

Ij на единицу младшего разряда, будет менее единицы (1x0,375) и при постоянной скорости вращения вала выходной код N изменяется монотонно. Частота обновления кода угла Np при этом определяется частотой следования импульса ПКЧ 20

W ° 25fo b

и в течение цикла преобразования остается постоянной. Причем, как отмечалось, fflifq может превышать предельную частоту преобразования умножающих ЦАП 3 и 4.

Формула изобретения

Преобразователь угла поворота вала в код, содержащий синусно-косинусный датчик угла, вход которого подключен к источнику опорного напряжения, а выходы соединены с информационными входами первого и второго ключей, первая группа выходов постоянного запоминающего устройства, кроме выхода старшего разряда, соединена с цифровыми входами первого перемножающего циЛроаналогового преобразователя, аналоговый вход которого подключен к выходу первого ключа, а выход соединен с первым входом аналогового сумматора второй вход которого подключен к выходу второго перемножающего цифроаналогового преобразователя, аналоговый вход которого подключен к выходу второго ключа, а цифровые входы соединены с второй группой выходов постоянного запоминающего устройства, выход старшего разряда первой группы выходов которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом старшего разряда первого перемножающего цифроаналогового преобразователя, вход первого устройства выборки и хранения подключен к выходу аналогового сумматора, а выход соединен с входом опорного напряжения первого преобразователя напряжение - код и одним входом компаратора, второй вход которого подключен к общей шине, а выход соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход аналогового сумматора соединен также с информационными входами третьего ключа непосредственно и четвертого ключа через инвертор, выходы третьего и четвертого ключей соединены с информационным входом интегратора, вы

10

15

35

20 25 30

40

45

0

5

- с управляю- запоминающего управляющим четвертый - входом четвертого клю- ьторым входом первого

хоц которого соединен с информационным входом первого преобразователя напряжение -код,выходы первого регистра соединены с первой группой входов первого блока суммирования, выходы которого через второй регистр подключены к входам постоянного запоминающего устройства, блок преобразования код-частота, выход которого соединен со счетным входом реверсивного счетчика, выходы которого соединены с второй группой входов первого блока суммирования, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является одним выходом кода угла поворота преобразователя, вход блока синхронизации подключен к источнику опорного напряжения, а выходы соединены: первый - с управляющими входами первого и второго ключей, второй щим входом постоянного устройства, третий - с входом третьего ключа, с управляющим ча, пятый - элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, шестой - с управляющим входом первого устройства выборки и хранения, седьмой - с управляющим входом первого регистра, восьмой - с входом Сброс интегратора, девятый - с управляющим входом второго регистра, блок вычитания, отличающийся тем, что, с целью повышения точности преобразователя, в него введены второе устройство выборки и хранения, второй преобразователь напряжение -код,третий и четвертый регистры, второй и третий блоки суммирования, а блок синхронизации снабжен дополнительными выходами с десятого по двенадцатый, выходы первого преобразователя напряжение - код соединены с информационными входами первого регистра, выходы которого соединены с одной группой входов второго блока суммирования, выходы которого, кроме выхода старшего разряда, который соединен с входом направления счета реверсивного счетчика, соединены с входами преобразователя код- частота, выходы, реверсивного счетчика соединены с одной группой входов третьего блока суммирования, выход старшего разряда которого соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а остальные являются другими выходами кода угла поворота преобразователя, выход интегратора соединен с информационным входом второго устройства выборки и хранения, выход которого соединен с информационным входом второго преоб- раэователя напряжение -код,вход опорного напряжения которого подключен к выходу первого устройства выборки и хранения, а выход соединен непосредственно и через третий регистр с дру- гой группой входов блока вычитания, выходы которого соединены с информационными входами четвертого регистра, выхрды которого соединеными с другими группами входов второго и третьего блоков суммирования и являются выходами кода угловой скорости преобразователя, десятый выход блока синхронизации соединен с управляющим входом второго устройства выборки и хранения, одиннадцатый и двенадцатый соединены с управляющими входами третьего и четвертого регистров соответственно.

I

CN

en зn

Ъ

cs o 4a«s bQ iЈ« 5 X 999999Q9999 Q

ъ

I

CSJ IS

§

i

i i t

фие.З

| Вульвет Дж | |||

| Датчики в цифровых системах | |||

| - М.: Энергоиздат, 1981, с.152 | |||

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-15—Подача