Изобретение относится к области радиолокации и предназначено для измерения скорости объекта; может быть использовано в радиолокационных системах распознавания, а также радиолокационных станциях управления воздушным движением для обнаружения и измерения скорости летательных аппаратов.

Известна импульсная РЛС с цифровой обработкой сигналов, состоящая из последовательно включенных АЦП, схемы подавления отражений и блока обработки доплеровской частоты, включающего преобразователь прямоугольных координат в полярные, блока задержки, сумматор, преобразователь полярных координат в прямоугольные и пороговую схему. Однако данное устройство обладает низкой точностью и усложненной реализацией из-за наличия двойного преобразования координат.

Известна также доплеровская РЛС для измерения скорости, состоящая из последовательно включенных гауссовского фильтра, двух каналов и устройства деления; каждый состоит из последовательно включенных линии задержки, детектора, ФНЧ и сумматора. Однако данное устройство использует непрерывный сигнал, что не обеспечивает высокой разрешающей способности радиолокационной станции и снижает дальность обнаружения по сравнению с импульсным режимом излучения.

Наиболее близким к изобретению является радиолокационное устройство для обнаружения движущейся цели, содержащее последовательно включенные блоки задержки, умножитель комплексных чисел и вычитатель. Однако это устройство обладает низкой точностью и неоднозначностью измерения, обусловленной периодичностью зондирующего сигнала.

Целью изобретения является повышение точности и расширение линейных пределов однозначности измерения скорости.

Для этого в радиолокационное устройство обнаружения движущейся цели, содержащее последовательно включенные блоки задержки, умножитель комплексных чисел и вычитатель, введены дополнительно первый и второй ключи, объединенные входы которых являются входом устройства, первый элемент НЕ, вход которого подключен к выходу блока управления и является управляющим входом второго ключа, а выход является управляющим входом первого ключа; выход второго ключа является входом первого блока задержки, выход которого объединен с выходом первого ключа и является входом второго блока задержки и вторым входом умножителя комплексных чисел, первым входом которого является выход второго блока задержки, причем первый квадратурный канал с выхода второго блока задержки подключен к входу умножителя комплексных чисел непосредственно, а второй - через первый инвертор; выход умножителя комплексных чисел является входом блока усреднения, выход которого подключен к входу блока вычисления фазы, а также к входу блока объединения; выход блока вычисления фазы подключен к второму входу вычитателя, к первому входу которого подключен выход элемента задержки, вход которого является также выходом блока вычисления фазы; выход вычитателя подключен к объединенным входам третьего и четвертого ключей, управляющие входы которых подключены к выходу блока управления: третьего ключа - через второй элемент НЕ, а четвертого ключа - непосредственно; кроме того, выход четвертого ключа является входом второго инвертора, выход которого подключен к входу пятого ключа, к которому также подключен выход третьего ключа; управляющим входом пятого ключа является выход порогового устройства, первым входом которого является выход блока объединения, а вторым входом - выход первого элемента памяти; выход пятого ключа является первым входом перемножителя, вторым входом которого является выход второго элемента памяти, выход перемножителя является выходом устройства.

Отличительными от прототипа признаками предложенного устройства являются дополнительно введенные первый, второй, третий, четвертый, пятый ключи, первый и второй элементы НЕ, элемент задержки, первый и второй инверторы, блок усреднения, блок вычисления фазы, блок объединения, пороговое устройство, первый и второй элементы памяти, перемножитель, блок управления и новые связи между ними.

Следовательно, вся заявляемая совокупность существенных признаков технического решения является новой и устройство соответствует критерию "новизна".

Вновь вводимые блоки известны, кроме блока вычисления фазы. Кроме того, вновь введенная совокупность связей не обнаружена. Таким образом, устройство соответствует критерию "существенные отличия".

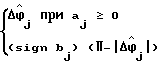

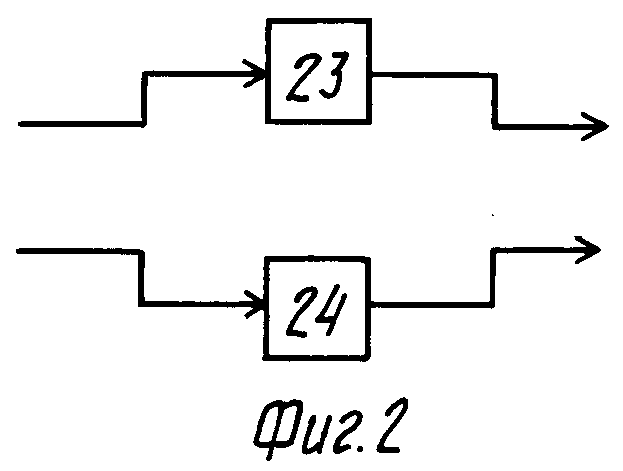

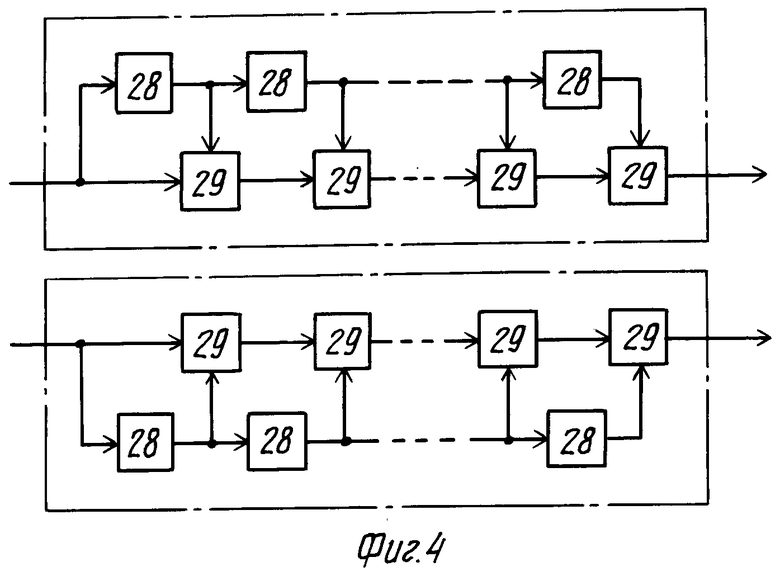

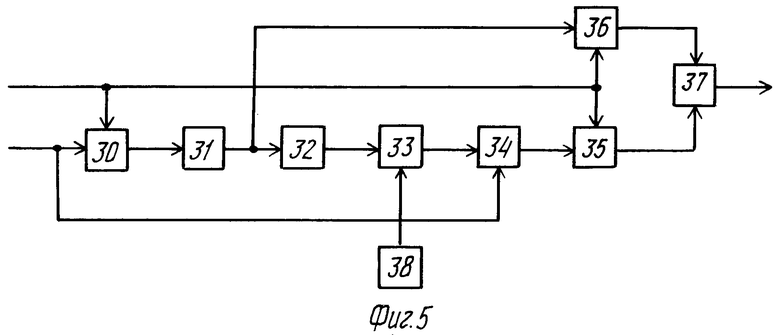

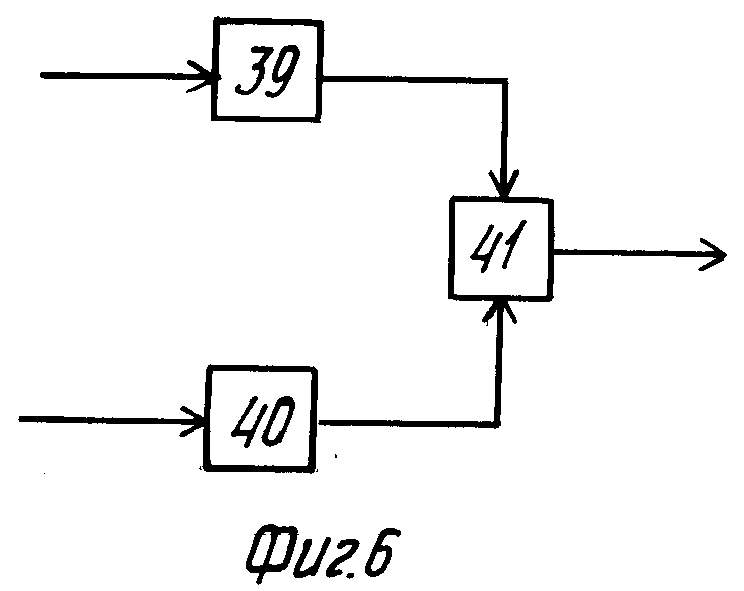

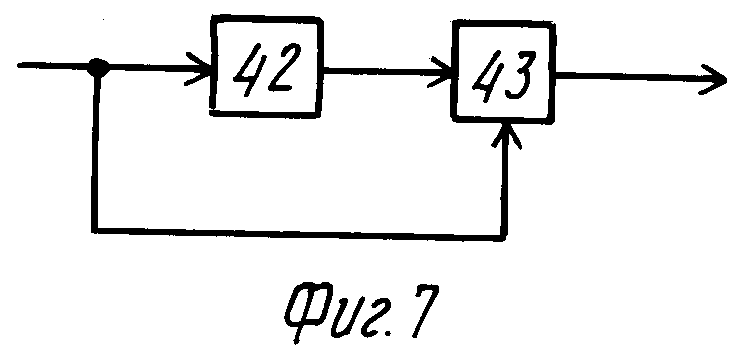

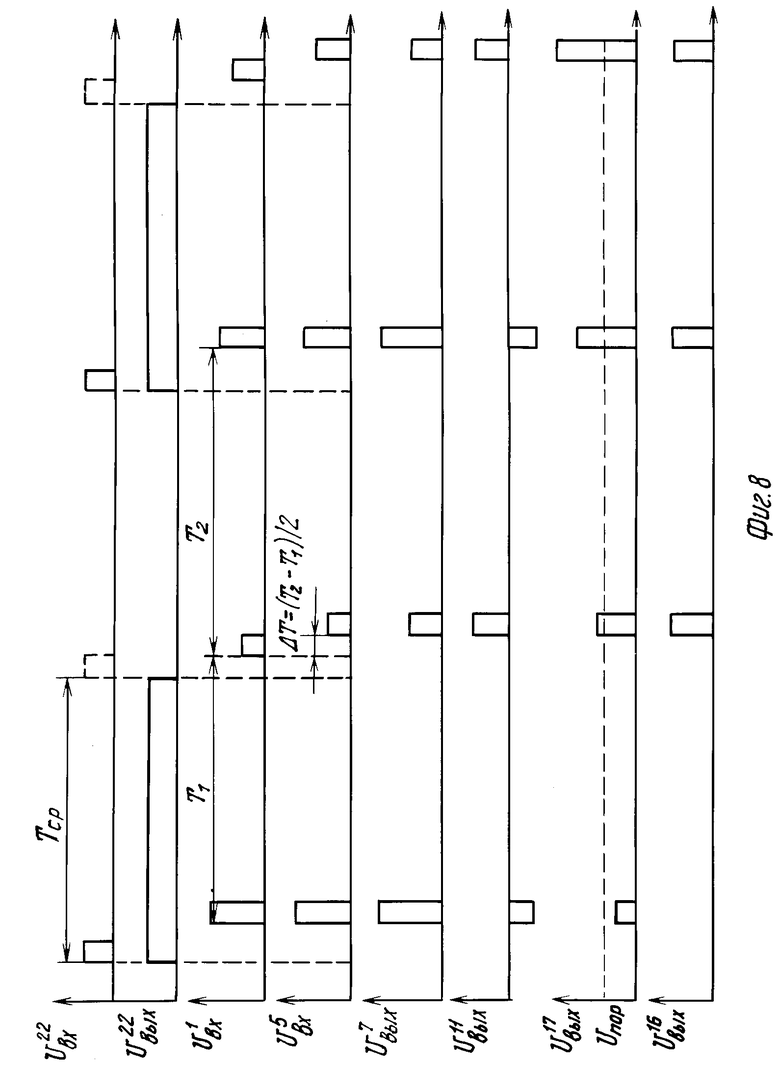

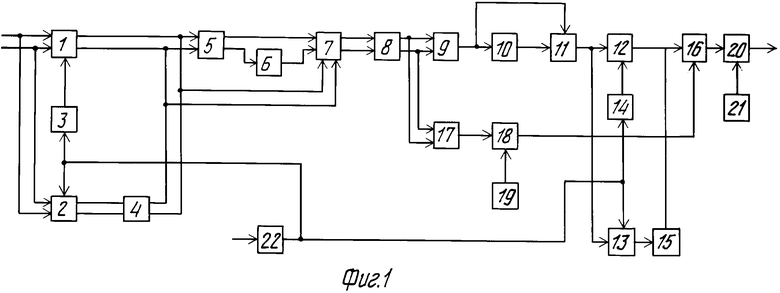

На фиг. 1 приведена структурная электрическая схема предложенного обнаружителя-измерителя доплеровских сигналов; на фиг.2 - то же, блока задержки; на фиг.3 - то же, умножителя комплексных чисел; на фиг.4 - то же, блока усреднения; на фиг.5 - то же, блока вычисления фазы; на фиг.6 - то же, блока объединения; на фиг. 7 - то же, блока управления; на фиг.8 - временные диаграммы работы предложенного устройства (на временных диаграммах Uвх1, Uвх5, Uвых7 показан сигнал лишь одной квадратурной составляющей; цифровой индекс соответствует номеру блока).

Обнаружитель-измеритель доплеровских сигналов (см.фиг.1) содержит первый 1 и второй 2 ключи, объединенные входы которых являются входом устройства, первый элемент НЕ 3, вход которого подключен к выходу блока 22 управления и является управляющим входом второго ключа 2, а выход является управляющим входом первого ключа 1; выход второго ключа является входом первого блока задержки 4, выход которого объединен с выходом первого ключа и является входом второго блока задержки 5 и вторым входом умножителя 7 комплексных чисел, первым входом которого является выход второго блока задержки 5, причем первый квадратурный канал с выхода второго блока задержки 5 подключен ко входу умножителя 7 комплексных чисел непосредственно, а второй - через первый инвертор 6. Выход умножителя 7 комплексных чисел является входом блока 8 усреднения, выход которого подключен к входу блока 9 вычисления фазы, а также к входу блока 17 объединения. Выход блока 9 вычисления фазы подключен к второму входу вычитателя 11, к первому входу которого подключен выход элемента 10 задержки, вход которого является также выходом блока 9 вычисления фазы. Выход вычитателя 11 подключен к объединенным входам третьего 12 и четвертого 13 ключей, управляющие входы которых подключены к выходу блока 22 управления: третьего ключа - через второй элемент НЕ 14, а четвертого ключа - непосредственно. Кроме того, выход четвертого ключа является входом второго инвертора 15, выход которого подключен к входу пятого ключа 16, к которому также подключен выход третьего ключа. Управляющим входом пятого ключа является выход порогового устройства 18, первым входом которого является выход блока 17 объединения, а вторым входом - выход первого элемента памяти 19. Выход пятого ключа является первым входом перемножителя 20, вторым входом которого является выход второго элемента памяти 21, выход перемножителя является выходом обнаружителя-измерителя доплеровских сигналов.

Блоки 4(5) задержки (см.фиг.2) содержат первый 23 и второй 24 элементы задержки соответственно для сигналов первого и второго квадратурных каналов.

Умножитель 7 комплексных чисел (см.фиг.3) содержит два канала I,II, каждый из которых включает первый перемножитель 25 и последовательно включенные второй перемножитель 26 и сумматор 27, выход первого перемножителя 25 соединен с другим входом сумматора 27 другого канала, а первым, вторым, третьим и четвертым входами умножителя комплексных чисел соответственно являются объединенные между собой первые входы первого 25 и второго 26 перемножителей каждого канала, вторые входы вторых перемножителей, объединенные вторые входы первых перемножителей, а выходы умножителя комплексных чисел являются выходы сумматоров каналов. Следует иметь в виду, что в описании устройства в целом и его работы под выходом умножителя комплексных чисел подразумеваются оба выхода квадратурных каналов в совокупности, равно как и под первым и вторым входами.

Блок 8 усреднения (см.фиг.4) содержит два канала, каждый из которых состоит из N/2 - 1 элементов задержки 28 и N/2 - 1 сумматоров 29; входом каждого а канала служат объединенные вход 1-го элемента задержки и первый вход 1-го сумматора, выход k-го, k=1 (N/2-1) элемента задержки является входом (k+1)-го, k=1

(N/2-1) элемента задержки является входом (k+1)-го, k=1 (N/2-1) элемента задержки и одновременно вторым входом k-го, k=1

(N/2-1) элемента задержки и одновременно вторым входом k-го, k=1 (N/2-1) cумматора, выход k-го, k=1

(N/2-1) cумматора, выход k-го, k=1 (N/2-1) сумматора служит первым входом (k+1)-го, k= 1

(N/2-1) сумматора служит первым входом (k+1)-го, k= 1 (N/2-1) сумматора, выход последнего, (N/2-1)-го сумматора служит выходом каждого канала блока усреднения.

(N/2-1) сумматора, выход последнего, (N/2-1)-го сумматора служит выходом каждого канала блока усреднения.

Блок 9 вычисления фазы (см.фиг.5) состоит из последовательно включенных делителя 30, функционального преобразователя 31 арктангенса, модульного блока 32, вычитателя 33, блока 34 присвоения знака и первого ключа 35, причем первый вход делителя служит входом мнимой части комплексного числа, соответствующей синусной составляющей квадратурных каналов, а второй вход делителя - входом действительной части комплексного числа и объединен с вторыми входами первого 35 и второго 36 ключей; выход функционального преобразователя арктангенса также подключен к первому входу второго ключа; первый вход делителя подключен к второму входу блока присвоения знака; вторым входом вычитателя является выход элемента памяти 38; выходы первого и второго ключей являются входами сумматора 37, выход которого является выходом блока вычисления фазы.

Блок 17 объединения (см.фиг.6) включает два квадратора 39,40 и сумматоры 41, причем входами блока объединения являются входы квадраторов, выходы квадраторов являются входами сумматора, выход сумматора является выходом блока объединения.

Блок 22 управления (фиг.7) состоит из блока 42 задержки и триггера 43, причем входом блока управления являются объединенные вход блока задержки и второй вход триггера, выход блока задержки является первым входом триггера, а выход триггера является выходом блока управления.

Обнаружитель-измеритель доплеровских сигналов работает следующим образом.

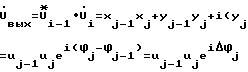

Последовательность квадратурных составляющих сумм сигнала и шума Uвх1, следующих с вобуляцией периода повторения (Т1, Т2), описываемых в одном элементе разрешения по дальности последовательностью комплексных величин: = xj+iyj= ujei(ϕj+ϕo), (1) где ϕj=ωд˙tj - доплеровский сдвиг фазы на момент прихода j-го импульса, поступает на коммутатор, состоящий из первого 1 и второго 2 ключей и элемента НЕ 3, управляющих сигналом Uвых22 с блока 22 управления. При нулевом управляющем сигнале открыт первый ключ 1, и сигнал проходит на входы второго блока 5 задержки напрямую. При единичном сигнале открыт второй ключ 2, и сигнал задерживается первым блоком 4 задержки на время ΔТ = (T2 - T1)/2. Таким образом, неэквидистантная последовательность квадратурных составляющих Uвх1 сигнала преобразуется в эквидистантную Uвх5 с периодом Тср = (T1 + T2)/2. Далее эта последовательность поступает на второй блок задержки 5 на время Тср, после чего составляющая, соответствующая мнимой части комплексного числа (синусной составляющей квадратурных каналов), дополнительно поступает на первый инвертор 3 с целью осуществления комплексного сопряжения. Далее в умножителе 7 комплексных чисел осуществляется обработка отсчетов в соответствии с алгоритмом:

= xj+iyj= ujei(ϕj+ϕo), (1) где ϕj=ωд˙tj - доплеровский сдвиг фазы на момент прихода j-го импульса, поступает на коммутатор, состоящий из первого 1 и второго 2 ключей и элемента НЕ 3, управляющих сигналом Uвых22 с блока 22 управления. При нулевом управляющем сигнале открыт первый ключ 1, и сигнал проходит на входы второго блока 5 задержки напрямую. При единичном сигнале открыт второй ключ 2, и сигнал задерживается первым блоком 4 задержки на время ΔТ = (T2 - T1)/2. Таким образом, неэквидистантная последовательность квадратурных составляющих Uвх1 сигнала преобразуется в эквидистантную Uвх5 с периодом Тср = (T1 + T2)/2. Далее эта последовательность поступает на второй блок задержки 5 на время Тср, после чего составляющая, соответствующая мнимой части комплексного числа (синусной составляющей квадратурных каналов), дополнительно поступает на первый инвертор 3 с целью осуществления комплексного сопряжения. Далее в умножителе 7 комплексных чисел осуществляется обработка отсчетов в соответствии с алгоритмом: xj-1-yj-1xj)= где - Δϕj= ϕj-ϕj-1= ωд(tj-tj-1)=

xj-1-yj-1xj)= где - Δϕj= ϕj-ϕj-1= ωд(tj-tj-1)=  -набег фазы за время между соседними отраженными импульсами.

-набег фазы за время между соседними отраженными импульсами.

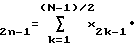

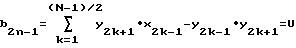

С выхода умножителя 7 комплексных чисел отсчеты Uвых7 поступают в блок 8 усреднения, осуществляющий с помощью двух каналов, каждый из которых содержит N/2-1 элементов 28 задержки на время 2Тcр = T1 + T2 и N/2-1 сумматоров 29, скользящее вдоль азимута череспериодное суммирование соответственно четных и нечетных отсчетов. На выходе блока 8 усреднения согласно описанному принципу работы образуются величины

a x2k+1+y2k-1·y2k+1=U cos

x2k+1+y2k-1·y2k+1=U cos  ,

,

, (3) а через период Тср величины

, (3) а через период Тср величины

,

,

, (4) где Δ ϕI2n-1=ωд T1,Δ ϕ2nI=ωд T2- усредненные доплеровские набеги фазы.

, (4) где Δ ϕI2n-1=ωд T1,Δ ϕ2nI=ωд T2- усредненные доплеровские набеги фазы.

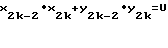

Величины аj и bj поступают на соответствующие входы блока 9 вычисления фазы (см. фиг.5), в котором с помощью делителя 30 и функционального преобразователя 31 арктангенса определяется оценка  =arctg(bj/aj), имеющая интервал однозначности [- π/2; π/2]. Последующие преобразования величины

=arctg(bj/aj), имеющая интервал однозначности [- π/2; π/2]. Последующие преобразования величины  с целью расширения этого интервала определяются знаком величины аj, пропорциональной косинусу исходного угла

с целью расширения этого интервала определяются знаком величины аj, пропорциональной косинусу исходного угла  . При aj ≥0 открыт второй ключ 36 и величина

. При aj ≥0 открыт второй ключ 36 и величина  через сумматор 37 непосредственно поступает на выход блока 9 вычисления фазы. При aj < 0 открыт первый ключ 35, а второй ключ 36 закрыт. При этом в модульном блоке 32 образуется

через сумматор 37 непосредственно поступает на выход блока 9 вычисления фазы. При aj < 0 открыт первый ключ 35, а второй ключ 36 закрыт. При этом в модульном блоке 32 образуется  , вычитываемый в вычитателе 33 из величины π, поступающей из элемента 38 памяти. Полученной разности в блоке 34 присваивается знак величины bj, пропорциональный синусу исходного угла. Рассмотренные операции позволяют расширить диапазон однозначного измерения до интервала [- π; π], т.е. получить на выходе сумматора 37 оценку усредненного по N отсчетам доплеровского сдвига фазы помехи в виде

, вычитываемый в вычитателе 33 из величины π, поступающей из элемента 38 памяти. Полученной разности в блоке 34 присваивается знак величины bj, пропорциональный синусу исходного угла. Рассмотренные операции позволяют расширить диапазон однозначного измерения до интервала [- π; π], т.е. получить на выходе сумматора 37 оценку усредненного по N отсчетам доплеровского сдвига фазы помехи в виде

при

при На выходе блока 9 вычисления фазы образуются величины

На выходе блока 9 вычисления фазы образуются величины  =ωдT1 и следующие через период Тср величины

=ωдT1 и следующие через период Тср величины  = ωдT2 .

= ωдT2 .

Проходя через элемент 10 задержки, величина  (а через период

(а через период  ) вычитается в блоке 11 вычитания из следующей за ней величины

) вычитается в блоке 11 вычитания из следующей за ней величины  (через период -

(через период - ); получаемая величина Uвых11

); получаемая величина Uвых11 =

= -

- (через период -

(через период -  =

= -

- поступает на коммутатор, состоящий из третьего 12 и четвертого 13 ключей и элемента НЕ 14. При нулевом выходном сигнале блока 22 управления Uвых22 открыт третий ключ 12, и величины

поступает на коммутатор, состоящий из третьего 12 и четвертого 13 ключей и элемента НЕ 14. При нулевом выходном сигнале блока 22 управления Uвых22 открыт третий ключ 12, и величины  =

= -

- проходит на вход пятого ключа 16 напрямую, при этом четвертый ключ 13 закрыт. При единичном сигнале блока 22 управления третий ключ 12 закрыт, а четвертый ключ 13 открыт, и величина

проходит на вход пятого ключа 16 напрямую, при этом четвертый ключ 13 закрыт. При единичном сигнале блока 22 управления третий ключ 12 закрыт, а четвертый ключ 13 открыт, и величина  =

= -

- инвертируется вторым инвертором 15 и также поступает на пятый ключ 16.

инвертируется вторым инвертором 15 и также поступает на пятый ключ 16.

С целью исключения возможной работы устройства по шумам в него введена схема обнаружения, блокирующая выдачу оценки на выход в отсутствие отраженного сигнала. С выходов блока 8 усреднения величины и поступают на вход блока 17 объединения, где в соответствии с его структурой вычисляется квадрат модуля входной величины U = aj2 + bj2. Если происходит превышение этой величины над величиной порога Uпор, заложенной в элементе 19 памяти, то с выхода порогового устройства 18 поступает сигнал разрешения прохождения результата вычисления  через пятый ключ 16. В противном случае ключ 16 разомкнут, на выходе перемножителя 20 имеем сигнал Uвых16.

через пятый ключ 16. В противном случае ключ 16 разомкнут, на выходе перемножителя 20 имеем сигнал Uвых16.

Величина  , пройдя через ключ 16, умножается на величину K = c/[4πfo(T2 - T1)], где с - скорость света; fo - несущая частота излучаемых радиоимпульсов, записанная в элементе 21 памяти. На выходе перемножителя 20 образуется величина, пропорциональная скорости цели.

, пройдя через ключ 16, умножается на величину K = c/[4πfo(T2 - T1)], где с - скорость света; fo - несущая частота излучаемых радиоимпульсов, записанная в элементе 21 памяти. На выходе перемножителя 20 образуется величина, пропорциональная скорости цели.

На вход блока 22 управления (см.фиг.7) поступают импульсы синхронизатора передатчика с периодом повторения 2Тср и сбрасывает триггер 43 в нулевое состояние; этот же сигнал, задержанный в элементе 42 задержки на время Тср, устанавливает на выходе триггера 43 единицу. Вырабатываемые триггером 43 сигналы управляют работой первого 1, второго 2, третьего 12 и четвертого 13 ключей.

Эффективность предложенного обнаружителя-измерителя доплеровских сигналов заключается в увеличении точности за счет усреднения и расширения пределов линейного измерения скорости за счет введения сигналов с вобуляцией периода повторения.

Например, при использовании обычного периодического зондирующего сигнала для обнаружения на максимальной дальности Rmax = 200 км период повторения должен быть не менее Т = 2Rmax/c = 1333 мкс, при этом однозначно измеряемая скорость vrmax (т.е. удовлетворяющая неравенству ωдТ = (4πvrmax/ λ)T< π) для длины волны λ= 10 см определяется vrmax = λ/4T = =18,75 м/с.

При введении вобуляции периода повторения зондирующего сигнала появляется возможность расширения пределов однозначного измерения; например, для измерения скорости vrmax = 2М = 660 м/с при длине волны λ= 10 см величина вобуляции может быть рассчитана как

ΔT = λ/4vrmax = 0,1/4x660 = 37,9 мкс

Таким образом, при одинаковой однозначно измеряемой дальности Rmax=200 км интервал однозначно измеряемой скорости при вобуляции периода повторения на λ= =10 см с параметрами Т1 = 1333 мкс, Т2 = =1371 мкс расширяется в ΔТ/Т раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АДАПТИВНОГО ПОДАВЛЕНИЯ ПОМЕХ | 1990 |

|

SU1802616A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Фазометр доплеровского набега фазы радиоимпульсных сигналов | 1990 |

|

SU1748086A1 |

| УСТРОЙСТВО АДАПТИВНОЙ РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 1981 |

|

SU1098399A1 |

| ОБНАРУЖИТЕЛЬ-ИЗМЕРИТЕЛЬ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2000 |

|

RU2166772C1 |

| ОБНАРУЖИТЕЛЬ-ИЗМЕРИТЕЛЬ КОГЕРЕНТНО-ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ | 2015 |

|

RU2600111C1 |

| ОБНАРУЖИТЕЛЬ-ИЗМЕРИТЕЛЬ РАДИОИМПУЛЬСНЫХ СИГНАЛОВ | 2014 |

|

RU2546988C1 |

| ОБНАРУЖИТЕЛЬ-ИЗМЕРИТЕЛЬ КОГЕРЕНТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 2012 |

|

RU2507536C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ-ИЗМЕРЕНИЯ РАДИОИМПУЛЬСНЫХ СИГНАЛОВ | 2014 |

|

RU2560130C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1982 |

|

SU1090136A1 |

Сущность изобретения: обнаружитель-измеритель содержит пять ключей 1, 2, 12, 13, 16, два элемента НЕ 3, 14, два блока задержки 4, 5, два инвертора 6, 15, умножитель комплексных чисел 7, блок усреднения 8, блок вычисления фазы 9, элемент задержки 10, вычитатель 11, блок объединения 17, пороговый блок 18, два элемента памяти 19, 21, перемножитель 20, блок управления 22. 22 - 3 - 1 - 5 - 6 - 7 - 8 - 9 - 10 - 11 - 12 - 16 - 20; 8 - 17 - 18 - 16; 22 - 14 - 12; 22 - 13 - 15 - 16; 9 - 11; 1 - 2 - 4 - 5 - 7; 4 - 7; 22 - 2; 21 - 20; 19 - 18. 4 з.п. ф-лы, 8 ил.

| Способ приготовления сернистого красителя защитного цвета | 1915 |

|

SU63A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-07-30—Публикация

1991-07-01—Подача