Изобретение относится к области радиолокации и предназначено для обнаружения многочастотных радиоимпульсных периодических сигналов и измерения радиальной скорости объекта; может быть использовано в радиолокационных системах распознавания, а также радиолокационных станциях управления воздушным движением для обнаружения и измерения скорости летательных аппаратов.

Известен фильтровой не следящий многоканальный измеритель [1], каждый канал которого содержит последовательно соединенные согласованный фильтр и детектор, выходы каналов объединены решающим устройством. Однако это устройство обладает невысокой эффективностью обнаружения и точностью измерения, а также сложностью реализации многоканальной обработки.

Известно также радиолокационное устройство для обнаружения движущейся цели [2] , содержащее последовательно включенные блоки задержки, умножитель комплексных чисел и вычитатель. Однако это устройство обладает низкой точностью и неоднозначностью измерения.

Наиболее близким к изобретению является обнаружитель-измеритель доплеровских сигналов [3], выбранный в качестве прототипа, содержащий блок задержки, выходы которого соединены со входами блока комплексного сопряжения (на основе инвертора), выходы которого соединены с первыми входами блока комплексного умножения, вторые входы которого объединены со входами блока задержки, являющимися входами обнаружителя-измерителя, выходы блока комплексного умножения соединены со входами блока усреднения, выходы которого соединены со входами блока вычисления модуля и входами блока вычисления фазы, выход блока вычисления модуля соединен со вторым входом порогового блока, первый вход которого соединен со вторым блоком памяти, управляющий вход ключа соединен с выходом порогового блока, являющегося первым выходом обнаружителя-измерителя, вторым выходом которого является выход блока умножения, первый и второй входы которого соответственно соединены с выходом первого блока памяти и выходом ключа. Однако данное устройство обладает невысокой эффективностью обнаружения и точностью измерения за счет наличия большого числа функциональных преобразований, связанных с обработкой сигнала, использующего вобуляцию периода повторения.

Задачей, решаемой в изобретении, является повышение эффективности обнаружения и точности измерения за счет меньшего числа функциональных преобразований при применении совместной обработки многочастотного сигнала.

Для решения поставленной задачи в обнаружитель-измеритель многочастотных сигналов, содержащий I-й канал, блок вычисления фазы, блок умножения, первый блок памяти, пороговый блок, второй блок памяти, ключ и синхрогенератор, причем I-й канал состоит из блока задержки, блока комплексного сопряжения, блока комплексного умножения, блока усреднения, блока вычисления модуля, введены дополнительно II-й канал, дополнительный блок комплексного сопряжения, дополнительный блок комплексного умножения, дополнительный сумматор, причем II-й канал состоит из блока задержки, блока комплексного сопряжения, блока комплексного умножения, блока усреднения, блока вычисления модуля, помимо этого в I-й канал дополнительно введены два блока деления, два блока умножения и сумматор, во II-й канал дополнительно введены два блока деления, два блока умножения и сумматор.

Дополнительные блоки, введенные в предлагаемое устройство, являются известными. Так, соединенные вместе блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения и блок вычисления модуля, составляющие и I-й и II-й каналы, совместно с пороговым блоком образуют инвариантную систему обработки радиосигналов и применяются для их обнаружения. Однако неизвестно совместное применение I-го и II-го каналов, объединенных дополнительным сумматором, также неизвестно применение в I-м и во II-м канале дополнительно введенных блоков деления, умножения и сумматора, обеспечивающих в каждом канале адаптивную к доплеровской фазе сигнала обработку входных отсчетов сигнала, что обеспечивает повышение эффективности обнаружения. Неизвестным также является применение схемы объединения частотных каналов на основе дополнительных блоков комплексного сопряжения и умножения, кроме того наличие новых связей между блоками обеспечивает повышение точности измерения за счет меньшего числа функциональных преобразований при применении совместной обработки многочастотного сигнала. Связи между синхрогенератором и всеми блоками доплеровского фазометра многочастотных сигналов обеспечивают согласованную обработку многочастотной последовательности радиоимпульсов.

Сравнение с техническими характеристиками, известными из опубликованных источников информации, показывает, что заявляемое решение обладает новизной и имеет изобретательский уровень.

Заявляемое решение носит технический характер, осуществимо, воспроизводимо и, следовательно, является промышленно применимым.

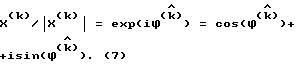

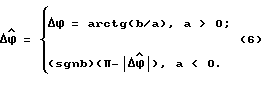

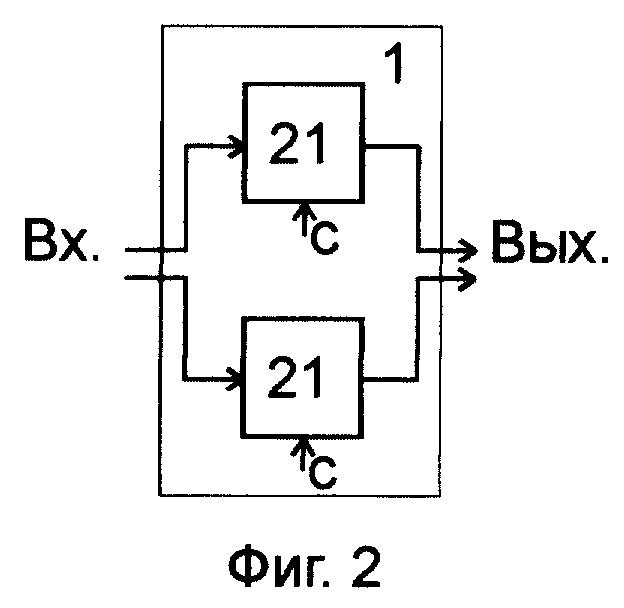

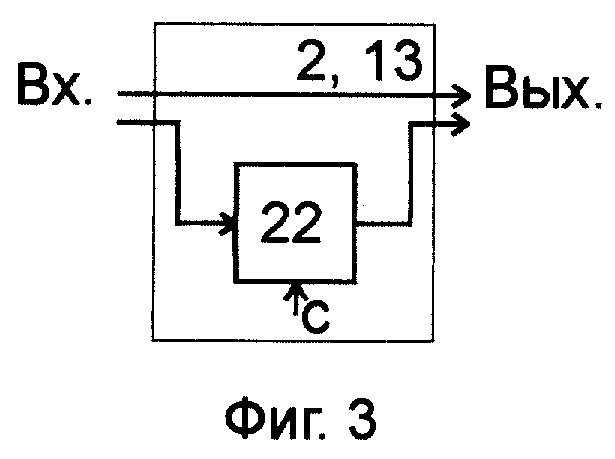

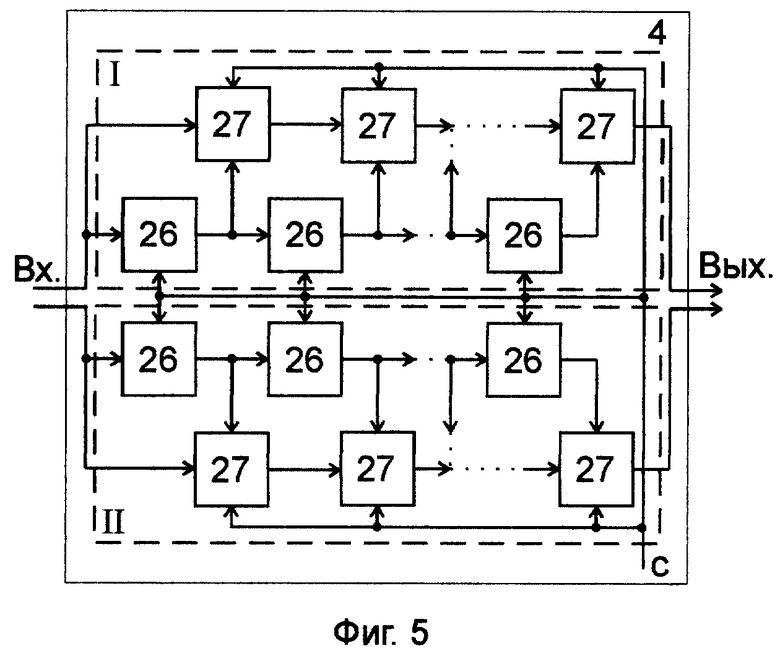

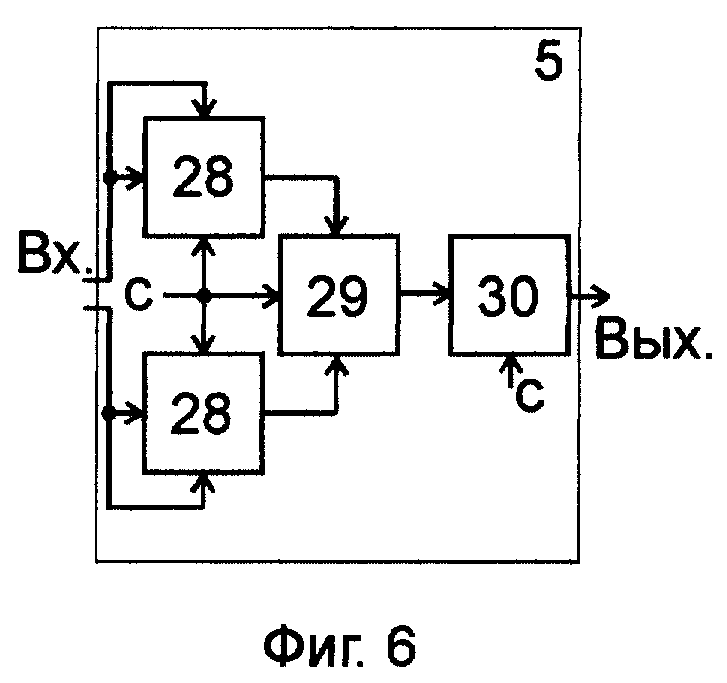

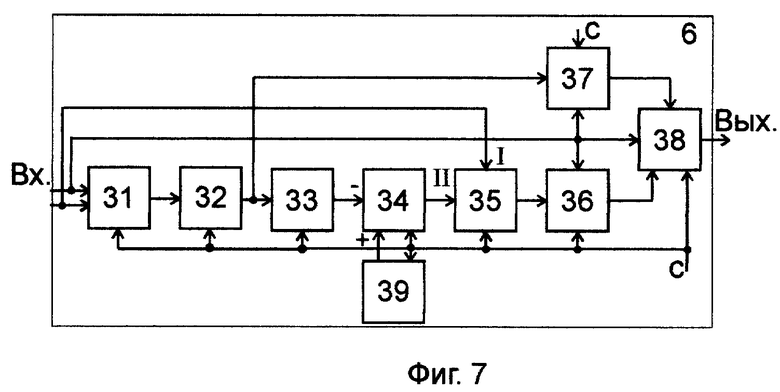

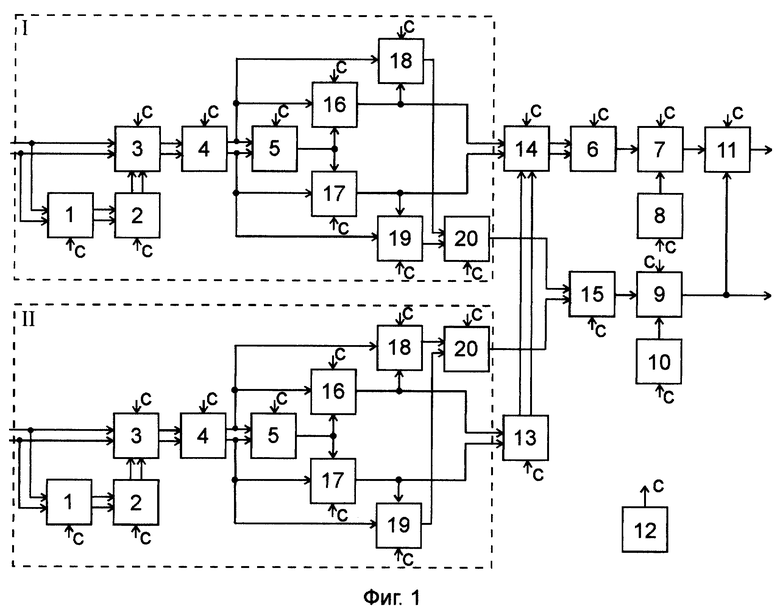

На фиг. 1 представлена структурная электрическая схема обнаружителя-измерителя многочастотных сигналов; на фиг.2 - блока задержки; на фиг.3 - блока комплексного сопряжения; на фиг.4 - блока комплексного умножения; на фиг. 5 - блока усреднения; на фиг.6 - блока вычисления модуля; на фиг. 7 - блока вычисления фазы; на фиг. 8 - блока присвоения знака; на фиг. 9 изображены характеристики обнаружения прототипа и предложенного устройства.

Обнаружитель-измеритель многочастотных сигналов содержит два канала (I, II), каждый из которых включает блок 1 задержки, блок 2 комплексного сопряжения, блок 3 комплексного умножения, блок 4 усреднения, блок 5 вычисления модуля, при этом выходы блока 1 задержки соединены со входами блока 2 комплексного сопряжения, выходы которого соединены с первыми входами блока 3 комплексного умножения, выходы которого соединены со входами блока 4 усреднения, выходы которого соединены со входами блока 5 вычисления модуля, входами I-го канала и II-го канала являются объединенные между собой одноименные входы блока 1 задержки и вторые входы блока 3 комплексного умножения соответствующих каналов, блок 6 вычисления фазы, блок 7 умножения, первый блок 8 памяти, пороговый блок 9, второй блок 10 памяти, ключ 11, синхрогенератор 12, дополнительный блок 13 комплексного сопряжения, дополнительный блок 14 комплексного умножения, дополнительный сумматор 15, выход первого блока 8 памяти соединен с первым входом блока 7 умножения, выход которого соединен со входом ключа 11, управляющий вход которого соединен с выходом порогового блока 9, первый вход которого соединен с выходом второго блока 10 памяти, выходы дополнительного блока 13 комплексного сопряжения соединены с первыми входами дополнительного блока 14 комплексного умножения, выходы которого соединены со входами блока 6 вычисления фазы, выход которого соединен со вторым входом блока 7 умножения, выход дополнительного сумматора 15 соединен со вторым входом порогового блока 9, кроме того, I-й и II-й каналы дополнительно содержат два блока 16, 17 деления, два блока 18, 19 умножения и сумматор 20, при этом выход блока 5 вычисления модуля соединен с первыми входами блоков 16, 17 деления, выходы блока 5 усреднения соединены с объединенными между собой одноименными вторыми входами блоков 16, 17 деления и 18, 19 умножения, выходы блоков 18, 19 умножения соединены со входами сумматора 20, первым выходом I-го канала является выход сумматора 20 I-го канала, первым выходом II-го канала является выход сумматора 20 II-го канала, выходы блоков 16, 17 деления I-го канала соответственно соединены с первыми входами блоков 18,19 умножения I-го канала и являются его вторыми выходами, выходы блоков 16, 17 деления II-го канала соответственно соединены с первыми входами блоков 18, 19 умножения II-го канала и являются его вторыми выходами, первый выход I-го и первый выход II-го канала соединены со входами дополнительного сумматора 15, вторые выходы I-го канала соединены со вторыми входами дополнительного блока 14 комплексного умножения, вторые выходы II-го канала соединены со входами дополнительного блока 13 комплексного сопряжения, выход синхрогенератора 12 соединен с синхровходами всех блоков обнаружителя-измерителя многочастотных сигналов, первыми и вторыми входами которого являются соответственно входы I-го и II-го каналов, а первым и вторым выходами - соответственно выходы порогового блока 9 и ключа 11.

Блоки 1 задержки I-го и II-го каналов содержат две линии задержки 21 на интервал Т, входами блоков задержки являются входы линии задержки 21, выходы которых являются выходами блоков задержки.

Блоки 2 комплексного сопряжения I-го, II-го каналов и дополнительный блок 13 комплексного сопряжения содержат инвертор 22, первый вход блока комплексного сопряжения является его первым выходом, вторым входом является вход инвертора 22, выход которого является вторым выходом блока комплексного сопряжения.

Блоки 3 комплексного умножения I-го, II-го каналов и дополнительный блок 14 комплексного умножения содержат два канала (I, II), каждый из которых включает первый перемножитель 23, последовательно включенные второй перемножитель 24 и сумматор 25, выход первого перемножителя 23 одного канала соединен со вторым входом сумматора 25 другого канала, а первыми и вторыми входами блока комплексного умножения соответственно являются объединенные между собой первые входы первого и второго перемножителей 23, 24 каждого из каналов, объединенные вторые входы вторых перемножителей 24 и объединенные вторые входы первых перемножителей 23, а выходами блока комплексного умножения являются выходы сумматоров 25 каналов.

Блоки 4 усреднения I-го и II-го каналов содержат два канала (I, II), каждый из которых состоит из N-1 последовательно включенных линий задержки 26 на интервал Т и N-1 сумматоров 27, входами блока усреднения являются объединенные входы первой линии задержки 26 и первого сумматора 27 каждого канала (I, II), а выход К-й (K=2,(N-l)) линии задержки 26 соединен со вторым входом K-го (K=2,(N-1)) сумматора 27 каждого канала (I, II), выходами блока усреднения служат выходы (N-1)-го сумматора.

Блоки 5 вычисления модуля I-го и II-го каналов содержат два блока 28 умножения, сумматор 29 и блок 30 извлечения квадратного корня, входами блока вычисления модуля являются входы блоков 28 умножения, выходы которых соединены с первым и вторым входами сумматора 29, выход которого соединен со входом блока 30 извлечения квадратного корня, выход которого является выходом блока вычисления модуля.

Блок 6 вычисления фазы состоит из последовательно включенных делителя 31, функционального преобразователя 32, модульного блока 33, сумматора 34, блока 35 присвоения знака и первого ключа 36, выход функционального преобразователя 32 соединен со входом второго ключа 37, второй вход сумматора 34 соединен с выходом блока 39 памяти, управляющие входы первого и второго ключей 36,37 соединены со входом делителя 31, соответствующим входу действительной части комплексного числа, первый вход блока 35 присвоения знака соединен со входом делителя 31, соответствующим входу мнимой части комплексного числа, выходы первого и второго ключей 36,37 соединены со входами сумматора 37, выход которого является выходом блока вычисления фазы, входами которого являются входы делителя 31.

Блок 35 присвоения знака содержит блоки 40, 43 умножения, блок 41 памяти и ограничитель 42, причем первый вход блока присвоения знака является первым входом блока 40 умножения, второй вход которого соединен с выходом блока 41 памяти, выход блока 40 умножения соединен со входом ограничителя 42, выход которого соединен с первым входом блока 43 умножения, второй вход которого является вторым входом блока присвоения знака, выходом блока присвоения знака служит выход блока 43 умножения.

Доплеровский фазометр многочастотных сигналов работает следующим образом.

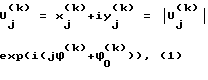

Многочастотный сигнал, состоящий из двух частотных компонент, поступает на вход каждого частотного канала приемника, где последовательно проходит каскады усиления, преобразуется в квадратурных фазовых детекторах на видеочастоту и через аналого- цифровые преобразователи (перечисленные блоки на фиг. 1 не показаны) поступает на входы заявляемого устройства. При этом квадратурные составляющие сигнала в каждом частотном канале описываются в одном элементе разрешения по дальности последовательностью комплексных величин

где U(k)j - j-й отсчет последовательности комплексных величин в k-м частотном канале;

x(k)j и y(k)j - соответственно действительная и мнимая части комплексного отсчета;

k - номер частотного канала, причем k = 1,2;

Φ

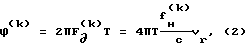

Φ(k) - доплеровские сдвиги фаз сигнала за период повторения Т в k-м частотном канале, равный

где F

Т - период повторения импульсов;

f(k)н - k-я несущая частота, причем f(1)н больше fн(2);

vr - радиальная скорость цели.

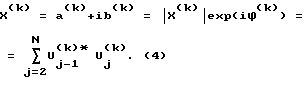

Отсчеты U(1)j и U(2)j поступают соответственно на входы I-го и II-го канала (фиг. 1), где в блоках 1 задержки (фиг. 2) задерживаются на период повторения Т. После этого в блоках 2 комплексного сопряжения (фиг. 3) осуществляется комплексное сопряжение задержанного отсчета. Далее в блоках 3 комплексного умножения (фиг. 4) осуществляется обработка отсчетов в соответствии с алгоритмом

С выходов блоков 3 комплексного умножения отсчеты поступают в блоки 4 усреднения (фиг. 5), осуществляющие с помощью элементов 26 задержки и сумматоров 27 скользящее вдоль азимута суммирование, что приводит к образованию на выходах блоков 4 усреднения величин:

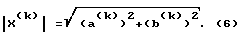

Далее величины a(k) и b(k) поступают на входы блоков 5 вычисления модуля (фиг. 6), где в соответствии с его структурой вычисляется модуль входной величины X(k)

Величины  и X(k) в соответствующих каналах поступают соответственно на первый и второй входы блоков 16, 17 деления, на основе которых вычисляется величина, равная:

и X(k) в соответствующих каналах поступают соответственно на первый и второй входы блоков 16, 17 деления, на основе которых вычисляется величина, равная:

Оценки exp(iΦ(k)) и величины X(k) поступают соответственно на первый и второй входы блоков 18, 19 умножения I-го и II-го канала, результаты вычисления с выхода этих блоков поступают на входы сумматора 20. На основе блоков 18, 19 умножения и сумматора 20 I-го канала, блоков 18,19 умножения и сумматора 20 II-го канала при условии, что оценка exp(iΦ(k)) равна истинному значению exp(iΦ(k)), реализуется алгоритм:

Отсчеты z(1) и z2 (выражение 8) с первых выходов I-го и II-го канала поступают на входы дополнительного сумматора 15, с выхода которого величина, равная

z=z(1)+z(2)≥z0, (9)

поступает на второй вход порогового блока 9. Если происходит превышение над величиной порога zo, записанной во втором блоке 10 памяти, то с выхода порогового блока 9, который является первым выходом обнаружителя-измерителя многочастотных сигналов, поступает сигнал, используемый для отсчета других координат, например дальности.

Оценка exp(iΦ(1)) непосредственно, а оценка exp(iΦ(2)) через дополнительный блок 13 комплексного сопряжения (фиг. 3) поступают соответственно на вторые и первые входы дополнительного блока 14 комплексного умножения (фиг. 4), на выходе которого образуется величина, равная:

exp(iΔΦ) = a+ib = exp(i(Φ(1)-Φ(2))). (10)

Величины a и b поступают на соответствующие входы блока 6 вычисления фазы (фиг. 7), где на основе блока 31 деления и функционального преобразователя 32 вычисляется оценка ΔΦ = arctg(b/a). Последующие преобразования величины ΔΦ зависят от знака а. При а ≥ 0 открыт второй ключ 37 и величина через сумматор 38 непосредственно поступает на выход блока 6 вычисления фазы. При а < 0 открыт первый ключ 36, а второй ключ 37 закрыт. При этом в модульном блоке 28 образуется  вычитаемый в блоке 34 из величины π, поступающей от блока 39 памяти. Полученной разности в блоке 35 присваивается знак величины b.

вычитаемый в блоке 34 из величины π, поступающей от блока 39 памяти. Полученной разности в блоке 35 присваивается знак величины b.

Блок 35 присвоения знака (фиг.8) работает следующим образом. На первый вход блока присвоения знака поступает величина b (соотношение (10)), где в блоке 40 умножения производится ее умножение на постоянный множитель из блока 41 памяти с целью масштабирования и дальнейшего ограничения в ограничителе 42 по уровню ±1. Таким образом, после ограничения величина на выходе ограничителя 42 имеет смысл знака величины b, который, поступая на первый вход блока 43 умножения, присваивается разности  поступающей на второй вход блока 35 присвоения знака, то есть на второй вход блока 43 умножения с выхода сумматора 34.

поступающей на второй вход блока 35 присвоения знака, то есть на второй вход блока 43 умножения с выхода сумматора 34.

Рассмотренные операции позволяют в блоке 6 вычисления фазы сначала найти оценку разности фаз, находящуюся в пределах [-π/2, π/2], а затем при помощи преобразований расширить пределы ее однозначного измерения [-π, π], в соответствии с алгоритмом:

Блок 7 умножения (фиг. 1) осуществляет умножение найденной оценки разности фаз на коэффициент d, хранящейся в первом блоке 8 памяти, что позволяет найти однозначную оценку радиальной скорости в соответствии с алгоритмом:

Таким образом, соответствующим выбором разноса несущих частот обеспечивается необходимый диапазон однозначно измеряемых доплеровских скоростей, который расширяется по сравнению с одночастотным сигналом в fн/(f(1)н=f(2)н) раз. При этом сохраняется однозначность измерения дальности, которая обеспечивается соответствующим выбором периода повторения импульсов Т.

Для уменьшения вероятности работы устройства по шумам в нем исключается выдача полученной оценки на выход в отсутствии отраженного от цели сигнала. Если происходит превышение над величиной порога 20, то с выхода порогового блока 9 поступает сигнал разрешения прохождения результата вычисления с выхода блока 7 умножения через ключ 11 на второй выход обнаружителя-измерителя многочастотных сигналов. В противном случае ключ 15 разомкнут.

Синхронизация обнаружителя-измерителя многочастотных сигналов осуществляется подачей на все блоки заявляемого устройства последовательности синхронизирующих импульсов, вырабатываемых синхрогенератором 12 (фиг. 1), с периодом повторения tk, определяемым из условия обеспечения требуемой разрешающей способности по дальности.

На фиг. 9 изображены зависимости характеристик обнаружения D предложенного устройства (кривая 1) и прототипа (кривая 2) от отношения сигнал/шум на входе устройства. Характеристики получены методом статистического моделирования на ЭВМ при условии равных мощностей одночастотного и многочастотного сигналов, т.е. q(1)=q(2)=q/2, где q отношения сигнал/шум для одночастотного сигнала. Сравнение характеристик обнаружения D проводилось для случая медленных флюктуаций сигнала, вероятности ложной тревоги F=10-3, количества импульсов в пачке N= 20. Как видно, предложенное устройство по уровню 0.9 выигрывает у прототипа 4 дБ.

Таким образом обнаружитель-измеритель многочастотных сигналов позволяет повысить эффективность обнаружения без увеличения энергии сигнала и точность измерения за счет меньшего числа функциональных преобразований.

Библиография:

1. Ширман Я.Д. и Манжос В.Н. Теория и техника обработки радиолокационной информации на фоне помех. Москва. Радио и связь. - 1981. - 204 с. - Рис. 14.2.

2. Патент N 63-49193 (Япония), МКИ G 01 S 13/52. Радиолокационное устройство для обнаружения движущейся цели / К.К. Тосиба. Опубл. 03.10.1988 - Изобретения стран мира - 1989. - выпуск 109. - N 15. - 52 с.

3. Патент N 2017167 (Россия), МКИ G 01 S 13/58. Обнаружитель-измеритель доплеровских сигналов / Д. И. Попов, С.В. Герасимов и Е.Н. Матаев. Опубл. 30.07.1994 - Изобретения - 1994. - N 14. - 121 с. Ыд

Изобретение относится к области радиолокации и предназначено для обнаружения многочастотных радиоимпульсных периодических сигналов и измерения радиальной скорости объекта; может быть использовано в радиолокационных системах распознавания, а также радиолокационных станциях управления воздушным движением для обнаружения и измерения скорости летательных аппаратов. Обнаружитель-измеритель многочастотных сигналов содержит два частотных канала, осуществляющих на основе блоков задержки, комплексного сопряжения, комплексного умножения, усреднения, вычисления модуля, а также двух блоков деления, двух блоков умножения и сумматора обработки исходных отсчетов, схему вычисления оценки доплеровской скорости на основе последовательно соединенных блоков вычисления фазы и блока умножения и две схемы объединения частотных каналов на основе дополнительного сумматора и дополнительного блока комплексного умножения совместно с блоком комплексного сопряжения. Применение обнаружителя-измерителя многочастотных сигналов позволяет повысить эффективность обнаружения и точность измерения за счет меньшего числа функциональных преобразований, что и является достигаемым техническим результатом. 9 ил.

Обнаружитель-измеритель многочастотных сигналов, содержащий первый канал, блок вычисления фазы, блок умножения, первый блок памяти, пороговый блок, второй блок памяти, ключ и синхрогенератор, причем первый канал состоит из блока задержки, блока комплексного сопряжения, блока комплексного умножения, блока усреднения, блока вычисления модуля, при этом выходы блока задержки соединены с входами блока комплексного сопряжения, выходы которого соединены с первыми входами блока комплексного умножения, выходы которого соединены с входами блока усреднения, выходы которого соединены с входами блока вычисления модуля, входами первого канала являются объединенные между собой входы блока задержки и вторые входы блока комплексного умножения, выход первого блока памяти соединен с первым входом блока умножения, выход которого соединен с входом ключа, управляющий вход которого соединен с выходом порогового блока, первый вход которого соединен с выходом второго блока памяти, выход синхрогенератора соединен с синхровходами блока задержки первого канала, блока комплексного сопряжения первого канала, блока комплексного умножения первого канала, блока усреднения первого канала, блока вычисления модуля первого канала, блока вычисления фазы, блока умножения, первого и второго блоков памяти, порогового блока, и ключа, отличающийся тем, что введены дополнительно второй канал, дополнительный блок комплексного сопряжения, дополнительный блок комплексного умножения, дополнительный сумматор, причем в первый и второй каналы дополнительно введены по два блока деления, по два блока умножения и сумматор, второй канал состоит из блока задержки, блока комплексного сопряжения, блока комплексного умножения, блока усреднения, блока вычисления модуля, при этом выходы блока задержки соединены с входами блока комплексного сопряжения, выходы которого соединены с первыми входами блока комплексного умножения, выходы которого соединены с входами блока усреднения, выходы которого соединены с входами блока вычисления модуля, входами второго канала являются объединенные между собой входы блока задержки и вторые входы блока комплексного умножения, выходы дополнительного блока комплексного сопряжения соединены с первыми входами дополнительного блока комплексного умножения, выходы которого соединены с входами блока вычисления фазы, выход которого соединен со вторым входом блока умножения, выход дополнительного сумматора соединен со вторым входом порогового блока, выход блока вычисления модуля первого канала соединен с первыми входами блоков деления первого канала, выход блока вычисления модуля второго канала соединен с первыми входами блоков деления второго канала, выходы блока усреднения первого канала соединены с объединенными между собой вторыми входами блоков деления и умножения второго канала, выходы блока усреднения второго канала соединены с объединенными между собой вторыми входами блоков деления и умножения второго канала, выходы блоков умножения первого канала соединены с входами сумматора первого канала, выход которого является первым выходом первого канала, выходы блоков умножения второго канала соединены с входами сумматора второго канала, выход которого является первым выходом второго канала, выходы блоков деления первого канала соединены с первыми входами блоков умножения первого канала и являются его вторыми выходами, выходы блоков деления второго канала соединены с первыми входами блоков умножения второго канала и являются его вторыми выходами, первый выход первого канала и первый выход второго канала соединены с входами дополнительного сумматора, вторые выходы первого канала соединены со вторыми входами дополнительного блока комплексного умножения, вторые выходы второго канала соединены с входами дополнительного блока комплексного сопряжения, выход синхрогенератора соединен с синхровходами блока задержки второго канала, блока комплексного сопряжения второго канала, блока комплексного умножения второго канала, блока усреднения второго канала, блока вычисления модуля второго канала, дополнительного блока комплексного сопряжения, дополнительного блока комплексного умножения, дополнительного сумматора, двух блоков деления первого канала, двух блоков деления второго канала, двух блоков умножения первого канала и сумматора первого канала, двух блоков умножения второго канала и сумматора второго канала, причем первыми и вторыми входами обнаружителя-измерителя многочастотных сигналов являются соответственно входы первого и второго каналов, а первым и вторым выходами - соответственно выходы порогового блока и ключа.

| ОБНАРУЖИТЕЛЬ-ИЗМЕРИТЕЛЬ ДОПЛЕРОВСКИХ СИГНАЛОВ | 1991 |

|

RU2017167C1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ ОБЪЕКТА | 1997 |

|

RU2126544C1 |

| US 5579011 A, 26.11.1996 | |||

| DE 3800024 А1, 14.07.1988. | |||

Авторы

Даты

2001-05-10—Публикация

2000-03-06—Подача