Изобретение относится к технической диагностике и может быть использовано в производстве РЗА для отбраковки ненадежных микросхем.

Известен способ отбраковки ИС, который может быть использован для прогнозирования отказов, сводящийся к измерению длительности переходного процесса ИС и сравнению измеренной величины с ее эталонным значением. Потенциально ненадежными приборами признаются те, у которых длительность переходного процесса превосходит эталонную величину.

Однако длительность переходного процесса является не столько характеристикой надежности, сколько характеристикой быстродействия, связанной с надежностью очень опосредованно, т.е. с невысокой достоверностью.

Наиболее близким к предлагаемому решению является способ отбраковки микросхем памяти, заключающийся в том, что на микросхему подают электрические импульсы, соответствующие определенной тестовой последовательности, контролируют ее работоспособность, плавно снижая напряжение питания фиксируют два его критических значения: при котором отказывает одна ячейка памяти и заранее заданное количество ячеек памяти. Разница между этими двумя критическими значениями напряжения питания, фактически отражающая однородность свойств материалов по площади кристалла, косвенно характеризует надежность микросхемы.

Однако эта разница, характеризуя однородность свойств материалов по площади кристалла, не всегда характеризует потенциальную надежность ИС, тем более для ИС с неоднородной структурой.

Более достоверно характеризуют надежность ИС ее термодинамические свойства, имеющие универсальный характер и обеспечивающие интегральную оценку надежности объекта контроля.

Цель изобретения - повышение достоверности контроля надежности ИС.

Сущность предлагаемого способа заключается в измерении одной из термодинамических характеристик, а именно площади петли гистерезиса зависимости критического напряжения ИС от температуры кристалла при термоциклировании. Величина площади тем более информативна (т.е. более достоверно характеризует надежность), чем шире диапазон изменения температур и выше скорость измерения температуры. Повышенная в сравнении с прототипом достоверность способа объясняется следующим:

Площадь петли гистерезиса является интегральным диагностическим параметром, а как известно в реакции интегральных термодинамических параметров на внешнее воздействие проявляются и отдельные локальные процессы. По отношению к параметру, используемому в прототипе, площадь петли гистерезиса является интегральной характеристикой внутренней физической структуры ИС.

Таким образом, цель достигается тем, что в способе, включающем циклическую подачу на входы объекта контроля тестовых последовательностей, сравнение реакции ИС с эталонной и определение критических напряжений путем изменения напряжения питания сверх рабочего диапазона, согласно изобретению, охлаждают ИС, затем нагревают, снимая при этом температурную зависимость критических напряжений при положительном термоударе, вновь охлаждают ИС до минимальной температуры, снимая температурную зависимость критических напряжений при отрицательном термоударе, вычисляют площадь петли гистерезиса полученной зависимости и отбирают как высоконадежные ИС с площадью петли гистерезиса, меньшей заранее определенного порога.

Диапазон изменения температур выбирают, исходя из необходимости неразрушающего действия испытаний на объект контроля. Для достижения максимальной скорости изменения температуры рекомендуется при термоциклировании переносить ИС из одной термокамеры в другую. В термокамерах заранее устанавливаются необходимые для испытаний температуры.

Как показали проведенные исследования, благодаря осуществлению дополнительных к прототипу действий, а именно термоциклированию и определению, что зависимость критических напряжений от изменяющейся во времени внутренней температуры кристалла имеет вид петли гистерезиса, предлагаемый способ позволяет осуществить диагностику схем на более ранней стадии, чем повышается достоверность контроля.

В просмотренных источниках информации нами не обнаружены указанные отличительные признаки. Следовательно, предлагаемое решение отвечает критерию существенности отличий.

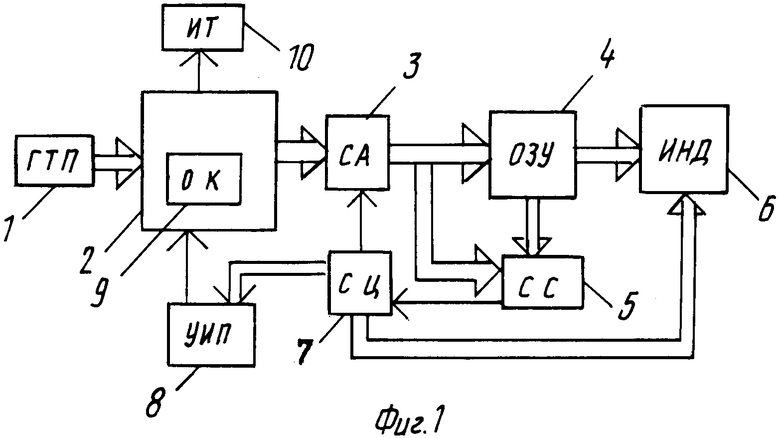

На фиг.1 представлена блок-схема устройства, реализующего способ.

Устройство содержит: генератор 1 тестовых последовательностей (ГТП), соединенный своими выходами с подключающим устройством 2; подключающее устройство 2 (ПУ), соединенное выходами со входами многоканального сигнатурного анализатора 3 (СА), причем информационные выходы последнего соединены со входами оперативного запоминающего устройства 4 (ОЗУ) и с первыми входами схемы 5 сравнения (СС); оперативное запоминающее устройство 4 (ОЗУ), соединенное выходами со вторыми входами схемы 5 сравнения и с индикатором 6 (ИНД); схему 5 сравнения (СО), соединенную выходом со входом счетчика 7 циклов (СЦ); счетчик 7 циклов (СЦ), соединенный первыми выходами с индикатором 6, вторыми выходами со входами управляемого источника 8 питания (УИП), а третьим выходом - со входом стробирования сигнатурного анализатора 3; управляемый источник 8 питания, соединенный выходом со входом питания ПУ 2; объект 9 контроля (ОК), выводы которого подключаются к ПУ; измеритель 10 температуры (ИТ), соединенный с ПУ 2.

Предлагаемый способ осуществляется следующим образом. ОК 9 подвергается термоциклированию, причем он постоянно подключен к устройству, осуществляющему измерение критических напряжений и контроль за работоспособностью ОК. Оператор снимает зависимость критического напряжения от внутренней температуры кристалла ОК, измеряемой ИТ 10.

Работа устройства контроля состоит в следующем. С 1 через 2 циклический тестовый сигнал поступает на входы ОК. Выходной сигнал с ОК 9 поступает на вход анализатора 3. После каждого цикла тестирования очередная полученная сигнатура сравнивается в схеме сравнения 5 с предыдущей, записанной в 4. При их совпадении объект 9 считается работоспособным, содержимое счетчика 7 увеличивается на единицу, под воздействием кода со счетчика 7 выходное напряжение управляемого источника 8 уменьшается на определенную величину (в конкретном устройстве 0,01 В), и цикл тестирования повторяется. Начальный уровень питающего напряжения принимается равным номинальному для данного объекта контроля. При несовпадении сигнатур тестирование завершается, на индикаторе 6 появляется значение запаса по критическому напряжению (разности между номинальным напряжением питания и величиной критического напряжения), пропорциональное содержимому счетчика циклов.

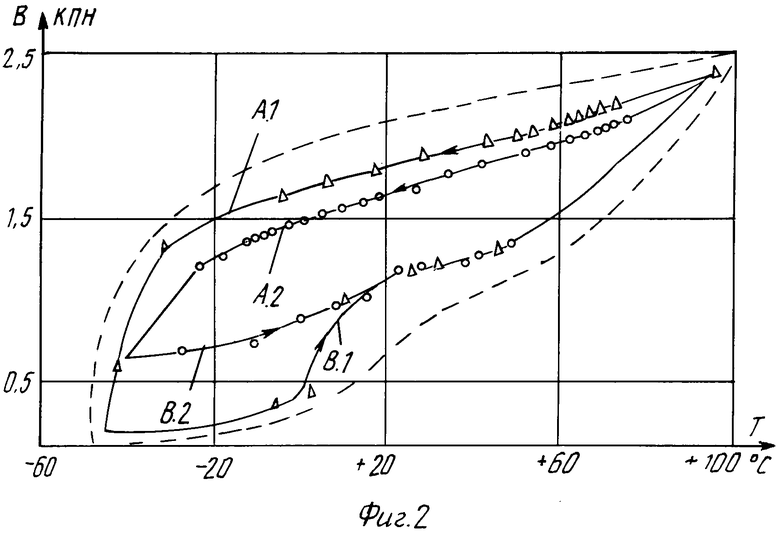

На фиг.2 представлен результат определения вида зависимости критических напряжений от внутренней температуры кристалла. Эксперимент проводился согласно описанному выше порядку действий. Как видно из фиг.2, на которой по оси Х указан запас критического напряжения, по Y - внутренняя температура кристалла, зависимость эта имеет вид петли гистерезиса, причем площадь петли у разных микросхем разная. Ветви А.1 и А.2 построены по значениям, полученным при нагревании соответственно микросхем 1 и 2, а В.1 и В.2 при охлаждении этих микросхем. Знаками Δ и 0 отмечены моменты снятия значений соответственно 1-ой и 2-ой микросхем. Штриховой линией указана пороговая площадь петли гистерезиса.

Для получения пороговой площади авторами были исследованы ИС серии К174АФ5, которые подвергались многократному термоциклированию. Выяснилось, что ИС, для которых после первого термоцикла получены различные значения площади петли, отказывают после того, как в ходе многократного термоциклирования изменяющаяся для каждой ИС площадь достигает определенного значения одинакового для всех ИС. Число термоциклов до отказа связано обратной зависимостью с площадью, полученной при первом термоцикле.

S1, S2, ..., Sn < Si где S1, S2, Sn - площади различных микросхем после первого термоцикла;

i - номер термоцикла, при котором получено значение пороговой площади;

Si - пороговое значение площади петли гистерезиса.

Отобранные таким образом ИС К174АФ5 были поставлены на дополнительные испытания по функционированию (электротермотренировка), которые подтвердили высокую достоверность заявляемого способа.

Таким образом, предлагаемый способ дает возможность по найденному термодинамическому параметру (площади петли гистерезиса) определять внутреннее физическое состояние объекта контроля (т.е. долю неупругих деформаций в кристалле, связанную с потенциальной безотказностью) в любой момент времени задолго до отказа. Причем, предлагаемый в заявке способ позволяет в группе надежных или устойчивых схем, что возможно определить способом прототипа, выделить образцы повышенного качества для устройств ответственного применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РАЗБРАКОВКИ ИС | 1998 |

|

RU2143704C1 |

| СПОСОБ РАЗДЕЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ ПО НАДЕЖНОСТИ | 2005 |

|

RU2284539C1 |

| Способ контроля КМОП интегральных схем | 1990 |

|

SU1772772A1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2003 |

|

RU2249228C1 |

| СПОСОБ РАЗБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ИЗДЕЛИЙ ПО НАДЕЖНОСТИ | 2009 |

|

RU2455655C2 |

| СПОСОБ РАЗДЕЛЕНИЯ АНАЛОГОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ ПО НАДЕЖНОСТИ | 2006 |

|

RU2311653C1 |

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 1998 |

|

RU2149417C1 |

| Способ контроля качества и надежности микросхем | 1984 |

|

SU1228052A1 |

| Микроконтакт для фотоприемной гибридной микросхемы | 2016 |

|

RU2621889C1 |

Сущность изобретения: способ заключается в том, что объект контроля подвергают циклическому воздействию тестовых сигналов, а также высоких и низких температур, а за информативный параметр принимают площадь петли гистерезиса полученной зависимости критических напряжений при нагревании и охлаждении. 2 ил.

СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ, включающий циклическую подачу на входы объекта контроля тестовых последовательностей, циклическое сравнение реакции объекта контроля с эталонной, определение критических напряжений объекта контроля путем снижения напряжения питания после каждого цикла до появления первой ошибки, отличающийся тем, что, с целью повышения достоверности контроля охлаждают объект контроля, затем нагревают, измеряют зависимость критических напряжений при нагревании, затем охлаждают, измеряют зависимость критического напряжения при охлаждении, вычисляют площадь петли гистерезиса полученной зависимости, отбирают интегральные схемы, для которых выполняется соотношение

S < Si,

где Si - максимально допустимая площадь петли гистерезиса.

| Способ отбраковки микросхем памяти | 1985 |

|

SU1310756A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-08-15—Публикация

1990-08-13—Подача