Изобретение относится к электронной технике и может быть использовано для повышения надежности электронной аппаратуры, построенной на КМОП ИС.

Известен способ [1] контроля интегральных схем, включающий измерение их статических параметров при номинальном напряжении питания, измерение статических параметров ИС при пониженном напряжении питания в диапазоне 3,1-3,2 В, определение разности значений статических параметров, измеренных при номинальном и пониженном напряжениях питания, и сравнение этой разности с эталонным значением.

Недостаток способа заключается в том, что способ не охватывает дефекты, проявляющиеся в динамическом режиме работы ИС. Известен также способ [2] отбраковки ИС, заключающийся в том, что на ИС подают номинальное напряжения питания и входные сигналы. Измеряют у всех ИС, входящих в контролируемую партию, величину активного сопротивления, включенного в цепь питания ИС, при которой прекращается функционирование. Затем определяют значение Ркрит.м, соответствующее максимуму распределения критических сопротивлений в партии ИС, и отбраковывают ИС по отличию индивидуальных значений Ркрит. от значений Ркрит.м на величину, превышающую среднеквадратическое отклонение.

Недостаток способа заключается в низкой производительности, обусловленной пошаговым изменением сопротивления в цепи питания до прекращения функционирования ИС.

Наиболее близким по технической сущности и достигаемому эффекту является способ [3] отбраковки потенциально ненадежных КМОП ИС, основанный на измерении критического питающего напряжения Екр. и его зависимости от частоты следования тестовых сигналов. В известном способе на испытуемую ИС подается тестовая последовательность импульсов, определяется и запоминается сигнатура на выходе ИС. В следующем цикле тестирования понижается напряжение питания испытуемой ИС, полученная сигнатура сравнивается с предыдущей. При их совпадении ИС считается работоспособной, напряжение питания уменьшается и тестирование продолжается при новом значении напряжения питания. Если сигнатуры не совпадают, то измерение на этом заканчивается. Сигнатурный анализ проводился на двух частотах, определялись значения Екр. и ΔЕкр., а разбраковка производилась по нормам Екр > 2,0 В и ΔЕкр≅ 0,03 В.

Недостатком этого способа является низкая производительность, обусловленная определением сигнатуры в i-том цикле измерения, уменьшением напряжения питания ИС, определением сигнатуры в i+1-м цикле, сравнением с предыдущим значением и т.д. пока сигнатурный анализатор не зафиксирует сбой работы ИС, а также низкая достоверность. При изменении питающего напряжения не изменяется амплитуда входного воздействия, что в отдельных случаях приводит к пробою ИС или ложным срабатываниям сигнатурного анализатора при отсутствии напряжения питания диагностируемой ИС. Кроме того, при определении сигнатуры не учитывается динамика развития отказа. Она заключается в том, что при уменьшении напряжения питания ИС сначала происходит увеличение времени задержки распространения при включении и выключении, проявляющееся в затягивании фронтов, и только при дальнейшем уменьшении напряжения выходной сигнал вырождается в постоянный уровень. Сигнатурный анализатор, таким образом, фиксирует сбой в работе на более позднем этапе развития отказа.

Цель изобретения разработка способа отбраковки КМОП ИС по степеням надежности, позволяющей увеличить производительность и достоверность по сравнению с известными способами.

Цель достигается следующим образом. На испытуемую микросхему подают напряжение питания, близкое к критическому, и входную тестовую последовательность импульсов с амплитудой, ограниченной напряжением питания испытуемой ИС для предотвращения ложных срабатываний и пробоя микросхемы.

В качестве информативного параметра для отбраковки ИС измеряют время задержки распространения при включении и выключении. Этот параметр позволяет в большей мере учесть дефекты ИС, чем измерение статических параметров, и в то же время является более ранним этапом обнаружения дефектов, чем нестабильная сигнатура. Пpоизводят отбраковку микросхем путем сравнения разности значений срабатывания при включении (выключении) между средним значением величины задержки выборки и значением задержки срабатывания конкретной ИС с эталонным значением.

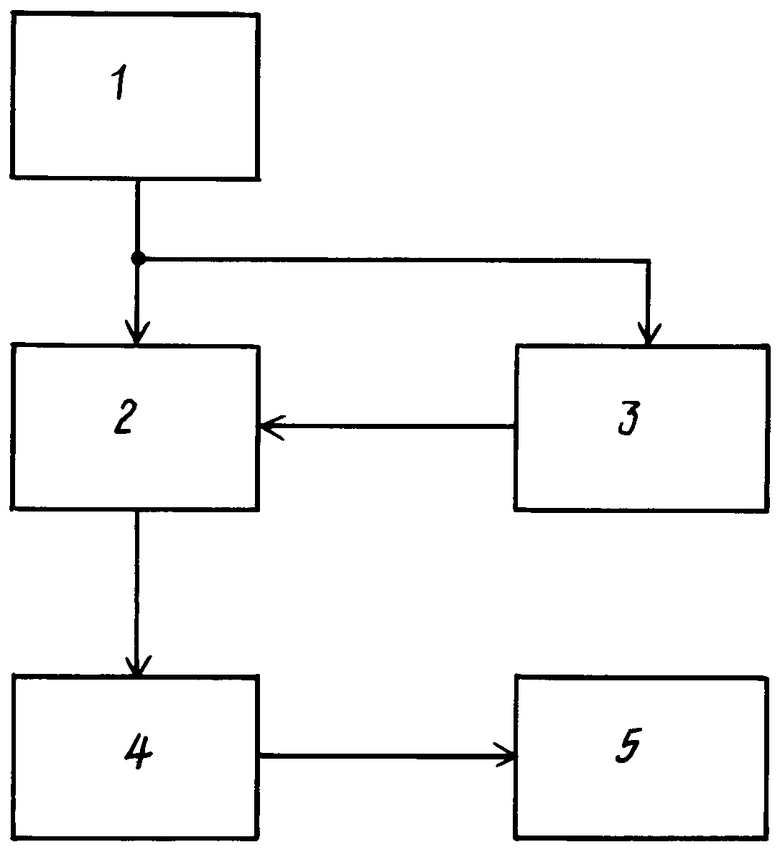

На чертеже изображена схема устройства, реализующего способ.

Устройство содержит источник 1 питания, выход которого соединен с выводами питания испытуемой ИС 2 и блоком 3 формирователя тестовой последовательности, соединенным с входами ИС 2. Выходы ИС 2 соединены через коммутатор 4 с входом блока 5 измерения задержек распространения при включении и выключении.

Способ отбраковки ИС осуществляется следующим образом. На источнике 1 питания устанавливают напряжение питания испытуемой ИС, близкое к критическому питающему напряжению. С блока 3 формирователя тестовой последовательности на испытуемую ИС 2 подают тестовую последовательность импульсов с амплитудой, равной напряжению питания испытуемой ИС. Коммутатором 4 выбирают заданный выход микросхемы. Времена задержки распространения при включении и выключении определяют блоком 5. Конкретное значение пониженного напряжения питания устанавливается эмпирически в зависимости от типа ИС и предъявляемых требований по надежности. Чем ближе это значение к критическому, тем сильнее проявляются дефекты ИС и поэтому выше достоверность разбраковки.

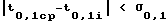

Для каждой испытуемой микросхемы измеряют времена задержки распространения при включении и выключении t0,1i и t1,0i. Находят средние значения задержек t0,1ср и t1,0ср, после чего отбраковывают микросхемы по критерию /t0,1ср t0,1i/ < δ 0,1 (1) /t1,0ср t1,0i/ < δ 1,0, (2) где t0,1ср среднее значение задержки распространения при включении;

t0,1i значение задержки распространения при включении i-той микросхемы;

δ 0,1 параметр, определяющий уровень качества ИС по задержке распространения при включении микросхемы;

t1,0ср, t1,0i, δ 1,0- то же, при выключении ИС.

В зависимости от предъявляемых требований по надежности можно использовать критерии (1) и (2) совместно или только один из критериев.

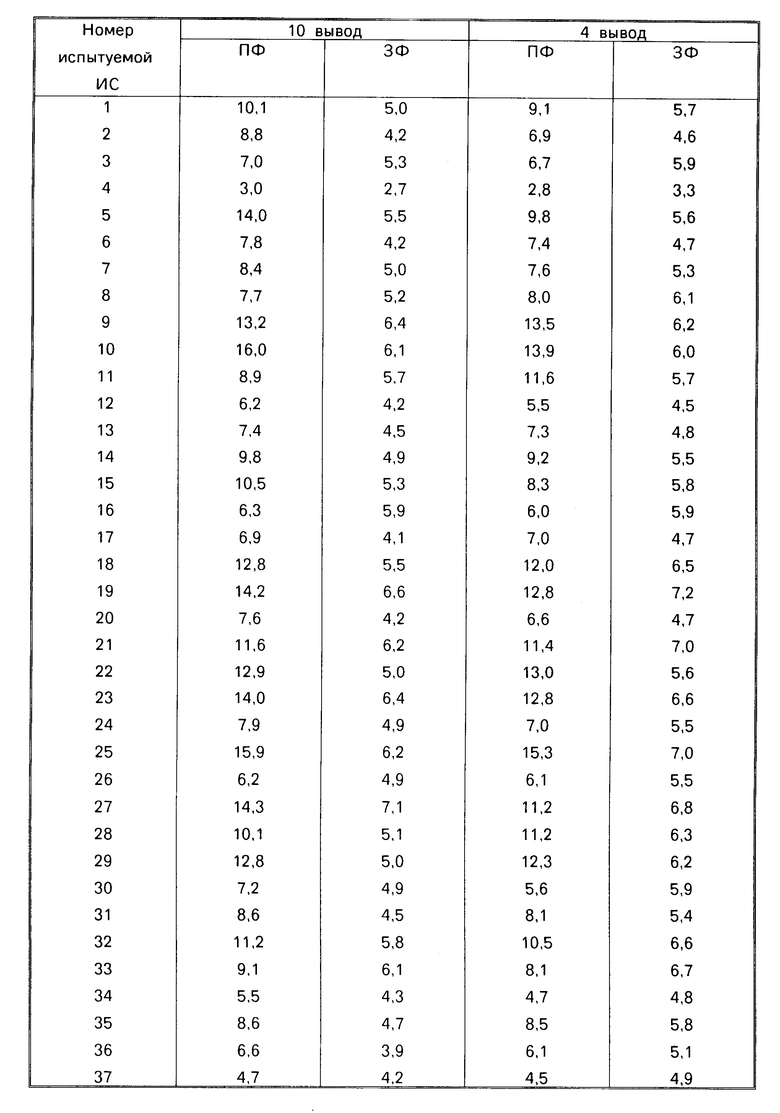

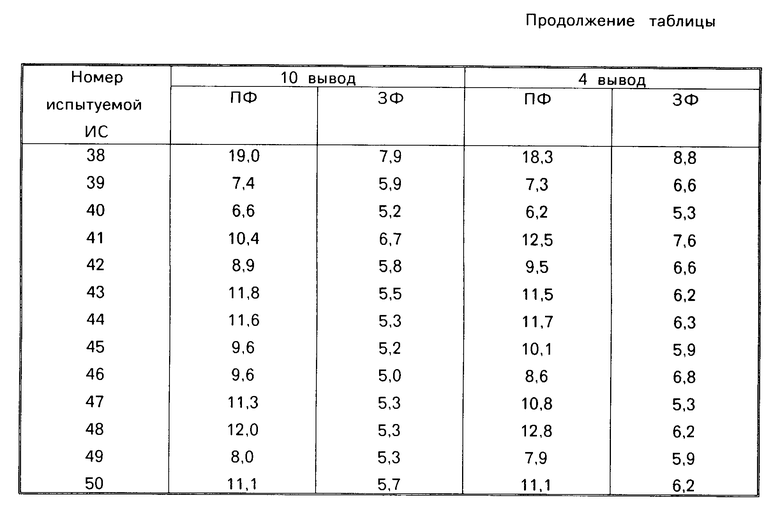

Описанный выше способ отбраковки ИС можно проиллюстрировать следующим примером. В таблице указаны времена задержек срабатывания в микросекундах при включении (ПФ) и выключении (ЗФ) для выборки N 50 шт. ИС серии 564ЛП2 ОС. Напряжение питания ИС составило 1,9 В, частота входной тактовой последовательности 10 кГц. Для 4 вывода ИС время t0,1ср составило 6,4 μS, t1,0ср 4,9 μS. Если в качестве параметра, определяющего качество ИС, принять дисперсию, то значение δ0,1 5,1 μS, δ1,0 1,1μ S.

Используя критерий (1), отбраковке как менее надежные подлежат ИС с номерами 9, 10, 11, 18, 19, 22, 23, 25, 29, 38, 41, 43, 44, 48. По критерию (2) отбраковываются ИС с номерами 8, 9, 10, 18, 19, 21, 23, 25, 27, 28, 29, 32, 33, 38, 39, 41, 42, 43, 44, 46, 48, 50. Экспериментально установлено, что времена задержки срабатывания при включении и выключении для одного выхода ИС имеют сильную корреляционную связь, коэффициент корреляции r > 0,6, поэтому для отбраковки ИС можно пользоваться критериями (1) и (2) как совместно, так и порознь. Кроме того, коэффициенты корреляции между временами задержек срабатывания при включении (выключении) для функционально одинаковых выходов ИС (для ИС 564ЛП2 выводы 10 и 4) также имеют сильную корреляционную связь. В связи с этим диагностирование ИС достаточно проводить по одному любому выходу микросхемы. Конкретные значения δ 0,1 и δ 1,0 определяются для каждого типа ИС в зависимости от жесткости требований по надежности, предъявляемых к микросхемам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ отбраковки потенциально ненадёжных цифровых интегральных схем по времени задержки распространения сигнала | 2024 |

|

RU2836117C1 |

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| Способ отбраковки КМОП интегральных схем по уровням надежности | 1985 |

|

SU1269061A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 2004 |

|

RU2257591C1 |

| Способ контроля КМОП интегральных схем | 1990 |

|

SU1772772A1 |

| Способ отбраковки КМОП интегральных схем по уровням надежности | 1988 |

|

SU1640660A2 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2003 |

|

RU2249228C1 |

| СПОСОБ ОТБОРА ПЛАСТИН С РАДИАЦИОННО-СТОЙКИМИ МОП-ИНТЕГРАЛЬНЫМИ СХЕМАМИ | 1995 |

|

RU2082178C1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 1998 |

|

RU2149417C1 |

| УСТРОЙСТВО ДЛЯ ВЫЯВЛЕНИЯ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ МЕТОДОМ АНАЛИЗА ФОРМ И/ИЛИ ПАРАМЕТРОВ ДИНАМИЧЕСКОГО ТОКА ПОТРЕБЛЕНИЯ | 2007 |

|

RU2348049C1 |

Использование: электронная техника. Сущность изобретения: на испытуемую интегральную схему (ИС) подают входную тестовую последовательность с амплитудой, равной напряжению питания ИС и соответствующей критическому уровню. По величинам отклонения времени распространения данной ИС от среднего значения при включении, либо выключении ИС от установленного критерия производят отбраковку ИС по надежности. 1 ил. 1 табл.

СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ, включающий подачу на испытуемую интегральную схему критического питающего напряжения, входной тестовой последовательности, измерение параметров интегральной схемы и сравнение их с эталонными значениями, отбраковку интегральных схем по уровню надежности, отличающийся тем, что на испытуемую интегральную схему подают входную тестовую последовательность с амплитудой, равной напряжению питания испытуемой интегральной схемы, измеряют время задержки распространения при включении и выключении и производят отбраковку интегральных схем по критериям

либо

где t0,1ср среднее время задержки распространения при включении интегральной схемы;

t0,1i время задержки распространения при включении i-й интегральной схемы;

σ0,1 параметр, определяющий уровень качества интегральных схем по задержке распространения при включении интегральных схем;

t1,0cp,t1,0i,σ1,0 то же при выключении интегральных схем.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аладинский В.К | |||

| и др | |||

| Критическое питающее напряжение как информативный параметр при электрофизическом диагностировании КМОП ИС Электронная техника, сер.8, вып.4, 1990. | |||

Авторы

Даты

1995-10-20—Публикация

1992-10-19—Подача