113

Изобретение относится к измерительной технике и может быть использовано для контроля надежности микросхем памяти.

Цель изобретения - повьшение достоверности отбраковки микросхем памяти, обладающих повьшенной надежностью.

Сущность предлагаемого способа заключается в том, что величина |Е,- -Е, I характеризует однородность накопителя. Чем меньше величина |Е,-Е, тем однороднее накопитель запоминающего устройства, т.е. тем меньше различаются между собой по электрическим характеристикам ячейки памяти накопителя. Высокая однородность накопителя свидетельствует о высокой однородности материалов и точности воспроизведения технологических процессов, используемых при изготовлении микросхем памяти, и, следовательно, высокой надежности микросхем памяти. При этом Е( - первое значение напряжения питагшя, при котором отказывает одна ячейка памяти, а Е. второе значение напряжения питания, при котором отказывает заданное большое количество ячеек, например половина всех ячеек.

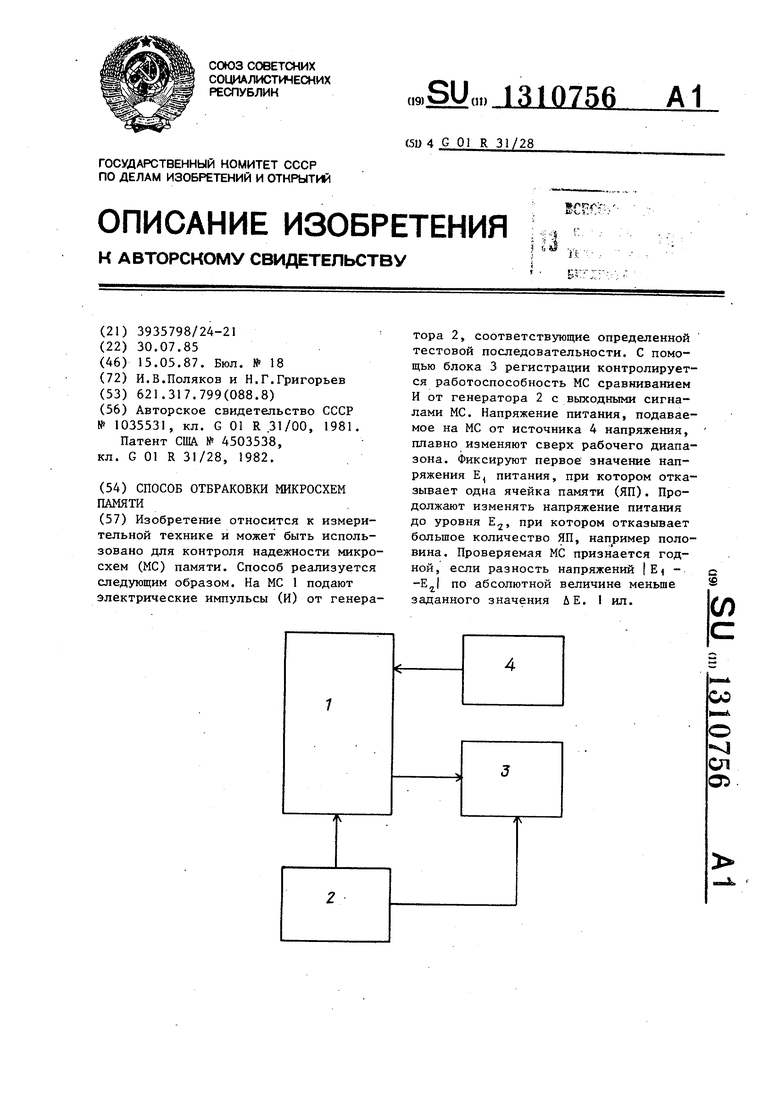

На чертеже изображена блок-схема устройства для реализации предлагаемого способа.

На схеме обозначены микросхема 1 памяти, генератор 2 импульсов, блок 3 регистрации числа отказавших ячеек памяти и источник.4 напряжения.

На испытываемую микросхему 1 подают электрические импульсы от генератора 2 импульсов, соответствующие определенной тестовой последовательности. Работоспособность микросхемы

Редактор А.Огар

Составитель В.Степанкин Техред А.Кравчук

Заказ 1887/42

Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретегшй и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

62

контролируют с помощью блока 3 регистрации, сравнивающего импульсы от генератора 2 с выходными сигналами микросхемы 1, Напряжение питания,

подаваемое на микросхему 1 от источника 4 напряжения, плавно изменяют сверх рабочего диапазона. При этом фиксируют первое значение напряжения питания Е , при котором отказывает одна ячейка памяти (адрес отказавшей ячейки не запоминают). Напряжение питания продолжают изменять до уровня Е,, при котором отказывает заданное большое количество ячеек памяти, например половина всех ячеек. Проверяемая микросхема признается годной, если разность напряжений JE, - по абсолютной величине меньше заданного значения Л Е,

Формула изобретения

Способ отбраковки микросхем памяти J состоящий в том, что записывают эталонную информацию в микросхему сравнивают считанную с микросхемы информацию с эталонной, понижают напряжение питания микросхемы памяти, измеряют величину напряжения питания, при котором происходит нарушение соответствия считанной информации эталону, отличающийся тем, что, с целью повьш1ения достоверности отбраковки микросхем памяти, изме- ряют первое значение напряжения питания, при котором отказывает одна ячейка памяти, измеряют второе значение напряжения питания, при котором отказывает заданное количество ячеек памяти, и считают микросхему годной, если разность первого и второго напряжений питания по абсолютной величине меньше заданного значения.

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| Способ контроля интегральных микросхем памяти | 1985 |

|

SU1247799A1 |

| Способ контроля интегральных микросхем памяти | 1987 |

|

SU1594458A1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 2003 |

|

RU2249228C1 |

| СПОСОБ РАЗБРАКОВКИ МИКРОСХЕМ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ПО УРОВНЮ БЕССБОЙНОЙ РАБОТЫ | 2008 |

|

RU2371731C1 |

| СПОСОБ РАЗБРАКОВКИ ПАРТИИ ИНТЕГРАЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ ПО РАДИАЦИОННОЙ СТОЙКОСТИ | 1998 |

|

RU2149417C1 |

| СПОСОБ ХАРАКТЕРИЗАЦИИ МИКРОПРОЦЕССОРНЫХ ДАТЧИКОВ ДАВЛЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2319125C2 |

| Способ отбраковки потенциально нестабильных цифровых интегральных микросхем | 1987 |

|

SU1525637A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| ПЕРЕНОСНОЙ ПРОГРАММНО-ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2007 |

|

RU2363975C2 |

Изобретение относится к измерительной технике и может быть использовано для контроля надежности микросхем (МС) памяти. Способ реализуется следующим образом. На МС 1 подают электрические импульсы (И) от генератора 2, соответствующие определенной тестовой последовательности. С помощью блока 3 регистрации контролируется работоспособность МС сравниванием И от генератора 2 с выходными сигналами МС. Напряжение питания, подаваемое на МС от источника 4 напряжения, плавно изменяют сверх рабочего диапазона. Фиксируют первое значение напряжения Е, питания, при котором отказывает одна ячейка памяти (ЯП). Продолжают изменять напряжение питания до уровня Ej, при котором отказывает большое количество ЯП, например половина. Проверяемая МС признается годной, если разность напряжений E - -Е.| по абсолютной величине меньше заданного значения АЕ. I ил. с (Л со о ел 05

| Устройство для поверки измерителей девиации частоты | 1982 |

|

SU1035531A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4503538, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-05-15—Публикация

1985-07-30—Подача