Изобретение относится к технике построения АЦП, предназначенных для кодирования мгновенных значений быстропротекающих процессов.

Известен АЦП параллельного сравнения, содержащий группу компараторов, один из входов каждого из которых (опорный вход) смещен относительно соседнего на величину напряжения - шаг квантования последовательным равноступенчатым делителем [1].

Недостатком известного АЦП является ограниченная точность и разрядность (6+8 бит). С увеличением разрядности (числа уровней квантования) возрастает число ступеней последовательного резистивного делителя, на котором формируется шкала опорных уровней квантования, и усиливается влияние входных токов компараторов на рост погрешности преобразования. При этом образуются различные паразитные смещения нулевого уровня каждого из компараторов, вызывающие как следствие, рост нелинейности характеристики преобразования. Для их уменьшения используют низкоомные делители, что вызывает увеличение тока, а значит, и увеличение температуры элементов. Это, в свою очередь, вызывает возникновение дополнительной погрешности. Одновременно с увеличением числа ступеней последовательного резистивного делителя возрастают паразитные реактивности, поэтому снижается быстродействие АЦП.

Наиболее близким по технической сущности к предлагаемому является АЦП параллельного сравнения, содержащий источник опорного напряжения, n p-разрядных блоков кодирования с одинаковым шагом квантования, каждый из которых выполнен на p-ступенчатом резистивном делителе и группе компараторов, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам p-ступенчатого резистивного делителя, причем вторые входы компараторов всех блоков кодирования объединены и являются входной шиной, третьи входы объединены и являются шиной стробирования, а их выходы являются выходной шиной единичного кода, первый вход p-ступенчатого резистивного делителя первого блока кодирования является шиной нулевого потенциала [2]. Разрядность такого устройства при этом возрастает.

Но так как опорное напряжение на делителе не должно по условиям пробоя и нагрева превышать предельно допустимого значения для одного из блоков кодирования, то каждый из них может работать только в диапазоне напряжений, в n раз меньшем (n - число используемых блоков кодирования) по сравнению с предельно допустимым опорным напряжением. Однако снижение опорного напряжения вызывает снижение тока через делитель, что приводит к относительному увеличению входных паразитных токов компараторов и росту соответствующей погрешности. Одновременно уменьшение тока через делитель вызывает и снижение быстродействия АЦП, так как уменьшение тока приводит к увеличению времени заряда паразитной емкости, значение которой осталось неизменным по сравнению с непрерывным по структуре делителем.

Целью изобретения является уменьшение погрешности преобразования.

Цель достигается тем, что в АЦП параллельного сравнения, содержащем источник опорного напряжения, n p-разрядных блоков кодирования с одинаковым шагом квантования, каждый из которых выполнен на p-ступенчатом резистивном делителе и группе компараторов, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам p-ступенча- того резистивного делителя, причем вторые входы компараторов всех блоков кодирования объединены и являются входной шиной, третьи входы объединены и являются шиной стробирования, а их выходы являются выходной шиной единичного кода, первый вход p-ступенчатого резистивного делителя первого блока кодирования является шиной нулевого потенциала, в каждом из последующих блоков кодирования между первым входом резистивного делителя и шиной нулевого потенциала включен соответствующий резистивный элемент смещения, во все блоки кодирования введены элементы развязки, входы которых объединены и соединены с выходом источника опорного напряжения, при этом выход элемента развязки n-го блока кодирования подключен к второму входу p-ступенчатого резистивного делителя данного блока кодирования, а в первых n-1 блоках кодирования между выходом соответствующего элемента развязки и вторым входом p-ступенчатого резистивного делителя каждого из данных блоков кодирования включен соответствующий дополнительный резистивный элемент смещения.

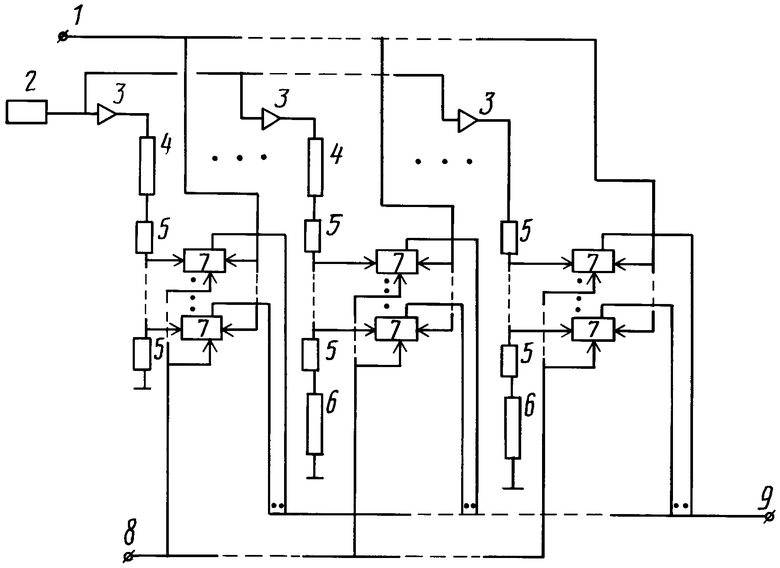

Схема АЦП приведена на чертеже, где 1 - входная шина, 2 - источник опорного напряжения, 3 - элементы развязки, 4 - дополнительный резистивный элемент сравнения, 5 - p-ступенчатый резистивный делитель, 6 - резистивный элемент смещения, 7 - компараторы, 8 - шина стробирования, 9 - шина единичного кода.

АЦП работает следующим образом.

Он содержит группу из n малоразрядных блоков кодирования параллельного сравнения. Число p единичных уровней квантования в каждом блоке кодирования и шаг квантования выбирают исходя из условия достижения максимального быстродействия и минимальной погрешности блока. Если общее число ступеней квантования (число единичных разрядов кода) АЦП должно составлять Z, то n = [Z/p].

Уровни квантования каждого блока кодирования смещены относительно друг друга, образуя совокупную шкалу из n p последовательно возрастающих уровней квантования. Требуемое смещение уровней в блоке достигается последовательным включением с делителем 5 каждого из блоков резисторов 4 и 5, образующих в совокупности неравноступенчатый делитель. Причем в первом из блоков включен резистор 4 так, что образуются последние p младших уровней, а в последнем n=m блоке последовательно с делителем 5 включается только резистор 6, чем образуются первые p старших уровней квантования. В совокупности все n блоков образуют параллельную шкалу n˙p уровней квантования, последовательно изменяющихся на шаг квантования. Если суммарное сопротивление резисторов 4 и 6 составляет RΣ= (Z-p)R, где R - сопротивление ступени делителя 5, то сопротивление резистора 6 составляет R6 = =ipR, где i = i= - номер блока, а сопротивление резистора 4 при этом равно R4 = = RΣ- R6.

- номер блока, а сопротивление резистора 4 при этом равно R4 = = RΣ- R6.

По сигналу, поступившему на вход 8, производится параллельное стробирование всех компараторов и считывается текущее мгновенное значение измеряемой величины, как и в известной схеме АЦП параллельного сравнения (одного отсчета). Так как число компараторов в каждом блоке минимизировано, а сами блоки развязаны между собой элементами 3, то это приводит к уменьшению погрешности преобразования, в частности, вследствие уменьшения нелинейности характеристики преобразования каждого из блоков и увеличению быстродействия, так как уменьшаются паразитные реактивности каждого из блоков, питаемых параллельными токами.

Элементами развязки могут служить, например, повторители напряжения, при помощи которых можно осуществлять также градуировку каждого из блоков. Для упрощения на чертеже не указаны источники напряжений для коррекции (при необходимости) нулевых точек характеристик каждого из блоков. При необходимости могут быть включены элементы развязки между блоками и во входной шине.

Наличие общего опорного источника обеспечивает минимизацию относительных погрешностей каждого из блоков.

Предельное разрешение АЦП ограничивается только шумом компаратора (сегодня оно много хуже), а его предельное быстродействие определяется задержкой компараторов и дешифратора.

Изобретение относится к технике построения АЦП, преназначенных для кодирования мгновенных значений быстропротекающих процессов. Цель изобретения - уменьшение погрешности преобразования достигается за счет того, что в АЦП, содержащий n-p-разрядных блоков кодирования, состоящих каждый из p-ступенчатого резистивного делителя и группы компараторов, введены во все блоки кодирования, кроме первого блока, резистивный элемент смещения, включенный между первым входом резистивного делителя и шиной нулевого потенциала, во все блоки кодирования элементы развязки, а в первые n-1 блоки кодирования дополнительный резистивный элемент смещения, который включен между вторым входом резистивного делителя и выходом элемента развязки соответствующего блока. 1 ил.

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ, содержащий источник опорного напряжения, np-разрядных блоков кодирования с одинаковым шагом квантования, каждый из которых выполнен на p-ступенчатом резистивном делителе и группе компараторов, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам p-ступенчатого резистивного делителя, вторые входы компараторов всех блоков кодирования объединены и являются входной шиной, третьи входы объединены и являются шиной стробирования, а их выходы являются выходной шиной единичного кода, первый вход p-ступенчатого резистивного делителя первого блока кодирования является шиной нулевого потенциала, отличающийся тем, что, с целью уменьшения погрешности преобразования, в каждом из последующих блоков кодирования между первым входом резистивного делителя и шиной нулевого потенциала включен соответствующий резистивный элемент смещения, во все блоки кодирования введены элементы развязки, входы которых объединены и соединены с выходом источника опорного напряжения, выход элемента развязки n-го блока кодирования подключен к второму входу p-ступенчатого резистивного делителя данного блока кодирования, а в первых n-1 блоках кодирования между выходом соответствующего элемента развязки и вторым входом p-ступенчатого резистивного делителя каждого из данных блоков кодирования включен соответствующий дополнительный резистивный элемент смещения.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с.87-90. | |||

Авторы

Даты

1994-08-30—Публикация

1991-07-03—Подача