Изобретение относится к технике построения аналого-цифровых преобразователей (АЦП) и предназначено для кодирования мгновенных значений сигналов быстропротекающих процессов.

Известен АЦП параллельно сравнения, содержащий группу компараторов, один их входов каждого из которых (опорный вход) смещен относительно соседнего на величину напряжения - шаг квантования [1].

Недостатком известного АЦП является ограниченная точность и разрядность (6-8 битов). С увеличением разрядности (числа уровней квантования) возрастает число ступеней резистивного делителя, на котором формируется шкала опорных уровней квантования, и усиливается влияние входных токов компараторов на рост погрешности преобразования. При этом образуются паразитные, различные по значениям падения напряжений на ступенях делителя, вызывающие различные паразитные смещения нулевого уровня каждого из компараторов. Для их уменьшения используют низкоомные делители, что вызывает увеличение тока, а значит и увеличение температуры элементов, что, в свою очередь, обусловливает возникновение дополнительной погрешности. Одновременно с увеличением числа ступеней резистивного делителя возрастают паразитные реактивности.

Наиболее близким по технической сущности к предлагаемому является АЦП параллельного сравнения, содержащий дешифратор единичного кода, выходы которого являются выходной шиной, источник опорного напряжения, источники напряжений смещения, n, р-разрядных блоков кодирования, каждый из которых выполнен на резистивном делителе и группе компараторов, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам резистивного делителя, причем вторые входы компараторов всех блоков кодирования объединены и являются входной шиной, третьи входы объединены и являются шиной стробирования, первый вход резистивного делителя первого блока кодирования является шиной нулевого потенциала [2].

Целью изобретения является повышение точности преобразования при сохранении максимального быстродействия.

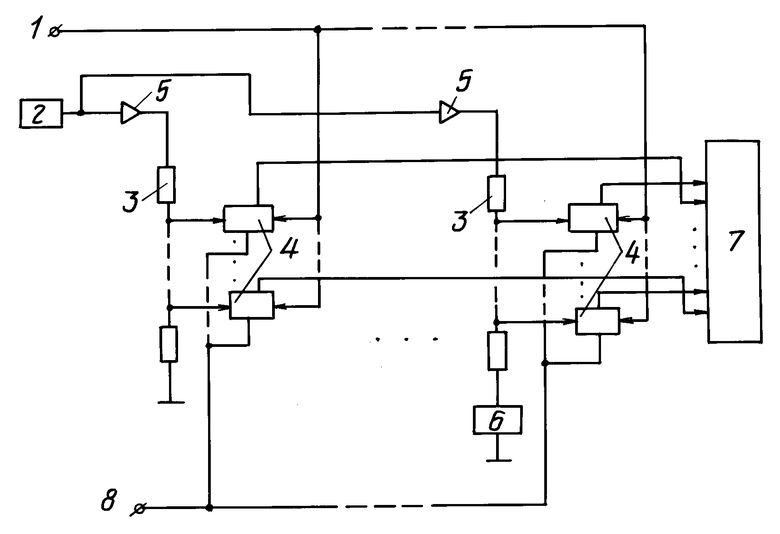

Схема АЦП приведена на чертеже, где 1 - входная шина, 2 - источник опорного напряжения, 3 - резистивный делитель, 4 - компаратор, 5 - элемент развязки, 6 - источник напряжения смещения, 7 - дешифратор единичного кода, 8 - шина стробирования.

Сущность изобретения заключается в том, что в АЦП параллельного сравнения, содержащий дешифратор 7 единичного кода, выходы которого являются выходной шиной, источники 6 напряжений смещения, n,р-разрядных блоков кодирования, каждый из которых выполнен на резистивном делителе 3 и группе компараторов 4, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам резистивного делителя, причем вторые входы компараторов всех блоков кодирования объединены и являются входной шиной 1, третьи входы объединены и являются шиной 8 стробирования, первый вход резистивного делителя первого блока кодирования является шиной нулевого потенциала, в каждый блок кодирования введен элемент 5 развязки, р-разрядные блоки кодирования выполнены с одинаковым шагом квантования, а источники напряжения смещения выполнены со смещением напряжения относительно друг друга на часть шага квантования, при этом первые входы резистивных делителей блоков кодирования, кроме первого, соединены с выходами соответствующих источников напряжения смещения, вторые входы всех резистивных делителей через соответствующие элементы развязки подключены к выходу источника опорного напряжения, выход i-го компаратора блока кодирования (i= ) подключен к [(p K )+S]-у входу дешифратора единичного кода, где S - номер блока кодирования (s=

) подключен к [(p K )+S]-у входу дешифратора единичного кода, где S - номер блока кодирования (s= ); K - коэффициент (K=

); K - коэффициент (K= ).

).

Количество разрядов, т.е. число ступеней резистивного делителя с параллельными компараторами кодирующего блока, выбирают исходя из условия достижения максимального быстродействия, т.е. оптимальности тока через делитель при заданном предельном опорном напряжении, и минимизации погрешности. При этом шаг квантования по уровню составляет Δ . Для достижения разрешения в n раз лучшего необходимо использовать n идентичных кодирующих блоков, причем напряжение источника 6 в каждом блоке смещается относительно напряжения источника 6 соседнего блока Δ /n. Тем самым смещаются опорные уровни каждой из групп компараторов относительно соседней на значение Δ /n. Иначе говоря, образуется ряд параллельных шкал, уровни с одинаковыми номерами которых смещены в пределах шага Δ . Но в отличие от нониусной шкалы, реализуемой в АЦП поразрядного сравнения и требующей последовательных операцией отсчета, в рассматриваемом случае отсчет значения измеряемой величины выполняется за один такт по сигналу стробирования, поступающему в шину 8. Единичный (термометрический) код компараторов преобразуется (сжимается) дешифратором 7 в двоичный или двоично-десятичный, например, по схеме, описанной в [2].

Выход каждого i-го компаратора (i= ) S-го блока кодирования (s=

) S-го блока кодирования (s= ) подключен к [(p ˙K) + S]-у входу дешифратора единичного кода, где р - число компараторов в блоке кодирования; К - коэффициент (K=

) подключен к [(p ˙K) + S]-у входу дешифратора единичного кода, где р - число компараторов в блоке кодирования; К - коэффициент (K= ).

).

При необходимости к первому из блоков кодирования подключают источник напряжения для коррекции нуля, а нули остальных блоков корректируются теми же источниками 6 напряжения смещения.

Напряжения смещения для развязки резистивных делителей могут задаваться либо отдельным активным источником в каждом блоке кодирования, либо при помощи делителя напряжения с общим активным источником и с повторителем напряжения для каждого блока кодирования, либо при помощи дополнительного резистора в делителе каждого блока кодирования, включаемого между соответствующим концом делителя и общей шиной. В последнем случае напряжение смещения образуется за счет падения напряжения на дополнительном резисторе при протекании тока через делитель, а требуемое напряжение смещения в каждом блоке кодирования задают выбором соответствующего сопротивления этого резистора. При этом может быть достигнута большая стабильность напряжения смещения с меньшими затратами по сравнению с использованием активных источников напряжения. Для развязки резистивных делителей блоков сравнения с целью уменьшения паразитной емкости эти делители подключены к опорному источнику 2 через элементы 5 развязки, например через повторители напряжений, через которые можно также осуществлять индивидуально градуировку отдельных делителей по верхнему пределу преобразования.

При необходимости для развязки измерительных входов компараторов могут быть включены соответствующие широкополосные повторители во входной шине между группами компараторов блоков кодирования. Предельное разрешение данного устройства ограничивается только шумами компараторов, т.е. превышает разрешение известных устройств, а его предельное быстродействие определяется задержкой компараторов и дешифратора, т.е. как и в малоразрядных быстродействующих АЦП.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1991 |

|

RU2020748C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1991 |

|

RU2019031C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1992 |

|

RU2066923C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020750C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (АЦП) | 2011 |

|

RU2477564C1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Устройство для измерения амплитуды импульсных сигналов | 1984 |

|

SU1223154A1 |

Изобретение относится к технике построения аналого-цифровых преобразователей (АЦП) и предназначено для кодирования мгновенных значений сигналов быстропротекающих процессов. Целью изобретения является повышение точности преобразования при сохранении максимального быстродействия. Цель достигается тем, что в АЦП параллельного сравнения, содержащий дешифратор единичного кода, источник опорного напряжения, источники напряжения смещения и np-разрядных блоков кодирования, каждый из которых выполнен на резистивном делителе и группе компараторов, в эти блоки введен элемент развязки, каждый из блоков кодирования выполнен с одинаковым шагом квантования, а источники напряжения смещения выполнены со смещением напряжения относительно друг друга на часть шага квантования. 1 ил.

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ, содержащий дешифратор единичного кода, выходы которого являются выходной шиной, источник опорного напряжения, источники напряжений смещения, np-разрядных блоков кодирования, каждый из которых выполнен на резистивном делителе и группе компараторов, первые входы которых в каждом блоке кодирования подключены к соответствующим выходам резистивного делителя, вторые входы компараторов всех блоков кодирования объединены и являются входной шиной, третьи входы объединены и являются шиной стробирования, первый вход резистивного делителя первого блока кодирования является шиной нулевого потенциала, отличающийся тем, что, с целью повышения точности преобразования при сохранении максимального быстродействия, в каждый блок кодирования введен элемент развязки, p-разрядные блоки кодирования выполнены с одинаковым шагом квантования, а источники напряжения смещения выполнены со смещением напряжения друг относительно друга на часть шага квантования, при этом первые входы резистивных делителей блоков кодирования, кроме первого, соединены с выходами соответствующих источников напряжения смещения, вторые входы всех резистивных делителей через соответствующие элементы развязки подключены к выходу источника опорного напряжения, выход i-го компаратора блока кодирования (i= ) подключен к [(p˙k) + s] -му входу дешифратора единичного кода, где s - номер блока кодирования (s=

) подключен к [(p˙k) + s] -му входу дешифратора единичного кода, где s - номер блока кодирования (s= ), k - коэффициент (k=

), k - коэффициент (k= ) .

) .

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гельман М.М | |||

| Аналого-цифровые преобразователи для информационно-измерительных систем | |||

| -М.: Издательство стандартов, 1989, с.90, рис.2.2. | |||

Авторы

Даты

1994-09-30—Публикация

1991-05-23—Подача