Изобретение относится к цифровой измерительной технике и может быть использовано в информационно-измерительных системах для кодирования широкополосных сигналов.

Известен АЦП поразрядного сравнения с использованием коммутируемых многоразрядных делителей [1]. Его недостатком является относительная сложность изготовления.

Наиболее близким к предлагаемому по своей технической сущности является АЦП поразрядного сравнения [2] . Его недостатком является необходимость использования ЦАП для преобразования значения каждого из разрядов в эквивалентное напряжение, что снижает быстродействие и увеличивает погрешность, в том числе динамическую, АЦП.

Цель изобретения - повышение быстродействия и уменьшение погрешности преобразования.

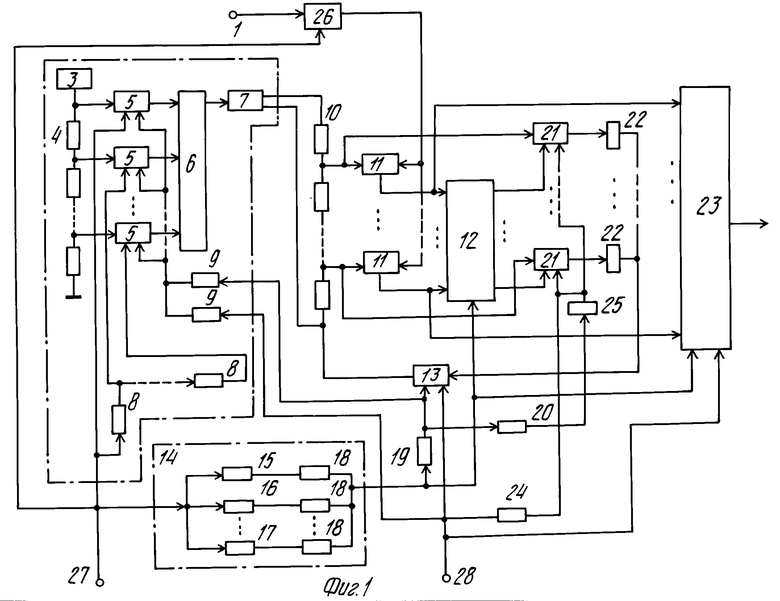

Схема АЦП изображена на фиг.1 и содержит входную шину 1, блок 2 коммутации опорного напряжения включающий источник 3 опорного напряжения, делитель 4 напряжения, блоки 5 выборки-хранения, блок 6 элементов развязки, повторитель 7 напряжения, элементы 8 задержки и элементы 9 развязки, делитель 10 напряжения, компараторы 11, дешифратор 12 кода, блок 13 выборки напряжения смещения, распределитель 14 импульсов, включающий дополнительные элементы 15, 16,..., 17 задержки и элементы 18 развязки, первый 19 и второй 20 элементы задержки, группу блоков 21 выборки-хранения, группу элементов 22 развязки, выходной регистр 23, первый 24 и второй 25 дополнительные элементы развязки, блок 26 выборки-хранения измерительного сигнала, шину 27 запуска, шину 28 сброса.

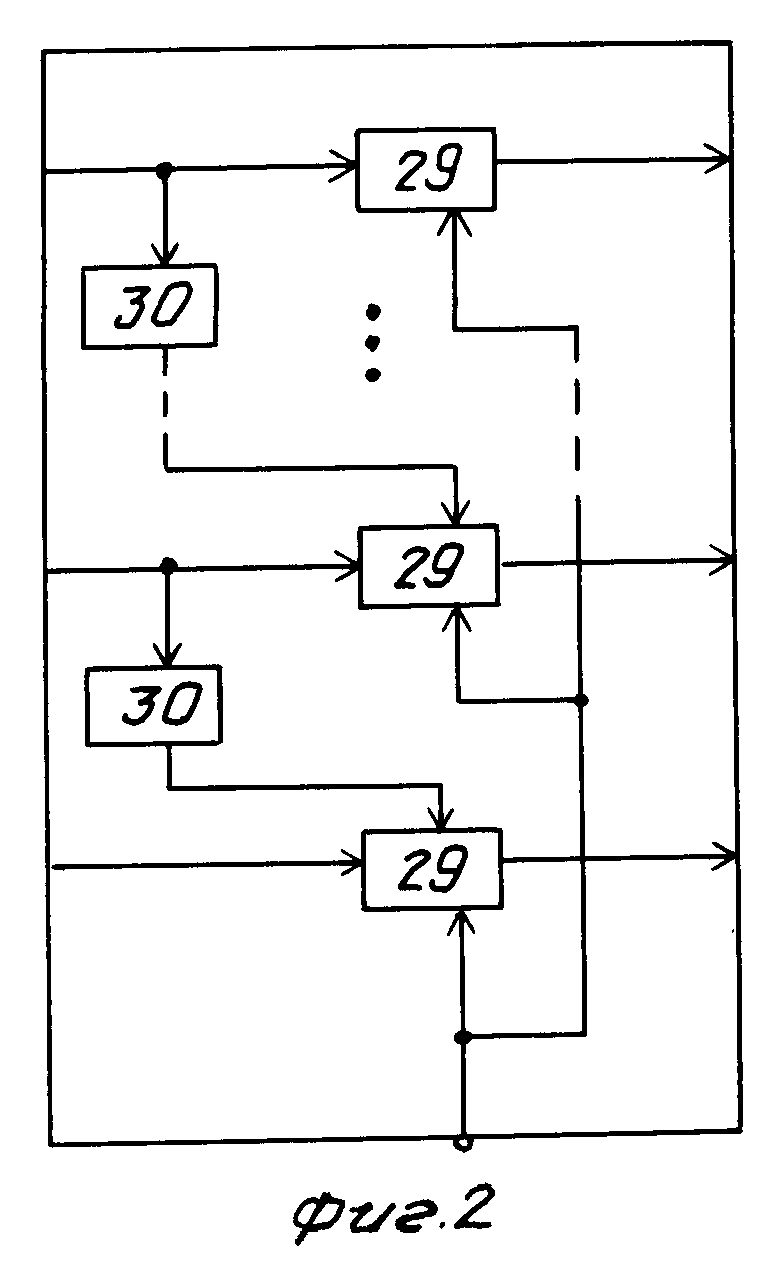

На фиг. 2 изображена схема дешифратора 12 кода, который содержит элементы И 29 и элементы НЕ 30.

В исходном состоянии АЦП, которое он принимает по сигналу сброса (шина 28), все блоки выборки-хранения обнуляются при поступлении общего сигнала сброса на их соответствующие входы.

АЦП работает следующим образом.

Сигнал запуска (шина 27) в качестве стробирующего (управляющего) поступает в блок 5 выборки-хранения, подключенный непосредственно к источнику 3 опорного напряжения, равного пределу измерений. В случае подекадного сравнения этот предел составляет 10n единиц напряжения, где n - число декад-десятичных разрядов кода. Масштабный делитель 4 напряжения делит опорное напряжение источника 3 на уровни, равные квантам - "весам" единиц соответствующих разрядов кода от (n-1)-го до последнего младшего, а соответствующие блоки 5 последовательно их запоминают при последовательном поступлении с соответствующих отводов цепочки элементов 8 задержки стробирующих импульсов. Цепочка элементов 8 задержки выполняет функцию распределителя импульсов стробирования блока 5.

При запоминании опорного напряжения, равного 10n единицам, первым из блоков 5 оно через соответствующий элемент блока 6 развязки и повторитель 7 напряжения передается на делитель 10 напряжения, распределяясь по его ступеням с шагом, равным 10n-1 единицам. Смещение делителя 10, задаваемое выходным сигналом блока 13, в первом такте определения старшего разряда кода равно нулю.

Одновременно со стробированием первого из блоков 5 стробируется блок 26, и в нем запоминается текущее мгновенное значение измеряемого сигнала, которое сравнивается в компараторах 11 с установленными уровнями напряжения делителя 10. С задержкой в элементе 15, равной времени τ1 упомянутой передачи опорного напряжения и установления соответствующих цепей, импульс запуска через соответствующий элемент 18 развязки передается на управляющий вход стробирования дешифратора 12. Этот дешифратор преобразует параллельный единичный выходной код компараторов 11 в позиционный единичный. При этом деблокируется соответствующий элемент И 29 дешифратора (фиг.2) и стробирующий импульс передается через него на вход стробирования соответствующего блока 21, в который считывается уровень напряжения, эквивалентный полученному значению старшего разряда кода. Одновременно параллельный код с выходов компараторов 11 считывается в выходной регистр 23 для последующей его передачи во внешнее устройство памяти. Этот регистр выполнен на блоках выборки-хранения, что повышает скорость записи кода.

Далее стробирующий импульс (сигнал запуска) с задержкой в элементе 19, равной необходимому времени τ2 записи сигнала в блок 21 и регистр кода, передается на вход стробирования блока 13 и в него переписывается содержимое простробированного в данном такте определения старшего разряда кода блока 21. Одновременно этим импульсом стробирования переданным через соответствующий элемент 9 развязки на входы сброса блока 5, обнуляются блок 5. Далее с задержкой в элементе 20, равной времени τ3 записи сигнала в блок 13 и сброса блока 5, импульс стробирования передается на входы сброса блока 21 и они обнуляютсся. Одновременно с задержкой в первом из элементов 8, равной времени τ4=τ1+τ2+τ3 , сигнал запуска (импульс стробирования) поступает на вход стробирования второго из блоков 5, подключенного к выходу первой ступени делителя 4, и в него переписывается ступень опорного напряжения, равная 10n-1 единицам. При этом на ступенях делителя 10 шаг приращения напряжения становится равным 10n-2 единицам, а сами шаги (кванты) оказываются смещенными выходным напряжением блока 13, переданным на делитель 10 и эквивалентным старшему разряду кода, т.е. "цена" деления делителя 10 стала равной "весу" единицы второго старшего разряда кода. Далее с задержкой в элементе 16, равной τ5=τ4+τ1 , работа АЦП повторяется аналогично описанному и определяется значение второго старшего разряда кода. Аналогично с соответствующими задержками (i-1) τ5, где i = 2,...,n определяются остальные разряды кода вплоть до младшего.

Сигналами синхронизации для переписи кодов из выходного регистра могут служить сигналы с выхода элемента 20 задержки. При этом обнулять блоки выборки выходного регистра в каждом такте определения разрядов кода нет необходимости, так как при стробировании они работают в режиме слежения за входными сигналами (выходными сигналами компараторов). В таком же режиме слежения работают блоки 13 и 2. Прочие блоки выборки-хранения коммутируются и работают на общую цепь, поэтому перед каждым тактом определения текущего разряда кода их необходимо обнулять.

Цепочка элементов 8 и набор элементов 15-17 задержки выполняют функции распределителей сигнала запуска, а дешифратор 12 - функцию коммутатора блока 21 выборки-хранения.

Изобретение относится к цифровой измерительной технике и может быть использовано в информационно-измерительных системах для кодирования широкополосных сигналов. Цель изобретения - повышение быстродействия и уменьшение погрешности преобразования. Цель достигается тем, что в АЦП поразрядного сравнения, содержащий блок коммутации опорного напряжения, делитель напряжения, компараторы, дешифратор кода, выходной регистр, два элемента задержки и блок выборки-хранения измерительного сигнала, введены группа блоков выборки-хранения, распределитель импульсов, включающий дополнительные элементы задержки, а также элементы развязки, блок выборки напряжения смещения, группа элементов развязки и два дополнительных элемента развязки, при этом блок коммутации опорного напряжения содержит источник опорного напряжения, делитель напряжения, блоки выборки-хранения, элементы задержки, элементы развязки, блок развязки и повторитель напряжения. 1 з.п. ф-лы, 2 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 1149410, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-09-30—Публикация

1991-03-12—Подача