Изобретение относится к цифровой измерительной технике и может быть использовано в информационно-измерительных системах для кодирования широкополосных сигналов.

Известен АЦП поразрядного сравнения с использованием коммутируемых многоразрядных делителей [1]. Его недостатком является относительная сложность изготовления.

Наиболее близким к предлагаемому по своей технической сущности является АЦП поразрядного сравнения [2] . Его недостатком является необходимость использования ЦАП для преобразования значения каждого из разрядов в эквивалентное напряжение, что снижает быстродействие и увеличивает погрешность, в том числе динамическую, АЦП.

Цель изобретения - повышение быстродействия и снижение динамической погрешности преобразования.

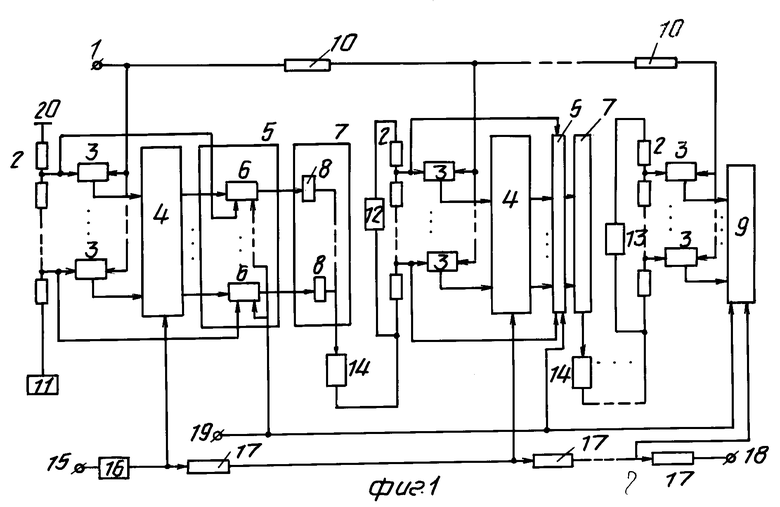

Схема устройства представлена на фиг.1 и содержит входную шину 1, делители 2 напряжения, группы компараторов 3, дешифраторы 4 кода, группы 5 блоков 6 выборки-хранения, блоки 7 элементов 8 развязки, выходной регистр 9, линии 10 задержки, источники 11, 12,...,13 опорного напряжения 1-го (старшего), 2-го,...,(n-1)-го разрядов, блоки 14 согласования, шину 15 запуска, генератор 16 тактовых импульсов, элементы 17 задержки, шину 18 конца преобразования, шину 19 сброса, шину 20 нулевого потенциала.

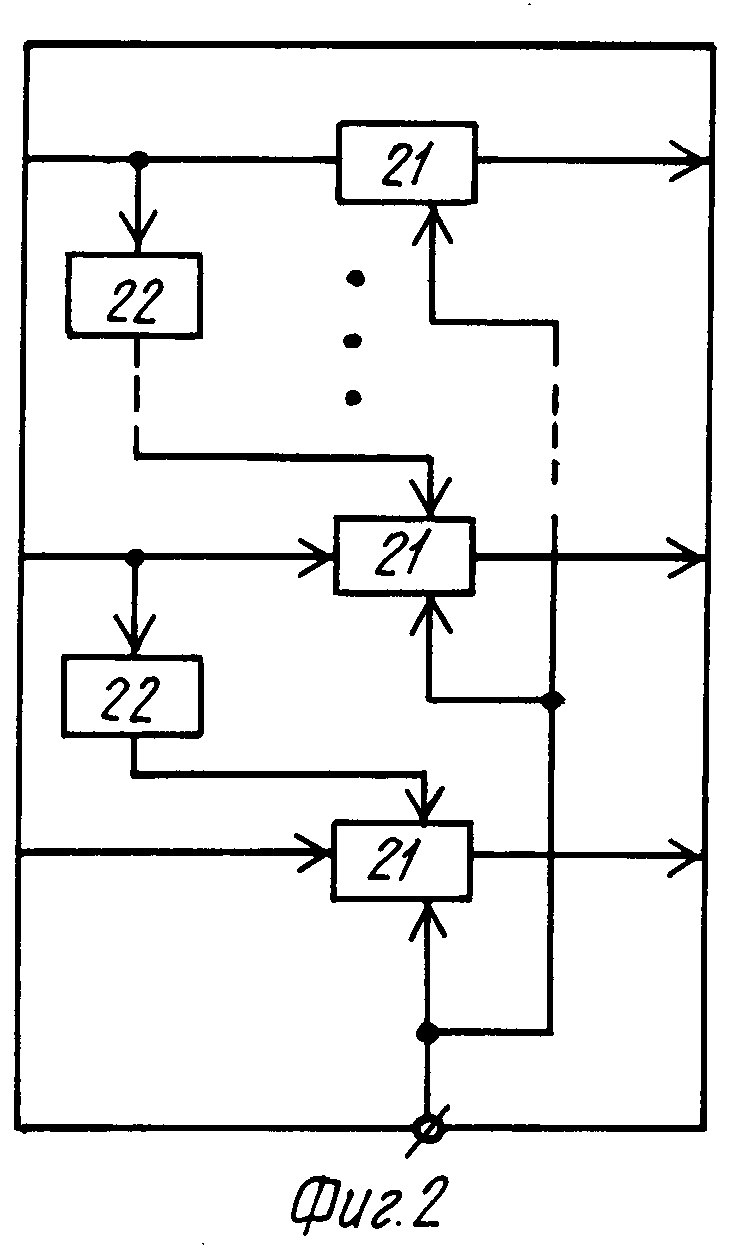

Схема дешифратора 4 кода приведена на фиг.2 и содержит элементы И 21 и элементы НЕ 22.

АЦП работает следующим образом.

По сигналу сброса, поступившему на шину 19, все группы 5 блоков 6 выборки-хранения и регистр 9 обнуляются. Измеряемая величина поступает на входы группы компараторов 3 старшего разряда (в цепи делителя напряжения с источником 11) и последовательно с задержками в линиях 10 на входы других групп компараторов. Число компараторов в группе определяется видом используемого кода. Так, для десятичного кода число компараторов в группе равно девяти, а делители 2 являются декадными. Тогда опорные напряжения источников 11,12,13 пропорциональны 10 и отличаются друг от друга на десятичный порядок, т.е. равны от 10n (источник 11 первого старшего разряда) до 10 (источник 13 младшего разряда).

По сигналу запуска (шина 15) в генераторе 16 формируется одиночный тактовый импульс, который поступает на вход стробирования элементов И 21 дешифратора 4, подключенного к компараторам группы первого старшего разряда. Выходные сигналы компараторов, представляющие параллельный единичный код старшего разряда, преобразуются в дешифраторе в эквивалентный позиционный, единичная позиция которого соответствует полученному коду старшего разряда. При этом деблокируется соответствующий элемент И дешифратора (фиг.2), тактовый импульс передается через него на вход стробирования соответствующего блока 6 выборки-хранения, в который считывается и запоминается уровень напряжения соответствующей ступени делителя 2. Этот уровень напряжения, эквивалентный старшему разряду кода, передается через соответствующий элемент 8 развязки блока 7 и блок 14 согласования и смещает делитель 2 напряжения соседнего, второго старшего разряда. Шаг квантования в этом делителе оказывается равным (в случае десятичного кода) 10n-2, а опорное напряжение источника 12 равно 10n-1 единицам напряжения. С задержкой в первом из элементов 17, равной времени установления напряжения на выходе блока 14 согласования и в делителе напряжения, тактовый импульс передается в дешифратор 4, подключенный к соответствующей группе компараторов, и аналогично описанному формируется код второго старшего разряда, а на выход соответствующего блока 14 согласования передается напряжение, эквивалентное сумме первых двух старших разрядов кода.

Аналогично формируются последующие разряды кода, вплоть до последнего, младшего, который непосредственно считывается в соответствующий регистр 9, выполненный на блоках выборки-хранения. Время формирования каждого из разрядов кода минимизировано использованием блоков выборки-хранения, что позволяет увеличить быстродействие устройства и снизить динамическую погрешность измерений по сравнению с прототипом. Последовательная задержка измеряемого сигнала линиями 10 на входах групп компараторов каждого из разрядов позволяет дополнительно уменьшить динамическую погрешность измерений (задержки линии 10 и элемента 17 идентичны). Коды n-1 старших разрядов могут считываться с выходов соответствующих групп компараторов в регистры кода, аналогичные регистру 9, (на фигурах не показаны, выполнены на блоках выборки-хранения) параллельно со считыванием уровней напряжений в блоки 6 выборки-хранения соответствующих групп 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1991 |

|

RU2019031C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1991 |

|

RU2020747C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1991 |

|

RU2020748C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1992 |

|

RU2066923C1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1979 |

|

SU964981A1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

Изобретение относится к цифровой измерительной технике и может быть использовано в информационно-измерительных системах для кодирования широкополосных сигналов. Цель изобретения - повышение быстродействия и снижение динамической погрешности преобразования. Цель достигается тем, что в АЦП, содержащий n источников опорных напряжений, делители напряжения, группы компараторов, генератор тактовых импульсов, элемент задержки, n - 1 дешифраторов кода и выходной регистр, введены n - 1 групп блоков выборки-хранения, n - 1 блоков развязки, n - 1 блоков согласования, n - 1 линий задержки и n - 1 элементов задержки. 2 ил.

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ, содержащий n по числу старшего и младших разрядов источников опорных напряжений, делители напряжения, группы компараторов, первые входы компараторов группы старшего разряда являются входной шиной, а их вторые входы и первые входы компараторов остальных групп подключены к соответствующим выходам делителя напряжения соответствующего разряда, входы делителя напряжения старшего разряда соединены с выходами источника опорного напряжения старшего разряда и с шиной нулевого потенциала, а каждый из источников опорного напряжения остальных разрядов подключен параллельно делителю напряжения соответствующего разряда, генератор тактовых импульсов, выход которого соединен с входом первого элемента задержки, вход является шиной запуска, n - 1 дешифраторов кода и выходной регистр, выходы которого являются выходной шиной, отличающийся тем, что, с целью повышения быстродействия и снижения динамической погрешности, в него введены n - 1 групп блоков выборки-хранения, n - 1 блоков развязки, n - 1 блоков согласования, последовательно соединенные n - 1 линий задержки и последовательно соединенные с второго по n - 1 элементов задержки, вход второго из которых соединен с выходом первого элемента задержки, а вход (n - 1)-го элемента задержки является шиной конца преобразования, вход каждого элемента задержки, кроме последнего, объединен с управляющим входом соответствующего дешифратора кода, информационные входы которого соединены с выходами компараторов группы соответствующего разряда, а выходы - с управляющими входами блоков выборки-хранения группы соответствующего разряда, информационные входы которых подключены к выходам делителя напряжения данного разряда, входы сброса объединены с входом сброса выходного регистра и являются шиной сброса, а выходы через соответствующие блоки развязки и согласования подключены к второму входу делителя напряжения следующего более младшего разряда, вход первой линии задержки является входной шиной, а выходы линий задержки подключены к вторым входам компараторов соответствующих групп разрядов, кроме старшего, информационные входы выходного регистра соединены с выходами компараторов группы младшего разряда, а вход записи объединен с входом (n - 1)-го элемента задержки.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-09-30—Публикация

1991-03-01—Подача