Изобретение относится к приборостроению, в частности к электроизмерительной технике, и может быть использовано в тензо- и термометрии для измерения сигналов тензо- и термодатчиков.

Известен регистратор (система) "Прочность", предназначенный для автоматизации процессов измерения, сбора и обработки информации преобразователей различных величин, характеризующих тепловое, деформированное и напряженное состояние конструкций. Измерительные сигналы в каждом канале поступают на измерительный модуль, представляющий собой преобразователь сигналов датчиков в напряжение и АЦП на выходе, цифровые сигналы которого поступают через информационную шину цифровой части системы в ЭВМ. Поскольку получение цифрового результата измерения в АЦП (уравновешивание) проходит при совместной работе преобразователя сигналов датчиков, датчиков и линий связи, получение результатов измерения требует большого времени из-за неизбежных переходных процессов, связанных с уравновешиванием входной измерительной цепи.

Наиболее близким по технической сущности и достигаемому эффекту является регистратор (система) "Ресурс 23/27", состоящий из восьми нормализаторов и блока АЦП. Для формирования временной диаграммы управления работой регистратора имеется тактовый генератор. Имеется также один общий формирователь управления нормализаторами на их управляющих входах. Результаты измерения из блока АЦП поступают в ЭВМ. Блок АЦП с восемью аналоговыми входами и одним цифровым выходом представляет собой многоканальный АЦП. ЭВМ, осуществляющая прием результатов измерения, по существу выполняемых функций является приемником данных, который может быть реализован не только ЭВМ как таковой, а и микропроцессором, цифровым автоматом, цифровым регистратором и т. д. В этой системе существенно увеличено быстродействие за счет введения нормализаторов, не требующих участия в аналого-цифровом преобразовании сигналов датчиков, проводов подсоединения их к системе и входных измерительно-преобразовательных цепей. Однако для ряда задач (статодинамические испытания конструкций) этого быстродействия оказывается недостаточно. Период поступления пакетов по n результатов измерений в приемник данных определяется выражением

Т=Тн+Тацп+Тприем+Твозврат,

где Тн - время работы нормализатора;

Тацп - время работы АЦП;

Тприем - время приема n результатов измерения;

Твозврат - время возврата регистратора на исходную позицию;

n - число каналов нормализации (число нормализаторов) регистратора.

К недостаткам следует также отнести СТАРТ-СТОП-й режим работы нормализаторов, отрицательно сказывающийся на точности результатов нормализации из-за ухудшения их повторяемости. Построение блока АЦП (многоканального АЦП) из восьми отдельных АЦП добавляет в результаты измерения дополнительную погрешность из-за неидентичноси точностных характеристик отдельных АЦП и существенно усложняет и удорожает конструкцию регистратора, увеличивая, кроме того, его надежность и затраты на метрологическое обеспечение.

Целью изобретения является повышение быстродействия, точности и надежности регистратора.

Цель достигается тем, что в многоканальный регистратор, содержащий тактовый генератор, многоканальный аналого-цифровой преобразователь с нормализаторами на входах, формирователь управления нормализаторами, подключенный выходом к управляющим входам нормализаторов, и приемник данных, введены счетчик-делитель, запоминающее устройство и блок синхронизации, синхровход которого соединен с выходом деления счетчика-делителя, вход которого соединен с выходом тактового генератора и входом запуска аналого-цифрового преобразователя, а счетным выходом - с управляющим входом аналого-цифрового преобразователя, выход которого соединен с информационным входом запоминающего устройства, выход которого соединен с входом приемника данных, вход управления записью - с выходом конца преобразования аналого-цифрового преобразователя, синхровход - с выходом деления или со счетным выходом счетчика-делителя, а управляющий вход - с выходом стробирования приемника данных, управляющий вход которого соединен с выходом блока синхронизации, а вход формирователя управления нормализаторами подключен к выходу деления или счетному выходу счетчика-делителя; блок синхронизации выполнен в виде одновибратора, вход и выход которого являются синхровходом и выходом готовности блока синхронизации соответственно; блок синхронизации выполнен в виде RS-триггера, S- и R-входы и выход которого являются синхровходом, входом сброса готовности и выходом готовности блока синхронизации соответственно, причем вход сброса готовности соединен с выходом стробирования приемника данных; блок синхронизации выполнен в виде D-триггера, S-, С- и R-входы и выход которого являются синхровходом, дополнительным синхровходом, входом сброса готовности и выходом готовности блока синхронизации соответственно, причем D-вход триггера соединен с шиной нулевого сигнала, а дополнительный синхровход - с выходом тактового генератора.

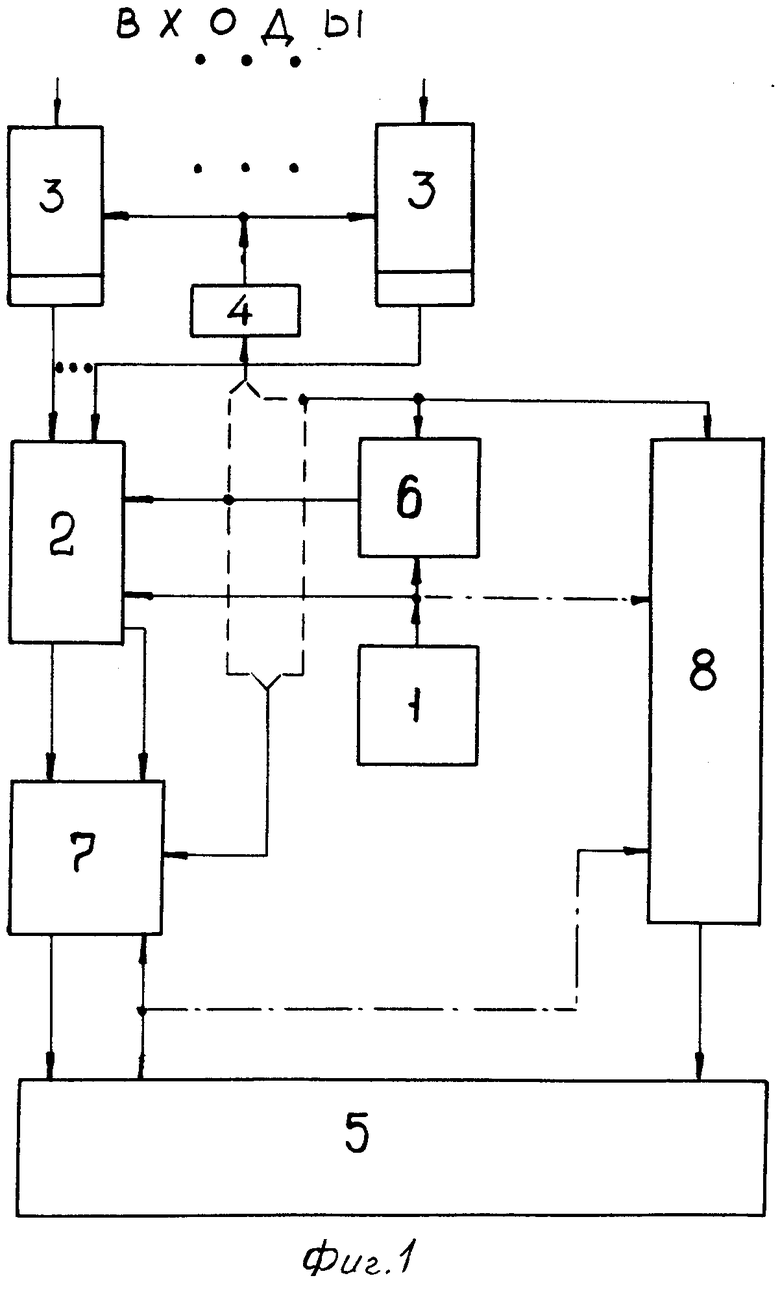

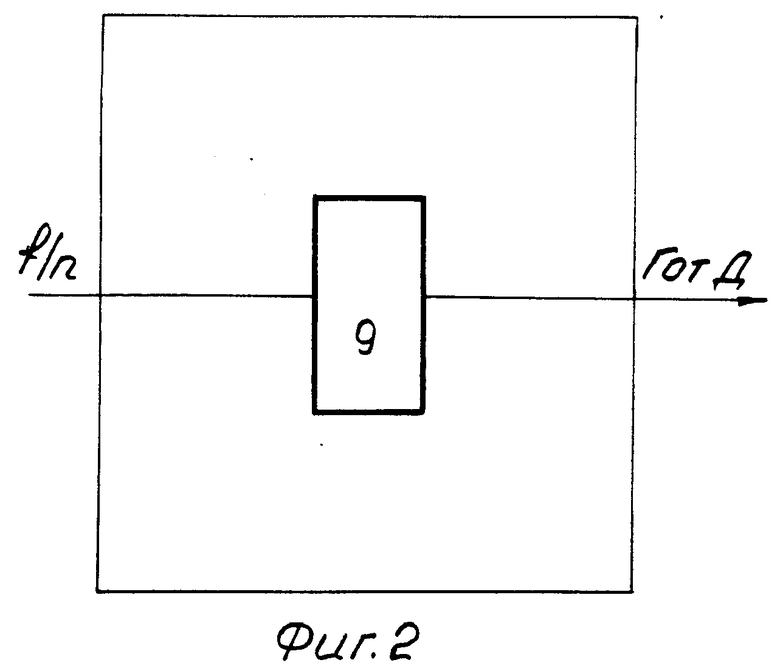

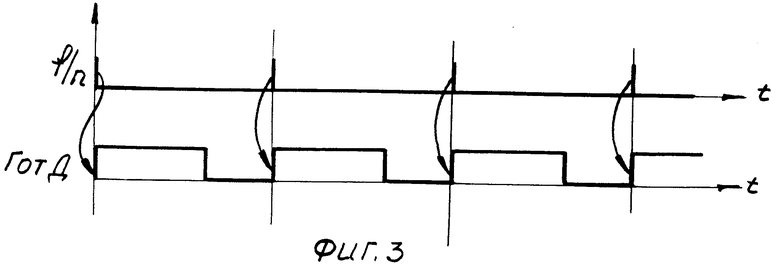

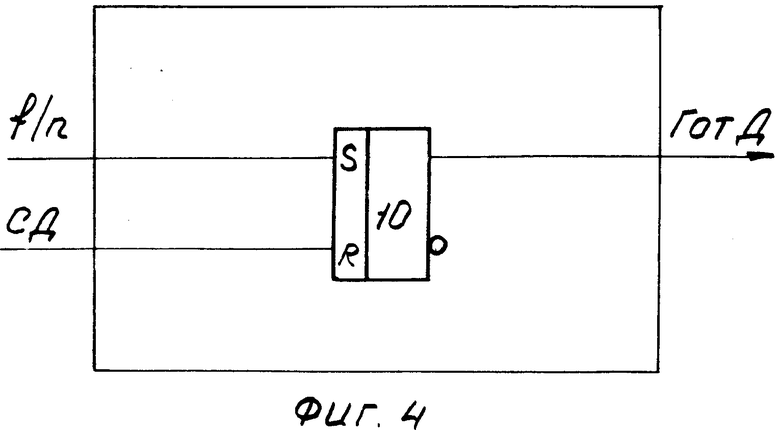

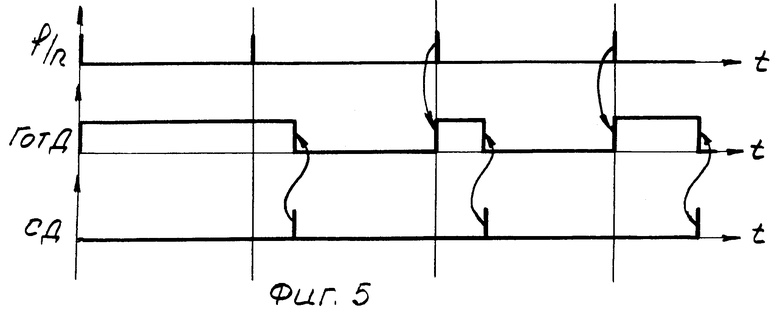

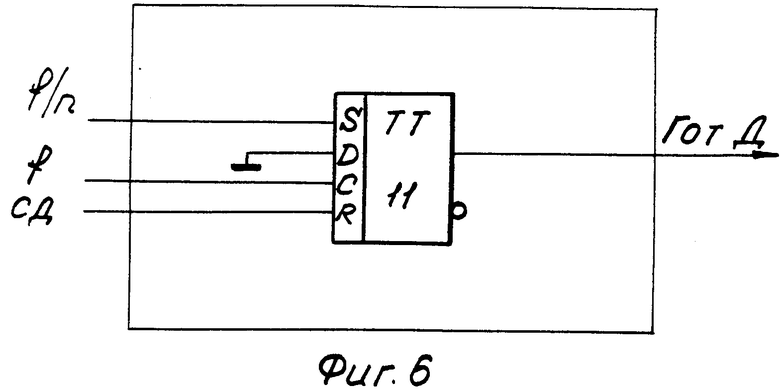

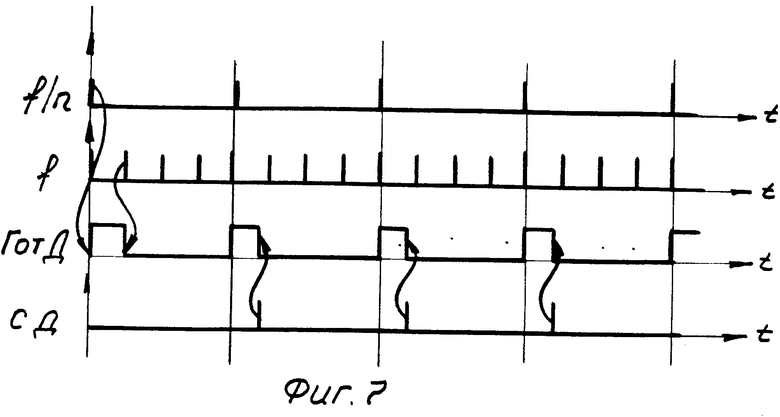

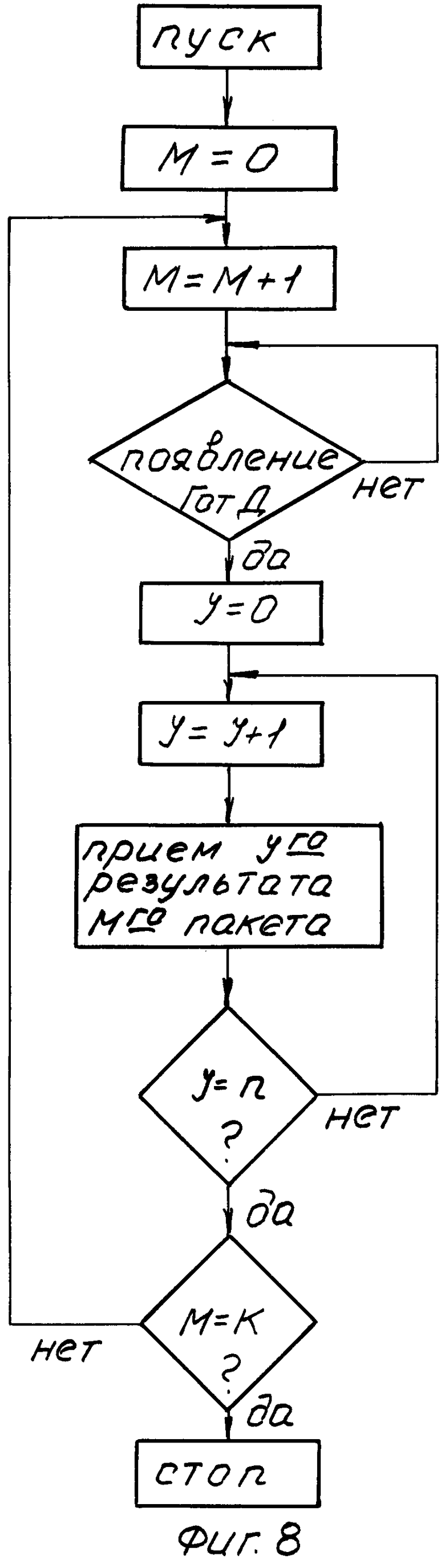

На фиг. 1 представлена схема заявляемого регистратора; на фиг. 2 и 3 - схема и временная диаграмма работы блока синхронизации, построенного на базе одновибратора; на фиг. 4 и 5 - схема и временная диаграмма работы блока синхронизации, выполненного на базе RS-триггера; на фиг. 6 и 7 - схема и временная диаграмма работы блока синхронизации, выполненного на базе D-триггера; на фиг. 8 - алгоритм работы приемника данных.

Многоканальный регистратор состоит из тактового генератора 1 и многоканального АЦП 2 с нормализаторами 3 на входах, формирователя 4 управления нормализаторами 3, подключенного выходом к управляющим входам нормализаторов 3, приемника 5 данных, счетчика-делителя 6, соединенного входом с выходом тактового генератора 1 и входом запуска АЦП 2, счетным выходом - с управляющим входом АЦП 2, запоминающего устройства 7, соединенного входом с выходом АЦП 2, выходом - с входом приемника 5 данных, входом управления записью - с выходом конца преобразования АЦП 2, синхровходом - с выходом деления либо со счетным выходом счетчика-делителя 6, входом управления считыванием - с выходом стробирования приемника 5 данных и блока 8 синхронизации, соединенного синхровходом с выходом деления счетчика-делителя 6, причем приемник 5 данных имеет управляющий вход, соединенный с выходом блока 8 синхронизации, а вход формирователя 4 управления нормализаторами 3 подключен к выходу деления либо счетному выходу счетчика-делителя 6 (фиг. 1). Блок 8 синхронизации выполнен в виде одновибратора 9, вход и выход которого являются синхровходом и выходом готовности блока 8 синхронизации соответственно; блок 8 синхронизации выполнен в виде RS-триггера 10, S- и R-входы и выход которого являются синхровходом, входом сброса готовности и выходом готовности блока 8 синхронизации соответственно, причем вход сброса готовности соединен с выходом стробирования приемника 5 данных; блок 8 синхронизации выполнен в виде D-триггера 11, S-, C- и R-входы и выход которого являются синхровходом, дополнительным синхровходом, входом сброса готовности и выходом готовности блока 8 синхронизации соответственно, причем D-вход триггера 11 соединен с шиной нулевого сигнала, а дополнительный синхровход - с выходом тактового генератора 1.

Регистратор работает следующим образом. Генератор 1 вырабатывает тактовые сигналы f системы, поступающие на счетчик-делитель 6 с коэффициентом деления (счета) n, равным числу нормализаторов 3 системы (фиг. 1). Счетчик-делитель 6 считает тактовые сигналы f и выдает на выходе деления сигнал f/n цикла нормализации через каждые n тактовых сигналов f, а на счетном выходе - кодовый сигнал или дешифрированный эквивалент числа считаемых тактовых сигналов f. АЦП 2 запускается каждым тактовыми сигналом f, а через управляющий вход последовательно в соответствии с сигналами со счетного выхода счетчика-делителя 6 подключает информационные входы для аналого-цифрового преобразования сигналов нормализаторов 3 с цикличностью, равной циклу нормализации (время преобразования нормализаторов 3). Все нормализаторы 3 работают синхронно, по управляющим сигналам формирователя 4 управления нормализаторами 3 запускаются синхронно с сигналом f/n цикла нормализации и по окончании его в следующем цикле имеют на своих устройствах выходной аналоговой памяти соответствующие результаты предыдущего цикла нормализации. Запоминающее устройство 7 принимает цифровые результаты с АЦП 2 по сигналам его конца преобразования, поступающим на вход управления записью запоминающего устройства 7. Однозначность порядка (начала) укладки в запоминающем устройстве 7 результатов в соответствии с расположением нормализаторов обеспечивается сигналами на синхровходе запоминающего устройства 7, которыми могут быть сигнал f/n цикла нормализации с выхода деления либо со счетного выхода счетчика-делителя 6. Считывание результатов из запоминающего устройства 7 осуществляется приемником 5 данных последовательно по сигналам на входе управления считыванием. Таким образом, нормализация входных сигналов, аналого-цифровое преобразование и запись результатов в запоминающее устройство 7 происходят циклически, безостановочно, синхронно с работой генератора 1 и счетчика-делителя 8 независимо от работы приемника 5 данных. Приемник 5 принимает пакет последовательных n результатов непосредственно после появления каждого сигнала на выходе готовности данных блока 8 синхронизации. Прием каждого результата в приемнике 5 данных сопровождается стробирующим сигналом на его выходе стробирования. Сигналы управления для приемника 5 данных вырабатываются блоком 8 синхронизации, исходным сигналом для работы которого является сигнал цикла нормализации на его синхровходе.

В простейшем случае блок 8 синхронизации представляет собой одновибратор 9 (фиг. 2), запускающийся сигналом f/n цикла нормализации и вырабатывающий импульс сигнала "ГотД" готовности данных длительностью не менее времени, необходимого на его анализ, цифровым устройством 5 и не более времени цикла нормализации, уменьшенного на ту же величину времени анализа (фиг. 3). Алгоритм работы приемника 5 данных показан на фиг. 8. Перед пуском системы в приемнике 5 данных отводят место для К пакетов по n результатов измерения. С пуском системы обнуляется счетчик пакетов в приемнике 5 данных оператором М=0, увеличивается на "1" оператором М=М+1 и приемник 5 приступает к анализу момента появления на его управляющем входе от блока 8 синхронизации сигнала "ГотД". Появлением "ГотД" считается факт наличия этого сигнала сразу же после его отсутствия (путем анализа самого сигнала "ГотД"). Если после анализа делается отрицательное заключение по появлению "ГотД" ("Нет"), приемник 5 возвращается на исходную позицию анализа; если положительное ("Да") - обнуляется счетчик результатов в текущем пакете (J= 0), увеличивается на "1" (J=J+1) и принимается приемником 5 J-й результат М-го пакета. Далее проверяется условие J=n, означающее, принят ли последний (n-й) результат пакета или нет. Если "Нет" - переход на оператор J=J+1, если "Да" - анализ условия М=К, означающего, принят ли последний К-й пакет или нет. Если "Нет" - переход на оператор М=М+1, если "Да" - "Стоп". Входные сигналы нормируются и заносятся в свои выходные устройства аналоговой памяти за время Тн цикла нормализации. АЦП 2 по сигналам со счетного выхода счетчика-делителя 6 (для переключения входов АЦП 2) и по сигналам f с генератора (для запуска АЦП 2) для каждого пакета вырабатывает последовательно n цифровых результатов, соответствующих сигналам на выходах n нормализаторов 3. При этом по окончании преобразования каждого результата своим сигналом конца преобразования АЦП 2 переписывает его в запоминающее устройство 7. Приемник 5 принимает последовательно n результатов измерения из запоминающего устройства 7 по каждому сигналу "ГотД". Следовательно, пакеты результатов измерений поступают в приемник с периодом, равным времени Тн цикла нормализации, что существенно меньше, чем у прототипа.

Блок 8 синхронизации может быть выполнен с входом сброса готовности, соединенным с выходом стробирования приемника 5 данных, например, на базе RS-триггера 10, S, R-входы и выход которого являются синхровходом, входом сброса готовности и выходом готовности блока 8 синхронизации соответственно (фиг. 4). В этом случае триггер 10 устанавливается в "1" (выставление "ГотД") сигналом f/n цикла нормализации на синхровходе блока 8 синхронизации, а в "0" (сбрасывание "ГотД") - сигналом "СД" стробирования приемника 5 данных на входе сброса готовности (фиг. 5). Сигнал на выходе триггера 10 является сигналом "ГотД".

Блок 8 синхронизации может быть выполнен с дополнительным синхровходом, соединенным с выходом тактового генератора 1, например, на базе D-триггера 11 (фиг. 6). Установка триггера 11 в "1" при формировании на его выходе сигнала "ГотД" осуществляется сигналом f/n цикла нормализации на синхровходе блока 8 синхронизации. Сброс сигнала "ГотД" записью "0" в триггер 11 осуществляется сигналом "СД" стробирования на входе сброса готовности блока 8 синхронизации при приеме результатов (данных) приемником 5 данных. Если прием данных не начат в начале цикла нормализации, то сигнал "ГотД" сбрасывается сигналом f на дополнительном синхровходе блока 8 синхронизации (фиг. 7), что гарантирует прием данных без риска искажения при попадании на момент смены результатов в запоминающем устройстве 7 в начале цикла нормализации в случае, когда приемник 5 данных по каким-либо причинам задержался с приемом данных, соответствующих выданному сигналу "ГотД". В обоих последних вариантах выполнения блока 8 синхронизации в алгоритме приемника 5 данных не требуется анализировать "появление" сигнала "ГотД" - достаточно установить факт его наличия.

В качестве многоканального АЦП 2 в системе может быть использован один АЦП с аналоговым коммутатором входов либо АЦП с цифровым коммутатором на выходе. При связи синхровхода запоминающего устройства 7 со счетным выходом счетчика-делителя 6 переключение адреса принимаемых цифровых результатов осуществляется кодом счетчика-делителя 6, при связи с выхода деления в запоминающем устройстве 7 должен быть свой счетчик сигналов по входу управления записью с синхронизацией его по синхровходу запоминающего устройства 7 сигналом с выхода деления счетчика-делителя 6. Запоминающее устройство 7 может быть и однопортовым, но потребуется АЦП с более высоким быстродействием, чем в случае двухпортового запоминающего устройства 7. При двухпортовом запоминающем устройстве 7 переключение портов осуществляется по сигналам синхровходах. В качестве приемника 5 данных могут быть использованы микропроцессоры, мини- и микроЭВМ или специальные цифровые автоматы и цифровые регистраторы. Приведены: простейший вариант выполнения блока 11 синхронизации с использованием одновибратора 9 и на триггерах 10 и 11 со сбросом готовности. Возможны и другие модификации выполнения блока 8 синхронизации и алгоритмов работы приемника 5 данных. Вместо триггера 10 (фиг. 4) можно использовать счетчик с дешифратором для снятия сигнала "ГотД" по последнему результату в пакете, что может упростить алгоритм приемника 5 во время приема пакета результатов за счет исключения алгоритмического (программного) счета номеров результатов в пакете. Для случаев, когда стробирующие сигналы не используются для сбросов готовностей, в алгоритмах должен присутствовать для сигналов готовностей анализ их "появления"; если используются, то анализ их наличия. Формирователь 4 управления нормализаторами 3 выполняет задачу выработки необходимых сигналов функционирования нормализаторов 3. Конкретное исполнение его зависит от принципа, заложенного в работу нормализаторов 3. На вход его должен быть подан сигнал, позволяющий синхронизировать работу нормализаторов 3 с работой счетчика-делителя 6, чтобы обеспечить циклическую работу нормализаторов 3 синхронно с рассмотренными ранее блоками.

Изобретение обладает существенно большим быстродействием. Постоянный циклический режим работы нормализаторов и АЦП положительно сказывается на точности результатов измерения за счет улучшения их повторяемости. Возможность построения АЦП с коммутатором на входе устраняет погрешности из-за неидентичности аналого-цифрового преобразования для разных нормализаторов, существенно упрощает и удешевляет конструкцию регистратора, увеличивая, кроме того, его надежность и уменьшая затраты на метрологическое обеспечение. Все это выгодно отличает данное техническое решение от ранее известных.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020422C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020421C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020424C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020423C1 |

| Устройство для обнаружения и регистрации сейсмических и сейсмоакустических сигналов | 1987 |

|

SU1434383A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Способ регистрации сигналов при ультразвуковом контроле и устройство для его осуществления | 1989 |

|

SU1820319A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| ИЗМЕРИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2018173C1 |

| Устройство для ультразвукового измерения размеров глаза | 1986 |

|

SU1510842A1 |

Изобретение относится к приборостроению, в частности к электроизмерительной технике. Целью изобретения является повышение быстродействия, точности и надежности регистратора. Многоканальный регистратор содержит тактовый генератор (ТГ), многоканальный АЦП с нормализаторами (Н) на входах, формирователь управления нормализаторами (ФУН), подключенный выходом к управляющим входам Н, и приемник данных (ПД), а также счетчик-делитель (СД), запоминающее устройство (ЗУ) и блок синхронизации (БС), синхровход которого соединен с выходом деления СД, вход которого соединен с выходом ТГ и входом запуска АЦП, а счетным выходом - с управляющим входом АЦП, выход которого соединен с инфромационным входом ЗУ, выход которого соединен с входом: вход управления записью - с выходом конца преобразования АЦП, синхровод - с выходом деления или со счетным выходом СД, а управляющий вход - с выходом стробирования ПД, управляющий вход которого соединен с выходом БС. Вход ФУН подключен к выходу деления или счетному выходу СД. БС выполнен в виде одновибратора, вход и выходд которого являются синхровходом и выходом готовности БС соответственно, БС выполнен в виде RS - триггера, S- и R - вход и выход которого являются синхровходом, входом сброса готовности и выходом готовности БС соответственно, причем вход сброса готовности соединен с выходом стробирования ПД. БС выполнен в виде D-триггера, S-, C- и R-входы и выход которого являются синхровходом, дополнительным синхровходом, входом сброса готовности и выходом готовности БС соответственно, причем D-вход триггера соединен с шиной нулевого сигнала, а дополнительный синхровход - с выходом ТГ. 3 з.п.ф-лы, 8 ил.

| Труды ЦАГИ, М., ЦАГИ, 1984, вып.2227, с.12. |

Авторы

Даты

1994-09-30—Публикация

1990-07-10—Подача