Изобретение относится к приборостроению, в частности к электроизмерительной технике, и может быть использовано в тензо- и термометрии для измерения сигналов тензо- и термодатчиков.

Известен регистратор (система "Прочность"), предназначенный для автоматизации процессов измерения, сброса и обработки информации преобразователей различных величин, характеризующих тепловое, деформационное и напряженное состояние конструкций. Система состоит из нескольких измерительных подсистем (четырех) с двумя измерительными каналами каждая, устройства управления и обмена и ЭВМ. Измерительные сигналы в каждом канале через коммутаторы поступают на измерительный модуль, представляющий собой преобразователь сигналов датчиков в напряжение и АЦП на выходе, цифровые сигналы которого поступают через информационную шину цифровой части системы в ЭВМ. Поскольку получение цифрового результата измерения в АЦП (уравновешивание) проходит при совместной работе преобразователя сигналов датчиков, датчиков и линий связи, получение результата измерения требует большого времени из-за неизбежных переходных процессов, связанных с уравновешиванием измерительной цепи [1].

Наиболее близкой по технической сущности и достигаемому эффекту является система "Ресурс 23/27", состоящая из восьми нормализаторов с соответствующими коммутаторами на входе и блоком АЦП на выходе. Для формирования временной диаграммы управления работой системы имеется тактовый генератор и один общий формирователь управления нормализаторами на их управляющих входах. Результаты измерения из блока АЦП поступают в ЭВМ. Блок АЦП с восемью аналоговыми входами и одним цифровым выходом представляет собой многоканальный АЦП. ЭВМ, осуществляющая цифровое управление коммутаторами и принимающая цифровые результаты измерения (данные), по существу выполняемых функций является цифровым устройством управления и приема данных, которое может быть реализовано не только ЭВМ как таковой, а и микропроцессорами, цифровыми автоматами, цифровыми регистраторами и т.д. В этой системе существенно увеличено быстродействие за счет введения нормализаторов, не требующих участия в аналого-цифровом преобразовании сигналов датчиков. Однако для ряда задач (например, ресурсные испытания конструкций с количеством входов системы, достигающим тысяч и даже десятков тысяч) общее время измерения сигналов со всех входов оказывается значительным. Пусть D- число входов, подключенных через коммутатор к одному нормализатору. Тогда общее время измерения системой всех входных сигналов определится выражением

Т=D(Тпуск+Тк+Тн+Тацп+Тприем+Твозврат)

или

Т=DТн+D(Тпуск+Тк+Тацп+

+ Тприем+Твозврат), где Тпуск - время прохождения команды "Пуск" до ее исполнения; Тк - временная задержка для установления режима ключевых элементов коммутаторов; Тн - время нормализации сигналов в нормализаторе; Тацп - время работы АЦП; Тприем - время приема результатов измерения; Твозврат - время возврата системы на исходную позицию; D - число каналов нормализации (число нормализаторов) системы.

К недостаткам следует отнести СТАРТ/СТОП-ный режим работы нормализаторов, отрицательно сказывающийся на точности результатов нормализации из-за неритмичности запуска нормализаторов. Построение блока АЦП (многоканального АЦП) из восьми отдельных АЦП добавляют в результаты измерения дополнительную погрешность из-за неидентичности точностных характеристик отдельных АЦП и существенно усложняет и удорожает конструкцию системы, уменьшая, кроме того, ее надежность и увеличивая затраты на метрологическое обеспечение. Управление коммутаторами осуществляется от ЭВМ через единый регистр команд для всех нормализаторов параллельно, что не позволяет измерять одновременно сигналы различных входов для разных нормализаторов.

Целью изобретения является повышение быстродействия, точности и надежности регистратора.

Цель достигается тем, что в многоканальный регистратор, содержащий тактовый генератор, многоканальный аналого-цифровой преобразователь с последовательно соединенными коммутатором и нормализатором на каждом входе, цифровое устройство управления и приема данных, регистр команд на управляющем входе одного из коммутаторов и формирователь управления нормализаторами, подключенный выходом к управляющим входам нормализаторов, в него введены дополнительные регистры команд, подключенные к управляющим входам остальных коммутаторов, счетчик-делитель, запоминающее устройство команд и данных, блок синхронизации, синхровход которого соединен с выходом деления счетчика-делителя, вход которого соединен с выходом тактового генератора и входом запуска аналого-цифрового преобразователя, выход конца преобразования и информационные выходы которого соединены соответственно с управляющими и информационными входами запоминающего устройства данных, информационные выходы и управляющий вход считывания которого соединены соответственно с информационными входами и выходом стробирования цифрового устройства управления и приема данных, управляющий вход команд которого соединен с выходом готовности приема команд блока синхронизации, а выходы команд и стробирования соединены соответственно с входами команд и стробирования запоминающего устройства команд, выходы которого соединены с информационными входами регистров команд, входы записи которых соединены с выходом деления счетчика-делителя, вход формирователя управления нормализаторами соединен с выходом деления или со счетным выходом счетчика-делителя, синхровход запоминающего устройства данных соединен с выходом деления или со счетным выходом счетчика-делителя, управляющий вход аналого-цифрового преобразователя соединен со счетным выходом счетчика-делителя; блок синхронизации выполнен в виде одновибратора, вход и выход которого являются синхровходом и выходом готовности приема команд блока синхронизации соответственно; блок синхронизации состоит из элементов задержки, И и ИЛИ, сдвигового регистра и трех RS-триггеров, синхровход блока синхронизации соединен с S- входами первого и второго триггеров, R-входом третьего триггера, С-входом регистра и входом элемента задержки, вход сброса готовности приема команд - с первым входом элемента ИЛИ и S-входом третьего триггера, выход элемента задержки - с вторым входом элемента ИЛИ, выходы второго и третьего триггеров, регистра и элемента ИЛИ - соответственно с первым входом элемента И, D-входом регистра, вторым входом элемента И и R-входом первого триггера, причем входом сброса готовности данных, выходами готовностей приема команд и данных являются соответственно R-вход второго триггера, выходы первого триггера и элемента И, а выход готовности данных, вход сброса готовности приема команд и вход сброса готовности данных блока синхронизации соединены соответственно с управляющим входом данных, выходом стробирования команд и выходом стробирования данных цифрового устройства управления и приема данных.

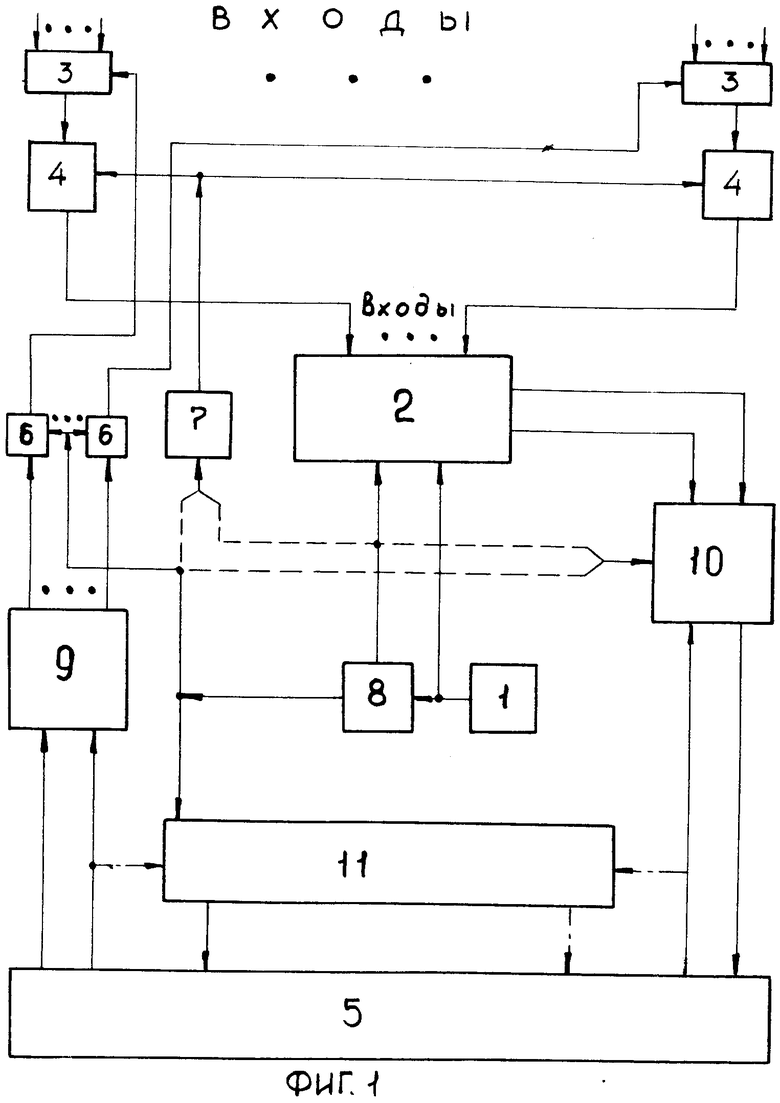

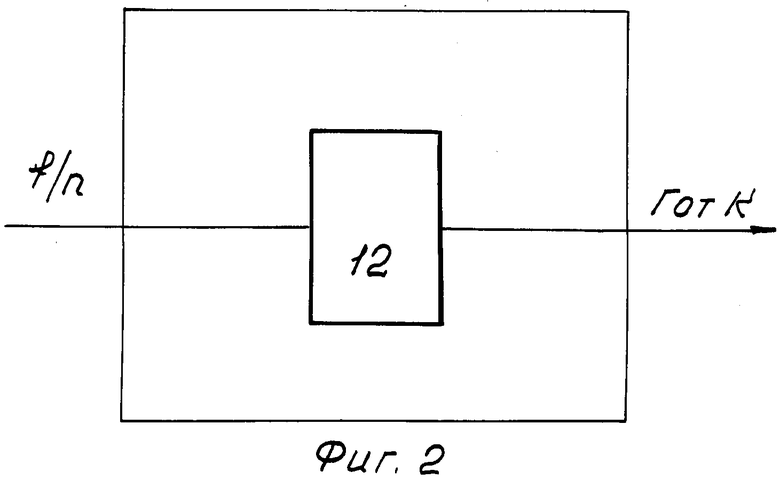

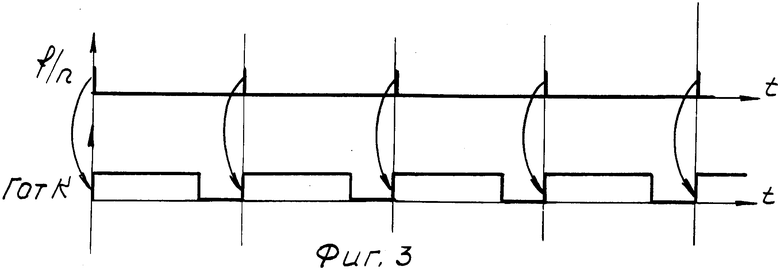

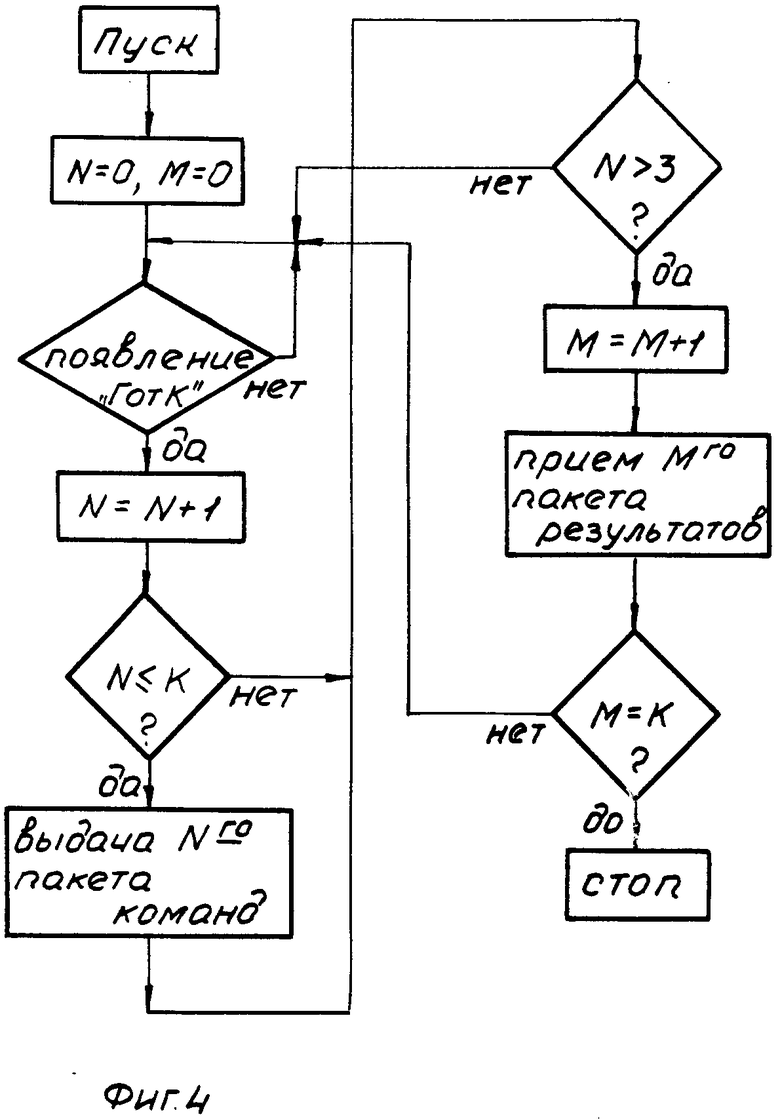

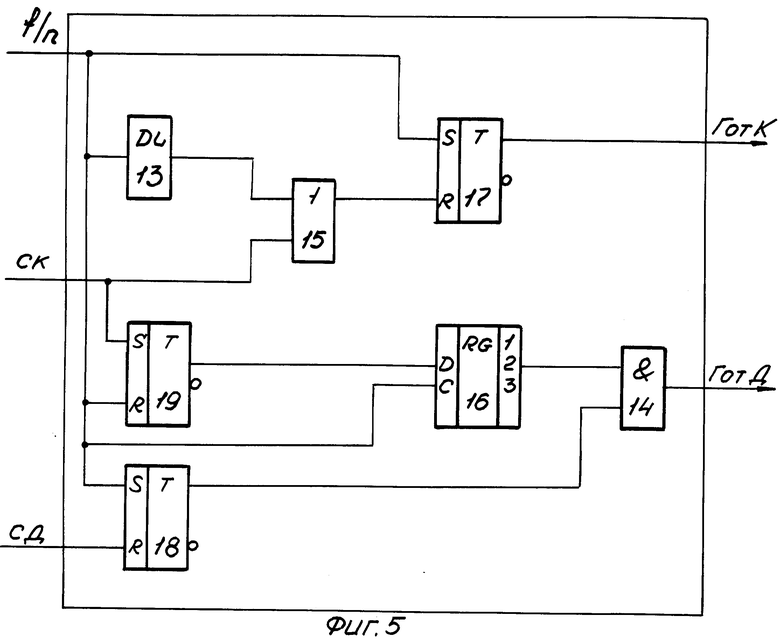

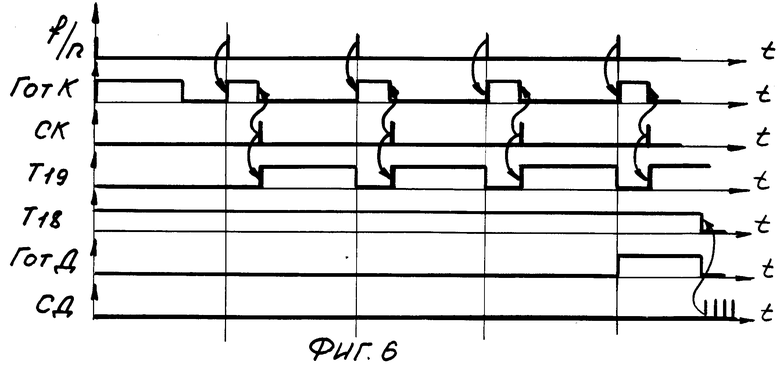

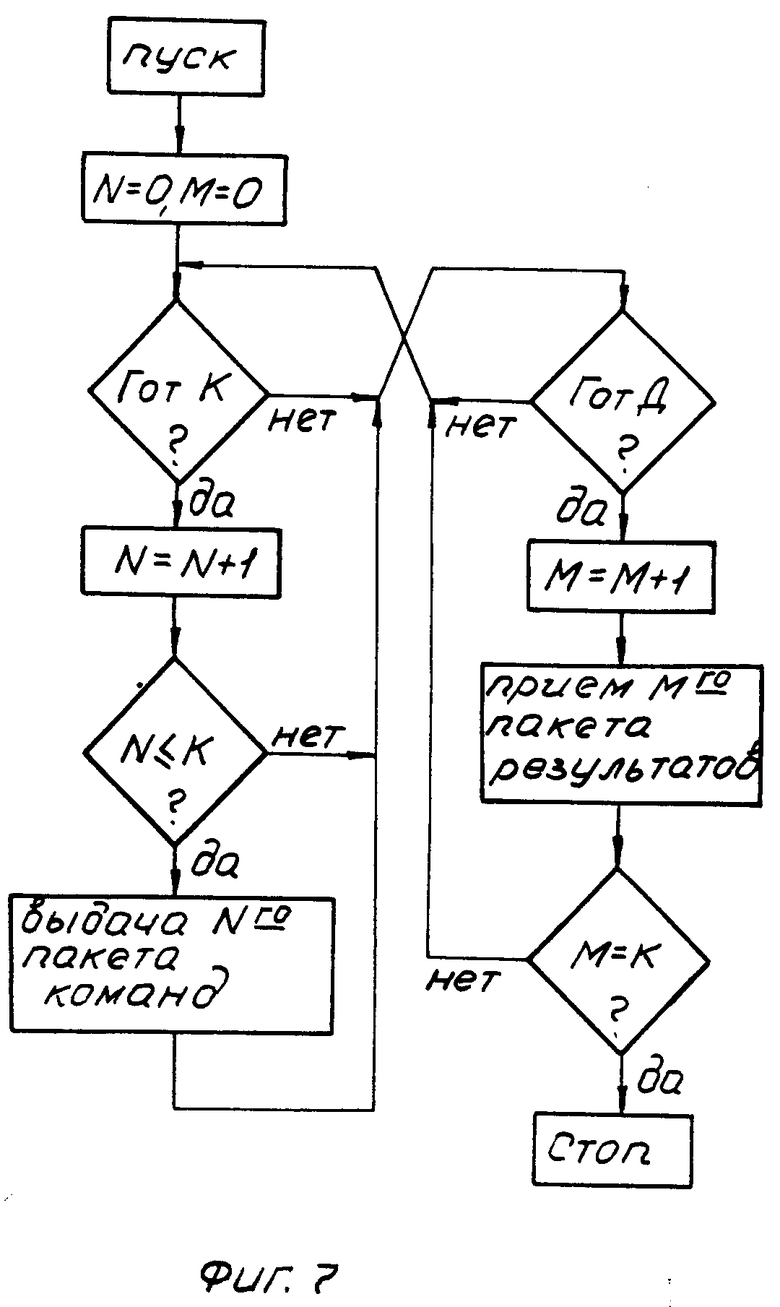

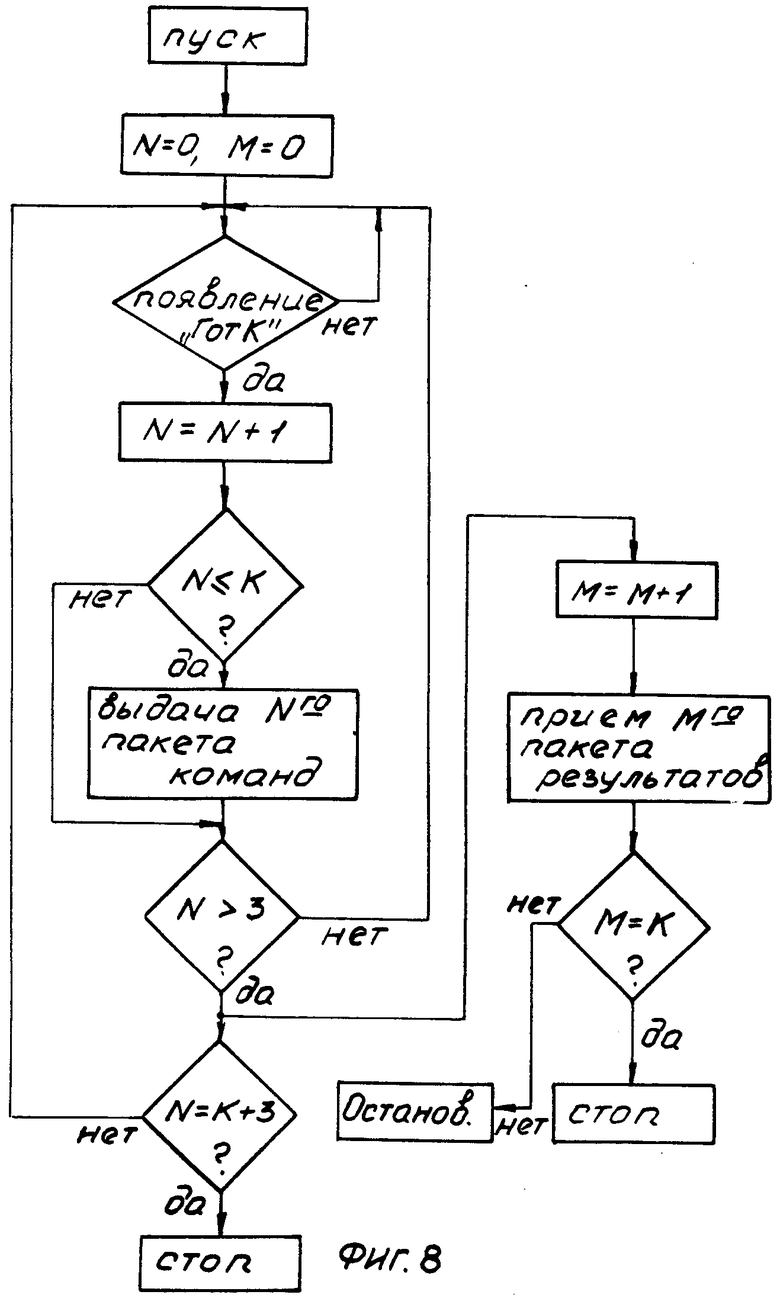

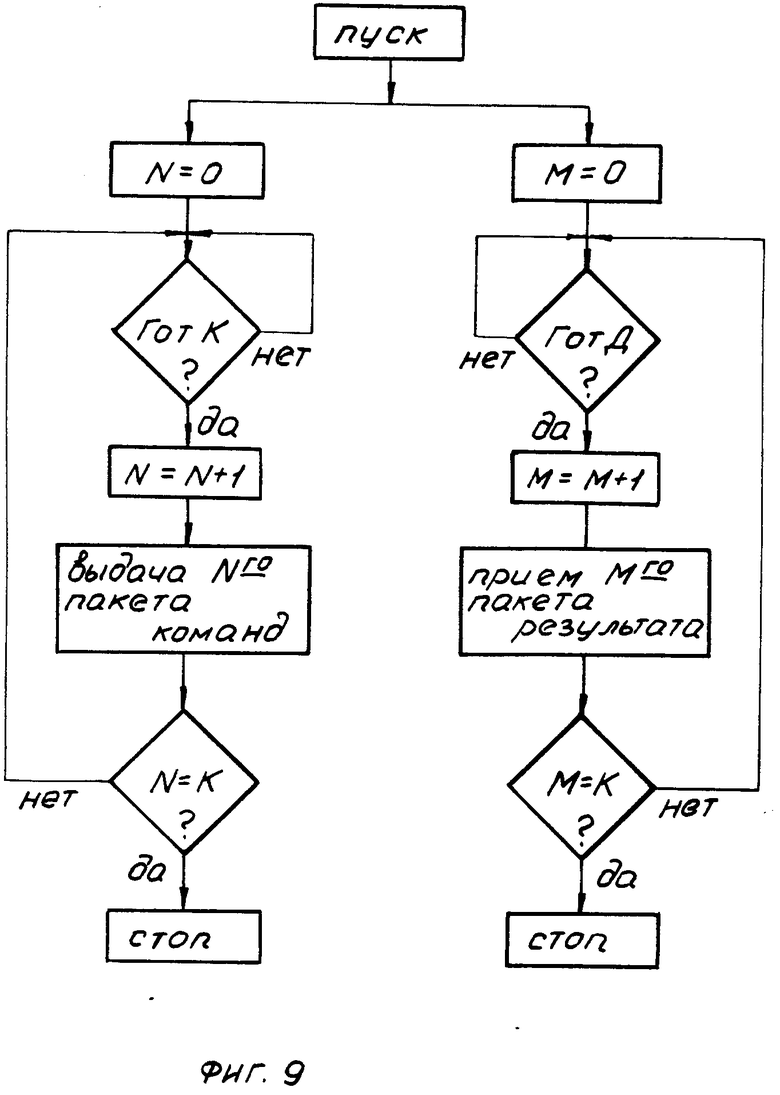

На фиг. 1 представлена схема заявляемого многоканального регистратора; на фиг. 2, 3 и 4 - схема, временная диаграмма работы блока синхронизации, выполненного на базе одновибратора, и соответствующий алгоритм работы цифрового устройства управления и приема данных; на фиг. 5, 6 и 7 - схема, временная диаграмма работы блока синхронизации, построенного на базе триггеров, и соответствующий алгоритм работы цифрового устройства управления и приема данных при построении его в виде двух независимых устройств (цифрового устройства управления и цифрового устройства приема данных) для указанных вариантов выполнения блока синхронизации.

Многоканальный регистратор состоит из тактового генератора 1, многоканального АЦП 2 с последовательно соединенными коммутатором 3 и нормализатором 4 на каждом входе, цифрового устройства 5 управления и приема данных, регистров 6 команд на управляющих входах коммутаторов 3, формирователя 7 управления нормализаторами 4, подключенного выходом к управляющим входам нормализаторов 4, счетчика-делителя 8, соединенного входом с выходом генератора 1 и входом запуска АЦП 2, счетным выходом - с управляющим входом АЦП 2, выходом деления с входами записи регистров 6 команд, запоминающего устройства 9 команд, соединенного выходами с входами регистров 6 команд соответственно, входами команд и стробирования - с выходами команд и стробирования команд цифрового устройства 5 управления и приема данных соответственно, запоминающего устройства 10 данных, соединенного входами данных и управления записью с выходами данных и конца преобразования АЦП 2, выходом и входом управления считыванием - с входом и выходом стробирования данных цифрового устройства 5 управления и приема данных соответственно, синхровходом - со счетным выходом либо выходом деления счетчика-делителя 8, блока 11 синхронизации, соединенного синхровходом с выходом деления счетчика-делителя 8, причем цифровое устройство 5 управления и приема данных имеет управляющий вход команд, соединенный с выходом готовности приема команд блока 11 синхронизации, а вход формирователя 7 управления нормализаторами 4 подключен к выходу деления либо счетному выходу счетчика-делителя 8 (фиг. 1). Цифровое устройство 5 управления и приема данных имеет управляющий вход данных, соединенный с выходом готовности данных блока 11 синхронизации. Блок 11 синхронизации имеет вход сброса готовности приема команд, соединенный с выходом стробирования команд цифрового устройства 5 управления и приема данных. Блок 11 синхронизации имеет вход сброса готовности данных, соединенный с выходом стробирования данных цифрового устройства 5 управления и приема данных. Блок 11 синхронизации выполнен в виде одновибратора 12, вход и выход которого являются синхровходом и выходом готовности приема команд соответственно (фиг. 2). Блок 11 синхронизации состоит из элемента 13 задержки, элементов И и ИЛИ 14 и 15, сдвигового регистра 16 и RS-триггеров 17-19, синхровход блока синхронизации соединен с S-входами первого 17 и второго 18 триггеров, R-входом третьего триггера 19, С-входом регистра 16 и входом элемента 13 задержки, вход сброса готовности приема команд - с первым входом элемента ИЛИ 15 и S-входом третьего триггера 19, выход элемента 13 задержки - с вторым входом элемента ИЛИ 15, выходы второго 18 и третьего 19 триггеров, регистра 16 и элемента ИЛИ 15 - соответственно с первым входом элемента И 14, D-входом регистра 16, вторым входом элемента И 14 и R-входом первого триггера 17, причем входом сброса готовности данных, выходом готовностей приема команд и данных являются соответственно R-вход второго триггера 18, выходы первого триггера 17 и элемента И 14 (фиг. 5).

Регистратор работает следующим образом. Генератор 1 вырабатывает тактовые сигналы f системы, поступающие на счетчик-делитель 8 с коэффициентом деления (счета) n, равным числу нормализаторов 4 системы (фиг. 1). Счетчик-делитель 8 считает тактовые сигналы f и выдает на выходе деления сигналы f/n цикла нормализации через каждые n тактовых сигналов f, а на счетном выходе - кодовый или дешифрированный эквивалент числа считываемых тактовых сигналов f. АЦП 2 запускается каждым тактовым сигналом f, а через управляющий вход последовательно в соответствии с сигналами со счетного выхода счетчика-делителя 8 подключает информационные входы для аналого-цифрового преобразования сигналов нормализаторов с цикличностью, равной циклу нормализации (время преобразования нормализаторов). Все нормализаторы 4 работают параллельно, по управляющим сигналам формирователя 7 управления нормализаторами 4, запускаются одновременно синхронно с сигналом f/n цикла нормализации и по окончании его в следующем цикле имеют на своих устройствах выходной аналоговой памяти соответствующие результаты предыдущего цикла нормализации. Запоминающее устройство 10 данных принимает цифровые результаты с АЦП 2 по сигналам его конца преобразования, поступающим на вход управления записью запоминающего устройства 10. Однозначность порядка (начала) укладки в запоминающем устройстве 10 результатов в соответствии с расположением нормализаторов обеспечивается сигналами на синхровходе запоминающего устройства 10, которыми могут быть сигнал f/n цикла нормализации с выхода деления либо со счетного выхода счетчика-делителя 8. Считывание результатов из запоминающего устройства 10 осуществляется цифровым устройством 5 последовательно по сигналам на входе управления считыванием. Запоминающее устройство 9 команд имеет для команд один вход и n выходов. Входные командные цифровые сигналы поступают из устройства 5 в запоминающее устройство 9 последовательно и имеют адресную часть, в соответствии с которой происходит запись и выдача на соответствующие выходы соответствующих командных сигналов, которые хранятся до поступления новых. Командные сигналы поступают на входы регистров 6 в соответствии с выходами запоминающего устройства 9, переписываются в регистры 6 по сигналам f/n цикла нормализации с выхода деления счетчика-делителя 8 и поступают на управляющие входы коммутаторов 3, в соответствии с чем и происходит подключение входов регистратора к нормализаторам. Таким образом, подключение коммутаторами 3 входов к нормализаторам 4 в соответствии с командами, имеющимися на выходах запоминающего устройства 9, нормализация входных сигналов, аналого-цифровое преобразование и запись результатов в запоминающее устройство 10 происходят циклически, безостановочно, синхронно с работой генератора 1 и счетчика-делителя 8 независимо от работы цифрового устройства 5 управления и приема данных. Устройство 5 выдает пакет последовательных n команд непосредственно после каждого появления сигнала на его управляющем входе команд и принимает пакет последовательных n результатов (при наличии управляющего входа данных непосредственно после появления каждого сигнала на выходе готовности данных блока 11 синхронизации). Соответствие пакетов команд и данных и их состава осуществляется в цифровом устройстве 5 путем сопоставления последовательности исходно установленных команд с последовательностью принятых данных.

Выдача каждой команды и прием каждого результата соответственно в цифровом устройстве 5 сопровождаются стробирующим сигналом на его выходах стробирования. Сигналы управления для цифрового устройства 5 вырабатываются блоком 11 синхронизации, исходным сигналом для работы которого является сигнал цикла нормализации на его синхровходе.

В простейшем случае блок 11 синхронизации представляет собой одновибратор (фиг. 2), запускающийся сигналом f/n цикла нормализации и вырабатывающий импульс сигнала "ГотК" готовности приема команд длительностью не менее времени, необходимого на его анализ цифровым устройством 5, и не более времени самого цикла нормализации (фиг. 3). Алгоритм работы цифрового устройства 5 в этом случае показан на фиг. 4. Перед началом обмена регистратора с цифровым устройством 5 в нем устанавливают К последовательных пакетов по n последовательных команд и отводят место и устанавливают порядок для такого же числа последовательных результатов. С пуском регистратора обнуляются счетчики циклов в устройстве 5 операторами N=0, М=0 и устройство 5 приступает к анализу момента появления на его управляющем входе команд от блока 11 синхронизации сигнала "ГотК". Появлением "ГотК" считается факт наличия этого сигнала сразу же после его отсутствия (путем анализа самого сигнала "ГотК"). Если после анализа делается отрицательное заключение по появлению "ГотК" ("Нет"), устройство 5 возвращается на исходную позицию анализа; если положительное ("Да") - число N счетчика циклов увеличивается на "1" (N= N+1). Далее проверяется условие N<К, означающее, имеются ли еще не выполненные команды в объеме установленных перед пуском в устройстве 5. Если "Да", то на выход выдается N-й пакет последовательных n команд; если "Нет" - выдача пропускается. Затем проводится анализ условий N>3, определяющее появление результатов, предназначенных для приема устройством 5 ("3" - количество циклов нормализации, на которое запаздывает появление результата измерения, соответствующего команде, выданной ранее). Если "Нет" (т.е. результатов измерения, соответствующих выданным командам, готовых к приему еще нет), то устройство 5 возвращается на исходную позицию анализа появления готовности "ГотК", если "Да", то устройство 5 приступает к приему М-го пакета результатов с предварительным увеличением на "1" числа М счетчика циклов (М=М+1). Далее проводится анализ конца операций оператором N=К+3, определяющего максимальное число счетчика циклов устройства 5, соответствующего приему последнего результата измерения. Если "Нет", устройство 5 возвращается на исходную позицию; если "Да" - останавливается командой "СТОП".

Проследим работу, соответствующую первому пакету команд. После запуска системы устройство 5 дожидается появления "ГотК" от блока 11 синхронизации (в среднем в течение времени Тпуск, равного половине времени Тн цикла нормализации) и выдает пакет из n команд, который записывает в запоминающее устройство 9 команд. Команды с выходов запоминающего устройства 9 поступают на входы регистров 6. По следующему (второму) сигналу f/n цикла нормализации (сигнал "ГотК" синхронен с сигналом f/n цикла нормализации (см. фиг. 3)) происходит запись команд в регистры 6, подключение соответствующих входов к нормализаторам 4 и их запуск. За время Тн цикла нормализации входные сигналы нормируются и заносятся в свои выходные устройства аналоговой памяти. Начиная с 3-го сигнала f/n цикла нормализации АЦП 2 по сигналам со счетного выхода счетчика-делителя 8 (для переключения входов АЦП 2) и по сигналам f с генератора (для запуска АЦП 2) вырабатывает последовательно n цифровых результатов, соответствующих сигналам на выходах нормализаторов 4. При этом по окончании преобразования каждого результата своим сигналом конца преобразования АЦП 2 переписывает его в запоминающее устройство 10 данных. С момента начала 4-го сигнала f/n устройство 5 принимает пакет (последовательно n) результатов измерения из запоминающего устройства 10. Следовательно, пакет результатов измерения запаздывает по отношению к моменту выдачи соответствующего пакета команд на время 3Тн. Работа по второму, третьему и т. д. пакетам команд идет аналогично последовательно со сдвигом на Тн. Поэтому общее время измерения регистратором будет равно

Т=Тпуск+DТн+2Тн+Тприем, гдеТпуск и Тприем<< Тн.

При D>>1 (в многоточечных системах соблюдается практически всегда) Т= DТн, что существенно меньше, чем у прототипа.

Блок 11 синхронизации может быть выполнен и с выходом готовности данных (сигнал "ГотД"), подключенным к управляющему входу данных устройства 5. В этом случае управляющий сигнал "ГотД" для устройства 5 вырабатывает в блоке 11 синхронизации, а не алгоритмическим (программным) путем в устройстве 5. Можно использовать стробирующие сигналы устройства 5 для сброса готовностей в блоке 11 синхронизации, в результате чего не потребуется в устройстве 5 проводить ряд логических операций по выявлению появления готовностей (достаточно установить факт их наличия). Все это облегчает реализацию устройства 5 и упрощает его алгоритм, что создает дополнительную возможность упрощения и увеличения быстродействия системы. Выполнение блока 11 синхронизации с выходами "ГотК" и "ГотД", а также с входами сброса готовностей показано на фиг. 5, временная диаграмма на фиг. 6 поясняет его работу. В этом случае устройство 5 работает по следующему алгоритму (фиг. 7). Как и ранее перед пуском регистратора в устройстве 5 устанавливают К пакетов по n команд и отводят место для такого же числа результатов. С пуском регистратора числа N и М счетчиков циклов в устройстве 5 обнуляются (N=0, М=0) и устройство 5 приступает к анализу наличия сигнала "ГотК". Если для анализируемого момента времени готовности нет, происходит переход на анализ сигнала "ГотД"; если готовность есть, число N соответствующего счетчика увеличивается на "1", после чего проверяется условие N<К, означающее, имеются ли еще не выполненные команды в объеме установленных перед пуском в устройстве 5. Если "Да", то на выход выдается N-й пакет команд; если "Нет" - выдача пропускается. Затем (или на начальном этапе перехода от анализа "ГотК" при "Нет") проводится анализ сигнала "ГотД". Если сигнала "ГотД" нет, происходит переход на исходную позицию анализа "ГотК"; если "Да", число М соответствующего счетчика увеличивается на "1" (М=М+1) и устройством 5 проводится прием М-го пакета результатов из запоминающего устройство 10 данных. На конечном этапе алгоритма проверяется условие М=К, означающее, все ли результаты (данные) от поданных команд получены. Если "Нет" - возврат на исходную позицию анализа сигнала "ГотК", если "Да" - СТОП.

Сигналом f/n цикла нормализации триггер 17 устанавливается в "1" (формируется сигнал "ГотК"), сдвиговый регистр 16 - в состояние триггера 19 (соответствующего наличию или отсутствию сигнала сброса готовности команд в предыдущем цикле нормализации, т. е. была или отсутствовала передача команд), триггер 19 - в "0" ("0" - устанавливается или подтверждается), триггер 18 - в "1" (разрешается через элемент И 14 проход сигнала, если он есть, сдвигового регистра 16 в качестве сигнала "ГотД" на выход блока 11 синхронизации), а в сдвиговом регистре 16 осуществляется сдвиг на 3 цикла нормализации сигналов, записанных через D-вход с триггера 19 (отражающий запаздывание появления соответствующих результатов после передачи команд). Сигналом сброса готовности данных триггер 18 устанавливается в "0" и через элемент И 14 снимает (блокирует) сигнал "ГотД" на выходе блока 11 синхронизации. В отсутствие сигнала готовности команд (передача команд отсутствует, т. е. регистратор находится в режиме "Все команды выданы - ожидание следующего ПУСКа регистратора") по истечении некоторого времени, заданного элементом 13 задержки, сигнал "ГотК" самосбрасывается в триггере 17 через элемент ИЛИ 15. Время задержки, формируемое элементом 13, определяется временем, необходимым с гарантией для анализа сигнала "ГотК" цифровым устройством 5 управления и приема данных, но не более времени цикла нормализации, уменьшенного на ту же величину времени анализа.

В качестве многоканального АЦП 2 в системе может быть использован один АЦП с аналоговым коммутатором входов (см. Хоровиц П., Хилл У. Искусство схемотехники. Т.2. М.: Мир, 1984, с. 69, рис. 9.47), либо n АЦП с цифровым коммутатором на выходе (см. Труды ЦАГИ. М. Издательский отдел ЦАГИ, 1984, вып. 2227, рис. 1 и 3). Известны стандартные счетчики-делители, например микросхема 564ИЕ11. В системе используются известные запоминающие устройства: запоминающее устройство команд (см. Шило В.Л. Популярные цифровые микросхемы. Справочник. М.: Радио и связь, 1988, с. 121, рис. 186), запоминающее устройство данных (см. Система КАМАК. Запоминающее устройство ФК701. Руководство по эксплуатации Ба 3.065.000 РЭ. Вильнюсский завод электронной техники). При связи синхровхода запоминающего устройства 10 данных со счетным выходом счетчика-делителя 8 переключение адреса принимаемых цифровых результатов осуществляется кодом счетчика-делителя 8, при связи с выхода деления в запоминающем устройстве 10 должен быть свой счетчик сигналов по входу управления записью с синхронизацией его по синхровходу запоминающего устройства 10 сигналом с выхода деления счетчика-делителя 8. Запоминающее устройство 10 может быть и однопортовым, но потребуется АЦП с более высоким быстродействием, чем в случае двухпортового запоминающего устройства. При двухпортовом запоминающем устройстве переключение портов осуществляется по сигналам синхровхода. В качестве цифрового устройства 5 управления и приема данных могут быть использованы микропроцессоры, мини- и микроЭВМ или специальные цифровые автоматы. Рассмотренный вариант алгоритмов предназначен для использования одной общей ЭВМ для выполнения функции управления и приема данных: через выходной регистр ЭВМ - передача команд, через входной регистр - прием данных, через регистр команд и состояний - принятие сигналов готовностей. Возможен вариант выполнения цифрового устройства 5 управления и приема данных в виде двух отдельных устройств: программатора команд и приемника данных с соответствующими функциями, в качестве которых могут быть использованы микропроцессоры, цифровые автоматы и отдельные ЭВМ. На фиг. 8 и 9 приведены для этого случая соответствующие алгоритмы, аналогичные рассмотренным, где левая часть соответствует программатору команд, правая - приемнику данных. Пакет команд может состоять как из n различных команд, так и одной общей, адресная часть которой должна разрешать выдачу этой команды сразу на все выходы одновременно. В заявке описаны: простейший вариант выполнения блока 11 синхронизации с использованием одновибратора и полный - на триггерах со сбросами готовностей. Возможны и промежуточные смешанные комбинации: одна - готовность на одновибраторе, другая - на триггере (может быть со сбросом готовности или без). Вместо триггера 18 (фиг. 5) можно использовать счетчик с дешифратором для снятия сигнала "ГотД" по последнему результату в пакете, что может упростить алгоритм устройства 5 во время приема пакета результатов за счет исключения алгоритмического (программного) счета номеров результатов в пакете. Сброс сигнала "ГотК" в триггере 17 в случае отсутствия выдачи команд может быть осуществлен не элементом 13 задержки, а одним из импульсов генератора 1. Для случаев, когда стробирующие сигналы не используются для сброса готовностей, в алгоритмах должен присутствовать для сигналов готовностей анализ их появления; если используются, то анализ их наличия. Формирователь 7 управления нормализаторами 4 выполняет задачу выработки необходимых сигналов функционирования нормализаторов 4. Конкретное исполнение его зависит от принципа, заложенного в работу нормализаторов 4; может быть использован известный формирователь 7, например, как в прототипе. На вход его должен быть подан сигнал, позволяющий синхронизировать работу нормализаторов 4 с работой счетчика-делителя 8, чтобы обеспечить циклическую работу нормализаторов 4 синхронно с рассмотренными ранее блоками.

Изобретение обладает существенно большим быстродействием. Постоянный циклический режим работы нормализаторов и АЦП положительно сказывается на точности результатов измерения за счет улучшения их повторяемости. Возможность построения АЦП с коммутатором на входе устраняет погрешности из-за неидентичности аналого-цифрового преобразования для разных нормализаторов, существенно упрощает и удешевляет конструкцию системы, увеличивая, кроме того, ее надежность и уменьшая затраты на метрологическое обеспечение. Управление коммутаторами через регистры позволяет расширить функциональные возможности системы за счет возможности измерения одновременно сигналов различных входов для различных нормализаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020422C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020420C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020421C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020423C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 2004 |

|

RU2253842C1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 1995 |

|

RU2084011C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИССЛЕДОВАНИЯ АВАРИЙНЫХ И ПРЕДАВАРИЙНЫХ СОСТОЯНИЙ РАЗЛИЧНЫХ КОНСТРУКЦИЙ | 1994 |

|

RU2082145C1 |

| ИЗМЕРИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2018173C1 |

Изобретение относится к приборостоению, в частности к электроизмерительной технике. С целью повышения быстродействия, точности и надежности многоканальный регистратор состоит из тактового генератора, многоканального АЦП с последовательно соединенными коммутатором и нормализатором на каждом входе и запоминающего устройства данных на выходе, цифрового устройства управления и приема данных, регистров команд на управляющих входах коммутаторов, формирователя управления нормализаторами, счетчика-делителя, запоминающего устройства команд и блока синхронизации. Даны дополнительно вариант выполнения цифрового устройства и приема данных и четыре варианта выполнения блока синхронизации. 2 з.п. ф-лы, 9 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Труды ЦАГИ, М., 1984, вып.2227. | |||

Авторы

Даты

1994-09-30—Публикация

1990-07-10—Подача