Изобретение относится к приборостроению, в частности к электроизмерительной технике, и может быть использовано в тензо- и термометрии для измерения сигналов тензо- и термодатчиков.

Известен регистратор (система) "Прочность", предназначенный для автоматизации процессов измерения, сбора и обработки информации преобразователей различных величин, характеризующих тепловое, деформированное и напряженное состояние конструкций. Измерительные сигналы в каждом канале поступают на измерительный модуль, представляющий собой преобразователь сигналов датчиков в напряжение и АЦП на выходе, цифровые сигналы которого поступают через информационную шину цифровой части системы в ЭВМ. Поскольку получение цифрового результата измерения в АЦП (уравновешивание) проходит при совместной работе преобразователя сигналов датчиков, датчиков и линий связи, получение результата измерения требует большого времени из-за неизбежных переходных процессов, связанных с уравновешиванием входной измерительной цепи.

Наиболее близким по технической сущности и достигаемому эффекту является регистратор (система) "Ресурс 23/27", состоящий из восьми нормализаторов и блока АЦП. Для формирования временной диаграммы управления работой регистратора имеется тактовый генератор. Имеется также один общий формирователь управления нормализаторами на их управляющих входах. Результаты измерения из блока АЦП поступают в ЭВМ. Блок АЦП с восемью аналоговыми входами и одним цифровым выходом представляет собой многоканальный АЦП. ЭВМ, осуществляющая прием результатов измерения, по существу выполняемых функций является приемником данных, который может быть реализован не только ЭВМ как таковой, а и микропроцессором, цифровым автоматом, цифровым регистратором и т. д. В этой системе существенно увеличено быстродействие за счет введения нормализаторов, не требующих участия в аналого-цифровом преобразовании датчиков, проводов подсоединения их к системе и входных измерительно-преобразовательных цепей. Однако для ряда задач (статодинамические испытания конструкций) этого быстродействия оказывается недостаточно. Период поступления пакетов по n результатов измерений в приемник данных определяется выражением

Т=Тн+Тацп+Тприем+Твозврат,

где Тн - время работы нормализатора;

Тацп - время работы АЦП;

Тприем - время приема n результатов измерения;

Твозврат - время возврата регистраторов на исходную позицию;

n - число каналов нормализации (число нормализаторов) регистратора.

К недостаткам следует отнести СТАРТ-СТОП-ный режим работы нормализаторов, отрицательно сказывающийся на точности результатов нормализации из-за ухудшения их повторяемости. Построение блока АЦП (многоканального АЦП) из восьми отдельных АЦП добавляет в результаты измерения дополнительную погрешность из-за неидентичности точностных характеристик отдельных АЦП и существенно усложняет и удорожает конструкцию регистратора, увеличивая, кроме того, его надежность и затраты на метрологическое обеспечение.

Целью изобретения является повышение быстродействия, точности и надежности регистратора.

Цель достигается тем, что в многоканальный регистратор, содержащий тактовый генератор и многоканальный аналого-цифровой преобразователь с нормализаторами на входах и приемником данных на выходе, формирователь управления нормализаторами, подключенный выходом к управляющим входам нормализаторов, введены блок синхронизации и счетчик-делитель, вход которого соединен с выходом тактового генератора и входом запуска аналого-цифрового преобразователя, а счетный выход - с управляющим входом аналого-цифрового преобразователя, выход деления - с синхровходом блока синхронизации, вход формирования которого соединен с выходом конца преобразования аналого-цифрового преобразователя, вход сброса - с выходом стробирования приемника данных, управляющий вход которого соединен с выходом готовности блока синхронизации, а вход формирователя управления нормализаторами подключен к выходу деления счетчика-делителя либо к его счетному выходу; блок синхронизации содержит элемент задержки, элемент ИЛИ и два D-триггера, выходы первого D-триггера, элемента задержки, элемента ИЛИ соединены соответственно с D-входом второго D-триггера, первым входом элемента ИЛИ, R-входом второго D-триггера, причем синхровходом, входом формирования, входом сброса, выходом блока синхронизации являются соответственно объединенные S-вход первого D-триггера и вход элемента задержки, R-вход первого D-триггера и С-вход второго D-триггера, С-вход первого D-триггера и второй вход элемента ИЛИ, выход второго D-триггера, а D-вход первого D-триггера подключен к источнику единичного сигнала; блок синхронизации содержит элемент ИЛИ и два D-триггера, выходы первого D-триггера и элемента ИЛИ соединены соответственно с D- и R-входами второго D-триггера, причем синхровходом, входом формирования, входом сброса, дополнительным синхровходом, выходом блока синхронизации являются соответственно S-вход первого D-триггера, объединенные R-вход первого D-триггера и С-вход второго D-триггера, С-вход первого D-триггера и первый вход элемента ИЛИ, второй вход элемента ИЛИ, выход второго D-триггера, а D-вход первого D-триггера подключен к источнику единичного сигнала, дополнительный синхровход - к выходу тактового генератора.

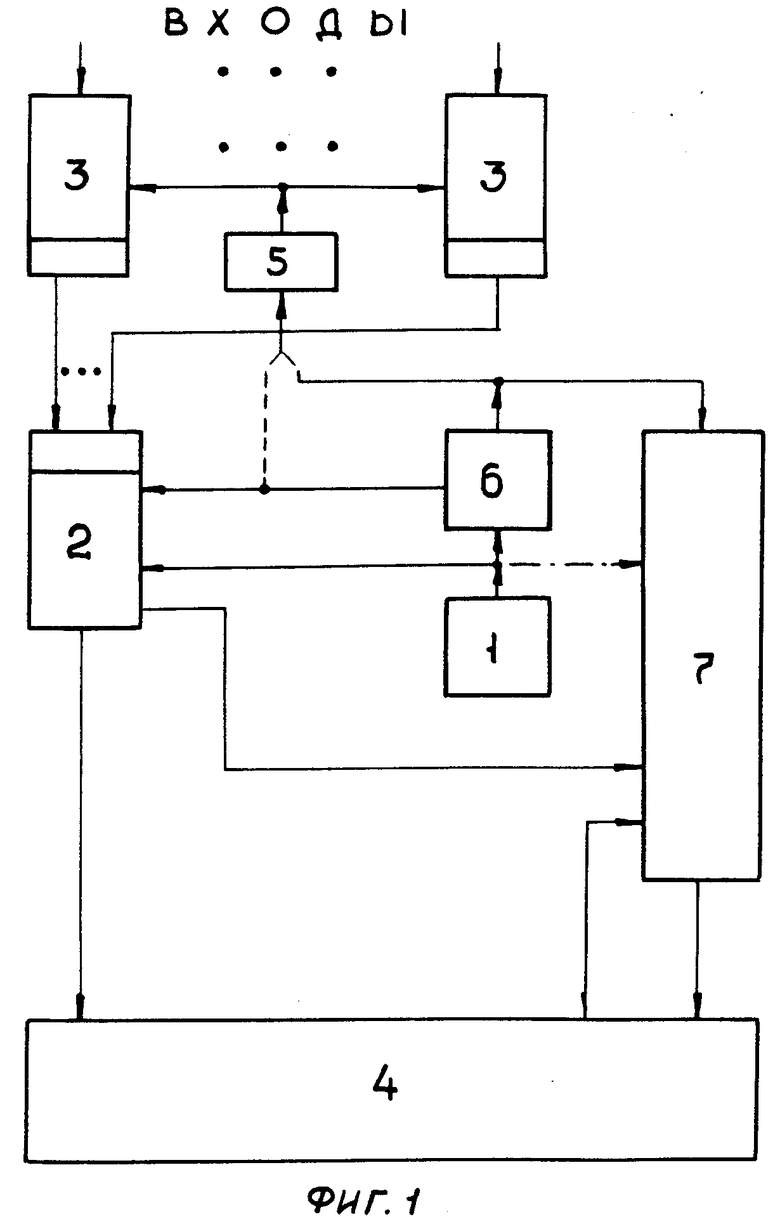

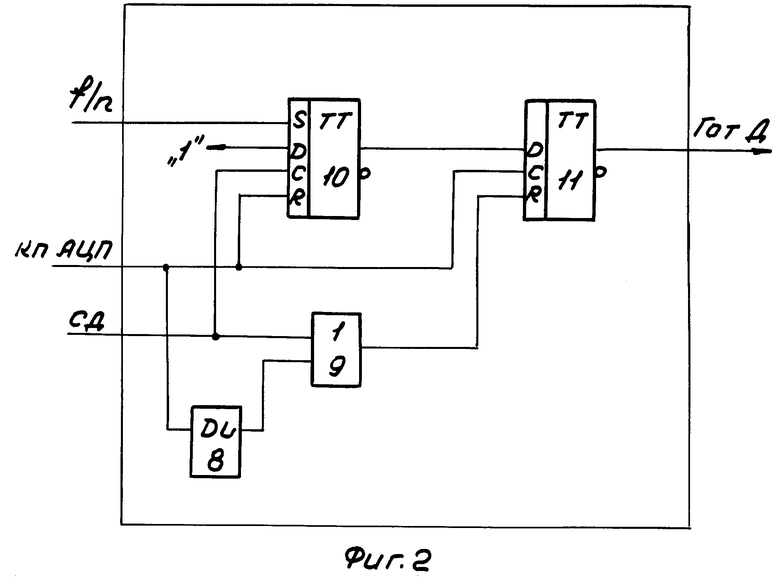

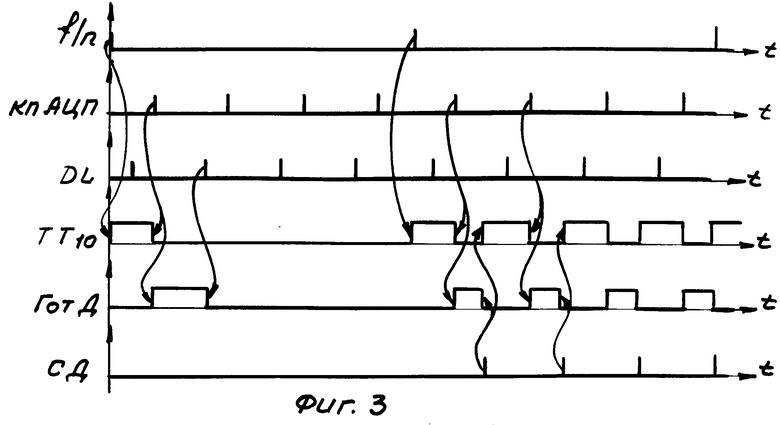

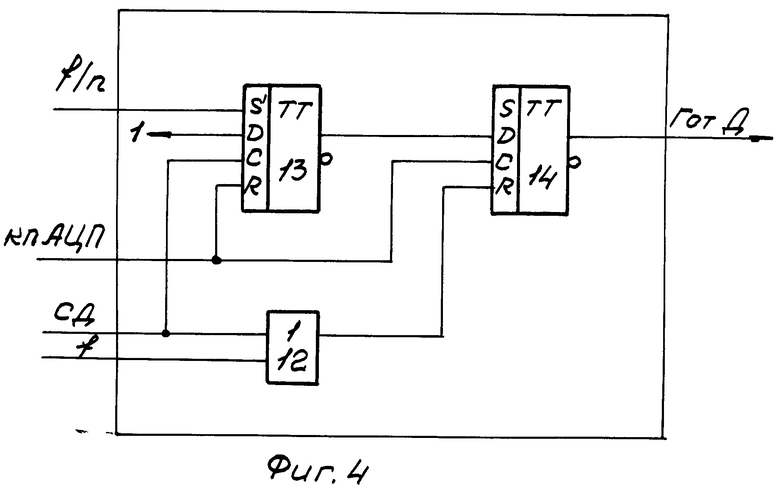

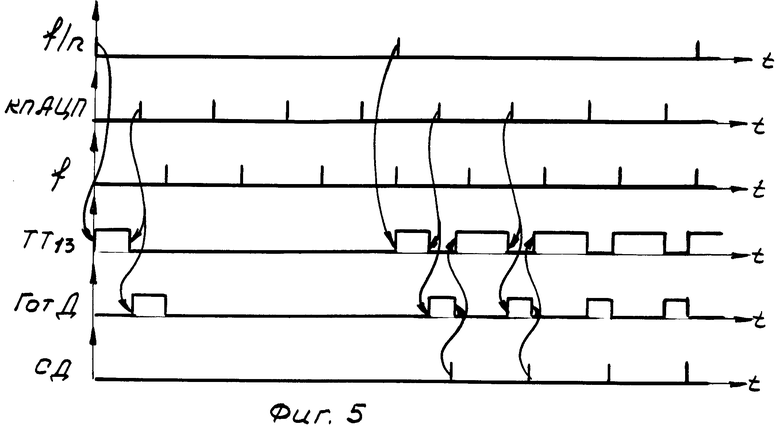

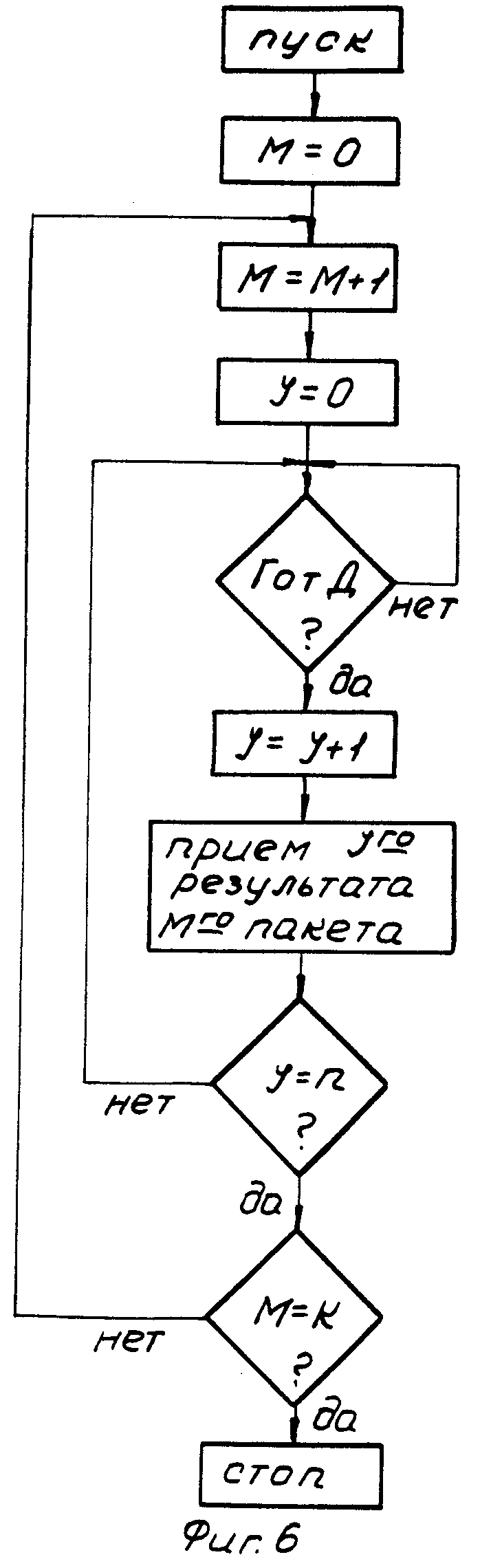

На фиг. 1 представлена схема предлагаемого регистратора; на фиг. 2 и 3 - схема и временная диаграмма работы блока синхронизации, выполненного без дополнительного синхровхода; на фиг. 4 и 5 - схема и временная диаграмма работы блока синхронизации, выполненного с дополнительным синхровходом; на фиг. 6 - алгоритм работы приемника данных.

Многоканальный регистратор состоит из тактового генератора 1 и многоканального АЦП 2 с нормализаторами 3 на входах и приемником 4 данных на выходе, формирователя 5 управления нормализаторами 3, подключенного выходом к управляющим входам нормализаторов 3, счетчика-делителя 6, соединенного входом с выходом тактового генератора 1 и входом запуска АЦП 2, счетным выходом - с управляющим входом АЦП 2, и блока 7 синхронизации, соединенного синхровходом с выходом деления счетчика-делителя 6, входом формирования - с выходом конца преобразования АЦП 2, входом сброса - с выходом стробирования приемника 4 данных, причем приемник 4 данных имеет управляющий вход, соединенный с выходом готовности блока 7 синхронизации, а вход формирователя 5 управления нормализаторами 3 подключен к выходу деления либо счетному выходу счетчика-делителя 6 (фиг. 1). Блок 7 синхронизации имеет дополнительный синхровход, соединенный с выходом тактового генератора. Блок 7 синхронизации содержит элемент 8 задержки, элемент ИЛИ 9 и два D-триггера 10 и 11, выходы первого D-триггера 10, элемента 8 задержки, элемента ИЛИ 9 соединены соответственно с D-входом второго D-триггера 11, первым входом элемента ИЛИ 9, R-входом второго D-триггера 11, причем синхровходом, входом формирования, входом сброса, выходом блока 7 синхронизации являются соответственно объединенные S-вход первого D-триггера 10 и вход элемента 8 задержки, R-вход первого D-триггера 10 и С-вход второго D-триггера 11, С-вход первого D-триггера 10 и второй вход элемента ИЛИ 9, выход второго D-триггера 11, а D-вход первого D-триггера 10 подключен к источнику единичного сигнала (фиг. 2). Блок 7 синхронизации содержит элемент ИЛИ 12 и два D-триггера 13 и 14, выходы первого D-триггера 13 и элемента ИЛИ 12 соединены соответственно с D-, R-входами второго D-триггера 14, причем синхровходом, входом формирования, входом сброса, дополнительным синхровходом, выходом блока 7 синхронизации являются соответственно S-вход первого D-триггера 13, объединенные R-вход первого D-триггера 13 и С-вход второго D-триггера 14, С-вход первого D-триггера 13 и первый вход элемента ИЛИ 12, второй вход элемента ИЛИ 12, выход второго D-триггера 14, а D-вход первого D-триггера 13 подключен к источнику единичного сигнала (фиг. 4).

Регистратор работает следующим образом. Генератор 1 вырабатывает тактовые сигналы f регистратора, поступающие на счетчик-делитель 6 с коэффициентом деления (счета) n, равным числу нормализаторов 3 регистратора (фиг. 1). Счетчик-делитель 6 считает тактовые сигналы f и выдает на выходе деления сигнал f/n цикла нормализации через каждые n тактовых сигналов f, а на счетном выходе - кодовый или дешифрированный эквивалент числа считываемых тактовых сигналов f. АЦП 2 запускается каждым тактовым сигналом f, а через управляющий вход последовательно в соответствии с сигналами со счетного выхода счетчика-делителя 6 подключает информационные входы для аналого-цифрового преобразования сигналов нормализаторов 3 с цикличностью, равной циклу нормализации (время преобразования нормализаторов 3). Все нормализаторы 3 работают параллельно, по управляющим сигналам формирователя 5 управления нормализаторами 3, запускаются синхронно с сигналом f/n цикла нормализации и по окончании его в следующем цикле имеют на своих устройствах выходной аналоговой памяти соответствующие результаты предыдущего цикла нормализации. Цифровые результаты (данные) появляются на выходе АЦП 2 последовательно в соответствии с переключением его выходов, т.е. расположением нормализаторов. Сигналы на выходе конца преобразования АЦП 2 определяют моменты появления соответствующих цифровые результатов (данных). Прием результатов от АЦП осуществляется приемником 4 данных последовательно по сигналам на управляющем входе данных. Таким образом, нормализация входных сигналов, аналого-цифровое преобразование и подача цифровых результатов на вход приемника 4 данных происходят циклически, безостановочно, синхронно с работой тактового генератора 1 и счетчика-делителя 6 независимо от работы приемника 4 данных. Приемник 4 данных принимает пакет последовательных результатов по одному непосредственно после появления каждого сигнала на выходе готовности данных блока 7 синхронизации. Прием каждого результата в приемнике 4 данных сопровождается стробирующим сигналом на его выходе стробирования. Сигналы управления для приемника 4 данных вырабатываются блоком 7 синхронизации, исходным сигналом для работы которого является сигнал цикла нормализации на его синхровходе.

Алгоритм работы приемника 4 данных показан на фиг. 6. Перед пуском системы в приемнике 4 данных отводят место для К пакетов по n результатов. С пуском системы обнуляется счетчик пакетов в приемнике 4 данных оператором М= 0, увеличивается на "1" оператором М=М+1, обнуляется счетчик результатов в пакете (J=0) и приемник 4 приступает к анализу сигнала "Гот Д" готовности данных на его управляющем входе от блока 7 синхронизации. Если после анализа делается отрицательное заключение ("Нет") по наличию "Гот Д", приемник 4 возвращается на исходную позицию анализа; если положительное ("Да"), - число J счетчика результатов в пакете увеличивается на "1" (J=J+1) и приемник 4 данных приступает к приему J-го результата М-го пакета результатов. Далее проверяется условие J=n, означающее, принят ли последний (n-й) результат пакета или нет. Если "Нет" - переход на анализ сигнала "Гот Д", если "Да" - анализ условия М=К, означающего, принят ли последний (К-й) пакет или нет. Если "Нет" - переход на оператор J=0, если "Да" - "СТОП".

Входные сигналы нормируются и заносятся в свои выходные устройства аналоговой памяти за время Тн цикла нормализации. АЦП 2 по сигналам со счетного выхода счетчика-делителя 6 (для переключения входов АЦП 2) и по сигналам f c генератора (для запуска АЦП 2) для каждого пакета вырабатывает последовательно n цифровых результатов, соответствующих сигналам на выходах n нормализаторов 3. При этом по окончании преобразования каждого результата своим сигналом конца преобразования АЦП 2 инициирует появление сигнала "Гот Д", по которому приемник 4 принимает соответствующий результат и сбрасывает сигналом стробирования сигнал "ГОТ Д" в блоке 7 синхронизации. Следовательно, пакеты результатов измерения поступают в приемник с периодом, равным времени Тн цикла нормализации, что существенно меньше, чем у прототипа.

Рассмотрим работу блока 7 синхронизации по фиг. 2 и 3. Каждый сигнал f/n цикла нормализации устанавливает триггер 10 в "1". Каждый сигнал "КП АЦП" конца преобразования переписывает "1" из, триггера 10 в триггер 11 (появление сигнала "ГОТ Д" готовности данных) и обнуляет триггер 10. При приеме данных сигналом "СД" стробирования данных, поступающим от приемника 4 данных на вход сброса блока 7 синхронизации, обнуляется триггер 11 (сброс сигнала "ГОТ Д") и в триггер 10 записывается "1". Если приемник 4 данных прием данных не проводит (нет сигнала "СД"), то через элемент 8 задержки и элемент ИЛИ 9 сигналом "КП АЦП" происходит сброс "Гот Д" обнулением триггера 10, причем до появления нового сигнала "КП АЦП", но не ранее, чем через время, необходимое с гарантией для анализа приемником 4 сигнала "ГОТ Д".

Работа блока 7 синхронизации по другому варианту, показанному на фиг. 4 и 5, отличается тем, что сброс "ГОТ Д" при отсутствии приема данных осуществлен не через элемент 8 задержки, а с помощью сигнала генератора 1 через дополнительный синхровход.

В качестве многоканального АЦП 2 в системе может быть использован один АЦП с аналоговым коммутатором входов либо n АЦП с цифровым коммутатором на выходе. Известны стандартные счетчики-делители, например микросхема 564ИЕ11. В качестве приемника 4 данных могут быть использованы микропроцессоры, мини- и микроЭВМ или специальные цифровые автоматы и цифровые регистраторы. Возможны и другие модификации выполнения блока 7 синхронизации и алгоритмов работы приемника 4 данных. Формирователь 5 управления нормализаторами 3 выполняет задачу выработки необходимых сигналов функционирования нормализаторов 3. Конкретное исполнение его зависит от принципа, заложенного в работу нормализаторов 3; может быть использован известный формирователь 5, например, как в прототипе. На вход его должен быть подан сигнал, позволяющий синхронизировать работу нормализаторов 3 с работой счетчика-делителя 6, чтобы обеспечить циклическую работу нормализаторов 3 синхронно с рассмотренными ранее блоками.

Изобретение обладает существенно большим быстродействием. Постоянный циклический режим работы нормализаторов и АЦП положительно сказывается на точности результатов измерения за счет улучшения их повторяемости. Возможность построения АЦП с коммутатором на входе устраняет погрешности из-за неидентичности аналого-цифрового преобразования для разных нормализаторов, существенно упрощает и удешевляет конструкцию системы, увеличивая, кроме того, ее надежность и уменьшая затраты на метрологическое обеспечение. Управление коммутаторами через свои регистры позволяет расширить функциональные возможности измерения одновременно сигналов различных нормализаторов. Все это выгодно отличает данное техническое решение от ранее известных.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020421C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020422C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020420C1 |

| МНОГОКАНАЛЬНЫЙ РЕГИСТРАТОР | 1990 |

|

RU2020424C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 2004 |

|

RU2253842C1 |

| Устройство для голосования и счетчик со случайным порядком счета Ордынцева | 1990 |

|

SU1751792A1 |

| Устройство для сбора данных | 1984 |

|

SU1213427A1 |

| АВТОНОМНЫЙ РЕГИСТРАТОР СЕЙСМИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2331087C1 |

| ИЗМЕРИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2018173C1 |

Изобретение относится к приборостроению, в частности к электроизмерительной технике. С целью повышения быстродействия, точности и надежности многоканальный регистратор содержит тактовый генератор, многоканальный АЦП с нормализаторами на входах и приемником данных на выходе, формирователь управления нормализаторами, счетчик-делитель и блок синхронизации. Приведены варианты выполнения блока синхронизации. 2 з.п. ф-лы, 6 ил.

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| М., Издательский отдел ЦАГИ, 1984, вып.2227. | |||

Авторы

Даты

1994-09-30—Публикация

1990-07-10—Подача