Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, имеющих канал МПИ, в автоматизированной системе управления, работающей в режиме реального времени.

Целью изобретения является расширение функциональных возможностей устройства.

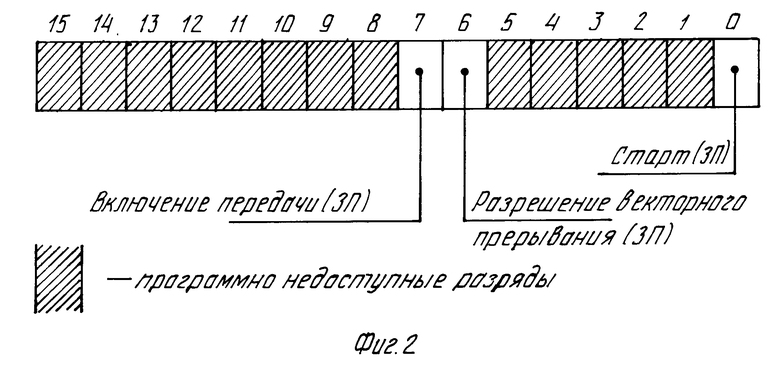

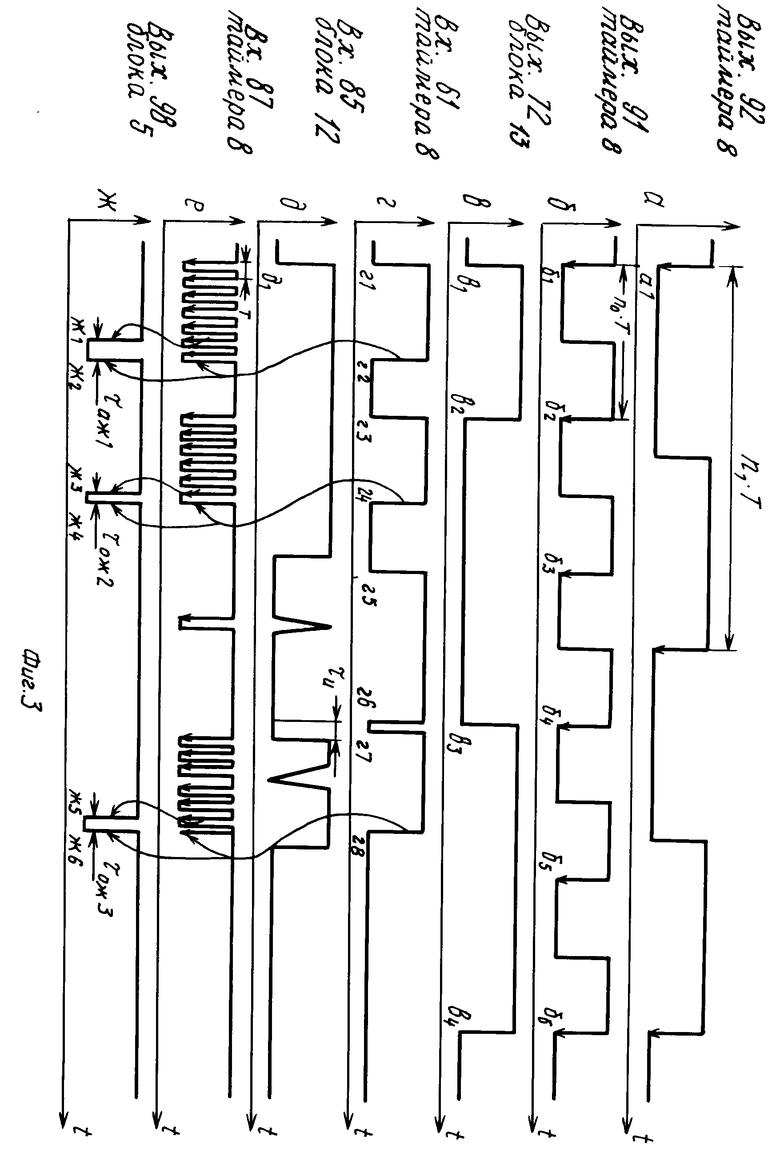

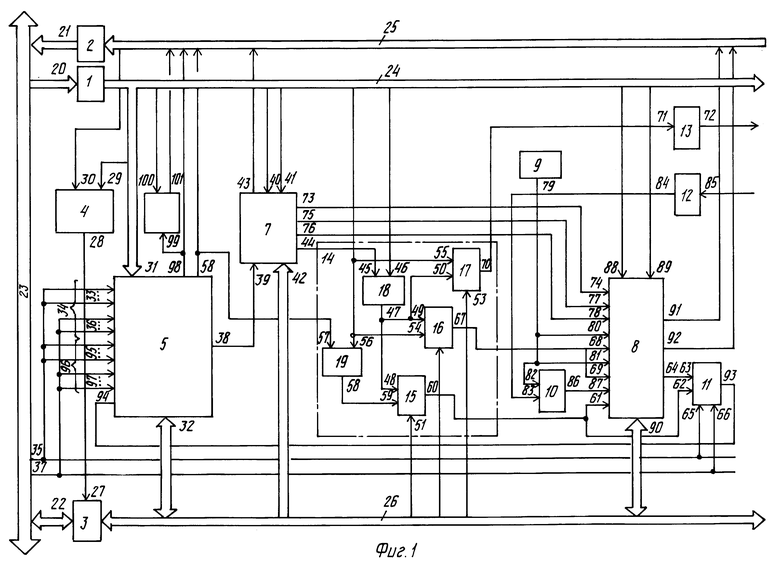

На фиг. 1 представлена схема устройства; на фиг. 2 приведены формат и назначение отдельных разрядов регистра состояния; на фиг. 3 - временные диаграммы, иллюстрирующие ввод и вывод дискретных сигналов.

Устройство (фиг. 1) содержит канальные приемники 1, канальные передатчики 2, канальные приемопередатчики 3, блок 4 управления, блок 5 селекции адресов и выдачи вектора, блок 6 прерывания, компаратор 7 адресов, программируемый таймер 8, генератор 9 импульсов, элемент 2И-НЕ 10, IK-триггер 11, первый блок 12 гальванической развязки, второй блок 13 гальванической развязки, регистр 14 состояния, содержащий первый D-триггер 15, второй D-триггер 16, третий D-триггер 17, элемент И 18 и элемент ИЛИ 19. Входы 20 канальных приемников 1 являются группой входов управления обменом устройства. Выходы 21 канальных передатчиков 2 являются группой выходов управления обменом устройства. Первая группа входов-выходов 22 канальных приемопередатчиков 3 является входами-выходами адреса данных устройства. Входы 20 канальных приемников 1, выходы 21 канальных передатчиков 2 и первая группа входов-выходов 22 канальных приемопередатчиков 3 подключены к каналу 23 ЭВМ. Выходы канальных приемников 1 образуют внутреннюю шину 24 входных сигналов управления обменом устройства. Входы канальных передатчиков 2 образуют внутреннюю шину 25 выходных сигналов управления обменом устройства. Вторая группа входов-выходов канальных приемопередатчиков 3 образует внутреннюю шину 26 сигналов адреса-данных устройства. Вход 27 переключения направления передачи канальных приемопередатчиков 3 подключен к выходу 28 блока 4 управления, вход 29 синхроимпульса ввода блока 4 управления соединен с линией соответствующего сигнала внутренней шины 24, вход 30 синхроимпульса ответа блока 4 управления соединен с линией соответствующего сигнала внутренней шины 25. Группа входов 31 управления обменом блока 5 соединена с линиями соответствующих сигналов внутренней шины 24. Группа входов-выходов 32 адреса-данных блока 5 соединена с линиями соответствующих сигналов адреса-данных внутренней шины 26. Первая группа 33 входов 34 установки адресов сравнения блока 5 соединена с шиной 35 "Плюс источника питания", вторая группа 36 входов 34 блока 5 соединена с шиной 37 "Общий провод". Выход 38 сравнения блока 5 соединен с управляющим входом 39 компаратора 7 адресов. Вход 40 ввода и вход 41 вывода компаратора 7 соединены с линиями соответствующих сигналов внутренней шины 24. Адресные входы 42 компаратора 7 соединены с линиями сигналов трех младших разрядов внутренней шины 26. Выход 43 синхроимпульса ответа компаратора 7 соединен с линией соответствующего сигнала внутренней шины 25. Выход 44 строба управления компаратора 7 соединен с первым входом 45 элемента И 18, второй вход 46 которого соединен с линией синхроимпульса вывода внутренней шины 24. Выход 47 элемента И 18 соединен с синхровходами 48, 49 и 50 D-триггеров 15, 16 и 17 соответственно. D-вход 51 первого D-триггера 15 соединен с линией сигнала шестого разряда адреса-данных внутренней шины 26. D-вход 52 второго D-триггера 16 соединен с линией сигнала нулевого разряда адреса-данных внутренней шины 26. D-вход 53 третьего D-триггера 17 соединен с линией сигнала седьмого адреса-данных внутренней шины 26. Входы 54 и 55 сброса второго 16 и третьего 17 D-триггеров соединены между собой, с первым входом 56 элемента ИЛИ 19 и с линией сигнала начальной установки внутренней шины 24. Второй вход 57 элемента ИЛИ 19 соединен с выходом 58 синхроимпульса ответа блока 5 и с линией соответствующего сигнала внутренней шины 25. Выход 58 элемента ИЛИ 19 соединен с входом 59 сброса первого D-триггера 15. Прямой выход 60 этого триггера соединен с входом 61 разрешения счета второго канала программируемого таймера 8 и с входом 62 сброса IК-триггера 11. Синхровход 63 этого триггера соединен с выходом 64 второго канала таймера 8. I-вход 65 триггера 11 соединен с шиной 35 "Плюс источника питания" устройства, а К-вход 66 - с шиной 37 "Общий провод". Прямой выход 67 второго D-триггера 16 соединен с входами 68 и 69 разрешения счета нулевого и первого каналов программируемого таймера 8. Прямой выход 70 третьего D-триггера 17 соединен с входом 71 второго блока 13 гальванической развязки. Выход 72 этого блока является информационным выходом устройства. Выход 73 сигнала разрешения компаратора 7 соединен с входом 74 выбора кристалла программируемого таймера 8. Младший адресный выход 75 и старший адресный выход 76 компаратора 7 соединены соответственно с младшим адресным входом 77 и старшим адресным входом 78 программируемого таймера. Выход 79 генератора 9 импульсов соединен с частотным входом 80 нулевого канала таймера 8, с частотным входом 81 первого канала таймера 8, а также с первым входом 82 элемента 2И-НЕ 10. К второму входу 83 элемента 2И-НЕ 10 подключен выход 84 первого блока 12 гальванической развязки. Вход 85 этого блока является информационным входом устройства, на который поступают вводимые дискретные сигналы. Выход 86 элемента 2И-НЕ соединен с частотным входом 87 второго канала таймера 8. Вход 88 синхроимпульса чтения и вход 89 синхроимпульса записи таймера 8 соединены с линиями сигналов соответственно ввода и вывода внутренней шины 24. Группа входов-выходов 90 данных таймера 8 соединена с линиями соответствующих сигналов адреса-данных внутренней шины 26. Выход 91 нулевого канала таймера 8 подключен к линии сигнала второго радиального прерывания внутренней шины 25. Выход 92 первого канала таймера 8 подключен к линии сигнала первого радиального прерывания внутренней шины 25. Инверсный выход 93 IK-триггера 11 соединен с входом 94 требования прерывания блока 5. Первая группа 95 входов 96 установки адреса вектора прерывания блока 5 соединена с шиной 35 "Плюс источника питания", вторая группа 97 входов 96 соединена с шиной 37 "Общий провод". Выход 98 требования прерывания блока 5 соединен с одноименным входом 99 блока 6 и с линией соответствующего сигнала внутренней шины 25. Вход 100 предоставления прерывания блока 6 соединен с линией входного сигнала предоставления прерывания внутренней шины 24, а выход 101 предоставления прерывания блока 6 соединен с линией выходного сигнала предоставления прерывания внутренней шины 25.

На выходе 38 блока 5 селекции адресов и выдачи вектора появляется сигнал сравнения, если в адресной части циклов ВВОД и ВЫВОД на группе входов-выходов 32 блока 5 будет комбинация логических "0" и логических "1", совпадающая с комбинацией, установленной на группе входов 34, т.е. если адрес на группе входов-выходов 32 совпадает с адресом, установленным на группе входов 34. Сигнал сравнения на выходе 38 блока 5 длится до окончания текущего цикла. Селектор адресов, заключенный внутри блока 5, осуществляет сравнение не одного адреса, а группы из восьми смежных адресов. Адреса внутри этой группы отличаются один от другого значением одного из трех младших разрядов. При поступлении на вход 94 блока 5 сигнала требования прерывания на выходе 98 блока 5 также появляется сигнал требования прерывания. Этот сигнал поступает на линию сигнала требования прерывания внутренней шины 25, а оттуда через канальные передатчики 2 на линию сигнала требования прерывания канала 23. Процессор ЭВМ (на фигурах не показан), получив из этой линии сигнал требования прерывания, завершает выполнение текущей команды и проводит цикл ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ. Адрес вектора, установленный на входах 96 блока 5 в сопровождении синхроимпульса ответа, вырабатываемого на выходе 58 этого блока, поступает на группу входов-выходов 32 адреса-данных, а оттуда по линиям сигналов адреса-данных внутренней шины 26 через канальные приемопередатчики 3 на линии сигналов адреса-данных канала 23 ЭВМ.

Канальные приемопередатчики 3 исходно включены в напpавлении передачи сигналов из канала 23 во внутреннюю шину 26. Переключения направления передачи происходят в моменты ввода информации из устройства в ЭВМ в циклах ВВОД или ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ. Канальные приемники 1 постоянно включены в направлении передачи сигналов из канала 23 во внутреннюю шину 24. Канальные передатчики 2 постоянно включены в направлении передачи сигналов из внутренней шины 25 в канал 23.

Блок 4 выполняет функцию переключателя направления передачи канальных приемо-передатчиков 3.

Блок 6 предназначен для выработки запрета на распространение синхроимпульса предоставления прерывания при выполнении цикла ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ в том случае, если прерывания требовало данное устройство. Во всех остальных случаях запрет не вырабатывается и синхроимпульс предоставления прерывания, поступающий из канала 23 через канальные приемники 1 на внутреннюю шину 24 устройства, ретранслируется блоком 6 по внутренней шине 25 через канальные передатчики 2 в канал 23.

Компаратор 7 адресов в группе из восьми смежных адресов, выделенной блоком 5, распознает четыре адреса, относящиеся к регистрам таймера 8, и один адрес, относящийся к регистру 14 состояния. При обращении ЭВМ к регистрам таймера 8 в циклах ВВОД и ВЫВОД, а также при обращении к регистру 14 состояния в цикле ВЫВОД на выходе 43 компаратора 7 адресов вырабатывается синхроимпульс ответа, поступающий по линии синхроимпульса ответа внутренней шины 25 через канальные передатчики 2 в канал 23 ЭВМ.

Регистр 14 состояния имеет доступ только для записи. Формат и назначение разрядов регистра 14 состояния иллюстрирует фиг. 2. При включении питания ЭВМ и при запуске программы импульсом начальной установки канала 23, поступающим через канальные приемники 1 по внутренней шине 24 на вход регистра 14 состояния, производится начальный сброс триггеров 15, 16 и 17 регистра состояния, что приводит к запрету счета всех каналов таймера 8, к запрету первого и второго радиальных прерываний и к запрету сигнала требования прерывания на выходе 93 триггера 11.

Таймер 8 содержит три независимых идентичных программируемых 16-разрядных счетчика, работающих в двоичном или двоично-десятичном коде. Каждый из счетчиков (каналов) программируют независимо друг от друга, записывая управляющее слово и число, с которого счетчик начинает вычитание. ЭВМ осуществляет записи (инициализацию) счетчиков, обращаясь в цикле ВЫВОД к регистру управляющего слова и к трем регистрам данных каналов таймера 8. При этом на входе 74 выбора кристалла таймера 8 должен действовать сигнал разрешения, адресация регистров таймера 8 осуществляется с помощью сигналов на его адресных входах 77 и 78, а запись данных в регистры таймера 8 осуществляется по линиям сигналов восьми младших разрядов адреса-данных внутренней шины 26, подключенных к группе входов-выходов 90 таймера 8, во время действия синхроимпульса вывода на входе 89 записи таймера 8. По окончании инициализации каждый из трех каналов таймера 8 начинает работать независимо друг от друга, осуществляя уменьшение на единицу своего содержимого по заднему фронту каждого импульса, действующего на частотном входе этого канала, при условии разрешения счета на соответствующем входе 68, 69, 61. В зависимости от управляющего слова возможен один из шести режимов работы каждого канала таймера 8.

В составе ЭВМ устройство работает в программном режиме и в режиме прерываний.

В программном режиме производится инициализация всех каналов таймера 8, т.е. программирование каждого канала таймера 8 на определенный режим работы и занесение в каждый канал своего начального значения n. В программном режиме ЭВМ производит также обращение в цикле ВЫВОД к регистру 14 состояния, устанавливая или сбрасывая D-триггеры 15, 16, 17 этого регистра. Допустим каналы таймера 8 программируются на режим деления частоты, в нулевой канал заносится начальное число no, в первый канал n1, во второй канал - n2, прием n0, n1, n2 - четные числа от 2 до 65534 (10). Затем ЭВМ обращается к регистру 14 состояния в цикле ВЫВОД. В адресной части этого цикла срабатывают селектор адресов, заключенный внутри блока 5, и компаратор 7 адресов, на выходе 44 которого активируется строб управления регистром 14 состояния, а сигналы на выходах 73, 75, 76 пассивны. Этот строб поступает на вход 45 элемента И 18 регистра 14 состояния и остается активным до конца цикла. По окончании адресной части цикла ВЫВОД ЭВМ активирует линию сигнала нулевого разряда адреса-данных канала 23, сопровождая выводимые данные синхроимпульсом вывода. Компаратор 7 адресов, получив на входе 41 синхроимпульс вывода из внутренней шины 24, вырабатывает на выходе 43 синхроимпульс ответа, поступающий по соответствующей линии внутренней шины 25 через канальные передатчики 2 в канал 23. С приходом на вход 46 элемента И 18 синхроимпульса вывода из внутренней шины 24 на выходе 47 элемента И 18 вырабатывается строб занесения, поступающий на синхровходы 48, 49, 50 триггеров 15, 16, 17. Поскольку на входе 52 триггера 16 сигнал нулевого разряда адреса-данных в рассматриваемый момент времени активен, а на D-входах 51 и 53 триггеров 15 и 17 сигналы шестого и седьмого разрядов адреса-данных пассивны, триггер 16 взводится, а триггеры 15 и 17 остаются в состоянии сброса. На входах 68 и 69 таймера 8 устанавливается разрешение (старт) счета. Таким образом, осуществляется старт счета нулевого и первого каналов таймера 8. На этом процесс инициализации заканчивается. Он проводится, как правило, один раз за все время после включения ЭВМ.

В режиме прерываний устройство, во-первых, организует режим реального времени ЭВМ, а во-вторых, производит вывод дискретных сигналов по программе вывода и ввод дискретных сигналов по программе ввода, причем вводимые дискретные сигналы проходят двухпороговую селекцию по длительности. Получив разрешение на входе 69, первый канал таймера 8 начинает работу как делитель частоты генератора 9 в n1 раз. С выхода 92 этого канала импульсы скважности, близкой к двум, периода n1. Т (Т - период импульсов на выходе 79 генератора 9) поступают на линию первого радиального прерывания внутренней шины 25 и через канальные передатчики 2 на одноименную линию канала 23 ЭВМ. Эти импульсы являются метками реального времени, по которым ЭВМ организует режим реального времени. Получив разрешение на входе 68, нулевой канал таймера 8 начинает работу как делитель частоты генератора 9 в n0 раз. С выхода 91 этого канала импульсы скважности, близкой к двум, периода n0. T поступают на линию второго радиального прерывания внутренней шины 25 и через канальные передатчики 2 на одноименную линию канала 23 ЭВМ. Моменты перехода уровня этих импульсов из логической "1" в логический "0" означают точки начала, продолжения или окончания вывода дискретных сигналов или их ввода с двухпороговой селекцией по длительности.

Рассмотрим работу устройства в режиме прерываний, пользуясь временными диаграммами, приведенными на фиг. 3. Стрелками на фиг. 3а показаны моменты перехода импульсов с выхода 92 первого канала таймера 8 логической "1" в логический "0". Соответствующие этим переходам первые радиальные прерывания (метки реального времени) обозначены точками а1, а2, а3. Получив от устройства метку реального времени, поступающую по линии первого радиального прерывания канала 23, процессор ЭВМ завершает выполнение текущей команды и обращается к фиксированной ячейке памяти ЭВМ, в которой указан начальный адрес подпрограммы обработки первого радиального прерывания. Эта подпрограмма осуществляет наращивание на единицу счетчика меток реального времени, организованного в одной или нескольких ячейках памяти ЭВМ, по каждому факту первого радиального прерывания. Моменты перехода импульсов с выхода 91 нулевого канала таймера 8 из логической "1" в логический "0" обозначены на фиг. 3б точками б1...б6. Этим точкам соответствуют вторые радиальные прерывания (метки ввода-вывода дискретных сигналов). Получив от устройства метку ввода-вывода, поступающую по линии второго радиального прерывания канала 23, процессор ЭВМ завершает выполнение текущей команды и обращается к другой фиксированной ячейке памяти ЭВМ, в которой указан начальный адрес подпрограммы ввода-вывода дискретных сигналов. Под управлением этой подпрограммы ЭВМ в необходимые моменты времени, совпадающие с метками ввода-вывода, производит включение или отключение D-триггера 17 регистра 14 состояния, осуществляя вывод дискретных сигналов, а также производит включение или отключение D-триггера 15, разрешая двухпороговую селекцию и ввод дискретных сигналов. Так, например, в момент прихода метки ввода-вывода б1 программы ЭВМ необходимо осуществить вывод дискретного сигнала и одновременно разрешить ввод дискретного сигнала. Для этого ЭВМ, обращаясь к регистру 14 состояния в цикле ВЫВОД, активирует линии нулевого, шестого и седьмого разрядов адрес-данных канала 23, сопровождая выводимые данные синхроимпульсом вывода. Происходит взведение триггеров 15 и 17 и подтверждение взведенного состояния триггера 16н. На выходе 70 триггера 17 устанавливается логическая "1", что приводит к появлению дискретного сигнала на выходе 72 блока 13 (участок в1-в2 на фиг. 3в). Дискретный сигнал выводится до момента очередного воздействия по метке ввода-вывода б2. Взведенное состояние триггера 15 разрешает работу второго канала таймера 8 (участок г1-г2 на фиг. 3г). Поскольку на вход 85 блока 12 в этот момент поступает вводимый дискретный сигнал (участок д1-д2 на фиг. 3д), на частотный вход 87 второго канала таймера 8 с выхода 86 элемента 2И-НЕ 10 поступают импульсы периода Т от генератора 9, и по каждому заднему фронту этих импульсов происходит уменьшение на единицу начального значения n2, записанного в регистр второго канала таймера 8 при инициализации (участок е1 - е3 на фиг. 3е). В момент времени е2 содержимое счетчика второго канала таймера 8 становится равным нулю и на выходе 64 этого канала появляется сигнал логического "0". Взводится триггер 11, что приводит к появлению сигнала требования прерывания на выходе 98 блока 5, поступающего через канальные передатчики 2 в канал 23 (точка ж1 на фиг. 3ж). Процессор ЭВМ, получив этот сигнал, в течение времени ж1-ж2, называемого временем ожидания предоставления прерывания τож (фиг. 3ж), завершает выполнение текущей команды и вводит адрес вектора прерывания, как это было указано выше при описании работы блока 5 и блока 6. Синхроимпульсом ответа с выхода 58 блока 5, поступающим через элемент ИЛИ 19 на вход 59 сброса триггера 15, последний сбрасывается (точка г2 на фиг. 3г), что приводит к запрету счета второго канала таймера 8 (точка е3 на фиг. 3е), сбросу триггера 11 и к снятию сигнала требования прерывания на выходе 98 блока 5 (точка ж2 на фиг. 3ж). Подпрограмма обслуживания векторного прерывания, начальный адрес которой находится в ячейке памяти ЭВМ, на которую указывает введенный вектор, по факту векторного прерывания информируется о том, что принят дискретный сигнал длительностью τ, причем (б2 - е1) > τ ≥ (е2 - е1).

По приходе очередной метки ввода-вывода б2 программа вывода дискретных сигналов должна прекратить вывод (точка в2 на фиг. 3в), а программа ввода дискретных сигналов должна продолжить ввод. Поэтому в седьмой бит регистра состояния записывается "0", в шестой и нулевой биты - "1" (см. также фиг. 2). Триггер 17 сбрасывается, и на выходе 72 блока 13 выводится дискретный сигнал уровня логического "0" до очередной записи "1" в седьмой бит регистра состояния, т.е. до очередного взведения триггера 17 (участок в2-в3 на фиг. 3в). Запись "1" в шестой бит регистра состояния приводит к новому взведению триггера 15 (точка г3 на фиг. 3г), что вызывает новый цикл ввода дискретного сигнала (участок е4 - е6 на фиг. 3е), происходит новое векторное прерывание (участок ж3 - ж4 на фиг. 3ж), приводящее к сбросу триггера 15 (точка г4 на фиг. 3г). По факту векторного прерывания программа ввода информируется о том, что принят дискретный сигнал (б3 - е4) > τ ≥ (е5 - е4).

По приходе метки ввода-вывода б3 программа вывода должна продолжить вывод дискретного сигнала, равного логическому "0", а программа ввода должна продолжить ввод (участок б3 - б4). В седьмой бит регистра 14 состояния записывается "0", в шестой и нулевой биты - "1". На этом участке вводимый дискретный сигнал длительностью б3-б4, уровень которого равен логическому "0", искажает помехи в виде всплеска малой длительности (участок д3 - д4). Поскольку длительность помехи ниже нижнего порога двухпороговой селекции, на частотный вход 87 второго канала таймера 8 хотя и поступают счетные импульсы, их количество за время б3-б4 меньше числа n2 (участок е7-е8 на фиг. 3е), и векторное прерывание не возникает. По факту отсутствия векторного прерывания за время б3-б4 программа ввода информируется о том, что уровень вводимого дискретного сигнала на этом отрезке равен логическому "0". Снятие условия разрешения векторного прерывания осуществляется в этом случае по приходе метки б4 (точка г6 на фиг. 3г).

Фронт вводимого дискретного сигнала, показанного на участке д5 - д9 (фиг. 3д), запаздывает относительно метки ввода-вывода б4 на время τз. Кроме того, этот сигнал искажает помеха в виде провала малой длительности (д7 - д8). Однако, поскольку суммарная длительность вводимого дискретного сигнала за время б4-б5 даже за вычетом длительности провала превышает нижний порог селекции по длительности, на счетчик второго канала таймера 8 успевает поступить число импульсов, равное n . 2 (участок е9 - е11 на фиг. 3е), и векторное прерывание происходит (участок ж5-ж6 на фиг. 3ж).

Таким образом, временные диаграммы на фиг. 3 интерпретируются следующим образом. Устройство в составе ЭВМ вырабатывает метки реального времени периода n1. T (фиг. 3а) и метки ввода-вывода периода n0. T (фиг. 3б) независимо друг от друга, причем ЭВМ, работающая в режиме реального времени, осуществляет вывод кода 10011 за промежуток времени б1 - б6 (фиг. 3в) и одновременно осуществляет ввод кода 1101 на фоне помех (фиг. 3ж). На участке б5 - б6 ЭВМ не вводит дискретные сигналы (фиг. 3г). Конфликтные ситуации, связанные с одновременным приходом нескольких запросов на прерывание (например, в точках а1, б1 или а3, б3), разрешаются системой приоритетов процессора ЭВМ.

Применение устройства позволяет ЭВМ, работающей в режиме реального времени, производить дуплексный ввод-вывод дискретных сигналов по прерываниям основных программ. Отвлечения процессора ЭВМ на обслуживание устройства заключаются лишь в однократной за все время работы программы инициализации таймера 8, обслуживании первых и вторых радиальных прерываний, обращениях к регистру состояния устройства в циклах ВЫВОД и обслуживании векторных прерываний от устройства. Эти отвлечения процессора ЭВМ оказывают весьма малое воздействие на его загрузку и практически не мешают выполнению основных программ при условии, что период следования меток ввода-вывода хотя бы на порядок больше длительности машинного цикла ЭВМ.

Применение устройства позволяет организовать полудуплексный и дуплексный обмен информацией с периферийными устройствами, а также межмашинный обмен по различным последовательным каналам связи, в том числе по радиоканалу, в условиях действия импульсных помех в канале связи. С помощью устройства может быть реализован практически любой стандартный или нестандартный протокол обмена по последовательному каналу связи, причем для изменения протокола обмена нужно лишь изменить программу ввода-вывода.

Экспериментальный образец устройства применен в составе автоматизированной системы управления на базе микроЭВМ ДВК-2М для организации межмашинного обмена дискретной информацией по последовательному каналу связи с применением нестандартного протокола обмена с кодированием по Хеммингу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| Устройство для согласования интерфейсов | 1988 |

|

SU1688249A1 |

| Устройство для сопряжения внешних устройств с магистралью ЭВМ | 1987 |

|

SU1527639A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1985 |

|

SU1315988A1 |

| Устройство для сопряжения ЭВМ с внешним накопителем | 1988 |

|

SU1672459A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1990 |

|

SU1734099A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, в автоматизированной системе управления, работающей в режиме реального времени. Целью изобретения является расширение функциональных возможностей. Устройство содержит канальные приемники 1, канальные передатчики 2, канальные приемопередатчики 3, блок 4 управления, блок 5 селекции адресов и выдачи вектора, блок 6 прерывания, компаратор 7 адресов, программируемый таймер 8, генератор 9 импульсов, элемент 2И - НЕ 10, JK-триггер 11, блоки 12 и 13 гальванической развязки, регистр 14 состояния. Устройство позволяет вводить дискретные сигналы, период следования которых не кратен периоду временных меток, а также осуществляет возможность вывода дискретных сигналов. 3 ил.

УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ, содержащее канальные приемники, канальные передатчики, канальные приемопередатчики, блок управления, блок селекции адресов и выдачи вектора, блок прерывания, компаратор адресов, программируемый таймер, генератор импульсов, элемент 2И - НЕ, JK-триггер, первый блок гальванической развязки, регистр состояния, содержащий первый и второй D-триггеры, элемент И и элемент ИЛИ, при этом входы канальных приемников являются группой входов управления обменом устройства, выходы канальных передатчиков - группой выходов управления обменом устройства, первая группа входов-выходов канальных приемопередатчиков - входами-выходами адреса данных устройства, вход переключения направления передачи канальных приемопередатчиков подключен к выходу блока управления, вход синхроимпульса ввода блока управления соединен с соответствующим выходом канальных приемников, вход синхроимпульса ответа блока управления соединен с соответствующим входом канальных передатчиков, группа входов управления обменом блока селекции адресов и выдачи вектора соединена с соответствующими выходами канальных приемников, группа входов-выходов адреса данных блока селекции адресов и выдами вектора соединена с второй группой входов-выходов канальных приемопередатчиков, первая и вторая группы входов установки адресов сравнения блока селекции адресов и выдачи вектора соединены соответственно с положительным и нулевым потенциалами источника питания, выход сравнения блока селекции адресов и выдачи вектора соединен с управляющим входом компаратора адресов, входы ввода и вывода которого соединены с соответствующими выходами канальных приемников, адресные входы компаратора адресов соединены с тремя младшими разрядами второй группы входов-выходов канальных приемопередатчиков, выход синхроимпульса ответа компаратора адресов соединен с соответствующим входом канальных передатчиков, выход строба управления компаратора адресов - с первым входом элемента И, второй вход элемента И соединен с выходом синхроимульса вывода канальных приемников, выход элемента И - с синхровходами первого и второго D-триггеров, D-входы которых соединены соответственно с шестым и нулевым разрядами входов-выходов второй группы входов-выходов канальных приемопередатчиков, вход сброса второго D-триггера соединен с первым входом элемента ИЛИ и с выходом начальной установки канальных приемников, второй вход элемента ИЛИ соединен с выходом синхроимпульса ответа блока селекции адресов и выдачи вектора и с соответствующим входом канальных передатчиков, выход элемента ИЛИ - с входом сброса первого D-триггера, прямой выход первого D-триггера - с входом разрешения счета второго канала программируемого таймера и с входом сброса JK-триггера, синхровход которого соединен с выходом второго канала программируемого таймера, J- и K-входы JK-триггера соединены соответственно с положительным и нулевым потенциалами источника питания, прямой выход второго D-триггера соединен с входами разрешения счета нулевого и первого каналов программируемого таймера, инверсный выход JK-триггера - с входом требования прерывания блока селекции адресов и выдачи вектора, первая и вторая группы входов установки адреса вектора прерывания которого соединены соответственно с положительным и нулевым потенциалами источника питания, выход требования прерывания блока селекции адресов и выдача вектора соединен с соответствующим входом канальных передатчиков и с входом требования прерывания блока прерывания, вход предоставления прерывания которого соединен с соответствующим выходом канальных приемников, выход предоставления прерывания - с соответствующим входом канальных передатчиков, выходы сигнала разрешения, младший и старший адресные выходы компаратора адресов соединены соответственно с входом выбора кристалла, с младшим и старшим адресными входами порограммируемого таймера, вход синхроимпульса чтения и вход синхроимпульса записи программируемого таймера соединены соответственно с выходом синхроимпульса ввода и с выходом синхроимпульса вывода канальных приемников, группа входов-выходов данных программируемого таймера соединена с соответствующими входами-выходами второй группы входов-выходов канальных приемопередатчиков, частотный вход первого канала программируемого таймера соединен с первым входом элемента 2И - НЕ, к второму входу которого подключен выход первого блока гальванической развязки, вход которого является информационным входом устройства, выход элемента 2И - НЕ соединен с частотным входом второго канала программируемого таймера, выход первого канала которого соединен с входом радиального прерывания канальных передатчиков, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет возможности ввода дискретных сигналов, период следования которых не кратен периоду временных меток, а также возможности вывода дискретных сигналов, в него введен второй блок гальванической развязки, а в регистр состояния третий D-триггер, синхровход которого соединен с выходом элемента И и с синхровходами первого и второго D-триггеров регистра состояния, вход третьего D-триггера соединен с входом сброса второго D-триггера, а также с первым входом элемента ИЛИ и с выходом начальной установки канальных приемников, D-вход третьего D-триггера соединен с седьмым разрядом входов-выходов второй группы входов-выходов канальных приемопередатчиков, прямой выход третьего D-триггера соединен с входом второго блока гальванической развязки, выход которого является информационным выходом устройства, выход генератора импульсов соединен с частотными входами нулевого и первого каналов программируемого таймера и с первым входом элемента 2И - НЕ, а выход нулевого канала программируемого таймера подключен к входу второго радиального прерывания канальных передатчиков.

| Устройство для ввода дискретных сигналов | 1988 |

|

SU1522221A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-10-30—Публикация

1989-07-18—Подача