Изобретение относится к вычислительной технике и может быть использовано для электрического и алгоритмического согласования микроЗВМ, имеющих магистральный параллельный интерфейс ИЛИ (Электроника-60, ДВК), с периферийными устройствами ввода-вывода, имеющими другие интерфейсы.

Целью изобретения является сокращение аппаратурных затрат устройства, требуемых при подключении к ЭВМ раз- юобразных периферийных устройств.

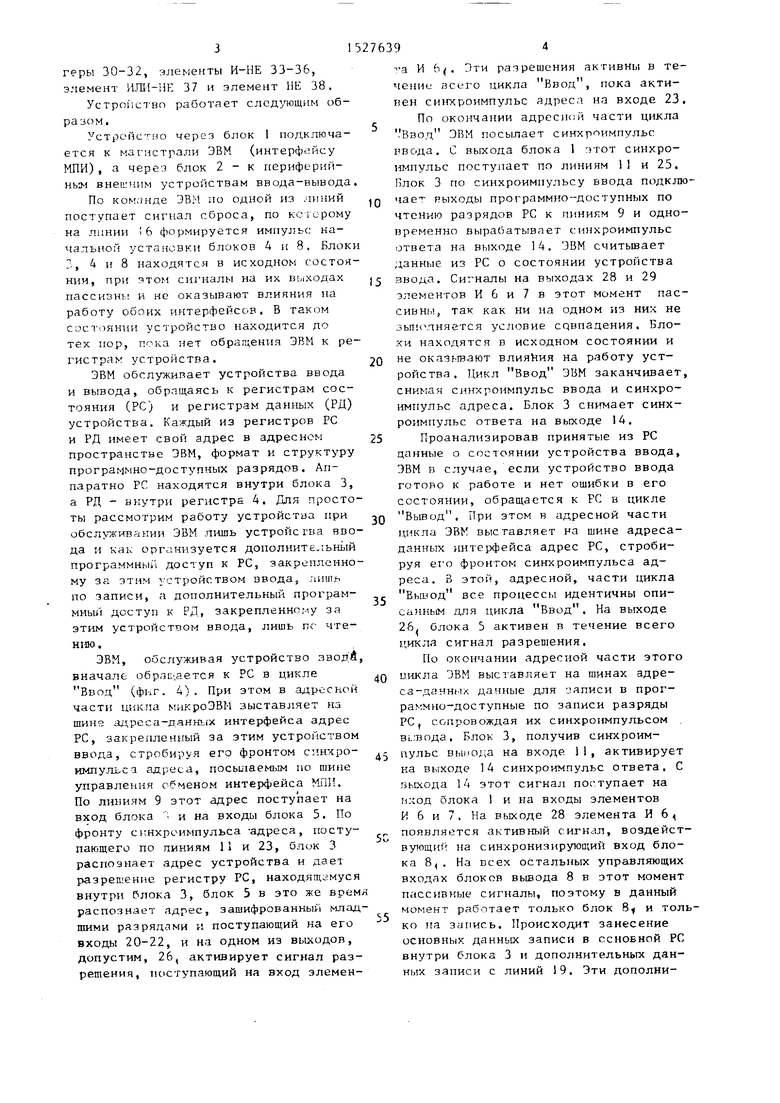

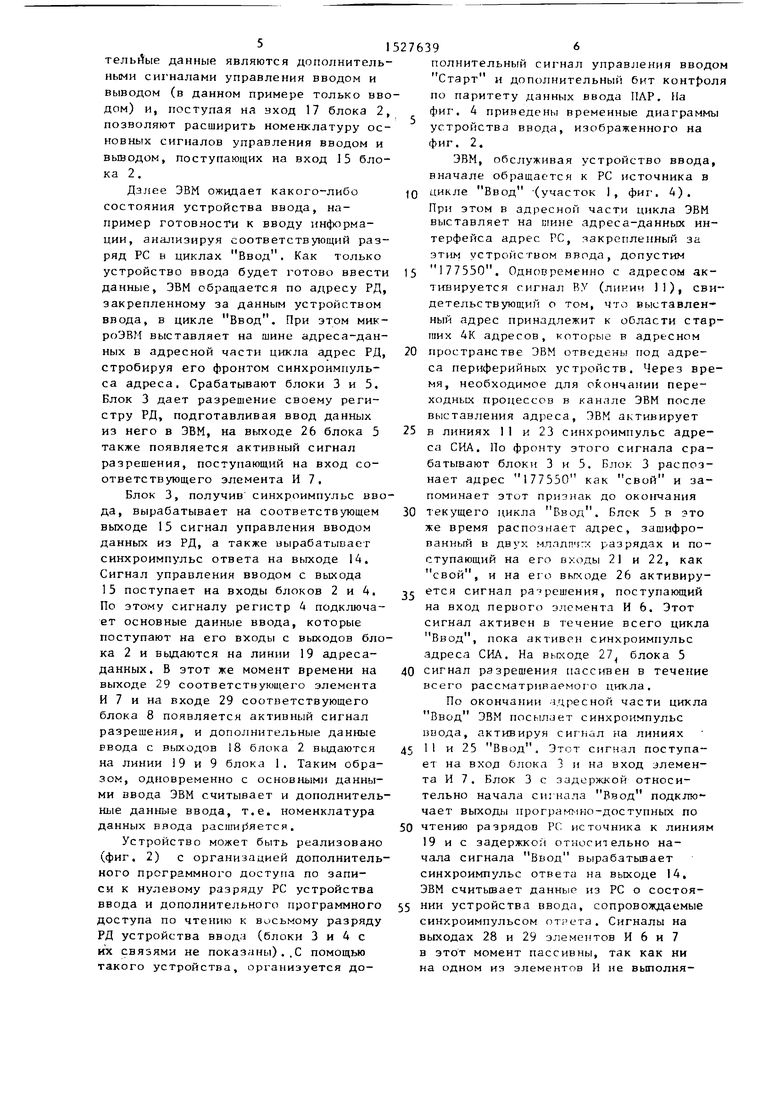

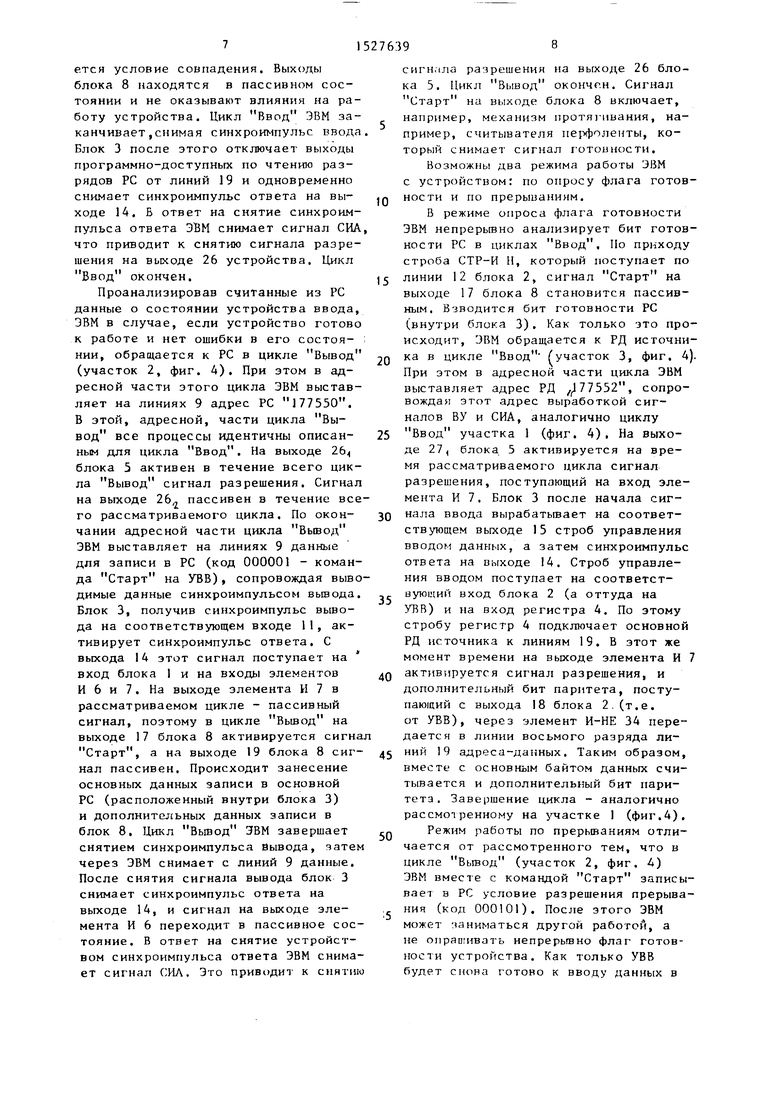

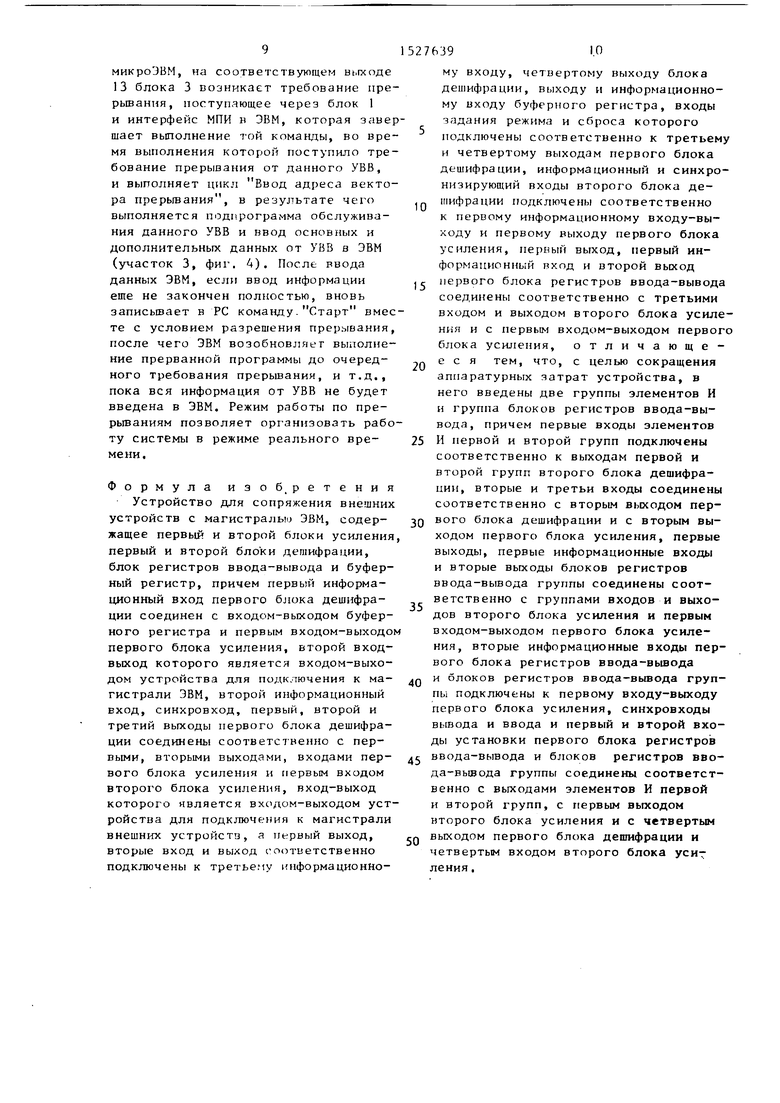

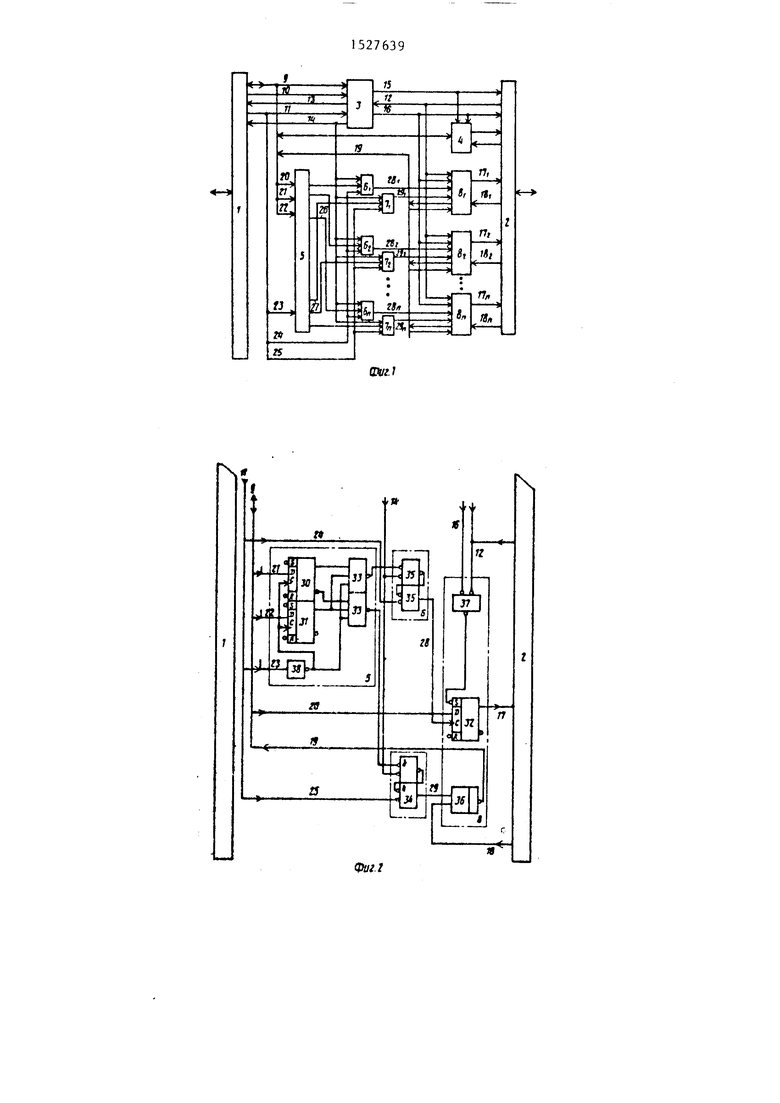

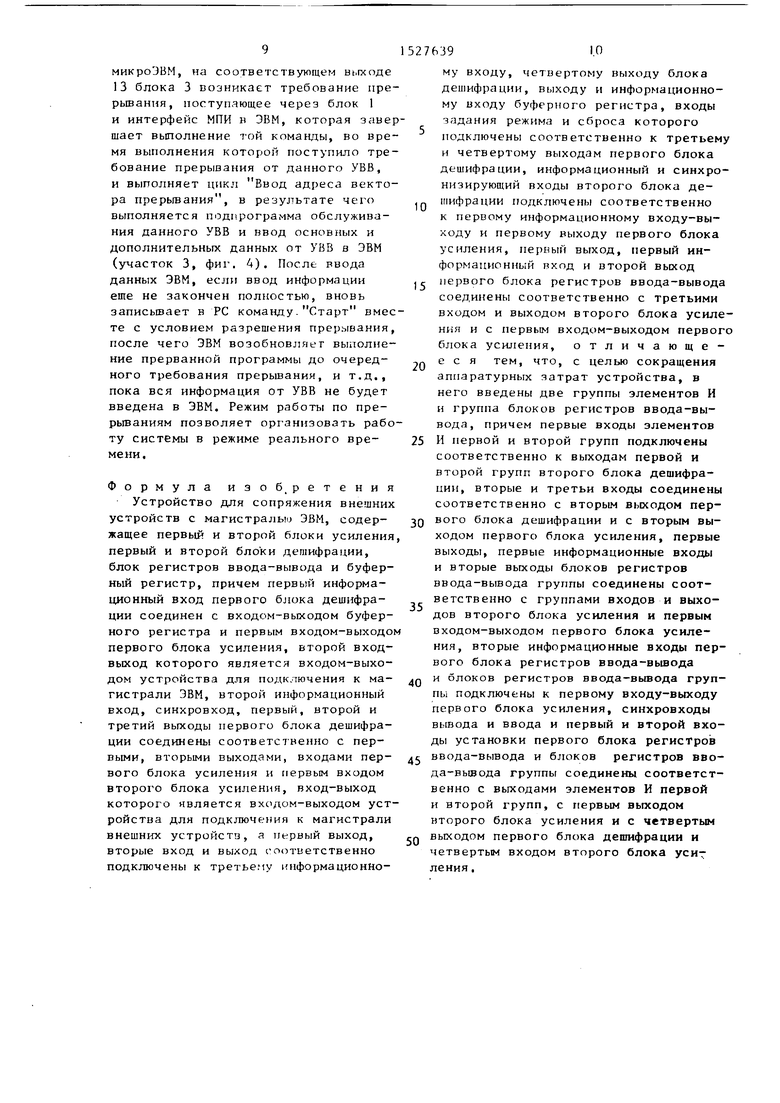

На фиг, 1 представлена блок-схема устройства; на фиг. 2 - схема второго блока дешифрации, групп элементов И и одного из блоков регистров ввода- вьшода; на фиг. 3 - схема программно- доступных разрядов регистров; на

фиг. 4 - временная диаграмма работы устройства.

Устройство содержит первый 1 и второй 2 блоки усиления, первый блок 3 дешифрации, буферный регистр 4, второй блок 5 дешифрации, элементы И 6 и 7 первой и второй групп, первый блок 8, регистров ввода-вьшода, группа блоков ,, регистров ввода-вывода. Кроме того, показаны внутренние связи входов и выходов (линий) 9-29 устройства.

Блок 3 может быть выполнен на БИС 1801ВП1-033, а блок 4 - на БИС 1801ВЛ1-034.

Блок 5 дешифрации, группы элементов И 6 и 7 и блоки 8 регистров содержат (фиг. 2), например, триггеры 30-32, элементы И-НЕ 33-36, элемент ИЛИ-ИЕ 37 и элемент НЕ 38.

Устройство работает след тощим образом.

ycTpofic HO через блок 1 подключается к маг истрали ЭВМ (интерфейсу МПИ), а через блок 2 - к перифернй- иым устройствам ввода-вывода

По команде ЭВМ по одной из линий поступает сигнал сброса, по ксгсрому на линии «6 формируется импу; ьс начальной установки блоков 4 и 8, Блоки 3, 4 и 8 находятся в исходном состоянии, при этом сигналы на их вь.ходах пассизнь и не оказывают влияния на работу обоих интерфейсов. В таком состоянии устройство находится до тех пор, пока нет обра ;ен11я ЭВМ к регистрам устройства.

ЭВМ обслуживает устройства ввода и вывода, обращаясь к регистрам состояния (PC) и регистрам данных (РД) устройства. Каждый из регистров ГС и РД имеет свой адрес в адресном пространстве ЭВМ, формат и структуру nporpaNjMHO-доступных разрядов. Ап- паратно PC находятся внутри блока 3, а РД - внутри регистра 4. Для простоты рассмотрим работу устройства при обслуживании ЭВМ л1-1шь устройства ввода и как Организуется дополните.тьньш программны; ) доступ к PC, закрепленному за этим устройством ввода, лишь по записи, а дополнительный программный доступ к РД, закрепленному за этим устройством ввода, лишь пс чтению.

ЭВМ, обслуживая устройство вводи вначале обрас .аетсн к PC в цикле Ввод (фкг. 4). При этом в адресной части цикла микроЭВМ зыставляет на шине адреса-даниых интерфейса адрес PC, закрепленный за этим устройством ввода, стробируя его фронтом синхроимпульса адреса, посьшаемым по шине управления обменом интерфейса МЛН, По линиям 9 этот адрес поступает на вход блока и на входы блока 5. По сьшхроимпульса -адреса, поступающего по пиниям 11 и 23, блок 3 распознает адрес устройства и дает разрешение регистру PC, находящемуся внутри блока 3, блок 5 в это же врем распознает адрес, зашифрованный младшими разрядами и поступающий на его входы 20-22, и на одном из выходов, допустим, 26, активирует сигнал разрешения, тюступающий на вход элемен276394

И 6, Эти разрешения активны в течение всего цикла Ввод, пока активен CHJrxpOHMnynhC адреса на входе 23,

По окончании адресной части цикла - Ввод ЭВМ посылает синхроимпульс ввода, С выхода блока 1 :ггот синхроимпульс поступает по линиям 11 и 25, 1шок 3 по синхроимпульсу ввода подклю- чае пыходы программно-доступных по чтению разрядов PC к линиям 9 и одновременно вырабатывает синхроимпульс

10

5

0

5

0

5

0

5

С

1зтвета на выходе 14. ЭВМ считьшает данные из PC о состоянии устройства ввода. Сигналы на выходах 28 и 29 элементов И 6 и 7 в этот момент пассивны, так как ни на одном из них не ;зьп с 1Няется условие совпадения. Блоки находятся в исходном состоянии и не оказьшают влияния на работу устройства. Цикл Ввод ЭВМ заканчивает, снимая синхроимпульс ввода и синхроимпульс адреса. Блок 3 снимает синхроимпульс ответа на выходе 14.

Проанализировав принятые из PC данные о состоянии устройства ввода, ЭВМ в случае, если устройство ввода готово к работе и нет ошибки в его состоянии, обращается к PC в цикле Вьюод, При этом в адресной части цикла ЭВМ выставляет на шине адреса- данных интерфейса адрес PC, стробируя его фронтом синхроимпульса адреса. В этой, адресной, части цикла Вывод все процессы идентичны описанным для цикла Ввод, На выходе 26. блока 5 активен в течение всего цикла сигнал разрешения.

По окончании адресной части этого цикла ЭВМ выставляет на шинах адре- са-данн(-гх данные для записи в программно-доступные по записи разряды PC, сопровождая их синхроимпульсом Вьшода, Блок 3, получив синхроимпульс выпода на входе 11, активирует на выходе 14 синхроимпульс ответа, С выхода 14 этот сигнал поступает на блока 1 и на входы элементов И 6 и 7, На выходе 28 элемента И 6 появляется активный сигнал, воздейст- вутщий на синхронизирующий вход блока 8 . На всех остальных управляющих входах блоков вьшода 8 в этот момент Псчссивные сигналы, поэтому в данный момент работает только блок 8 и только на запись. Происходит занесение основных данных записи в ссновной PC внутри блока 3 и дополнительных данных записи с линий 19, Эти дополни5

тельйые данные являются дополнительными си1 налами управления вводом и выводом (в данном примере только вводом) и, поступая на зход 17 блока 2 позволяют расширить номенклатуру основных сигналов управления вводом и вьшодом, поступающих на вход J5 блока 2.

Дзлее ЭВМ ожидает какого-либо состояния устройства ввода, например готовности к вводу информации, анализируя соответствующий разряд PC в циклах Ввод. Как только устройство ввода будет готово ввести данные, ЭВМ обращается по адресу РД, закрепленному за данным устройством ввода, в дикле Ввод. При этом мик- роЭВМ выставляет на шине адреса-дан- ных в адресной части цикла адрес РД, стробируя его фронтом синхроимпульса адреса. Срабатывают блоки 3 и 5, Блок 3 дает разрешение своему регистру РД, подготавливая ввод данных из него в ЭВМ, на выходе 26 блока 5 также появляется активный сигнал разрешения, поступающий на вход соответствующего элемента И 7,

Блок 3, получив синхроимпульс ввода, вырабатывает на соответствующем выходе 15 сигнал управления вводом данных из РД, а также иырабатывает синхроимпульс ответа на выходе 14. Сигнал управления вводом с выхода 15 поступает на входы блоков 2 и 4, По этому сигналу регистр 4 подключает основные данные ввода, которьЕе поступают на его входы с выходов блока 2 и выдаются на линии 19 адреса- данных. В этот же момент времени на выходе 29 соответствующего элемента И 7 и на входе 29 соответствующего блока 8 появляется активный сигнал разрешения, и дополнительные данные ввода с выходов 18 блока 2 выдаются на линии 19 и 9 блока 1, Таким образом, одновременно с основными данными ввода ЭВМ считывает и дополнительные данные ввода, т.е. номенклатура данных ввода расгт115яется .

Устройство может быть реализовано (фиг. 2) с организацией дополнительного программного доступа по записи к нулевому разряду PC устройства ввода и дополнительного программного доступа по чтению к восьмому разряду РД устройства ввода (блоки 3 и 4 с их связями не показаны)..С помощью такого устройства, организуется до276396

полнительный сигнал управления вводом Старт и дополнительный бит контроля по паритету данных ввода ПАР. На фиг. 4 приведены временные диаграммы устройства ввода, изображенного на фиг. 2.

ЭВМ, обслуживая устройство ввода, вначале обращается к PC источника в )Q цикле Ввод -(участок 1, фиг. 4).

При этом в адресной части цикла ЭВМ выставляет на тине адреса-данных интерфейса адрес PC, закрепленный за этим устройством ввода, допустим 15 177550. Односременно с адресом активируется сигнал ВУ (линии 11), свидетельствующий о том, что выставленный адрес принадлежит к области старших 4К адресов, которые в адресном 20 пространстве ЭВМ отведень под адреса периферийных устройств. Через время, необходимое для окончании переходных процессов в канале ЭВМ после выставления адреса, ЭВМ активирует 25 в линиях 11 и 23 синхроимпульс адреса СИЛ. По фронту этого сигнала срабатывают блоки 3 и 5. Блок 3 распознает адрес 177550 как свой и запоминает этот признак до око1гчания 30 текущего цикла Ввод. Блек 5 в это же время распознает адрес, зашифрованный в двух мллдпчп разрядах и поступающий на его входы 21 и 22, как свой, и на ег-о выходе 26 активиру- jr ется сигнал разрешения, поступающий на вход первого элемента И 6. Этот сигнал активен в течение всего цикла Ввод, пока активен синхроимпульс адреса СИЛ. На выходе 27 блока 5 40 сигнал разрешения uacciraeH в течение всего рассматриваемог О цикла.

По окончании а,г;ресной части цикла Ввод ЭВМ посылает синхроимпульс ввода, активируя сигнал на линиях 45 11 и 25 . Этот сигнал поступает на вход блока 3 и на вход элемента И 7 . Блок 3 с задержкой относительно начала сигнала Ввод подключает выходы программно-доступных по 50 чтению разрядов PC источника к линиям 19 и с задержкой относительно начала сигнала Ввод вырабатьшает синхроимпульс ответа на выходе 14. ЭВМ считьшает данные из PC о состоя- 55 НИИ устройства ввода, сопровождаемые синхроимпульсом отлета. Сигналы на выходах 28 и 29 элементов И 6 и 7 в этот момент пассивны, так как ни на одном из элементов И не выполня-

ется условие совпадения. Выходы блока 8 находятся в пассивном состоянии и не оказывают влияния на работу устройства. Цикл Ввод ЭВМ заканчивает ,снимая синхроимпульс ввода Блок 3 после этого отключает выходы программно-доступных по чтению разрядов PC от линий 19 и одновременно снимает синхроимпульс ответа на выходе 14. Б ответ на снятие синхроимпульса ответа ЭВМ снимает сигнал СИА что приводит к снятию сигнала разрешения на В1|Коде 26 устройства. Цикл Ввод окончен.

Проанализировав считанные из PC данные о состоянии устройства ввода, ЭВМ в случае, если устройство готово к работе и нет ошибки в его состоя- НИИ, обращается к PC в цикле Вывод (участок 2, фиг. А). При этом в адресной части этого цикла ЭВМ выставляет на линиях 9 адрес PC 177550. В этой, адресной, части цикла Вывод все процессы идентичны описанным для цикла Ввод. На выходе 26 блока 5 активен в течение всего цикла Вывод сигнал разрешения. Сигнал на выходе 26, пассивен в течение всего рассматриваемого цикла. По окончании адресной части цикла Вьшод ЭВМ выставляет на линиях 9 данные для записи в PC (код 000001 - команда Старт на УВВ), сопровождая выводимые данные синхроимпульсом вьшода. Блок 3, получив синхроимпульс вьшода на соответствующем входе 11, активирует синхроимпульс ответа. С выхода 14 этот сигнал поступает на вход блока 1 и на входы элементов И 6 и 7. На выходе элемента И 7 в рассматриваемом цикле - пассивный сигнал, поэтому в цикле Вьшод на выходе 17 блока 8 активируется сигна Старт, а на выходе 19 блока 8 сигнал пассивен. Происходит занесение основных данных записи в основной PC (расположенный внутри блока 3) и дополнительных данных записи в блок 8. Цикл Вьшод ЭВМ завершает снятием синхроимпульса Вывода, затем через ЭВМ снимает с линий 9 данные. После снятия сигнала вывода блок 3 снимает синхроимпульс ответа на выходе 14, и сигнал на выходе элемента И 6 переходит в пассивное состояние. В ответ на снятие устройством синхроимпульса ответа ЭВМ снимает сигнал СИЛ. Это приводит к снятию

.

10

276398

сигнала разрешения на выходе 26 блока 5. Цикл Вьшод окончг.н. Сигнал Старт на выходе блока 8 включает, например, механизм протя1-ивания, например, считывателя перфоленты, который снимает сигнал готовности.

Возможны два режима работы ЭВМ с устройством: по опросу флага готовности и по прерываниям.

В режиме опроса флага готовности ЭВМ непрерьшно анализирует бит готовности PC в циклах Ввод. По приходу строба СТР-И П, который поступает по линии 12 блока 2, сигнал Старт на выходе 17 блока 8 становится пассивным. Взводится бит готовности PC (внутри блока 3). Как только это происходит, ЭВМ обращается к РД источника в цикле участок 3, фиг. 4). При этом в адресной части цикла ЭВМ выставляет адрес РД / 77552, сопровождая этот адрес выработкой сигналов ВУ и СИА, аналогично циклу Ввод участка 1 (фиг. 4), На выхо15

20

25

0

5

0

5

0

де 27 блока 5 активируется на время рассматриваемого цикла сигнал разрешения, поступающий на вход элемента И 7. Блок 3 после начала сигнала ввода вырабатьшает на соответствующем выходе 15 строб управления вводом данных, а затем синхроимпульс ответа на выходе 14. Строб управления вводом поступает на соответствующий вход блока 2 (а оттуда на УВВ) и на вход регистра 4. По этому стробу регистр 4 подключает основной РД источника к линиям 19. В этот же момент времени на выходе элемента И 7 активируется сигнал разрешения, и дополнительный бит паритета, поступающий с выхода 18 блока 2.(т.е. от УВВ), через элемент И-НЕ 34 передается в линии восьмого разряда линий 19 адреса-данных. Таким образом, вместе с основным байтом данных считывается и дополнительный бит паритета , Завершение цикла - аналогично рассмо ренному на участке 1 (фиг.4). Режим работы по прерьшаниям отличается от рассмотренного тем, что в цикле Вьшод (участок 2, фиг. 4) ЭВМ вместе с командой Старт записывает в PC условие разрешения прерывания (код 000101). После этого ЭВМ может заниматься другой работой, а не опрапгивать непрерьшно флаг готовности устройства. Как только УВВ будет снова готово к вводу данных в

микроэвм, на соответствующем вьгходе 13 блока 3 возникает требование пре- рьшания, поступающее через блок 1 и интерфейс МПИ н ЭВМ, которая завер щает выполнение той команды, во время выполнения которой поступило требование прерывания от данного УЕВ, и выполняет цикл Ввод адреса вектора прерьтания, в результате чего выполняется подпрограмма обслуживания данного УВВ и ввод основных и дополнительных данных от УВВ в ЭВМ (участок 3, фиг. А). После ввода данных ЭВМ, если ввод информации еше не закончен полиостью, вновь записьшает в PC команду.Старт вместе с условием разрешения прерывания, после чего ЭВМ возобновляет выполие- ние прерванной программы до очередного требования прерьшанин, и т.д., пока вся информация от УВВ не будет введена в ЭВМ. Режим работы по пре- рьгоаниям позволяет организовать работу системы в режиме реального времени .

Формула изоб,ретения Устройство для сопряжения внешних устройств с магистралью ЭВМ, содержащее первый и второй блоки усиления первый и второй блоки дешифрации, блок регистров ввода-вывода и буферный регистр, причем первый информационный вход первого блока дешифрации соединен с входом-выходом буферного регистра и первым входом-выходо первого блока усиления, второй вход- выход которого является входом-выходом устройства для подключения к магистрали ЭВМ, второй информационный вход, синхровход, первый, второй и третий выходы первого блока дешифрации соединены соответственно с первыми, вторыми выходами, входами первого блока усиления и первым входом второго блока усиления, вход-выход которого является вхс дом-выходом устройства для подключения к магистрали внешних устройств, а первый выход, вторые вход и выход сосэтветственно подключены к третье.му кпформационно10

5

0

5

0

5

0

5

0

му входу, четвертому выходу блока дешифрации, выходу и информационному входу буферного регистра, входы задания режима и сброса которого подключены соответственно к третьему и четвертому выходам первого блока дешифрации, информационный и синхронизирующий входы второго блока дешифрации подключены соответственно к первому информационному входу-выходу и первому выходу первого блока усиления, первый выход, первый информационный пход и второй выход первого блока регистров ввода-вывода соединены соответственно с третьими входом и выходом второго блока усиления и с первым входом-выходом первого блока усиления, отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены две группы элементов И и группа блоков регистров ввода-вывода, причем первые входы элементов И первой и второй групп подключены соответственно к выходам первой и второй групп второго блока дешифрации, вторые и третьи входы соединены соответственно с вторым вькодом первого блока дешифрации и с вторым выходом первого блока усиления, первые выходы, первые информационные входы и вторые выходы блоков регистров ввода-вывода группы соединены соответственно с группами входов и выходов второго блока усиления и первым входом-выходом первого блока усиления, вторые информационные входы первого блока регистров ввода-вывода и блоков регистров ввода-вьшода группы подключены к первому входу-выходу первого блока усиления, сннхровходы вьшода и ввода и первый н второй входы установки первого блока регистров ввода-вывода и блоков регистров ввода-вьшода группы соединены соответственно с выходами элементов И первой и второй групп, с первым выходом второго блока усиления и с четвертым выходом первого блока дешифрации и четвертым входом второго блока уси7 ления.

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для согласования интерфейсов | 1988 |

|

SU1688249A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1515168A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения ЭВМ с микропроцессором | 1987 |

|

SU1411763A1 |

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1989 |

|

SU1683021A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1987 |

|

SU1413635A2 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

Изобретение относится к вычислительной технике и может быть использовано для электрического и алгоритмического согласования микроЭВМ с периферийными устройствами. Цель изобретения - сокращение аппаратурных затрат устройства. Устройство содержит два блока усиления, два блока дешифрации, буферный регистр, две группы элементов И, первый блок регистров ввода-вывода и группу блоков регистров ввода-вывода. Устройство позволяет организовать дополнительные сигналы управления периферийными устройствами или сигналы дополнительных состояний и стробов, или дополнительные данные периферийных устройств, доступные по чтению, записи или по записи и чтению со стороны микроЭВМ. 4 ил.

V

IL

X

L

31

«+.

л

к

toi Jl&

ч1 Lr:ii

«

&

П

и

i

а ппг1ю 9 и т s s л 3 1 о

isuvjinnttfestjzio

т

npotfia f« t9oe rtj/ bit

gc.vuHvmtiit iitiS i4 i tt}a/vffto-eectryf nn«

pOiftltStj

ЛИЛ уетройстёа Sfodo tomatHOcrr устройстве вводо

poipfuitHtjt пре. ыВота apotflOfmbi tfcmpoucffifOM iioOa

Sam noptifr emodoHHiiuSSo lUlJlJ

H K

кцАоо...т

Редактор В, Петраш

ФигМ

Составитель В. Вертлиб

Техред Л.Сердюкова Корректор Т. Малец

i

4

/top

) йонниг МоЛ

xzr

| Устройство для сопряжения ЭВМ с терминалом | 1985 |

|

SU1282148A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения внешних устройств с магистралью ЭВМ | 1987 |

|

SU1451709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-07—Публикация

1987-06-15—Подача