ел ISD to

k

С

г

itkM.J

Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, имеющих канал МПИ (Электроника-60 ДВК), в автоматизированной системе сбора и обработки дискретной информации, работающей в режиме реального времени.

Цель изобретения - повышение достоверности вводимой информации.

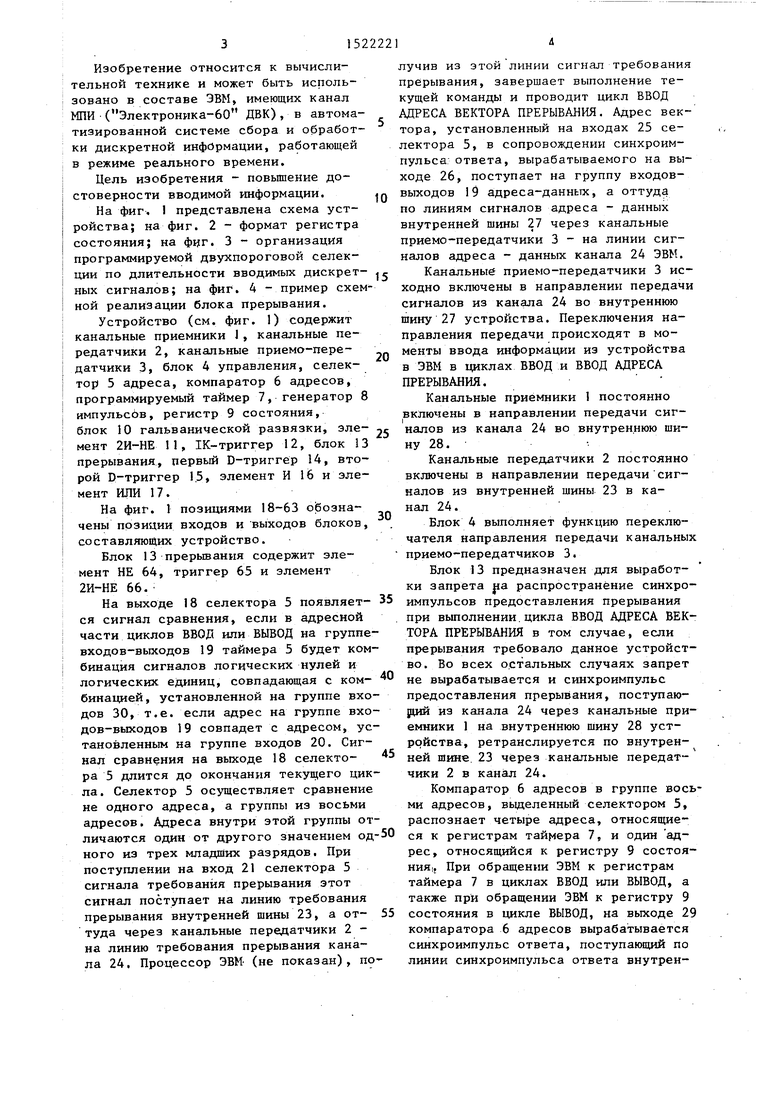

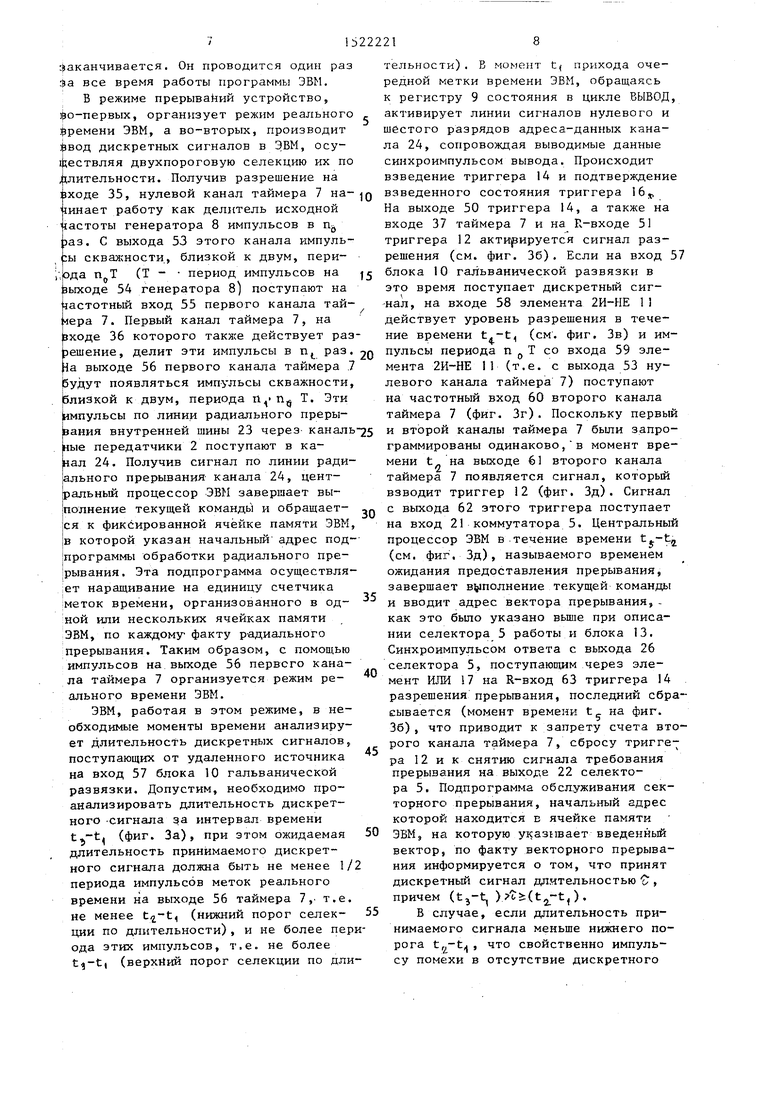

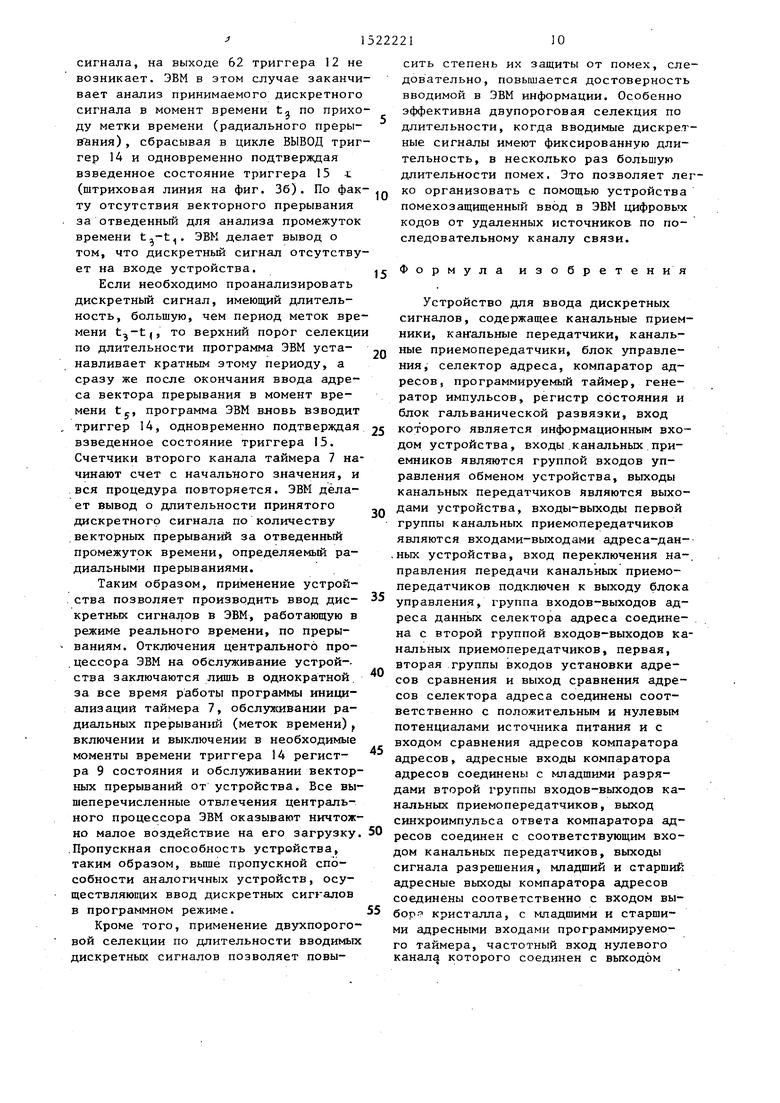

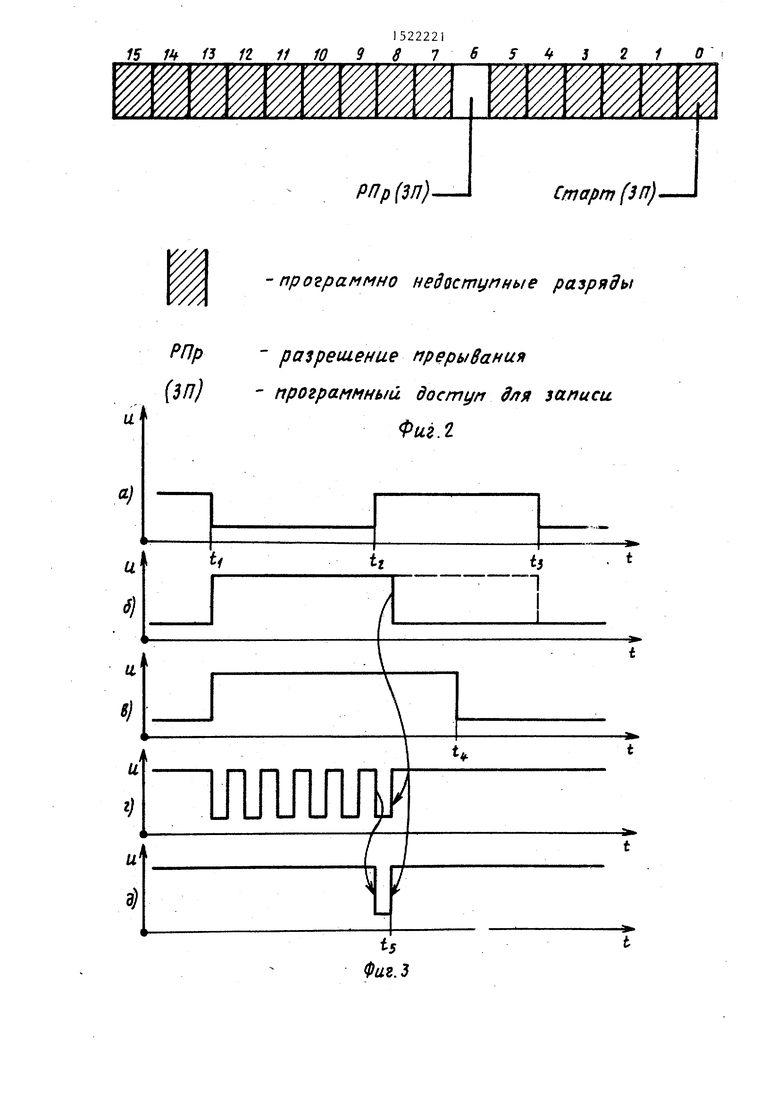

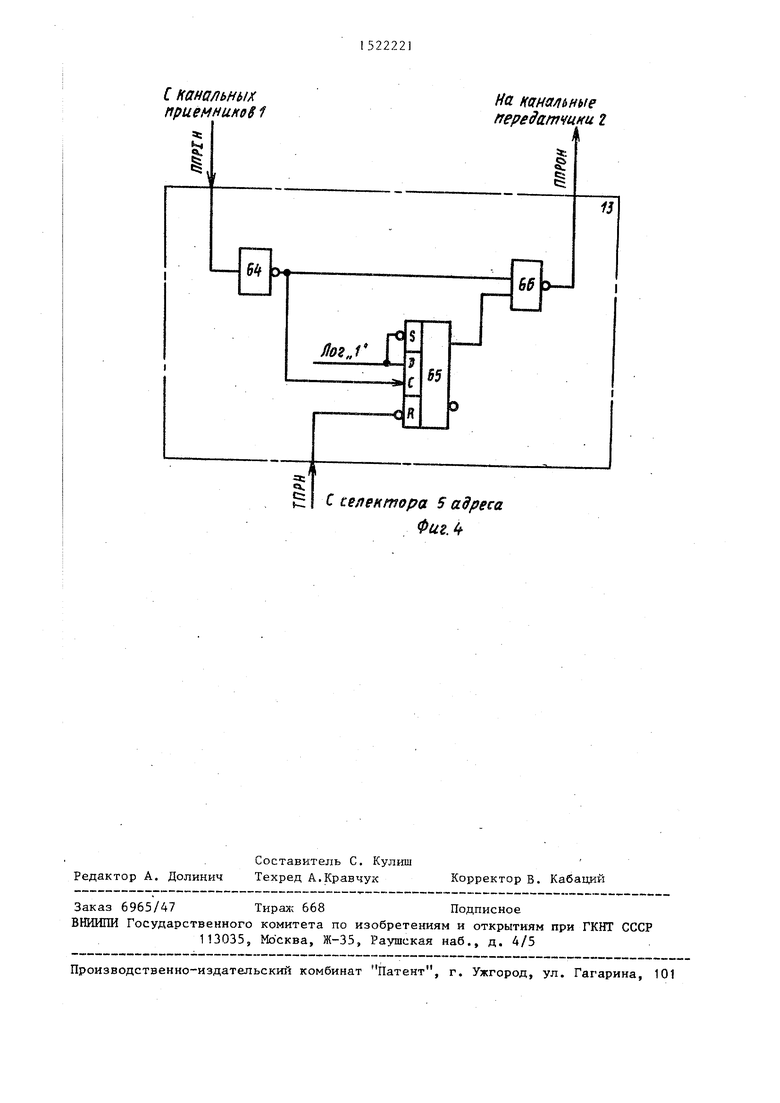

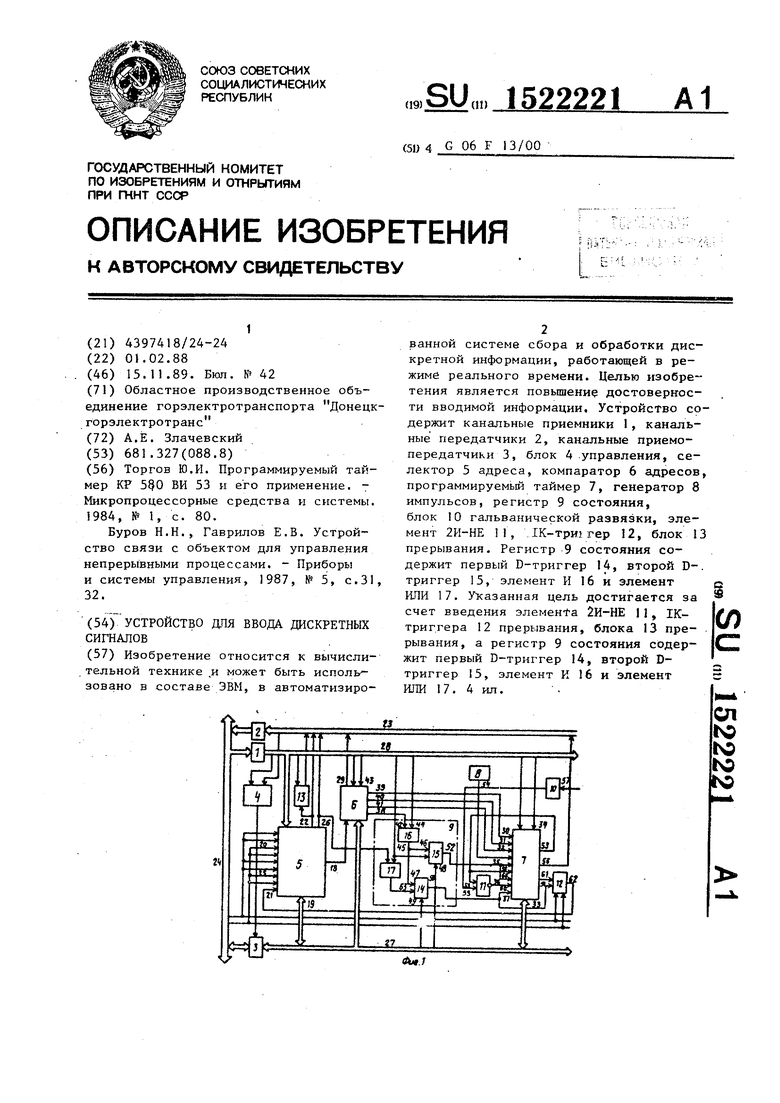

На фиг. I представлена схема устройства; на фиг. 2 - формат регистра состояния; на Фиг. 3 - организация программируемой двухпороговой селекции по длительности вводимых дискрет- ных сигналов; на фиг. 4 - пример схемной реализации блока прерывания.

Устройство (см. фиг. 1) содержит канальные приемники 1, канальные передатчики 2, канальные приемо-пере- датчики 3, блок 4 управления, селектор 5 адреса, компаратор 6 адресов, программируемый таймер 7, генератор 8 импульсбв, регистр 9 состояния, блок 10 гальванической развязки, элемент 2И-НЕ 11, 1К-триггер 12, блок 13 прерывания, первый D-триггер 14, второй D-триггер 1.5, элемент И 16 и элемент ИЛИ 17.

На фиг. 1 позициями 18-63 обозначены позиции входов и выходов блоков, составляющих устройство.

Блок 13 прерывания содержит элемент НЕ 64, триггер 65 и элемент 2И-НЕ 66.

На выходе 18 селектора 5 появляет- ся сигнал сравнения, если в адресной части циклов ВВОД или ВЫВОД на группе входов-выходов 19 таймера 5 будет комбинация сигналов логических нулей и логических единиц, совпадающая с комбинацией, установленной на группе вхо дов 30, т.е. если адрес на группе вхо дов-выходов 19 совпадет с адресом, ус тановленным на группе входов 20. Сигнал сравнения на выходе 18 селектора 5 длится до окончания текущего цик ла. Селектор 5 осуществляет сравнение не одного адреса, а группы из восьми адресов. Адреса внутри этой группы от личаются один от другого значением од ного из трех младших разрядов. При поступлении на вход 21 селектора 5 сигнала требования прерывания этот сигнал поступает на линию требования прерывания внутренней шины 23, а от- туда через канальные передатчики 2 - на линию требования прерывания канала 24. Процессор ЭВМ (не показан), по

20

25

Q

35 5530

40

45

50

лучив из этой линии сигнал требования прерывания, завершает выполнение текущей команды и проводит цикл ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ. Адрес вектора, установленный на входах 25 селектора 5, в сопровождении синхроимпульса ответа, вырабатываемого на выходе 26, поступает на группу входов- выходов 1 адреса-данных, а оттуд по линиям сигналов адреса - данных внутренней шины 27 через канальные приеме-передатчики 3 - на линии сигналов адреса - данных канала 24 ЭВМ.

Канальные приемо-передатчики 3 исходно включены в направлении передачи сигналов из канала 24 во внутреннюю шину 27 устройства. Переключения направления передачи происходят в моменты ввода информации из устройства в ЭВМ в циклах ВВОД и ВВОД АДРЕСА ПРЕРЫВАНИЯ.

Канальные приемники 1 постоянно включены в направлении передачи сигналов из канала 24 во внутреннюю шину 28 .

Канальные передатчики 2 постоянно включены в направлении передачи сигналов из внутренней шины 23 в канал 24.

Блок 4 выполняет функцию переключателя направления передачи канальных приемо-передатчиков 3.

Блок 13 предназначен для выработки запрета ра распространение синхроимпульсов предоставления прерывания при выполнении.цикла ВВОД АДРЕСА ВЕКТОРА ПРЕРЫВАНИЯ в том случае, если прерывания требовало данное устройство. Во всех о.стальных случаях запрет не вырабатывается и синхроимпульс предоставления прерывания, поступаю- рцй из канала 24 через канальные приемники 1 на внутреннюю шину 28 устройства, ретранслируется по внутренней шине. 23 через канальные передатчики 2 в канал 24.

Компаратор 6 адресов в группе восьми адресов, выделенный селектором 5, распознает четыре адреса, относящиеся к регистрам таймера 7, и один адрес, относящийся к регистру 9 состояния. При обращении ЭВМ к регистрам таймера 7 в циклах ВВОД или ВЫВОД, а также при обращении ЭВМ к регистру 9 состояния в цикле ВЫВОД, на выходе 29 компаратора 6 адресов вырабатывается синхроимпульс ответа, поступающий по линии синхроимпульса ответа внутрен

515

ней шины 23 через канальные передатчики 2 в канал 24 ЭВМ.

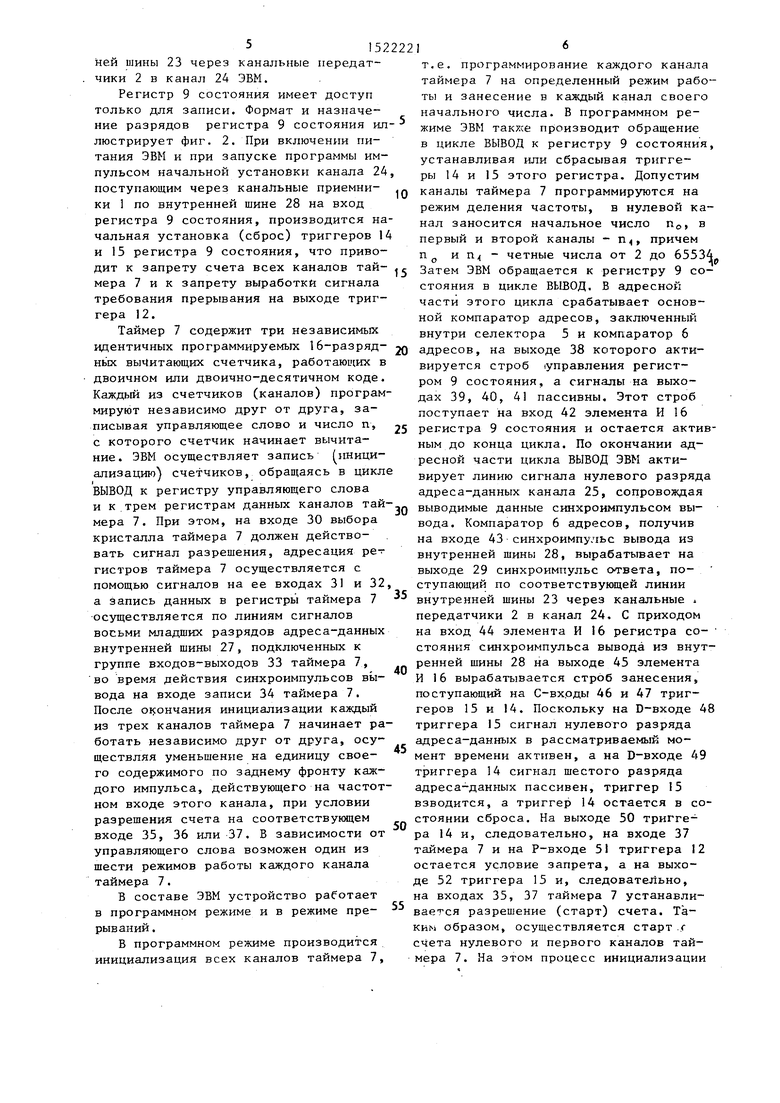

Регистр 9 состояния имеет доступ только для записи. Формат и назначение разрядов регистра 9 состояния ил люстрирует фиг. 2. При включении питания ЭВМ и при запуске программы импульсом начальной установки канала 24 поступающим через канальные приемни- ки 1 по внутренней шине 28 на вход регистра 9 состояния, производится начальная установка (сброс) триггеров 1 и 15 регистра 9 состояния, что приводит к запрету счета всех каналов тай- мера 7 и к запрету выработки сигнала требования прерывания на выходе триггера 12.

Таймер 7 содержит три независимых идентичных программируемых 16-разряд- ньЕх вы11итающих счетчика, работаю1цих в двоичном или двоично-десятичном коде. Каждый из счетчиков (каналов) программируют независимо друг от друга, записывая управляющее слово и число п, с которого счетчик начинает вычитание. ЭВМ осуществляет запись (инициализацию) счетчиков, обращаясь в цикл ВЫВОД к регистру управляющего слова и к трем регистрам данных каналов таймера 7. При этом, на входе 30 выбора кристалла таймера 7 должен действовать сигнал разрешения, адресация рет гистров таймера 7 осуществляется с помощью сигналов на ее входах 31 и 32 а запись данных в регистры таймера 7 осуществляется по линиям сигналов восьми младших разрядов адреса-данных внутренней шины 27, подключенных к группе входов-выходов 33 таймера 7, во время действия синхроимпульсов вывода на входе записи 34 таймера 7. После окончания инициализации каждый из трех каналов таймера 7 начинает работать независимо друг от друга, осуществляя уменьшение на единицу своего содержимого по заднему фронту каждого импульса, действующего на частотном входе этого канала, при условии разрешения счета на соответствующем входе 35, 36 или 37. В зависимости от управляющего слова возможен один из шести режимов работы каждого канала таймера 7.

В составе ЭВМ устройство работает в программном режиме и в режиме прерываний.

В программном режиме производится инициализация всех каналов таймера 7,

5

.с

20 js

35

40

45

50

5

т.е. программирование каждого канала таймера 7 на определенный режим работы и занесение в каждый канал своего начального числа. В программном режиме ЭВМ также прюизводит обращение в цикле ВЫВОД к регистру 9 состояния, устанавливая или сбрасывая триггеры 14 и 15 этого регистра. Допустим каналы таймера 7 программируются на режим деления частоты, в нулевой канал заносится начальное число По, в первый и второй каналы - п, причем Пд и п - четные числа от 2 до 65534 Затем ЭВМ обращается к регистру 9 состояния в цикле ВЫВОД. В адресной части этого цикла срабатывает основной компаратор адресов, заключенный внутри селектора 5 и компаратор 6 адресов, на выходе 38 которого активируется строб управления регистром 9 состояния, а сигналы на выходах 39, 40, 4 пассивны. Этот строб поступает на вход 42 элемента И 16 регистра 9 состояния и остается активным до конца цикла. По окончании адресной части цикла ВЫВОД ЭВМ активирует линию сигнала нулевого разряда адреса-данных канала 25, сопровождая выводимые данные синхроимпульсом вывода. Компаратор 6 адресов, получив на входе 43 синхроимпульс вывода из внутренней шины 28, вырабатывает на выходе 29 синхроимпульс ответа, поступающий по соответствующей линии внутренней шины 23 через канальные i передатчики 2 в канал 24. С приходом на вход 44 элемента И 16 регистра со- стояния синхроимпульса вывода из внутренней шины 28 на выходе 45 элемента И 16 вырабатывается строб занесения, поступающий на С-вхрды 46 и 47 триггеров 15 и 14. Поскольку на D-входе 48 триггера 15 сигнал нулевого разряда адреса-данных в рассматриваемый момент времени активен, а на D-входе 49 триггера 14 сигнал шестого разряда адреса-данных пассивен, триггер 15 взводится, а триггер 14 остается в состоянии сброса. На выходе 50 тригге- ра 14 и, следовательно, на входе 37 таймера 7 и на Р-входе 51 триггера 12 остается условие запрета, а на выходе 52 триггера 15 и, следовательно, на входах 35, 37 таймера 7 устанавливается разрешение (старт) счета. Таким образом, осуществляется старт ..г счета нулевого и первого каналов таймера 7. На этом процесс инициализации

.Заканчивается. Он проводится один раз $а все время работы программы ЭВМ, В режиме прерывайий устройство, i o-nepBbix, организует режим реального )ремени ЭВМ, а во-вторых, производит ивод дискретных сигналов в ЭВМ, осуществляя двухпороговую селекцию их по длительности. Получив разрешение на иходе 35, нулевой канал таймера 7 начинает работу как делитель исходной частоты генератора 8 импульсов в п эаз. С выхода 53 этого канала импуль- , 1:ы скважности., близкой к двум, пери- ,,ода п Т (Т - период импульсов на зыходе 54 генератора 8) поступают на частотный вход 55 первого канала тай- чера 7. Первый канал таймера 7, на зходе 36 которого также действует разрешение, делит эти импульсы в п раз. г1а выходе 56 первого канала таймера .7 |5удут появляться импульсы скважности, Злизкой к двум, периода Т. Эти импульсы по линии радиального прерывания внутренней шины 23 через каналь ные передатчики 2 поступают в канал 24. Получив сигнал по линии ради- janbHoro прерывания- канала 24, центральный процессор ЭВМ завершает вы- 1полнение текущей команды и обращает- ся к фиксированной ячейке памяти ЭВМ, JB которой указан начальньш адрес под- |программы обработки радиального пре- 1рывания. Эта подпрограмма осуществля- |ет наращивание на единицу счетчика |меток времени, организованного в од- :ной или нескольких ячейках памяти ЭВМ, по каждому факту радиального прерывания. Таким образом, с помощью импульсов на выходе 56 первого канала таймера 7 организуется режим ре ального времени ЭВМ.

ЭВМ, работая в этом режиме, в необходимые моменты времени анализирует длительность дискретных сигналов, поступающих от удгшенного источника на вход 57 блока 10 гальванической развязки. Допустим, необходимо проанализировать длительность дискретного Сигнала за интервал времени tj-t. (фиг. За), при этом ожидаемая длительность принимаемого дискретного сигнала должна быть не менее 1/2 периода импульсов меток реального времени на выходе 56 таймера 1,- т.е. не менее , (нижний порог селек- ции по длительности), и не более периода этих импульсов, т.е. не более ( (верхний порог селекции по дли

тельности). В момент t( прихода очередной метки времени ЭВМ, обращаясь к регистру 9 состояния в цикле ВЫВОД активирует линии сигналов нулевого и шестого разрядов адреса-данных канала 24, сопровождая выводимые данные синхроимпульсом вывода. Происходит взведение триггера 14 и подтверждение взведенного состояния триггера 16, На выходе 50 триггера 14, а также на входе 37 таймера 7 и на R-входе 51 триггера 12 активируется сигнал разрешения (см. фиг. Зб). Если на вход 5 блока 10 гальванической развязки в это время поступает дискретный сиг- -нал, на входе 58 элемента 2И-НЕ 11 действует уровень разрешения в течение времени t,-t (см. фиг. Зв) и импульсы периода п Т со входа 59 элемента 2И-НЕ 11 (т.е. с выхода 53 нулевого канала таймера 7) поступают на частотный вход 60 второго канала таймера 7 (фиг. Зг). Поскольку первый и второй каналы таймера 7 были запрограммированы одинаково, в момент времени t на выходе 61 второго канала таймера 7 появляется сигнал, который взводит триггер 12 (фиг. Зд). Сигнал с выхода 62 этого триггера поступает на вход 21 коммутатора 5. Центральный процессор ЭВМ в течение времени (см. фиг, Зд), называемого временем ожидания предоставления прерывания, завершает выполнение текущей команды и вводит адрес вектора прерывания, - как это бьто указано вьшге при описании селектора 5 работы и блока 13. Синхроимпульсом ответа с выхода 26 селектора 5, поступающим через элемент ИЛИ 17 на R-вход 63 триггера 14 разрешения прерывания, последний сбрасывается (момент времени t на фиг. 36), что приводит к запрету счета второго канала таймера 7, сбросу триггера 12 и к снятию сигнала требования прерывания на выходе 22 селектора 5. Подпрограмма обслуживания секторного прерывания, начальный адрес которой находится в ячейке памяти ЭВМ, на которую указывает введенный вектор, по факту векторного прерывания информируется о том, что принят дискретный сигнал длительностью , причем (tj-t, ) tS(t,-t,).

В случае, если длительность принимаемого сигнала меньше нижнего порога , что свойственно импульсу помехи в отсутствие дискретного

сигнала, на выходе 62 триггера 12 не возникает. ЭВМ в этом случае заканчивает анализ принимаемого дискретного сигнала в момент времени t по приходу метки времени (радиального преры- вгания) , сбрасывая в цикле ВЫВОД триггер 14 и одновременно подтверждая взведенное состояние триггера 15 i (штриховая линия на фиг. 36). По фак ту отсутствия векторного прерывания за отведенный для анализа промежуток времени t.,-t. ЭВМ делает вывод о том, что дискретный сигнал отсутствует на входе устройства.

Если необходимо проанализировать дискретный сигнал, имеющий длительность, большую, чем период меток времени , то верхний порог селекци по длительности программа ЭВМ уста- навливает кратным этому периоду, а сразу же после окончания ввода адреса вектора прерывания в момент времени tj, программа ЭВМ вновь бзводит триггер 14, одновременно подтверждая взведенное состояние триггера 15. Счетчики второго канала таймера 7 начинают счет с начального значения, и вся процедура повторяется. ЭВМ делает вывод о длительности принятого дискретного сигнала по количеству векторных прерываний за отведенный промежуток времени, определяемый радиальными прерываниями.

Таким образом, применение устрой- . ства позволяет производить ввод дис- кретных сигналов в ЭВМ, работающую в режиме реального времени, по прерываниям. Отключения центрального процессора ЭВМ на обслуживание устрой-. ства заключаются лишь в однократной. за все время работы программы инициализаций таймера 7, обслуживании радиальных прерываний (меток времени), включении и выключении в необходимые моменты времени триггера 14 регист- ра 9 состояния и обслуживании векторных прерываний от устройства. Все вышеперечисленные отвлечения центрального процессора ЭВМ оказывают ничтожно малое воздействие на его загрузку. .Пропускная способность устройства, таким образом, вьш1е пропускной способности аналогичных устройств, осу- ществляюп1их ввод дискретных сиггалов в программном режиме.

Кроме того, применение двухпорого- вой селекции по длительности вводимых дискретных сигналов позволяет повы

.„ с

- 5

5 0 5

0

сить степень их защиты от помех, следовательно, повышается достоверность вводимой в ЭВМ информации. Особенно эффективна двупороговая селекция по длительности, когда вводимые дискре.т- ные сигналы имеют фиксированную длительность, в несколько раз большую длительности помех. Это позволяет легко организовать с помощью устройства помехозащищенный ввод в ЭВМ цифровых кодов от удаленных источников по последовательному каналу связи.

Формула изобретения

Устройство для ввода дискретных сигналов, содержащее канальные приемники, кандальные передатчики, канальные приемопередатчики, блок управления, селектор адреса, компаратор адресов, программируемый таймер, генератор импульсов, регистр состояния и блок гальванической развязки, вход которого является информационным входом устройства, входы .канальных приемников являются группой входов управления обменом устройства, выходы канальных передатчиков являются выходами устройства, входы-выходы первой группы канальных приемопередатчиков являются входами-выходами адреса-дан- ,ных устройства, вход переключения направления передачи кансшьных приемопередатчиков подключен к выходу блока управления, группа входов-выходов адреса данных селектора адреса соединена с второй группой входов-выходов канальных приемопередатчиков, первая, вторая группы входов установки адресов сравнения и выход сравнения адресов селектора адреса соединены соответственно с положительным и нулевым потенциалами источника питания и с входом сравнения адресов компаратора адресов, адресные входы компаратора адресов соединены с младшими разрядами второй группы входов-выходов канальных приемопередатчиков, выход синхроимпульса ответа компаратора адресов соединен с соответствующим входом канальных передатчиков, выходы сигнала разрешения, младший и старший адресные выходы компаратора адресов соединены соответственно с входом выбор- кристалла, с младшими и старшими адресными входами программируемого таймера, частотный вход нулевого канала которого соединен с выходом

генератора импульсов, вход синхроимпульса чтения и вход синхроимпульса записи программируемого таймера соединены с соответствующими выходами канальных приемников, отличающееся тем, что, с целью повышения достоверности вводимой информации в устройство введены элемент 2И-НЕ, 1К-триггер| блок прерывания, а ре- Q гистр состояния содержит первый D- триггер, второй D-триггер, элемент И и элемент ИЛИ, .вход синхроимпульса ввода блока управления соединен с соответствующим выходом канальных при- 15 емников, вход синхроимпульса ответа соединен с соответствующим входом канальных передатчиков, группа входов управления обменом селектора адреса соединена с соответствующими выходами 2Q канальных приемников, входы ввода и . вывода компаратора адресов соединены с соответствующими выходами канальных приемников, группы входов-выходов данных программируемого таймера соединены25 , с соответствующими входами-выходами второй группы младщих разрядов канальных приемопередатчиков, выход нулевого канала программируемого таймера соединен с частотным вхбдом первого -.. канала и Ь первым входом элемента 2И- НЕ,к второму входу которого подключен выход блока гальванической развязки,выход элемента 2И-НЕ соединен с частотным входом второго канала программируемого таймера,выход радиального преры- вания первого канала которого соединен с соответствующим входом канальных передатчиков, прямой выход второго D-триг- гера соединен с входами размещения счета нулевого и первого каналов программируемого таймера, прямой выход первого D-триггера соединен с входом

.-40

Q 152Q25-.. 40

разрешения счета второго канала программируемого таймера и входом сброса 1К-триггера, синхров юд которого соединен с выходом второго канала программируемого таймера, I- и К-входы 1К-триггера соединены соответственно с положительным и нулевым потенциалами источника питания, первый вход элемента И соединен с выходом строба управления компаратора адресов, второй вход элемента И соединен с выходом синхроимпульса канальных приемников, выход элемента И соединен с синхро- входами первого и второго D-тригге- ров, D-входы которых соединены соответственно с шестым и нулевым разрядами входов-выходов второй группы канальных приемопередатчиков, вход сброса второго D-триггера соединен с первым входом элемента ИЛИ и с выходом начальной установки канальных приемников, второй вход элемента РШИ соединен с выходом синхроимпульса ответа селектора адреса, выход.элемента ИЛИ соединен с входом сброса первого D-триггера, инверсный выход IK- триггера соединен с входом требования прерывания селектора aдpecaj первая и вторая группы входов установки адреса вектора прерывания которого соединены соответственно с положительным и нулевым потенциалами источника питания, выход требования прерывания селектора адреса соединен с соответствующим входом канальных передатчиков, и с входом требования прерывания блока прерывания, вход предоставления прерывания и выход предоставления прерывания которого соединены соот-. ветственно с соответствующими выходами канальных приёмников и входов канальных передатчиков,

т

РПр

(зп)

и.

Ч

I

и

«9

U

ч

и г)

(

и в)

-программно недоступные разряды

pajpeuieHue прерыВаниУ программный доступ д/fя записи. Фиг.2

is 1

I

- t

ШЛШШР

is 1

I

- t

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 1989 |

|

RU2022344C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для сопряжения микроЭВМ с каналами связи | 1989 |

|

SU1786490A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе ЭВМ, в автоматизированной системе сбора и обработки дискретной информации, работающей в режиме реального времени. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит канальные приемники 1, канальные передатчики 2, канальные приемопередатчики 3, блок 4 управления, селектор 5 адреса, компаратор 6 адресов, программируемый таймер 7, генератор 8 импульсов, регистр 9 состояния, блок 10 гальванической развязки, элемент 2И-НЕ 11, УК-триггер 12, блок 13 прерывания. Регистр 9 состояния содержит первый Д-триггер 14, второй Д-триггер 15, элемент И 16 и элемент ИЛИ 17. Указанная цель достигается за счет введения элемента 2И-НЕ 11, УК-триггер 12 прерывания, блока 13 прерывания, а регистр 9 состояния содержит первый Д-триггер 14, второй Д-триггер 15, элемент И 16 и элемент ИЛИ 17. 4 ил.

is Фиг.З

t

С канальнш приемнико81

С селектора 5 адреса ФигЛ

На кс( передатчики г

| Торгов Ю.И | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| - Микропроцессорные средства и системы | |||

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Буров Н.Н., Гаврилов Е,В | |||

| Устройство связи с объектом для управления непрерывными процессами | |||

| - Приборы и системы управления, 1987, № 5, с.31, 32. | |||

Авторы

Даты

1989-11-15—Публикация

1988-02-01—Подача